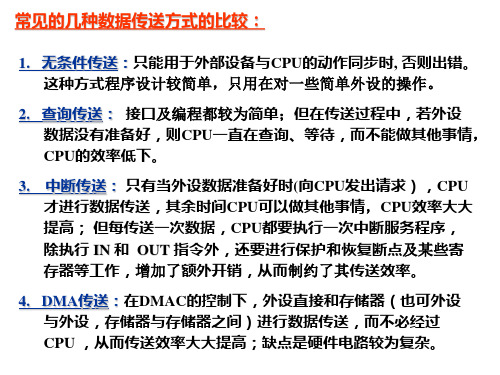

10-8255使用方法汇总

8255编程方法

8255编程方法

8255是一款并行I/O接口芯片,用于扩展微处理器的并行I/O端口。

以下

是8255的编程方法:

1. 初始化8255

在编程8255之前,需要对其进行初始化,为其分配输入输出端口、工作方式和控制字。

这些设置可以在写入控制寄存器时完成。

控制字定义了8255

的工作模式和输入输出端口。

2. 设置控制字

控制字用于设置8255的工作模式和输入输出端口。

控制字由三个部分组成:工作方式选择位、端口A和端口B选择位、C口高4位选择位。

控制字的

每一位都有特定的含义,需要根据需要进行设置。

3. 读写数据

通过8255的输入输出端口进行数据读写时,需要遵循特定的时序要求。

输入时序要求是:先写入输入选择字节,然后读入数据;输出时序要求是:先写入输出数据,然后写入输出选择字节。

在读写数据时,需要保证时序正确,否则可能导致数据传输错误。

4. 结束操作

在完成数据传输后,需要将8255的控制寄存器清零,以结束操作。

以上是8255的编程方法,需要根据具体的硬件设备和应用需求进行编程操作。

8255芯片知识点总结

8255芯片知识点总结一、8255芯片的功能8255芯片的主要功能是实现微处理器与外部设备之间的数据传输和交互。

它提供了24个I/O引脚,可配置为三个8位的并行输入/输出端口。

除了I/O功能之外,8255芯片还具有自动手摇功能,可通过设置控制字来进行不同模式的操作,包括模式0(基本I/O)、模式1(手摇方式)、模式2(双向通讯)和模式3(快速反射)。

在基本I/O模式下,8255芯片的三个端口A、B、C分别作为输出、输入、控制端口。

通过设置控制字可以配置每个端口的工作方式,包括输入、输出和双向通讯。

而在手摇方式下,8255芯片可以通过设置手摇信号来进行数据传输,可以实现16位数据的传输操作。

在双向通讯模式下,8255芯片可以通过读写控制字来实现双向数据传输。

而在快速反射模式下,8255芯片可以实现数据的快速输入和输出,适用于数据采集和高速数据传输等场景。

除了上述功能,8255芯片还可以实现对外设设备的中断请求响应、电源管理和自检功能等。

因此,8255芯片在微处理器系统中扮演着非常重要的角色,可以实现微处理器与外部设备的高效通讯和控制。

二、8255芯片的特点8255芯片具有以下几个显著的特点:1. 多功能性:8255芯片提供了多种工作模式和配置方式,可以适用于不同的应用场景。

用户可以通过编程来设置控制字,实现8255芯片的不同功能。

2. 高性能:8255芯片具有高速的数据传输和处理能力,可以满足对数据传输速度要求较高的应用。

3. 可编程性:8255芯片的功能和工作方式可以通过编程进行配置,可以根据具体的应用需求来设置控制字,实现不同的功能和模式。

4. 可靠性:8255芯片具有良好的稳定性和可靠性,可以在恶劣的环境条件下正常工作。

5. 兼容性:8255芯片广泛应用于各种微处理器系统中,与不同的微处理器兼容性强,可广泛应用于各种系统。

6. 低功耗:8255芯片采用低功耗设计,具有较低的能耗,适用于对电源管理要求较高的应用。

Ch10 8255

March 1, 2018

18

C口的作用与8255A的工作方式有关,它除 了作数据口以外,还有其他用途,故C口的使用 比较特殊,单独介绍如下:

a.作数据口。 b.作状态口。

c.作专用(固定)联络(握手)信号线。

d.作按位控制用。

March 1, 2018

19

10.2.2 8255的控制字

8255A有两类控制字

March 1, 2018

16

8255A的操作功能和端口地址

March 1, 2018

17

与外部设备的连接信号包括:

PA0~PA7:端口A的输入/输出线。 PB0~PB7:端口B的输入/输出线。

PC0~PC7:端口C的输入/输出线。

这24根信号线均可用来连接I/O设备和传送信息。其 中,A口和B口只作输入/输出的数据口用,尽管有时也利 用它们从I/O设备读取一些状态信号,如打印机的“忙” (Busy)状态信号、A/D转换器的“转换结束”(EOC) 状态信号,但对A口和B口来说,都是作8255A的数据口读 入,而不是作8255A的状态口读入的。

2

March 1, 2018

并行通信的定义:

用多根信号传输线进行数据传输,一个时刻可以传送 多个二进制数据位。 实现并行通信的接口就是并行接口。它拥有多根数据 线,一次能发送或接受多个二进制数据位。

并行接口的定义:

在并行接口中,除了少数据场合之外,一般都要 求在接口与外设之间设置并行数据线的同时,至 少还要设置两根握手(联线)信号线,以便进行 互锁异步握手方式(即查询方式)的通信。 参看下面的并行接口与外设连接的示意图

12

④ 读/写控制逻辑

8255工作方式

将OBF置为有效。对于A组,系统规定端口C的第 7位(PC7)用作从端口A输出的OBF信号,对于B组, 规定端口C的第1位(PC1)用作从端口B输出的OBF信

号。

② ACK ——外部应答信号。由外部输入,低电平有 效。 ACK有效,表示外部设备已收到由8255A输出的八 位数据,它实际上是对OBF信号的回答信号。对于A 组,指定端口C的第6位(PC6)用来接收向端口A输入 的ACK信号;对于B组,指定端口C的第2位(PC2)用 来接收向端口B输入的ACK信号。 ③ INTR——中断请求信号。向CPU输出,高电平有 效。

ACKA OBFA

&

O WR PC3 INTRA I/O

PC4, PC5

图7.4 端口A方式 1 输出

ACK:外设应答 OBF:输出缓冲器满 INTE:中断允许 INTR:中断请求

① CPU输出数据 ② CPU发出WR: (1) 数据写到 8255A的端口 (2) WR的低电平清除中断请求 信号INTR (3) WR的上升沿使OBF有效, 表示输出端口满,通知外设取数 据。 ③ 外设接受到数据后,发出 ACK信号: (1) ACK的下降沿使OBF变高, (2) ACK的上升沿使INTE=1, 则INTR变高,发出中断请求,请 求CPU输出新的数据。

3. STB 选通信号:由外设输入,低电平有效、

4. IBF 输入缓冲存储器满信号:向外部输出,高电平 有效。

5. INTR 中断请求信号:向CPU发出,高电平有效。

端口A工作于方式2所需控制信号如下: ① OBFA——输出缓冲存储器满信号。向外部 输出,低电平有效。OBFA有效,表示要求输 出的数据已锁存到端口A的输出锁存器中,正 等待向外部输出。CPU用OUT指令输出数据 时,由WR信号后沿将OBFA置成有效。系统 规定端口C的第7位(PC7)用作由端口A输出的 OBFA信号。

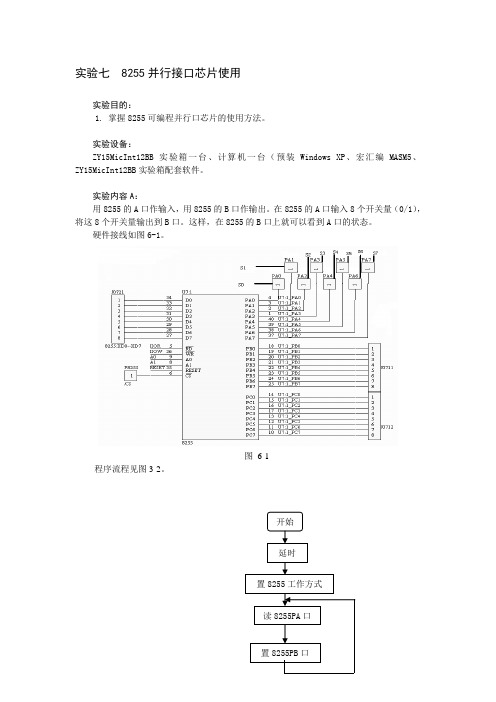

8255并行接口芯片使用

实验七 8255并行接口芯片使用实验目的:1. 掌握8255可编程并行口芯片的使用方法。

实验设备:ZY15MicInt12BB实验箱一台、计算机一台(预装Windows XP、宏汇编MASM5、ZY15MicInt12BB实验箱配套软件。

实验内容A:用8255的A口作输入,用8255的B口作输出。

在8255的A口输入8个开关量(0/1),将这8个开关量输出到B口。

这样,在8255的B口上就可以看到A口的状态。

硬件接线如图6-1。

图6-1程序流程见图3-2。

图6-2编写程序,读出A口状态,然后写到B口并不断重复这一操作(即循环)。

在A口接开关使之能够提供开关量(0/1),在B口的输出上接LED发光二极管及驱动器件,操作开关就可以LED发光或熄灭。

实验内容B:修改程序,使用B口作输入,C口作输出。

预习要求:1.弄懂8255的功能和编程方法。

2.读懂实验的硬件原理图,理解实验要求。

3.编辑建立实验源程序文件,存入U盘保存。

4.写出预习报告。

实验步骤:1.在实验箱上找到本实验主要用到的模块:系统模块、8255模块、开关量输出模块下、0-1指示模块、实验译码单元等。

2.PA0-PA7分别接开关量输出模块S0-S7对应的插座。

3.PB0-PB7分别接0-1指示模块DO71-DO78对应的插座。

4.8255A的片选/CS接地址译码单元的2A0-2A7。

5.数据线XD0—XD7接系统数据线区的任一插座。

6.用串口通信线连接计算机的COM1或COM2到实验箱7.打开实验箱电源。

8.运行实验箱配套软件,根据使用的串行口选择COM1或COM2。

9.建立实验程序文件,保存到C:\MASM50下,然后编译、连接、装载,然后运行。

10.操作8个开关,观察LED的变化。

重要提示:1.源程序应当用.ASM作扩展名,放入MASM50文件夹中。

2.在全速运行程序后,要再次下载程序或调试程序,必须重新启动系统。

实验内容B参考程序:L8255_CMD EQU 2A3HL8255_PA EQU 2A0HL8255_PB EQU 2A1HL8255_PC EQU 2A2HSTACK SEGMENT PARA STACK 'STACK'DB 100 DUP(?)STACK ENDSCODE SEGMENTASSUME CS:CODE,DS:CODEBEGIN:MOV CX,0FFHBB: LOOP BBMOV DX,L8255_CMDMOV AL,82H ;10000010,0方式,PB输入,PC输出 OUT DX,ALCC:MOV DX,L8255_PBIN AL,DXMOV DX,L8255_PCOUT DX,ALJMP CCMOV AX,4C00HINT 21HCODE ENDSEND BEGIN实验A的参考程序:L8255_CMD EQU 2A3HL8255_PA EQU 2A0HL8255_PB EQU 2A1HL8255_PC EQU 2A2HSTACK SEGMENT PARA STACK 'STACK'DB 100 DUP(?)STACK ENDSCODE SEGMENTASSUME CS:CODE,DS:CODEBEGIN:MOV CX,0FFHAA: LOOP AAMOV DX,L8255_CMDMOV AL,9CH ;10011000,0方式,PA输入,PB输出 OUT DX,ALBB:MOV DX,L8255_PAIN AL,DXMOV DX,L8255_PBOUT DX,ALJMP BBMOV AX,4C00HINT 21HCODE ENDSEND BEGIN。

8255设置

8255的方式设置(一)8255A的端口A可以在方式0、方式1、方式2这三种方式下工作,而端口B只能在方式0和方式1这两种方式下工作。

此外,我们也说明了端口的工作方式是由方式选择控制字决定的。

下面,介绍三种工作方式的具体含义。

(1)方式0的工作特点:方式0也叫基本输入/输出方式。

在这种方式下,端口A和端口B可以通过方式选择字规定为输入口或者输出口,端口C分为2个4位端口,高4位为一个端口,低4位为一个端口;这两个4位端口也可由方式选择字规定为输入口或输出口。

概括地说,方式O的基本特点如下:①任何一个端口可作为输入口,也可作为输出口,各端口之间没有规定必然的关系。

②各个端口的输入或输出,可以有16种不同的组合,所以可以适用于多种使用场合。

(2)方式0的使用场合有两种:一种是同步传送,另一种是查询式传送。

在同步传送时,发送方和接收方的动作由一个时序信号来管理,所以,双方互相知道对方的动作,不需要应答信号,也就是说,CPU不需要查询外设的状态。

这种情况下,对接口的要求很简单,只要能传送数据就行了。

因此,在同步传输下使用8255A时,3个数据端口可以实现三路数据传输。

查询式传输时,需要有应答信号。

但是,在方式0情况下,没有规定固定的应答信号,所以,这时,将端口A和端口B作为数据端口,把端口C的4个数位(高4位或者低4位均可)规定为输出口,用来输出一些控制信号,而把端口C的另外4个数位规定为输入口,用来读入外设的状态。

就是这样,利用端口C来配合端口A和端口B的输入/输出操作。

(1)方式1的工作特点:方式1也叫选通的输入/输出方式。

和方式O相比,最重要的差别是A端口和B端口用方式1进行输入/输出传输时,要利用端口C提供的选通信号和应答信号,而这些信号与端口C中的数位之间有着固定的对应关系,这种关系不是程序可以改变的,除非改变工作方式。

概括地讲,方式1有如下特点:①端口A和端口B可分别作为两个数据口工作在方式1,并且,任何一个端口可作为输入口或者输出口。

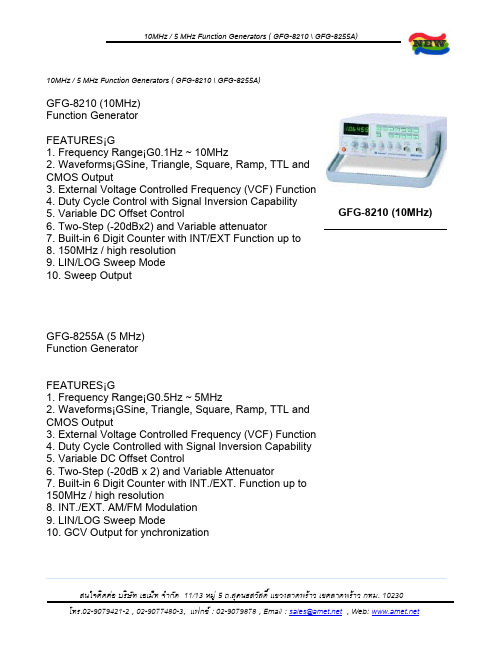

10MHz 5 MHz 功能发生器 (GFG-8210 GFG-8255A) 操作手册说明书

10MHz / 5 MHz Function Generators ( GFG-8210 \ GFG-8255A)Specifications:•10MHz GFG-8210 Specifications:o Maino Frequency Range 0.1Hz ~ 10MHz (8 ranges)o Amplitude >10Vp-p (into 50£[ load)o Impedance 50£[+10%o Attenuator -20dB+1dB x 2o DC Offset <-5V ~ >5V( into 50£[ load)o Duty Control 15% : 85% : 15% to 1MHz Continue variable (square wave only)o Display 6 digits LED displayo---------------------------------------------------------------------------o Sine Waveo Distortion 1% typicalo Flatness + 0.45dB (+5%)o---------------------------------------------------------------------------o Triangle Waveo Linear >98% to 100kHzo----------------------------------------------------------------------------o Square Waveo Symmetry +2%, 1Hz ~ 100kHzo Rise or Fall Time < 35nSo---------------------------------------------------------------------------o CMOS Outputo Max. Frequency 2MHzo Level <4Vpp ~ 14.5Vpp+0.5Vpp adjustableo Rise or Fall Time <120nSo---------------------------------------------------------------------------o TTL Outputo Level >3Vppo Rise or Fall Time <20nSo---------------------------------------------------------------------------o VCFo Input Voltage 0V~10V ¡1V(100 : 1)o Input Impedance 10k£[ ¡0%o---------------------------------------------------------------------------o Sweep Operationo Sweep/Manual Switch selectoro Sweep/Rate >100 : 1 ratio max. and adjustableo Sweep/Time 0.5sec. ~ 30sec. adjustableo Sweep/Mode Lin./Log. switch selectoro Sweep/Out 0V ~ 10+1Vo----------------------------------------------------------------------------o Frequency Countero INT./EXT. Switch selectoro Range 0.1Hz ~ 10MHz (5Hz ~ 150MHz EXT.)o Accuracy Timebase accuracy ¡ counto Timebase ¡Ӳ0ppm (23¢XC¡¢XC) after 30 minutes warm upo Resolution The maximum resolution is 100nHz for 1Hz and 1Hz for 100MHzo Input Impedance 1M£[//150pFo----------------------------------------------------------------------------o Power Source AC 115V/230V¡5%, 50/60Hzo----------------------------------------------------------------------------o Accessories Power cord ¡1,o Instruction manual ¡1,o GTL-101 ¡ 2o----------------------------------------------------------------------------o Dimensions & Weight 251(W) ¡91(H) ¡291(D) mm, Approx. 2.2 kg• 5 MHz GFG-8255A Specifications:o Maino Frequency Range 0.5Hz to 5 MHz (7 ranges)o Amplitude >10Vp-p (into 50£[ load)o Impedance 50£[ +10%o Attenuator -20dB+1dB x 2o DC Offset <-5V ~ >5V (into 50£[ load)o Duty Control 80% : 20% : 80% to 1MHz Continue variable o Display 6 digit LED displayo---------------------------------------------------------------------------o Sine Waveo Distortion <1%, 0.5Hz ~ 100kHzo Flatness <0.3dB, below 500kHz¡F <1dB, below 5MHzo----------------------------------------------------------------------------o Triangle Waveo Linear >98%, 0.5Hz ~ 100kHz¡F >95%, 100kHz ~ 5MHzo---------------------------------------------------------------------------o Square Waveo Symmetry +2%, 1Hz ~ 100kHzo Rise or Fall Time < 50nS at maximum output (into 50£[ load) o----------------------------------------------------------------------------o CMOS Outputo Level 4Vpp+1Vpp ~ 14.5Vpp+0.5Vpp adjustableo Rise or Fall Time <120nSo----------------------------------------------------------------------------o TTL Outputo Level >3Vppo Fan Out 20 TTL loado Rise/Fall Time <25nSo----------------------------------------------------------------------------o VCFo Input Voltage 0V~10V ¡V(100 : 1)o Input Impedance 10k£[ ¡0%o--------------------------------------------------------------------------o GCVo Output Voltage To set the voltage between 0V ~ 2V as per different frequency o----------------------------------------------------------------------------o Sweep Operationo Sweep/Manual Switch selectoro Sweep/Rate 100 : 1 ratio max. and adjustableo Sweep/Time 0.5sec. ~ 30sec. adjustableo Sweep/Mode Lin./Log. switch selectoro----------------------------------------------------------------------------o Amplitude Modulationo Depth 0 ~ 100%o MOD. Frequency 400Hz (INT), DC ~ 1MHz(EXT)o Carrier BW 100Hz ~ 5MHz (-3dB)o EXT Sensitivity <10Vpp for 100% modulationo----------------------------------------------------------------------------o Frequency Modulationo Deviation 0 ~ + 5%o MOD. Frequency 400Hz(INT), DC ~ 20kHz(EXT.)o EXT. Sensitivity <10Vpp for 10% modulationo----------------------------------------------------------------------------o Frequency Countero INT./EXT. Switch selectoro Range 0.5Hz ~ 5MHz (5Hz ~ 150MHz EXT.)o Accuracy Timebase accuracy ¡ Counto Timebase ¡Ӳ0ppm (23¢XC¡¢XC) after 30 minutes warm upo Resolution The maximum resolution is 100nHz for 1Hz and 1Hz for 100MHz o Input Impedance 1M£[//150pFo Sensitivity <35mVrms (5Hz ~ 100MHz)¡F< 45mVrms (100MHz ~ 150MHz)o----------------------------------------------------------------------------o Power Source AC 115V/230V¡5%, 50/60Hzo----------------------------------------------------------------------------o Accessories: Power cord ¡1, Instruction manual ¡1, GTL-101 ¡ 2o----------------------------------------------------------------------------o Dimensions & Weight 251(W) ¡91(H) ¡291(D) mm, Approx. 2.4kg。

8255芯片初始化编程方法

8255芯片初始化编程方法

8255芯片是一种并行I/O接口芯片,由Intel公司生产。

它有三个8位I/O 端口,分别为端口A、端口B和端口C,以及一个控制字寄存器。

通过向控制字寄存器写入不同的控制字,可以配置8255芯片的工作模式,包括输入、输出、中断等。

初始化8255芯片的编程方法如下:

1. 确定工作模式:根据实际需要,确定8255芯片的工作模式。

8255芯片

有四种工作模式,分别为方式0、方式1、方式2和方式3。

2. 配置控制字:根据工作模式,计算控制字的值,并向8255芯片的控制字寄存器写入控制字。

控制字的计算方法可以参考8255芯片的数据手册。

3. 配置端口:根据实际需要,向端口A、端口B和端口C写入相应的数据。

需要注意的是,向端口写入数据时需要将相应的控制位设置为1,否则数据无法写入。

4. 中断配置:如果需要使用8255芯片的中断功能,需要根据实际情况配置中断向量和中断触发方式等参数。

需要注意的是,具体的编程方法可能会因为不同的开发环境和编程语言而有所不同。

因此,在实际编程时,需要参考具体的开发环境和编程语言的相关文档。

8255功能与应用

(1)方式选择控制字

8255A有三种基本工作方式: (1) 方式0——基本输入输出方式 (2) 方式1——选通输入输出方式 (3) 方式3——双向传送方式 方式由CPU输出的命令字决定。

B

(2)C端口置1置0控制字:

•端口C的数位常常作为控制位来使用,所以,应使端 口C中的各位可以用置1置0控制字来单独设置。

A组 控制

A组 A口 (8 位) PA7~PA0

数据

D7~D0

总线 缓冲器

内 部 数 据 总 线

A组 C口 (4 位) PC7~PC4

RD WR A1 A0 RESET CS

读/写 控制 逻辑

B组 C口 (4 位) PC3~PC0

B组 控制

B组 B口 (8 位) PB7~PB0

图8-1

8255A的结构框图

825IOW 译 码 器

A0 A1

RD

WR CS

工作过程:

8255A不断查询打 印机的状态,当 打印机为忙状态, 8255A处于查询等 待状态。 当打印机为空闲 状态时,CPU通过 8255A向打印机输 出一个字符。

复位PC6:00001100(0CH) 置位PC6:00001101 (0DH)

A 口

B 口

图 8 2

-

82 55

A 引 脚 分 布 图

C 口

表5-1

8255A端口选择表

例:8255的A1、A0引脚分别接总线的A1、 A0,已知8255的A口地址为218H,问B 口、C口、控制口地址分别为多少? 219H、21AH、21BH

三、8255A的编程控制字

(1)工作方式控制字:用来设定通道的工作 方式及数据的传送方向的。 (2)C口按位置位/复位控制字:向控制寄存 器写入控制字,而使它的每一位置位或复位。 两个控制字的差别: 工作方式控制字放在程序的开始部分; 按位置位 / 复位控制字可放在初始化程序以 后的任何地方。

8255的使用

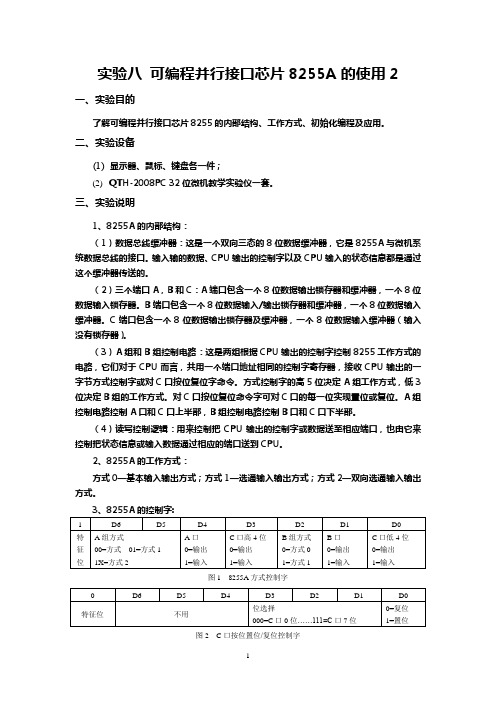

实验八可编程并行接口芯片8255A的使用2一、实验目的了解可编程并行接口芯片8255的内部结构、工作方式、初始化编程及应用。

二、实验设备(1)显示器、鼠标、键盘各一件;(2)QTH-2008PC 32位微机教学实验仪一套。

三、实验说明1、8255A的内部结构:(1)数据总线缓冲器:这是一个双向三态的8位数据缓冲器,它是8255A与微机系统数据总线的接口。

输入输的数据、CPU输出的控制字以及CPU输入的状态信息都是通过这个缓冲器传送的。

(2)三个端口A,B和C:A端口包含一个8位数据输出锁存器和缓冲器,一个8位数据输入锁存器。

B端口包含一个8位数据输入/输出锁存器和缓冲器,一个8位数据输入缓冲器。

C端口包含一个8位数据输出锁存器及缓冲器,一个8位数据输入缓冲器(输入没有锁存器)。

(3)A组和B组控制电路:这是两组根据CPU输出的控制字控制8255工作方式的电路,它们对于CPU而言,共用一个端口地址相同的控制字寄存器,接收CPU输出的一字节方式控制字或对C口按位复位字命令。

方式控制字的高5位决定A组工作方式,低3位决定B 组的工作方式。

对C口按位复位命令字可对C口的每一位实现置位或复位。

A组控制电路控制A口和C口上半部,B组控制电路控制B口和C口下半部。

(4)读写控制逻辑:用来控制把CPU输出的控制字或数据送至相应端口,也由它来控制把状态信息或输入数据通过相应的端口送到CPU。

2、8255A的工作方式:方式0—基本输入输出方式;方式1—选通输入输出方式;方式2—双向选通输入输出方式。

3、8255A的控制字:图1 8255A方式控制字图2 C口按位置位/复位控制字四、实验原理图图3 可编程并行接口8255电路五、实验内容I/O输入输出实验:利用8255的A口读取开关状态、B口把状态送发光二极管显示。

六、实验步骤(1)实验连线该模块的WR、RD分别连到PC104总线接口模块的IOWR、IORD。

该模块的数据(AD0~AD7)、地址线(A0~A7)分别连到PC104总线接口模块的数据(D0~D7)、地址线(A0~A7)。

8255方式一输入输出(中断)new

out dx,al

mov bl,8 ll: int_proc: jmp ll

;BL为中断次数计数器

;中断服务程序 mov dx,288h ;自8255A口输入一数据 in al,dx mov dl,al ;将所输入的数据保存到DL mov ah,02h ;显示ASCII码为DL的字符 int 21h mov dl,0dh ;回车 mov ah,02h int 21h mov dl,0ah ;换行 mov ah,02h int 21h mov dx,20h ;发出EOI结束命令 mov al,20h out dx,al dec bl ;计数器减1

DB

D0~D7

PA7 ~ PA0

8255 nRD nWR A1 PC A0 RESET (ACKIOW

AB

INTR nINTA

PC3

(INTA)

nRD nWR 20H 21H A0 D0 ~ D7 接CPU总线 槽里的数据 线D0~D7

288H

nCS A0

8259

IR3 INT

8255输出

nINTA

程序清单

start:

code segment assume cs:code mov ax,cs mov ds,ax mov dx,offset int_proc mov ax,250bh ;设外部中断int_proc类型号为0BH int 21h mov dx,21h in al,dx and al,0f7h ;开放IRQ3中断 out dx,al mov dx,28bh ;置8255为A口方式1输出 mov al,0a0h out dx,al mov al,0dh ;将PC6置位 out dx,al

nINTA

8255方式一输入

8255芯片说明及其应用

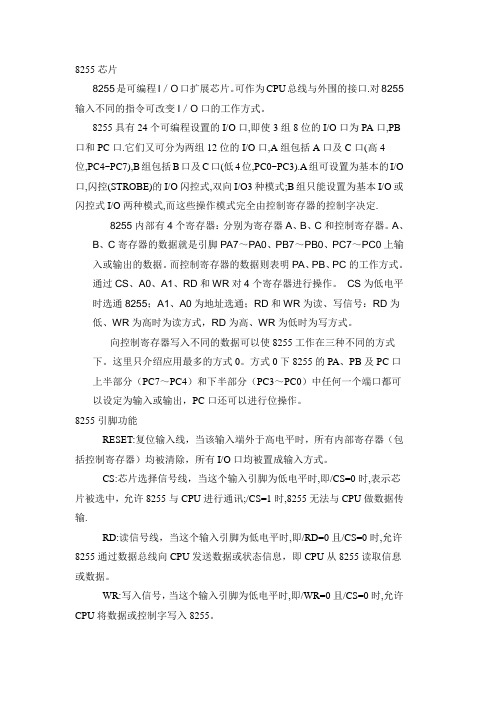

8255芯片8255是可编程I/O口扩展芯片。

可作为CPU总线与外围的接口.对8255输入不同的指令可改变I/O口的工作方式。

8255具有24个可编程设置的I/O口,即使3组8位的I/O口为PA口,PB 口和PC口.它们又可分为两组12位的I/O口,A组包括A口及C口(高4位,PC4~PC7),B组包括B口及C口(低4位,PC0~PC3).A组可设置为基本的I/O 口,闪控(STROBE)的I/O闪控式,双向I/O3种模式;B组只能设置为基本I/O或闪控式I/O两种模式,而这些操作模式完全由控制寄存器的控制字决定.8255内部有4个寄存器:分别为寄存器A、B、C和控制寄存器。

A、B、C寄存器的数据就是引脚PA7~PA0、PB7~PB0、PC7~PC0上输入或输出的数据。

而控制寄存器的数据则表明PA、PB、PC的工作方式。

通过CS、A0、A1、RD和WR对4个寄存器进行操作。

CS为低电平时选通8255;A1、A0为地址选通;RD和WR为读、写信号:RD为低、WR为高时为读方式,RD为高、WR为低时为写方式。

向控制寄存器写入不同的数据可以使8255工作在三种不同的方式下。

这里只介绍应用最多的方式0。

方式0下8255的PA、PB及PC口上半部分(PC7~PC4)和下半部分(PC3~PC0)中任何一个端口都可以设定为输入或输出,PC口还可以进行位操作。

8255引脚功能RESET:复位输入线,当该输入端外于高电平时,所有内部寄存器(包括控制寄存器)均被清除,所有I/O口均被置成输入方式。

CS:芯片选择信号线,当这个输入引脚为低电平时,即/CS=0时,表示芯片被选中,允许8255与CPU进行通讯;/CS=1时,8255无法与CPU做数据传输.RD:读信号线,当这个输入引脚为低电平时,即/RD=0且/CS=0时,允许8255通过数据总线向CPU发送数据或状态信息,即CPU从8255读取信息或数据。

WR:写入信号,当这个输入引脚为低电平时,即/WR=0且/CS=0时,允许CPU将数据或控制字写入8255。

8255输入输出知识要点

8255输入输出知识要点8255输入输出是指使用8255芯片进行输入和输出操作的技术。

8255芯片是一种通用输入输出设备,可用于控制和监测外部设备。

本文将介绍8255输入输出的原理、应用和特点。

一、8255芯片的原理8255芯片是一种具有三个8位双向并行端口的设备,分别称为PortA、PortB和PortC。

PortA和PortB可以用作输入端口或输出端口,而PortC的8位则用作控制信号。

通过对PortC的控制,可以实现输入输出的选择和控制。

8255芯片的输入和输出方式有两种:模式0和模式1。

模式0是将PortA和PortB分别设置为输入和输出端口,而模式1则是将PortA设置为输入端口,PortB设置为输出端口。

二、8255芯片的应用1. 控制外部设备:8255芯片可以与各种外部设备连接,如LED显示器、数码管、键盘等。

通过对PortA和PortB的输入输出控制,可以实现对外部设备的控制和监测。

2. 数据采集和传输:8255芯片可以将外部设备采集到的数据输入到计算机中,也可以将计算机处理后的数据输出到外部设备中。

这在工业自动化和科学实验中非常常见。

3. 并行通信:8255芯片可以作为并行通信接口的一部分,实现计算机和外部设备之间的高速数据传输。

4. 扩展IO端口:由于计算机的IO端口有限,当需要连接更多的外部设备时,可以使用8255芯片扩展IO端口,从而实现更多的输入输出功能。

三、8255芯片的特点1. 灵活性强:8255芯片可以根据需要配置为不同的输入输出模式,适应各种应用场景。

2. 高速传输:8255芯片支持高速数据传输,可以满足对数据传输速度要求较高的应用。

3. 兼容性好:8255芯片与多种外部设备兼容,可以与各种通信协议和设备进行连接。

4. 易于编程:8255芯片的控制信号可以通过编程来实现,编程语言可以是汇编语言或高级语言。

5. 成本低廉:8255芯片是一种低成本的通用IO设备,适用于大规模生产和广泛应用。

8255传输方式与工作方式

8255A传输方式与工作方式一、8255A芯片介绍8255A是Intel公司生产的可编程并行I/O接口芯片,它具有3个八位的并行I/O口,三种工作方式,可通过编程改变其功能,使用灵活方便,可作为单片机与多种外围设备连接时的中间接口电路。

1、引脚说明8255A共有40只引脚采用双列直插式封装,各引脚功能如下。

D7~DO:三态双向数据线,与单片机数据总线连接,用来传送数据信息。

V:片选信号线,低电平有效,表示本芯片被选中。

C CRD:读出信号线控制8255A数据的读出。

W R:写入信号线控制8255A的数据写入。

V:+5V电源。

C CPA7~PA0:A口输入/输出线。

PB7~PB0:B口输入/输出线。

PC7~PC0:C口输入/输出线。

A1~A0:地址线,用来选择8255A内部四个端口。

2、内部结构(1)端口A、B、CPA口:一个八位数据输出锁存器和缓冲器;一个八位数据输入锁存器。

PB口:一个八位数据输出锁存器和缓冲器;一个八位数据输入缓冲器。

PC口:一个八位数据输出锁存器;一个八位数据输入缓冲器。

通常PA口、PB口作为输出输入端口,PC口可作为输出输入端口,也可在软件控制下,分为两个四位端口,作为端口A、B 选通方式操作时的状态控制信号。

(2)A组和B组控制电路这是两组根据CPU写入的“命令字”控制8255A工作方式的控制电路。

A组控制PA口和PC口上半部分;B组控制PB口和PC口下半部,并可根据“命令字”对端口的每一位实现按位“置位”或“复位”。

(3)数据总线缓冲器数据总线缓冲器是一个三态双向8位缓冲器,作为8255A与系统总线之间的接口,用来传送数据、指令、控制命令以及外部状态信息。

(4)读/写控制逻辑电路读/写控制逻辑电路接收CPU发来的控制信号RD、W R、RESET、地址信号A1~A0等,根据要求,将端口数据读出送往CPU或者将CPU 送来的数据写入端口。

二、8255A 工作方式8255A 有三种基本工作方式:(1)方式0:基本输入输出;(2)方式1:选通输入输出;(3)方式2:双向传送(仅A 口有此工作方式)。

8255的编程和使用

8255的编程和使用姓名:王涛学号:PB07210360实验目的1. 学习并掌握 8255 的工作方式及其应用;2. 掌握 8255 典型应用电路的接法。

实验内容基本输入输出实验。

编写程序,使 8255 的 A 口为输入,B 口为输出,完成拨动开关到数据灯的数据传输。

要求只要开关拨动,数据灯的显示就发生相应改变。

实验原理(1)INTEL 8255是一种通用的可编程并行I/O接口芯片,是专为INTEL公司的微处理器设计的,也可用于其它系列的微型机系统中。

利用8086汇编指令系统,编制初始化程序,可以变更8255 的工作方式,通用性强,使用灵活。

8255具有3个带锁存或缓冲的数据端口,它的并行数据宽度为8位。

可与外设并行进行数据交换。

A口和B口内具有中断控制逻辑,在外设与CPU之间可用中断方式进行信息交换。

8255能与许多外部设备连接,例如:键盘、显示器、打印机等。

(a)工作方式控制字 (b)C口按位置位/复位控制字则可知,PORT_A工作方式0且输出,PORT_B工作方式0输出,工作方式控制字为10010000B。

(2)输入/输出接口编址输入/输出接口编址见下表。

若使用IOY1,PORT A~D地址为0640H、0642H、0644H和0646H。

附表2-2 输入/输出接口编址实验步骤本实验使 8255 端口 A 工作在方式 0 并作为输入口,端口 B 工作在方式 0 并作为输出口。

用一组开关信号接入端口 A,端口B 输出线接至一组数据灯上,然后通过对 8255 芯片编程来实现输入输出功能。

实验程序流程如图2-1,具体实验步骤如下述:(1)实验接线图如图2-2 所示,按图连接实验线路图;(2)编写实验程序,经编译、连接无误后装入系统;(3)运行程序,改变拨动开关,同时观察 LED 显示,验证程序功能。

图 2-1 8255基本输入输出参考程序流程图图 2-2 8255 基本输入输出实验接线图汇编源代码PORT_A EQU 0640H //A口地址PORT_B EQU 0642H//B口地址PORT_C EQU 0646H//C口地址CODE SEGMENTASSUME CS:CODESTART:MOV AL, 10010000BMOV DX, PORT_COUT DX, ALLOOP:MOV DX, PORT_AIN AL, DXMOV DX, PORT_BOUT DX, ALJMP LOOPCODE ENDSEND START代码分析:代码运行是个循环,不断地从端口a读入开关信号端口b输出控制灯的信号。

8255可编程并行接口知识点总结

可编程并行接口8255知识点总结8255A 是INTEL系列的并行接口芯片,由于它是一种可编程的外部接口部件,通常作为微机系统总线与外部设备的接口控制部件,可通过软件来设置芯片的工作方式,用8255A 连接外部设备时,通常不需要附加外部电路,给使用带来很大的方便。

1、内部结构2、引脚说明8255作为主机与外设的连接芯片,必须提供与主机相连的3个总线接口,即数据线、地址线、控制线接口。

同时必须具有与外设连接的接口A、B、C口。

由于8255可编程,所以必须具有逻辑控制部分,因而8255内部结构分为3个部分:与CPU连接部分、与外设连接部分、控制部分。

(1)与CPU连接部分根据定义,8255能并行传送8位数据,所以其数据线为8根D0~D7。

由于8255具有3个通道A、B、C,所以只要两根地址线就能寻址A、B、C口及控制寄存器,故地址线为两根A0、A1。

此外CPU要对8255进行读、写与片选操作,所以控制线为片选、复位、读、写信号。

各信号的引脚编号如下:总线分类:(2)与外设接口部分8255有3个通道A、B、C与外设连接,每个通道又有8根线与外设连接,所以8255可以用24根线与外设连接,若进行开关量控制,则8255可同时控制24路开关。

①数据端口A、B、C端口A(PA0-PA7):对应了1个8位的数据输入锁存器和1个数据输出锁存/缓冲器。

所以A 作为输入或输出时,数据均受到锁存。

端口B(PB0-PB7):对应了1个8位的数据输入缓冲器和1个数据输出锁存器/缓冲器。

所以B 输入锁存,输出不受到锁存。

端口C(PC0-PB7):对应1个8位数据缓冲器和1个数据输出锁存/缓冲器,所以C输入不锁村,输出锁存。

当8255工作于应答I/O方式时,C口用于应答信号的通信。

A、B组的逻辑控制功能A组:组成:端口A(PA0-PA7)和端口C的高4位(PC4-PC7)这几个端口由A组统一进行逻辑控制。

B组:组成:端口B(PB0-PB7)和端口C的低4位(PC0-PC3)(3)A、B组分配:A组由端口A作为与外设交换数据的输入/输出接口,C口的高4位作为外设连接的控制信号线和状态信号线,以配合A口工作。

ch10 并行输入输出接口8255解读

14

3、并行接口概述

并行接口连接CPU与并行外设,实现 两者间的并行通信, 在信息传送过程中,起到输出锁存或输入缓冲的作用。

并行接口的典型硬件结构包括: 1、一个或一个以上具有锁存或缓冲的数据端口 2、与CPU进行数据交换所必须的控制和状态信号 3、与外设进行数据交换所必须的控制和状态信号 4、端口译码电路 5、控制电路

总线

8255

22

端口A

有 3 种工作方式( 方式 0、方式 1、方式 2)

对外 8 根引脚 PA7 ~ PA0

reset

RESET

D7

D7 数据

~ D0

~

D0

缓冲器

IOR IOW

A9 ~ A2 A1 A0

RD WR

片选 CS 译码

A1 A0

读写 控制

片内 译码

端口A

端口C

端口B 控制口

D

总线

8255

→接口中状态寄存器发中断请求; (“输出准备好”=1,表示CPU可以往接口中输出数据)

→ CPU向接口输出数据,数据到接口缓冲寄存器; →接口自动清除“输出准备”好。 将数据送往外设: 接口向外设发送一个“驱动信号”,启动外设接收数据。 →外设收到数据向接口发一个“数据输出回答”信号; →接口收到的信号将状态寄存器中“输出准好”=1; → CPU输出下一个数据。

15

并行接口连接外设示意图

数据总线

读出信号

写入信号

复位

CPU

准备好

中断请求

控制寄存器 输入缓冲寄存器 输出缓冲寄存器

状态寄存器

地址 地址 译码

片选

A0 A1

数据输入准备好 输

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

• 扩展2764/27128

扩展程序存储器ROM

– 2764为8K紫外线可擦写EPROM,27128为16K紫外线可擦写 EPROM

扩展数据存储器RAM

• MCS-51的数据存储器

– 片内128Byte – 片外可扩展64K

• 常用数据存储器芯片

– 61162K × 8位 – 62648K × 8位 – 6225632K × 8位

~ D7 ~ D0

LE 74LS373

OE

Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0

思考:2片74LS373与89C51的连接图

计算74LS373的地址(8051送出何种地址码时可以将数送到Q端)

P27 P0.0 A15 P0.1 P0.2 0 P0.3 P0.4 1 P0.5 P0.6 89C51 P0.7 ALE P2.0 P2.1 P2.2 P2.3 P2.4 P2.5 P2.6 P2.7 P26 A14 1 P25 P24 P23 P22 P21 P2 0 P07 P06 P05 P04 74LS373 A0 D0 A13 D1 A12A0 A11 A10 A9 A8 A7 A6 A5 A4 A1 A2 * D2 * * * * * * * D3* A3 * D4 A4 * * A5* * * * * * * * D5 D6 A6 D7 A7 LE OE P03 P02 P01 P00 A3 * A2 A1 A0 * * *

• P0口输出低8位地址线信号时,ALE有效 • 扩展系统总线时采用ALE作锁存信号,将低8位地址锁存在 74HC373中 • 74HC373输出的地址总线低8位+P2输出的地址总线高8位构成 16位地址总线

MCS-51三总线(续)

• 数据总线(Data Bus, DB)

– P0口做8位数据总线

• 控制总线(Control Bus, CB)

A0

AB

A15

PSEN WR RD

A15

CB

+

地址码的计算

计算74LS373的地址(8051送出何种地址码时可以将数送到Q端)

P27 P26 P25 A13 * P24 A12 * P23 P22 P21 P2 0 P07 P06 P05 P04 P03 P02 P01 P00 A8 A7 A6 A5 * * * * A4 A3 * * A2 A1 A0 * * * A15 A14 0 * A11 A10 A9 * * *

• 6116的引脚

– – – – – – A0~A10,地址输入线 D0~D7,双向三态数据线 CE,片选输入线低电平有效,选中该芯片 OE,读选通输入信号,低电平有效 WE,写选通输入信号,低电平有效 VCC,GND,电源

扩展RAM 278255)

• 74LS373

– 带三态输出的8-D锁存器 – 三态控制端OE接地,保持常通状态 – G(CP/LE)端接ALE信号,每当ALE产生下跳变时,373 锁存P0口的低8位地址

8.1.1 74LS373的扩展

1、 74LS373的结构

D0 D1 D2 D3

D Q CP D Q CP D Q CP D Q CP D Q CP D Q CP D Q CP D Q CP

– – – – ALE低8位地址选通信号 PSEN扩展程序存储器读选通信号 EA内、外程序存储器选择信号 RD、WR扩展数据存储器、I/O口读、写选通信号

• 片上I/O口

– 扩展三总线后,MCS-51单片机剩下P1和部分P3口做I/O 口线

8.1 不可编程并行口芯片的扩展

8.1.1 74LS373的扩展

Q0 Q1 Q Q3 Q4 Q5 Q6 Q7

2、 74LS373的引脚

D4 D5 D6 D7 LE

OE

3、 74LS373与89C51的连接

连接图

思考

74LS373与89C51的连接图 DB

P0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 89C51 P0.7 ALE P2.0 P2.1 P2.2 P2.3 P2.4 P2.5 P2.6 P2.7 74LS373 D0 A0 D1 A1 D2 A2 D3 A3 D4 A4 D5 A5 D6 A6 D7 A7 LE OE

• CE接P2口地址线P2.7,A0~A12接地址总线的A0~A12,A13,A14未接, 地址范围为: A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 0 x x 0 0 0 0 0 0 0 0 0 0 0 0 0 0 x x 1 1 1 1 1 1 1 1 1 1 1 1 1 • 2764地址范围:0000H~1FFFH

第八章 MCS-51并行口的扩展

MCS51单片机内部有4个并行口,当内部并行口不够用

时可以外扩并行口芯片。可外扩的并行口芯片很多,分成2

类:不可编程的并行口芯片(74LS3734和74LS245)和可编 程的并行口芯片(8255)。 8.1 不可编程并行口芯片的扩展 8.2 可编程并行口芯片的扩展

扩展三总线

• 外部扩展总线

– 地址、数据、控制

MCS-51三总线

• 地址总线(Address Bus, AB)

– 传送地址信号,进行存储单元和I/O口访问 – 单向信号 – 地址总线数目决定访问存储单元数目

• MCS-51地址总线具有16条,可访问216 = 65536 =64K 存储单元

– MCS-51的地址总线由分时访问的P0口做低8位地址线, P2口做高8位地址线

8.2.1 8255的结构 8.2.2 8255的引脚 8.2.3 8255的工作方式 8.2.4 8255的控制字 8.2.5 8255的应用

DB

0

*

*

*

*

AB

A15

A14 A15

CB

+ +

PSEN WR RD

~ D7 ~ D0 LE 74LS373

OE

~ D7 ~ D0 LE 74LS373

OE

Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0

Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0

• 2764

扩展程序存储器

– 8K EPROM – 使用A0~A12共13根地址线,具有213=8192个存储单元 – CE为片选输入端,低电平有效。CE有效时,系统选中该芯片, 可以读取EPROM中的程序指令或数据 – 确定2764的地址