苹果Q41A笔记本电脑图纸

笔记本电脑主板新图纸(全)

29 38 PMH-7G/A Serial ATA I/F USB 2.0 Port1 Mocha-1 Block Diagram 34 Media Slice VCC1R8B S-BAT-PWR CRT UltraSlimBay RJ45 USB2514 USB Hub SMSC MAX6694 Thermal Sensor SMBus SATA Port 1 I/F 20,21,22,23 34 CRT Port Media Slice 195 40 Processor 15 Serial ATA 150MB/s PCI Express CRT I/F G-Sensor 42 CH10 Bluetooth 31 CH8 DDR3 1067/800 Channel A UNBUFFERED DDR3 SODIMM Reverse Socket 204-PIN DDR3 SODIMM 13 14 Channel B DDR3 1067/800 VCC1R05AMT/VCC1R5A VCC5V_OUT VCC3M VCC1R05AMT VCC1R5A VCC1R8B BD3550 VT351A 50 52,53 I2C Bus / SM Bus Thermal Sensor LM26 5

Trace should be less than 0.5 inch 2 2 2 2 2 TPAD302 22 2 22 2 2

E 2 2 22 MAX6694TE9A-2-GP 2 E 22 SC2200P50V2KX-2GP E 22 2 2 2 22 2 2 22

18 Display Port 3029 Azalia bus IOSUB Card Conn. 32 USB 2.0CH5 Media Card Reader 3-in-1 Slot USB 3 USB2.0 CH6VCC1R5A VCC0R75AMT BD3550 MAX1510 Display Port RJ 11Conn Audio Codec IOSUB Card (LCD Conn)HP OUT MIC IN 16

笔记本电脑主板新图纸(全)

Title21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,Wistron CorporationTaipei Hsien 221, Taiwan, R.O.C.<Variant Name>1067/800MHzAGTL+ FSBIntel ICH9-MUSB 2.0 (12 ports)LAN Connect I/F (LCI)AC97 2.3/Azalia InterfaceACPI 2.0INT. RTCLPC I/FPCI Rev 2.3L7:GND L3:Signal 1System DC/DCVINT20L4:VCC L8:ComponentL1:Component OUTPUTSL6:Signal 3L2:GND PCB Layer StackupINPUTSTPS51221L5:Signal 2Sep.4VCC3MVCC5M Battery Charger/SelectorADP3808DOCK_PWR20_FM-BAT-PWR VINT20VT1311CPU DC/DCVCCCPUCORE3,47,8,9,10,11,124449Penryn SV IntelIntel Cantiga-GMLVDS INTEGRATED GRAHPICSDDR3 1067/800MHz DMI x4MLF68Clock Generator 35,36H8S/2116BG20VKBCLPC Bus / 33MHz12.1'' WXGA LCDLVDS1617RGB CRT CRT SELECTIONWPCN38539LPC Debug Board Conn2938PMH-7G/ASerial ATA I/FUSB 2.0Port1Mocha-1 Block Diagram34Media Slice VCC1R8BS-BAT-PWRCRT UltraSlimBayRJ45USB2514USB HubSMSC MAX6694Thermal SensorSMBusSATA Port 1 I/F20,21,22,2334CRT PortMedia Slice19540Processor15Serial ATA 150MB/sPCI Express CRT I/FG-Sensor42CH10Bluetooth31CH8DDR3 1067/800Channel A UNBUFFERED DDR3 SODIMM Reverse Socket204-PIN DDR3 SODIMM1314Channel B DDR3 1067/800VCC1R05AMT/VCC1R5AVCC5V_OUTVCC3M VCC1R05AMT VCC1R5AVCC1R8BBD3550VT351A5052,53I2C Bus / SM Bus Thermal Sensor LM265UNBUFFERED DDR3 SODIMM Normal SocketWWAN Card27Mini PCI-E 24Intel GLANBOAZMANWLAN Card 27Mini PCI-E USB 2.0 CH3PCI Express25GBE Switch PI3L500AZFEXMedia Slice34RJ45 Conn263131USB2.0 CH5,6USB 2.0 CH7CH0,1USB 1USB 2Bus Switch ICCH9Finger Print1636Int. KB Track point IVKeyboard LightSPI-FLASHSPI GMCH GFX COREVT451&VT45051VINT20VCCGFXCOREVCC0R75AMT5455VCC1R05AUX/1R8AUX56VCC1R05AUX VCC1R8AUXVCC3MPort0Serial ATA I/F PCI Express USB 2.0 CH2PCI Express UWB28Mini PCI-E USB 2.0 CH4PCI Express 33Express Card SoltSATA HDDSATA CONNSUPER I/O WINBOND Camera (LCD Conn)USB 2.0 CH1107226-2-FinalProject Code: 91.47Q01.001PCB(Raw Card): 48.47Q01.001ITP Conn.6AC Coupling18Display Port3029Azalia bus IOSUB Card Conn.32USB 2.0CH5Media Card Reader 3-in-1 SlotUSB 3USB2.0 CH6VCC1R5A VCC0R75AMTBD3550MAX1510Display Port RJ 11Conn Audio CodecIOSUB Card(LCD Conn)HP OUT MIC IN16Trace should be less than 0.5 inch22222 TPAD3022 22 2222E222 2MAX6694TE9A-2-GP2E2 2SC2200P50V2KX-2GPE2 222222222 2VCC3BM_ODT32C 220R1J-GP 2275R1J-GP 2233R1J-GPTPAD30280D6R1F-GP 24K02R1F-GP 275R1J-GP 21KR1J-GP20R1J-GPAD46K24K02R1F-GP21KR1J-GP22K2R1J-GP 2C 2100KR1J-GP21KR1J-GP 230D1R1F-GP 222K2R1J-GP22K2R1J-GP 2100R1J-GP22K2R1J-GP 2222K2R1J-GP 22K2R1J-GP 22C2382SK3541-3-GP2C448222K2R1J-GP 22K4R2F-GP280D6R1F-GP222230D1R1F-GP 2C 2499R1F-GP2475R1F-GP222100KR1J-GP2275R1J-GP 2C2222C2372222222C2662C220DY2222BLM15EG121SN1D-GP 2222222C19120R3-0-U-GP 22222C460220R0306-PAD-GP 2C4372C2132C1802C4232222222222C233222C2862IND-10UH-106-GP222C2852K 2C24122C 4D 7U 6D 2R54122BLM15EG121SN1D-GP SC22U6D3V5MX-4-GP2U 6D 3V 520R0306-PAD-GP 2IND-10UH-106-GP2C43222C301222C422222C25021SC10U6D3V3MX-GP22222227K32R1F-GP2C463SC1KP50V2KX-1GPDY222222C2052SC2D2U6D3V3MX-1-GPSC2D2U10V3KX-1GP22SCD1U10V2KX-4GP2C1762SCD1U10V2KX-4GP2222SC2D2U10V3KX-1GP2SC2D2U6D3V3MX-1-GP2222SCD1U10V2KX-4GP222SCD1U10V2KX-4GP2222C177222C178VCC3AMT_CLKGEN_SECPUCLK_CPU_266M_R-CPUCLK_CPU_266M_R222R1J-GP 222233R1J-GP 2X-14D31818M-43GP20R1J-GP 233R1J-GP 20R1J-GP2SC22P50V2JN-4GPC660222K2R1J-GP 22C53222222222R1J-GP2SC12P50V2JN-3GP2C524SLG8SP568VTR-4-GP212R1J-GPDY22K2R1J-GP 22C305212R1J-GP DY 22C5262210KR1J-GP 2233R1J-GP 2Close to pinK2222MLX-CONN60A-9-GPU2PDTC114EE-1GPU2222DTC115EE-2-GP2DY42SCD047U25V3KX-GP2C52224545452SCD1U10V2KX-4GP 2SCD1U10V2KX-4GP 2SCD1U10V2KX-4GP 2SCD1U10V2KX-4GP 2SCD1U10V2KX-4GP 2SCD1U10V2KX-4GP 2SCD1U10V2KX-4GP 2SCD1U10V2KX-4GP222216TC7WT126FU-2GP2SC10P50V2JN-4GPSC10P50V2JN-4GP133332SC10P50V2JN-4GP3222222LPC_AD3254D9R1F-GP 23C65822222KCH520S-30PT-GP222222MLX-CON3-7-GP-UK22222C6732C64122P 22247R1J-GP 215R1J-GP 222P 22P 2P 222SCD1U10V2KX-4GP2P22222P 2522P 2P 22210KR1J-GP93102P92102P22100KR1J-GP 2P20R1J-GP 210KR1J-GP 28K2R1J-GP210KR1J-GP 2P210KR1J-GP2222P 2222C64222222SCD1U10V2KX-4GP 2D 1U 12222SC1U10V2KX-1GP2222C640222SCD1U10V2KX-4GP 2222C495TP702SCD1U10V2KX-4GP 2Keep to place on the same side of GBE KDS:25MHZ / 9PFUSE INTERNAL REGULATOR FOR 1.05V WG82567LM-Q036-GP2C672SC15P50V2JN-2-GP2222222 22 22222R7442 2DY22 2R656222222SKT-JACK-257-GPSC1KP50V2KX-1GP SKT-JACK-257-GP SCD1U10V2KX-4GPSCD1U10V2KX-4GPSKT-JACK-257-GPSC1KP50V2KX-1GP42SC4D7U10V5KX-1GP2SC1U10V2KX-1GP2C321222222C4312222SC1U10V2KX-1GP222222C602VCC3M_SPI233R1J-GP222233R1J-GP 233R1J-GP 22233R1J-GP233R1J-GP 252602222220R0306-PAD-GPSKT-SATA7P+15P-GP-USKT-USB-257-GP2 25 42222425TPS2066DGN-1-GPPDTC115EE-1-GP SDM20U30-7-GP22SDM20U30-7-GP HRS-CON40-5-GP2C6632222222U 1223CARDBUS-SKT99-GP-U12R800DY22222SC6800P25V2KX-1GP21K P 5100KR2J-1-GPEXPRESSCARD-26P-GP-U2227U 6D 222SCD1U50V3KX-GP 2SCD01U16V2KX-3GPK SCD01U16V2KX-3GP20R2J-2-GP SCD1U50V3KX-GPFDS6675BZ-GPSCD1U50V3KX-GP22222DF2116VBG20MSJV-GP K2210KR1J-GP 212330R1J-GPKD822DAP222-1-GP-U 210KR1J-GP21KR1J-GP2212SCD1U25V3KX-GP2C150SDM20U30-7-GP3321KR2J-1-GP DF2116VBG20MSJV-GP 22560R1J-GP3220R1J-GP20R1J-GPK SDM20U30-7-GP225SCD01U16V2KX-3GPK 2282621292722202JAE-CONN40A-1-U1GP233R1J-GP 220R1J-GP5RN1622SCD1U10V2KX-4GP233R1J-GP 2220R1J-GP 2227233R1J-GP 22SC1KP50V2KX-1GP20R1J-GP2232622RN14R 1J -222SCD1U10V2KX-4GPWPCN385DG-GPSRN10KJ-10-GP-UE2220R2J-2-GP E2NC7SZ384P5X-1-GPPDTC115EE-1-GP2NC7SZ384P5X-1-GP2C108SCD1U10V2KX-4GPNC7SZ384P5X-1-GP22C109SCD1U10V2KX-4GP2C145SCD1U10V2KX-4GP 222C110SCD1U10V2KX-4GP 22C144SCD1U10V2KX-4GP222222NC7SZ384P5X-1-GP 2222SCD1U16V2KX-3GPFDC658AP-GP222SCD1U10V2KX-4GPSCD1U10V2KX-4GPSCD1U10V2KX-4GP16SCD1U10V2KX-4GPE2247U 2522FDS6675BZ-GP122PDTC115EE-1-GPE FUSE-D5A32V-10-GPPDTC115EE-1-GP 2222E 2FUSE-D5A32V-10-GPPDTC115EE-1-GP2DAP222-1-GP-U222SCD01U50V2KX-1GP2SC2200P50V2KX-2GP22252252C350222C3972C 3402222C4622C2022C2822220R2J-2-GP ADP3808AJCPZS3-GP22222C342SCD01U25V2KX-3GPPDTC115EE-1-GP2S 22SCD1U25V3KX-GPSI3483DV-T1-GPDAN222-1-GP2DAN222-1-GP2470KR1J-GP22C352G P 212AMP-CON7-10-GP2C3532FUSE-10A125V-4GPE2DY22222SCD1U10V2KX-4GP22DY 222SC1KP50V2KX-1GPK 21002232222222232C782222222R101SC10U25V6KX-2GP2C872222522C13252DY22220R2J-2-GP 2D 1U 22C6322C8422252222R81222C154SC10U25V6KX-2GP5U15D2C4582VCORE_DB0Close to U51,pin32L8 PA2143NL_PA215-->CPL-2-50-R28K66R2D-GP 24K7R2D-GP20R2J-2-GP 2210KR2J-3-GP 239K2R2D-GP210KR2J-3-GP SRN0J-11-GP-U22VT1311SFCX-GP-U2100KR2F-L1-GP 222IND-350NH-1-GP210KR2J-3-GP 2DY2DY210KR2J-3-GP24K7R2D-GP210KR2J-3-GP 210KR2J-3-GP SRN0J-10-GP-U 210K7R2D-1-GP 268R2-GP2211KR2D-1-GP2222211K3R2D-GP 211KR2D-1-GP 20R2J-2-GP22DY2DY。

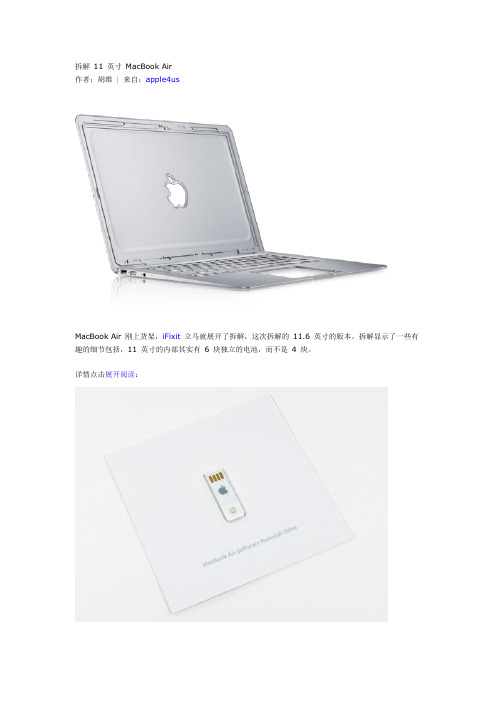

拆解 11 英寸 MacBook Air

拆解11 英寸MacBook Air作者:胡维|来自:apple4usMacBook Air 刚上货架,iFixit立马就展开了拆解,这次拆解的11.6 英寸的版本。

拆解显示了一些有趣的细节包括,11 英寸的内部其实有 6 块独立的电池,而不是 4 块。

详情点击展开阅读:因为没有光驱,苹果为MacBook Air 配备了一个USB 系统重装U 盘。

新的MacBook Air 的电源适配器仍然是45W 3.1A 14.5V ,但体积比上一代更小。

对比可以看出,新的MacBook Air 放弃了前侧面的「睡眠呼吸指示灯」和「红外接受器」。

新的MacBook Air 底部采用了五角的梅花螺丝,而之前都是普通的十字螺丝。

这一变化是因为,苹果不希望用户自己拆开新款MacBook Air ,因为其中没有用户可以自行替换的原件,比如SSD 硬盘或独立内存条等。

13.3 英寸MacBook Air 内部有4 块分隔的电池,但在11.6 英寸的版本中,电池已经被分隔成6 块。

11.6 英寸MacBook Air 的64GB 闪存由4 块16GB 的东芝芯片组成,配合一个控制器和一个微芯片,装在一个可拆卸的集成板上。

新一代MacBook Air 使用与旧款完全相同的Broadcom Wi-Fi 和Bluetooth 芯片。

这个机器的冷却和痛风完全依靠一个鼠笼式风扇,比MacBook 的风扇要薄。

MagSafe 电源端口、USB 端口和声卡及音频接口都在同一块线路板上。

处理器和显卡产生的热量通过白色的散热膏传导至散热塑料片,再传递到风扇处。

逻辑板上的酷睿 2 双核 1.4 GHz 处理器(红色)、NVIDIA GeForce 320M 显卡(橙色)和2GB Elpida 内存。

笔记本的电脑揭秘 苹果11寸MacBook Air拆解

新一代MacBook Air引来口水声一片,苹果也自豪的把它称作代表未来MacBook发展方向的作品。

如今的苹果已经认识到,他们的作品从内部看依然如同艺术品,在官方宣传中就呈上了内部结构照片。

不过,有关这款极限轻薄笔记本的更多奥妙,还要留待iFixit这样的拆解专家来探索。

新MacBook Air昨天已经在美国市场上市。

此次拆解的是全新的11.6寸屏幕版本,型号为A1370,基本配置包括:Intel Core 2 Duo SU9400 1.4GHz处理器(可选1.6GHz)2GB DDR3 SDRAM内存(可选4GB)64GB或128GB固态硬盘NVIDIA GeForce 320M集成显卡芯片组售价方面,64GB版999美元/7998元人民币,128GB版1199美元/9498元人民币。

苹果首次放弃安装光盘,而是随新MacBook Air附赠了一块操作系统安装U盘。

插入后在系统启动时按住键盘C键即可从U盘启动安装。

该U盘容量为8GB,内置Mac OS X 10.6 Snow Leopard操作系统和iLife '11的安装程序,默认设置为只读。

新MacBook Air的MagSafe电源适配器规格为45W 14.5V 3.1A,和上代机型相同,不过适配器体积有明显缩小。

和之前的独立按键不同,新设计中的电源键已经和键盘整合在了一起。

与上一代13寸MacBook Air对比。

前端厚度仅3mm,把上代机型本已相当惊人的锐利感又提高了一个层次。

整体尺寸299.5x192x3-17mm,重1.06kg。

苹果在新MacBook Air的底盖上使用了特殊的梅花形五角螺丝,苹果似乎并不希望用户轻松打开它。

废了一番力气寻找特殊螺丝刀后,终于打开底盖。

和苹果官方展示的图片(13寸机型)不同,11寸MacBook Air内部共包含了六块锂聚合物电池,总容量35Whr。

拆解电池需要拧下5颗螺丝。

取出电池模块。

imac4k拆机图解 显示屏与玻璃合为一体

imac4k 拆机图解显示屏与玻璃合为一体

iFixit 日前拆解了苹果的新款21.5 寸iMac,但只是1920×1080分辨率的普通版本,而今天,首次面世的4K Retina 版本终于也被拆了。

它们俩的基础和可选配置都是一模一样的,看起来唯一不同就是屏幕分辨率升级到了

4096×2304。

但是拆解表明,内部细节是有很多不同的,主板芯片也差很多。

产品型号仍是A1418,但电磁屏蔽编号是新的2833。

1080p、4K 到底有多大区别?不亲自体会是不会明白的,从放大镜下近距离看屏幕像素更是天差地别。

4K

1080p

4K 和1080p:940 多万个像素和207 万个像素,超过4.5 倍差距,前者确实不愧是视网膜级别的。

专业笔记本电脑电路图纸维修图概要

PCI DEVICE RESOURCE ASSIGNMENT LAN CardBus 1394MiniPCIIDSELPCI_REQ#PCI_GNT#INT_IRQ#PCI_AD21PCI_AD25PCI_AD19PCI_AD22 REQ#4REQ#1REQ#0REQ#2GNT#4GNT#1GNT#0GNT#2IRQD#IRQB#IRQF#IRQC#/IRQE#BUSDEVICE11115936Table of Content / HISTORYWistron Corporation21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,Taipei Hsien 221, Taiwan, R.O.C. LCDVDDRTC_AUX_S5ICH_VBIASAD+DCBATOUT MAX1631_VL5V_USB1_S05V_CRT_S0FAN1_VCC5V_USB0_S01394_AVDDVCC_ASKT_S0VPP_ASKT_S05VA_AUD_S03D3V_S35V_S05V_S53D3V_S05V_S3VCC_RTC_S51D5V_S51D5V_S01D8V_S01D2V_S0VCC_IO_S01D25V_S02D5V_S3VCC_CO RELCDVDD 11ICH_VBIAS15RTC_AUX_S515AD+17,38,39,41DCBATOUT 11,17,34,35,36,37,38,40,42MAX1631_VL375V_USB1_S0195V_CRT_S012FAN1_VCC171394_AVDD22VCC_ASKT_S023VPP_ASKT_S0235V_USB0_S0195VA_AUD_S026,27,433D3V_S311,19,26,30,35,36,405V_S511,16,27,28,37,405V_ S330,35,36,40,413D3V_S514,15,16,20,26,37,39,40,425V_S011,12,15,16,17,18,19,21,23,24,25,26,28,29,30,31,32,33,34,35,36,39,403D3V _S03,4,7,8,9,11,12,13,14,15,16,17,18,19,20,22,23,24,25,26,29,31,32,34,36,40,43VCC_R TC_S5151D5V_S516,371D5V_S07,8,13,14,16,361D8V_S04,361D2V_S06,8,17,36VCC_IO_S04,5,6,8,16,361D25V_S010,352D5V_S36,8,9,10,17,35VCC_CORE5,15,17,34Adaptor in to generate DCBATOUT *Layout* 150mil DCIN1 1 AD_JK L28 1 FBMJ3216HS480NT U8 2 AD+_1 AD+_2 1 2 C824 SCD1U50V3KX C827SCD1U50V3KX C823 SCD1U50V3KX C825 SCD1U50V3KX 5V_S3 1 2 1 3 D GBT_SCL_5 1 1 1 1 SYN-CON7-1 C298 SC1000P50V3KX BT_SDA_5 R291 0R2-0 2C300 SCD1U50V5KX C301 SC1000P50V3KX C299 SC1000P50V3KX 2 Q24 2N700284.27002.031 2 S 1 G C826 SCD1U50V3KX R290 10KR3 1 2 3 4 S S S G P-MOS FETD D D D 8 7 6 5 C47 SCD1U C62 SCD1U C61 SCD1U C60 SCD1U D2 3 HZM24NBZ83.24R03.031 2 AD+ 2 3 4 DC-JACK51-U1 C23 SCD1U C22 SCD1U C24SCD1U50V5KX R327 1 SI4435DY C399 SCD1U50V5KX 2 DUMMY-R5ZZ.DUMMY.XR5 R37 1 2 DUMMY-R5 ZZ.DUMMY.XR5 K 22 R367 100KR3 CHANGE 4435A EMI 1 1 R366 56KR3 3 5V_UP_S5 1 2 2 AD_OFF#_JK 2 K 22 3 30 AD_OFF 1 R365 100KR3 2 1 G 2 D Q30 2N7002 S 84.27002.031 Q31 DTA124EUA-U1 BATTERY CONNECTOR 1 2 1 2 G28 1 3 3 3 D18 BAV99LT1 83.00099.01A D20 BAV99LT1 83.00099.01A D19 BAV99LT1 83.00099.01A 1 1 BT+ 30,38 BAT_IN# 38 BT_SCL_5 38 BT_SDA_5 38 BT_TH 38 BT+SENSE R704 1 R288 1 R289 1 2 100R3 2 33R3 2 33R3 BTSMCLK BTSMDATA TH BT+SENSE BT+ 2 3 4 5 6 7 BAT1 2 GAP-CLOSE ZZ.CON2C.XX1 G29 2 GAP-CLOSE ZZ.CON2C.XX1 NEAR BATTERY CONNECTOR Q23 2N7002 84.27002.031 KBC_SCL_3 30 2 2 2 3 D KBC_SDA_3 30 BT+SENSE S Wistron Corporation 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title AD/BATT CONN Size A3 Document Number Rev B2I Sheet 41 of 44 Date: Tuesday, April 08, 2003A R247 47KR3 1 2 C269 SCD1U16V 5V_UP_S5 14 U32A TSAHCT1473.07414.0JB 1 3 S1N4148 7 U29 5 VCC A B 37 M1631_EN_BL3# 4 Y GND 1 2 3 BC23 SCD1U 2 BL3# 1 M1631_EN 1 R601 200KR5F 2 1 2 3 R600 DUMMY-R3 OUT VDD VSS NC NC 5 4 5V_UP_S5 7 2 1 R249 100KR3 TSLCX74-U 2 PM_SLP_S4# 6 Q 5V_UP_S5 14 4 U33A TSAHCT32 1 PWRBTN_74 10KR3 U34A 5 Q 1 5V_UP_S5 R251 2 3D3V_S5 1 R246 10KR3 1 R602 330KR3 2 2 DCBATOUT 5V_UP_S55V_UP_S5 1 R639 10KR3 2 U28 D12 15,39 PWRBTN#_ICH 1 2 2 VCC D CLK 14 2 37 CL 1 1 PR GND R253 S-80740SN-D4-U 14 2 5V_UP_S5 3 NC7SZ08-U 5V_UP_S5 14 6 D Q11 2N7002 S 84.27002.031 4 5 U33B TSAHCT32 7 1 R248 100KR3 2AC_VSENSE 39 1 G 2 22KR3 C271 SCD1U16V 9 39 M1631_EN M1631_EN 8 10 75V_UP_S5 14 R282 12 U33C TSAHCT32 11 13 7 2 0R3-0-U 1 CD5V_OFF#/ON63.00000.001 RTC_WK 15 1 5V_UP_S5 14 R283 100KR3 2 U32B TSAHCT1473.07414.0JB 3 PWRBTN#_1 5V_UP_S5 1 R240 47KR3 2 R242 2 1 PWRBTN# 30,39 1KR3 C267 SCD1U16V 4 2 7 U33D TSAHCT32 R244 PWRBTN#_ICH 1 1 DUMMY-R3 ZZ.DUMMY.XR3 POWER BUTTON 1 1 R265 10KR3 2 Q16 OUT 3 GND 1 47KR1 R2 5V_UP_S5 14 Q 9 DTC144EUA U32D TSAHCT14 CL Q 8 CD5V_OFF/ON# 9 8 CD5V_OFF#/ON CD5V_OFF#/ON 28,39,40 2 IN R264 DUMMY-R2 1 2 1 R2660R3-0-U 2 PM_SLP_S4# 15,16,23,39,40 PM_SLP_S3# 3,15,16,26,30,34,36,39,40CLR_CDPLAY PR 10 U34B 13 R281 100R3 1 2 5V_UP_S5 1 2 C295SCD01U16V3KX 7 TSLCX74-U CD PLAYER POWER ON LOGIC (SYSTEM TURN ON 5V_UP_S5 5V_UP_S5 1 C277 R241 100KR3 R243 10KR3 2 5V_UP_S5 14SCD1U16V U32C TSAHCT14 73.07414.0JB CD_SW2 6 14 12 11 7 C268 SCD1U16V 7 VCC D CLK GND 5V_UP_S5 25,39 CDPLAY_SW 1 2 CD_SW1 5 (SYSTEM TURN OFF 5V_UP_S5 14 U36 1 U32E 10 TSAHCT14 2 3 7 100KR3 C294 SCD1U16V A B GND (Make Low Pulse 5V_UP_S5 3 4 1 G 2 CLR_CDPLAY 1 R280 VCC 5 D Q21 S2N7002 84.27002.031 Title 2 11 Y Wistron Corporation 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. NC7SZ08-U POWER ON CIRCUIT Size A3 Document Number Rev B2I Sheet 42 of 44 Date: Tuesday, April 08, 2003 ANO USE LOGIC 1 3D3V_S0 5VA_AUD_S0 14 U56D 11 12 11 TSLCX125 13 7 TSAHCT86 1 14 13 U44D 12 K14 1 EMI-PLT-4 1 K15 1 EMI-PLT-4 1 K16 1 EMI-PLT-4 1 K17 1 EMI-PLT-4 K8 GNDPAD 34.49T19.001 1 K9 GNDPAD 34.49T19.001 1 K5 K7 K11 GNDPAD-S2 GNDPAD-S2 GNDPAD-S2 34.41T19.001 34.41T19.001 34.41T19.001 1 1 1 1 1 K2 1 EMI-PLT-4 1 K6 1 EMI-PLT-4 1 K10 1 EMI-PLT-4 1 K12 1 EMI-PLT-4 7 AUD_AGND AUD_AGND H4 H5 H10 H11 H6 H12 H2 H3 HOLE HOLE HOLE HOLE HOLE HOLE HOLE HOLE ZZ.0HOLE.XXX ZZ.0HOLE.XXXZZ.0HOLE.XXX ZZ.0HOLE.XXX ZZ.0HOLE.XXX ZZ.0HOLE.XXXZZ.0HOLE.XXX ZZ.0HOLE.XXX H9 HOLE H8 HOLE H7 H18 H19 H16 HOLE HOLE HOLE HOLE ZZ.0HOLE.XXX ZZ.0HOLE.XXX ZZ.0HOLE.XXXZZ.0HOLE.XXX H14 H17 H1 H13 HOLE HOLE HOLE HOLE ZZ.0HOLE.XXX ZZ.0HOLE.XXX ZZ.0HOLE.XXX H15 HOLE 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 30 30 30 30 30 30 30 30 30 30 30 30 KROW8 KROW7 KROW6 KROW5 KROW4 KROW3 KROW2 KROW1 KCOL16 KCOL15 KCOL14 KCOL13 EMI 1 1 1 1 1 1 1 1 1 1 1 C750 SC150P50V2JN C751 C753 C754 SC150P50V2JN SC150P50V2JN SC150P50V2JN 2 2 C312 C313 C755 SC150P50V2JN SC150P50V2JN SC150P50V2JN 2 2 C756 C757C758 SC150P50V2JN SC150P50V2JN SC150P50V2JN 2 2 C759 C760 SC150P50V2JN SC150P50V2JN 2 1 2 2 2 2 30 30 30 30 30 30 30 30 30 30 30 30 KCOL12 KCOL11 KCOL10 KCOL9 KCOL8 KCOL7 KCOL6 KCOL5 KCOL4 KCOL3 KCOL2 KCOL1 1 1 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2 2 2 2 2 2 2 25 25 25 25 25 25 25 STOP/EJECT FFLED_SEG0 LED_SEG2 LED_SEG4 LED_SEG6 LED_SCAN1 1 1 1 1 1 1 1 25 25 25 25 25 25 25 PLAY/PAUSE RW LED_SEG1 LED_SEG3 LED_SEG5 LED_SEG7LED_SCAN2 1 1 1 1 C383 C384 C8 C7 C6 C5 C375 SC100P50V2JN SC100P50V2JN SC100P50V2JN SC100P50V2JN SC100P50V2JN SC100P50V2JN SC100P50V2JN 2 2 2 2 2 2 1 2 2 2 2 2 2 2 C382 C381 C380 C379 C35 C377 C376 SC100P50V2JNSC100P50V2JN SC100P50V2JN SC100P50V2JN SC100P50V2JN SC100P50V2JNSC100P50V2JN 2 2 C737 SC150P50V2JN C739 C740 C741 SC150P50V2JNSC150P50V2JN SC150P50V2JN C742 C743 C744 SC150P50V2JN SC150P50V2JN SC150P50V2JN C745 C746 C747 SC150P50V2JN SC150P50V2JN SC150P50V2JN 2 C748 C749 SC150P50V2JN SC150P50V2JN 1 Wistron Corporation 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title MISC Size A3 Document Number Rev B2I Sheet 43 of 44 Date: Tuesday, April 08, 2003A B C D E CPU TEST POINT 4 GMCH TEST POINT 4 3 3 2 2 1 Wistron Corporation 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C.Title 1 TEST POINT Size Document Number Custom Rev B2I Sheet E Date: Tuesday, April 08, 2003 A B C D 44 of 44。

苹果MacBook Pro Retina版本拆机组图

苹果MacBook Pro Retina版本拆机组图新MacBook Pro Retina版本采用15.4英寸IPS屏幕,具备广视角、广色域等特性,分辨率高达2880×1800,即原有15.4英寸MBP的四倍!硬件方面,该机采用i7四核处理器,含HD 4000核芯显卡,配备8GB内存以及NVIDIA GeForce GT 650M独立显卡。

左侧接口方面,图中从左至右依次为MagSafe 2电源磁性接头、两个Thunderbolt雷电接口、1个USB3.0以及3.5mm 耳机插孔。

机身右侧,图中从左至右依次为1个USB3.0、1个HDMI 高清输出、SDXC读卡器。

此外,笔记本使用了全新散热方式,散热进气窗在侧面下方边缘。

MacBook Pro Retina版在屏幕下方并没有预留“MacBook Pro”的字样。

将笔记本翻过来,机身底部印有该机型号编码:A1398。

让我们近距离看看这个Retina视网膜屏幕,220ppi到底有多精细?菜单栏的苹果标识。

像素大幅提升的Finder图标,如此高的像素密度简直是不可思议!新的苹果MacBook Pro Retina版使用了苹果独有的Pentalobe螺丝。

一共十颗。

笔记本底盖被打开!苹果MacBook Pro Retina版内部总览,布局非常干净整洁!美国设计,中国组装的锂聚合物电池,不含汞,电量高达95Wh,远高于当前任何15英寸笔记本!(当前主流15英寸笔记本电量在54Wh左右)电池写有明确标语警告:如对电池进行更改,请到授权苹果服务站。

如果处理不当,可能引起灼热、燃烧。

请不要拆卸、拆解、穿刺、跌落、挤压、暴露于火中或高于100摄氏度的环境下。

开始拆解前,先断开电池。

断开电池的电源接口排线。

与之前机器不同,新的MacBook Pro Retina笔记本的电池不再由螺丝固定,但是,苹果却使用了另一样让我们头疼的固定介质!它就是胶水!让我们把电池放一放,先拆其它组件!我们从SSD开始拆起。

苹果iPad5 原厂原理图 元件分布图维修图纸.

TABLE_TABLEOFCONTENTS_HEADTABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_HEAD TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_HEAD TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEMTABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEMTABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEMTABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM 8B7DACC3456DB87654CSA SYNC MASTERCONTENTSDATEPDF 1N/AN/ATable of Contents151GRAPE: 1V8 POWER SWITCH65N/AN/ASYNC MASTERCSA CONTENTSPDF DATE2632RADIO_MLB_72_B706/03/2013CELL: BASEBAND PMU (1 0F 2DATE SYNC MASTERCONTENTSCSA PDF 52GRAPE: CUMULUS66N/AN/A53DISPLAY: EDP CONN70N/AN/A54POWER: BATTERY CONNECTOR75N/AN/A55 PMU: ANYA PAGE 181N/AN/A56PMU: ANYA PAGE 282N/AN/A57PMU: ANYA PAGE 383N/AN/A58PMU: ANYA PAGE 484N/AN/A59SOC: DEBUG90N/AN/A60TEST: TP/HOLES/FIDUCUALS93N/AN/A61 TEST: EE TP/PP94N/AN/A62POWER: ALIASES121N/AN/A63CONSTRAINTS: MLB RULES150N/AN/A64 CONSTRAINTS: LOW SPEED BUS151N/AN/A65 CONSTRAINTS: DISPLAY/AUDIO152N/AN/A66 CONSTRAINTS: DDR/FMI153N/AN/A67 CONSTRAINTS: POWER / GND154N/AN/A68 CONSTRAINTS: RF157N/AN/A69CONSTRAINTS: WIFI/BT158WIFI_DEV05/21/20132733RADIO_MLB_72_B706/03/2013CELL: BASEBAND PMU (2 OF 228 34RADIO_MLB_72_B706/03/2013CELL: BASEBAND (1 OF 22935RADIO_MLB_72_B706/03/2013CELL: BASEBAND(2 OF 23036RADIO_MLB_72_B706/03/2013CELL: TRANSCEIVER (1 0F 23137RADIO_MLB_72_B706/03/2013CELL: TRANSCEIVER (2 OF 23238RADIO_MLB_72_B706/03/2013CELL: TRANSCEIVER MATCHING33 39RADIO_MLB_72_B706/03/2013CELL: SAW BANK3440RADIO_MLB_72_B706/03/2013CELL: BAND 1/4 PAT3541RADIO_MLB_72_B706/03/2013CELL: BAND 2/3 PAD3642RADIO_MLB_72_B706/03/2013CELL: BAND 20 PAD3743RADIO_MLB_72_B706/03/2013CELL: BAND 5/8 PAD3844RADIO_MLB_72_B706/03/2013CELL: BAND 13/17 PAD3945RADIO_MLB_72_B706/03/2013CELL: PA DC/DC CONVERTER4046RADIO_MLB_72_B706/03/2013CELL: 2G FEM4147RADIO_MLB_72_B706/03/2013CELL: RX DIVERSITY42 48RADIO_MLB_72_B706/03/2013CELL: GPS4349RADIO_MLB_72_B706/03/2013CELL: ANTENNA FEEDS44 51N/AN/ACELL: SIM FLEX CONN4556N/AN/ASENSOR: PROX AD71494658WIFI_DEV05/21/2013WIFI/BT: MODULE4760N/AN/AIO: TRISTAR4861N/AN/AIO: FILTERING4962N/AN/AIO: FLEX HOTBAR PADS5063N/AN/AIO: HOME BUTTON FILTERS2N/AN/ABLOCK DIAGRAM: SYSTEM23N/AN/ABOM TABLES44N/AN/ASOC: MAIN65N/AN/ASOC: I/OS76N/AN/ASOC: NAND87N/AN/ASOC: DP,MIPI98N/AN/ASOC: DDR109N/AN/ASOC: IO POWER1110N/AN/ASOC: SRAM POWER1211N/AN/ASOC: CPU POWER1312N/AN/ADDR: CHANNEL 0 AND 11413N/AN/ASOC: MISC & ALIASES1514N/AN/ANAND: NAND1615N/AN/AAUDIO: L81 CODEC1716N/AN/AAUDIO: HP/DMIC FLEX CONNS1817 N/AN/AAUDIO: SPEAKER AMPS RIGHT1918 N/AN/AAUDIO: SPEAKER AMPS LEFT2019 N/AN/ASENSOR: OSCAR, GYRO, ACCEL2420 N/AN/ASENSOR: HALL EFFECT2521N/AN/AIO: BUTTON FLEX CONN2622N/AN/ACAMERA: FF AND ALS CONN2723N/AN/ACAMERA: REAR CONN2824N/AN/ASENSOR: COMPASS292506/03/2013RADIO_MLB_72_B7CELL: SYSTEM & DEBUG CONNECTORS30Edited by Foxit Reader ActiveX For Evaluation Only.Copyright(C 2006-2009 Foxit Corporation。

笔记本主板部分原理图

HDMI

PAGE 14

NB_CORE

PAGE 28

PCIE x4 CPU_CORE USB 2.0 BLUE TOOTH

DAUGHTER BOARD USB PORT x 2

PAGE 22

South Bridge AMD

PAGE 27

PAGE 23

1.1VS / 2.5VS 1.2V-USB

PAGE 31

2

1.2VS

1

2

2

C204 4.7UF

1

L510 2 1 120/0603-600mA C205 0.1uF

1

C567 10uF/0603

4 16 26 35 40 48 55 56 63 11 17 25 34 47 1 7 10 18 24 33 43 46 52 60 61 62 2 3

VDDDOT VDDSRC VDDATIG VDDSB VDD_SATA VDDCPU VDDHTT VDDREF VDD48 VDDSRC_IO VDDSRC_IO VDDATIG_IO VDDSB_IO VDDCPU_IO GND48 GNDDOT GNDSRC GNDSRC GNDATIG GNDSB GNDSATA GNDCPU GNDHTT GNDREF X1 X2

C

13,23,24,26,27,28,29,30,31,32,33 15 22,29 29 15,16,17,22,25,26,29,31,33 15,16,17,18,25,31,33 18,31 22,23,29,30,32,33, 13,33 04,05,06,07,08,30,33 04,05,07,08,30 06,13,14,17,18,21,22,23,25,27,28,31,32,33 23,33

笔记本图纸

笔记本图纸1. 简介笔记本图纸是指用于设计和制造笔记本电脑的技术图纸。

它包含了笔记本电脑的外形尺寸、组件位置、布局和电路设计等重要信息。

笔记本图纸对于制造商和设计师来说都是非常重要的参考资源,它们能够确保笔记本的外观和功能符合设计要求,同时也是实现一致生产的基础。

2. 笔记本图纸的组成部分笔记本图纸通常由多个不同的部分组成,每个部分都具有特定的功能和目的。

以下是常见的笔记本图纸的组成部分:2.1 外形图外形图是笔记本图纸的基本部分,它展示了笔记本电脑的尺寸、形状和外观设计。

外形图通常包括正面、侧面和背面的视图,以及笔记本的各个边缘和连接口的详细设计。

外形图对于设计师来说是非常重要的参考,它能够确保笔记本的外观符合设计要求,并提供给制造商用于生产的基础。

2.2 零部件图零部件图是指笔记本电脑的各个组件的详细设计图纸。

它们包括处理器、内存、硬盘、显示屏和键盘等主要部件的尺寸、位置和连接方式。

零部件图对于制造商来说非常重要,它们能够确保各个组件的安装和连接方式符合设计要求,并提供给制造商用于组装和测试的依据。

2.3 电路图电路图是指笔记本电脑主板的电路设计图纸。

它展示了主板上各个电子元件的位置、连接关系和工作原理。

电路图对于电子工程师来说是非常重要的参考资源,它能够确保主板的电路设计符合规范,同时也是制造商进行电路布线和测试的依据。

3. 制作笔记本图纸的工具制作笔记本图纸需要使用一些专业的工具软件,以下是一些常用的笔记本图纸制作工具:3.1 AutoCADAutoCAD是一款广泛使用的工程设计软件,它提供了丰富的绘图和设计功能,可以用于制作各种类型的图纸,包括笔记本图纸。

AutoCAD能够提供高精度的绘图工具和多种输出格式的支持,可以满足制造商和设计师的需求。

3.2 SolidWorksSolidWorks是一款专业的三维建模软件,它提供了强大的图形处理和建模功能,可以用于制作复杂的三维图纸。

SolidWorks具有直观的用户界面和丰富的建模工具,可以帮助设计师快速制作高质量的笔记本图纸。

产品设计分析

整体采用特殊钢化玻璃,十分耐刮, 手感十足,整机只有9.3毫米。

采用名为Retina的显示技 术,并且采用了960×640像 素分辨率的显示屏幕

苹果iPhone4 背部闪耀着 黑色的光芒 与中间苹果 的标志相得 益彰。在材 料的选择上 苹果可以说 是达到了精 益求精的地 步

耳机的设计更是能代表 苹果强大工业设计。细 节人性化的设计深入人 心

黑色的底层无论是在反射角度、放射亮度 方面都经过了精确的把控,任何光线的照 射都只会造成一条线状的反射,这样 iPhone4的背部看起来科技感十足。

1.手工吹制玻璃,晶莹剔 透,灵感来自矿泉水瓶 2.整体结构整洁,简单透 明,体现出设计者对生活 的理解 3.瓶身独特螺纹设计,既 防滑又方便把持 4.颜色简单,不同于市售 的其他产品,具有创意, 也显品味

3.符合人体右手 人机工程学的设 计,给使用者提 供最大舒适度

1.块状构成,通体 采用纯黑颜色,延 续经典

4.发光的雷蛇哑 光logo,延续经 典,体现雷蛇的 企业文化

2.特殊工艺材质, 接触皮肤手感十足, 即使有手汗也不影 响手感

5.流线型的造型,如同蛇一般, 风格时尚,酷炫

森 海 塞 尔

Adidas与森海合作的一款耳机,加入三 叶草元素,赋予耳机动感与时尚感 采用线构成,耳机线材质柔软,采用蓝 白相间的设计,具有创意,打破常规。

入耳式设计, 隔绝噪音, 胶套可供选 择,人性化 细节处理, 蓝色的造型 给人宁静, 舒适的感觉

产品分析

华 文

051120114

DELL

外星人系列电脑

配置引领行业最高端 霸气的外形设计如外星人一般引领非主流

1.采用面构成,金属材质 底面厚重,霸气十足 2.红黑色搭配,视觉冲击 很震撼 3.机身中没有圆角,通过 块材堆积成的钝角,展现 出高科技的肌肉美学 4.整体平行四边形的设计 模式相当动感

苹果笔记本电路图纸信号详解

DCIN:适配器主供电输入PPVBATT_G3H_CONN:电池主供电输入PP3V42_G3H:待机电压,3.42V,为主板待机电路提供供电;SMC_RESET_L:EC复位信号,待机电压产生后,由专门复位芯片进行电压检测后,发出高电平给EC;SMC_TPAD_RST_L:键盘组合键发出的EC复位信号;CHGR_BAGET:电池放电与充电开关管控制信号;PPVBAT_G3H_CHGR_R:电池充电或放电电压;!PPBUS_G3H:公共端电压,提供给主板各个供电单元主供电输入;P5VS3_EN:5V电压开启信号,在S3状态开启;P3V3S5_EN:3.3V电压开启信号,在S5状态开启;PP5V_S3:S3状态产生的5V电压;PP5V_S0:S0状态开启的5V电压3V3_S5:S5状态产生的3.3V电压;CPUIMVP_VR_ON:CPU核心供电开启信号,高电平3.3V开启CPU核心供电;.pCH或南桥部分:、PM_SLP_S5_L:S5状态电压开启信号。

PCH或南桥发出,在使用电池待机时,PM_SLP_S5_L 低电平,使用电源适配器时,此信号变为高电平。

用来减少电池待机时的电量损耗;PM_SLP_S4_L:内存供电(核心供电,不开启VTT)开启信号;PM_SLP_S3_L:S3状态电压开启信号;显示电路部分:BKLT_EN:LCD屏背光供电开启信号;OUT PPBUS_S0_LCDBKLT_PWRLCD屏背光高压板主供电,由PPBUS_G3H转换而来;EC部分:SMC_FAN_0_TACH:EC风扇转速检测信号;SMC_FAN_1_TACH:EC风扇转速检测信号;温控CPU内部热敏三极管正向连接;CPU_THERMD_N:CPU内部热敏三极管反向连接;SMBUS_SMC_B_S0_SDA:I2C信号线,与EC通信;SMBUS_SMC_B_S0_SCL:I2C信号线,与EC通信;GPU_TDIODE_P:显卡内部热敏三极管正向连接;.GPU_TDIODE_N:显卡内部热敏二极管反向连接;风扇部分:FAN_LT_PWM:左边风扇转速驱动控制信号;FAN_LT_TACH:左侧风扇转速反馈信号;FAN_RT_PWM:右侧风扇转速控制信号;FAN_RT_TACH:右侧风扇转速反馈信号;。

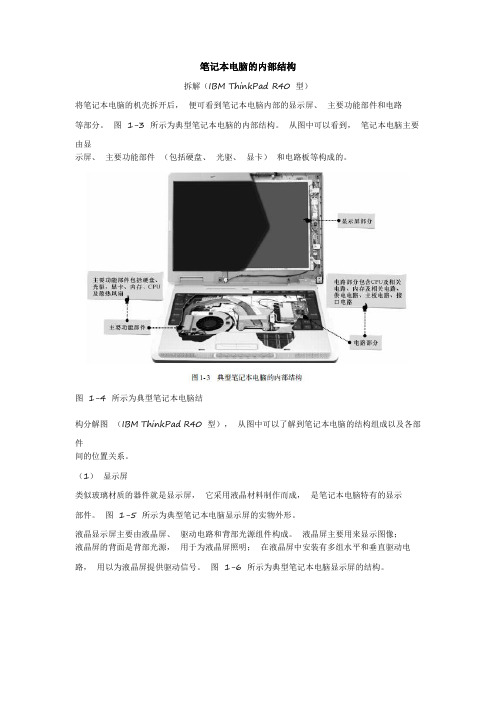

笔记本电脑维修的内部结构拆解看图认识零件

笔记本电脑的内部结构

拆解(IBM ThinkPad R40 型)

将笔记本电脑的机壳拆开后,便可看到笔记本电脑内部的显示屏、主要功能部件和电路

等部分。

图1-3 所示为典型笔记本电脑的内部结构。

从图中可以看到,笔记本电脑主要

由显

示屏、主要功能部件(包括硬盘、光驱、显卡)和电路板等构成的。

图1-4 所示为典型笔记本电脑结

构分解图(IBM ThinkPad R40 型),从图中可以了解到笔记本电脑的结构组成以及各部

件

间的位置关系。

(1)显示屏

类似玻璃材质的器件就是显示屏,它采用液晶材料制作而成,是笔记本电脑特有的显示

部件。

图1-5 所示为典型笔记本电脑显示屏的实物外形。

液晶显示屏主要由液晶屏、驱动电路和背部光源组件构成。

液晶屏主要用来显示图像;

液晶屏的背面是背部光源,用于为液晶屏照明;在液晶屏中安装有多组水平和垂直驱动电路,用以为液晶屏提供驱动信号。

图1-6 所示为典型笔记本电脑显示屏的结构。

压及信号传输。

● 供电电路

供电电路是笔记本电脑的动力源,由于主板上各部分的供电电压、电流各有不同,因此

需要供电电路将电压进行转换、稳压、滤波等一系列处理后再变为多路输出,为笔记本电脑的各部分提供工作电压。

● 接口电路

笔记本电脑在工作时,常需要连接外部设备,例如打印机、U 盘、外接鼠标、外接键盘

等,而连接这些设备通常需要与其相匹配的不同接口,方能实现笔记本电脑与这些设备之间的信号传输。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

20%

2

6.3V CERM

805

1 C8

10uF

20%

2

6.3V CERM

805

1 C153

0.1uF

20%

2

10V CERM

402

5%

1 C223

0.1uF

20%

2

10V CERM

402

1 C91

0.1uF

20%

2

10V CERM

402

1 C114

0.1uF

20%

2

10V CERM

402

1 C104

+3V_MAIN +3V_SLEEP

3V_5V_OK

+2_5V_MAIN

~11MS ~13.5MS

2.4V - ??? MS

2.6 MS

+BATT

+2_5V_SLEEP +1_5V_MAIN

2.6 MS

3Sቤተ መጻሕፍቲ ባይዱ3P PRISMATIC CELLS

NO INRUSH PROTECTION

WHEN ONLY BATTERY IS CONNECTED

1625 NOT RUNNING

SHUTDOWN: RUNNING SLEEP: RUNNING RUN: RUNNING

RC AT 1M*0.047UF @ 24V

STARTS 2.0MSEC AFTER DCDC_EN_L BECOMES LOW

+5V_MAIN

DCDC_EN_L

SHUTDOWN: STOPPED SLEEP: RUNNING RUN: RUNNING

U21 PG 31 +

RUN/SS

INRUSH LIMITER

PG 30

BUCK +24V_PBUS VCC REGULATOR

(LTC1625)

BACKLIGHT INVERTER

+PBUS (12.8V)

+5V_MAIN

VCC

MAIN 2.5V/1.5V DC/DC

(MAX1715) PG 35 PGOOD

WHEN ONLY BATTERY IS CONNECTED

+24V_PBUS

SLEEP SLEEP_L_LS5

B

BACKUP BATTERY CIRCUIT CHARGES OFF +PBUS AND PREVENTS +PBUS AND +24V_PBUS FROM DROPPING BELOW 6V (UNTIL DRAINED)

+1_5V_SLEEP

1_5V_MAXBUS

R702

0

1

2

MPC7447 PULL-UPS

R2411

470

5% 1/16W

MF 402 2

D

C25

10uF

20% 6.3V CERM

805

C342

10uF

20% 6.3V CERM

805

1 C344

10uF

20%

2

6.3V CERM

805

1 C346

10uF

U17

BOOT ROM 1M X 8

U52

USB 2.0 CONTROLLER

CARDBUS Connector

33MHZ

16/32 BITS

C

3.3V/5V

U26

TI PCI1510 CardBus

Controller

USB PORT E

PCI

J9

32BITS

PCI BUS

Modem Board Connector

+1_5V_SLEEP

1_5V_2_5V_OK

(MAX1715 OUTPUT)

A

BATTERY VOLTAGE FEED-IN PATH

+PBUS

1_5V_2_5V_OK

(AT LTC1778 RUN/SS)

GPU_VCORE

(D3HOT)

~???MS

A

GPU_VCORE

PG 31

(D3COLD)

+1_8V_MAIN

1.9 MS

POWER BLOCK DIAGRAM

8

7

6

5

4

3

2

1

8

7

6

5

4

3

2

1

CPU_VCORE_SLEEP 5 6 34 38 39

CPU_VCORE DECOUPLING NETWORK

MAXBUS_SLEEP 5 7 8 15 16 23 34 38

CPU_OVDD DECOUPLING NETWORK

PG 20

SHUTDOWN: STOPPED

GPU_VCORE +1.2V/+1.0V

SLEEP: D3HOT/D3COLD

RUN: RUNNING

RUN: RUNNING

CPU_VCORE (+1.4V/+1.5V)

+PBUS

WHEN IT’S OPEN

D3_COLD

TURNS ON AS LOW AS 0.8V/TYP 1.5V

1394 OHCI

ULTRA ATA/100

U39

3.3V 8BIT TX/RX

Connector

EIDE

U48/J2/J4

PMU

100MHZ

I2S I2C

Fan

I2C Circuit

J10

UIDE

J3 (SHARE WITH BLUETOOTH)

LEFT USB

ETHERNET

10/100/1000

SHDN

DC/DC (MAX1717)

PG 34

C

PG 32

+4_6V_BU

RUN/SS - 5V

TURNS ON AT >1V <100UA ALLOWED INTERNAL ZENER CLAMP TO 6V

+5V_MAIN

+PBUS (12.8V)

VCC

EXT_VCC

DC/DC

SHUTDOWN: STOPPED SLEEP: STOPPED

J11

OPTICAL DRIVE

Connector

J14

TUBA (SOUND)

Battery

Power Supply

Connector

& Charger

SMBUS

U36

SUTRO (PWR)

Connector

D

G/MII

J13

Connector

3.3V

LMU

I2C

3.3V 10/100/1000

8BIT TX 8BIT RX 125MHZ

NOT USED

USB PORT B USB PORT C USB PORT D

U44

INTREPID

VIA/PMU BOOTROM

J5 Serial Debug Connector

SERIAL 5V

J15

TRACKPAD Connector

Keyboard Connector

KB LED LIGHT SENSOR

0.1uF

20%

2

10V CERM

402

1 C48

0.1uF

20%

2

10V CERM

402

1 C38

0.1uF

20%

2

10V CERM

402

1 C74

0.1uF

20%

2

10V CERM

402

1 C275

0.1uF

20%

2

10V CERM

402

1 C46

0.1uF

20%

2

10V CERM

402

1 C47

C

MAIN 3V/5V PGOOD DC/DC

(LTC3707) VCC PG 33 STBYMD

3V_5V_OK

HOLDS BOTH RUN/SS AT GND WHEN IT’S CONNECTED TO GND TURNS CONTROL TO RUN/SS

DCDC_EN SLEEP

(LTC1778)

0.1UF

20%

2

10V CERM

402

1 C170

0.1UF

20%

2

10V CERM

402

+1_8V_SLEEP

1/16W MF 603

1_8V_MAXBUS

R693

0

1

2

38 34 23 16 15 8 7 5 MAXBUS_SLEEP

FIREWIRE UATA 100 EIDE

800 MB/S

NOT USED CARDSLOT I2S I2C

USB 2.0

C

J12

USB PORT A

SCCA

RIGHT USB

BACKUP BATTERY

NOT USED

USB 2.0

J3 (SHARE WITH LEFT USB)

BlueTooth

HOWEVER, 5V SHOULD TURN ON ~2.23MS AFTER DCDC_EN_L OR PMU_POWERUP_L BECOMES ’1’; MUCH LESS THAN THE RC CHARGING AT INT_VCC (5V)

DCDC_EN_L D3_HOT