K60芯片详述

K60(Rev6-Ch55-TSI)(中文)

第55 章触屏输入(Touch senseinput ,TSI)55.1 引言触摸感应输入(TSI)模块具有高灵敏和强鲁棒性的电容触摸感应检测能力。

通过独立的可编程的检测阈值和结果寄存器,TSI模块可以完成电容的测量。

TSI 模块在带有超低电流加法的低功耗模式下运行,能以一个触摸事件唤醒CPU。

它是一种稳定的电容测量模块,能够实现键盘触摸,旋转和滑动。

55.2 特点(1)具有多达16个输入的电容触摸感应式引脚和独立结果寄存器(2)具有可编程的阈值上下限,自动检测电极电容量的改变(3)在运行模式和低功耗模式下,自动周期扫描单元会有不同的占空比(4)为了实现键盘触摸,旋转,滑动,完全支持FSL触摸感应SW库(TTS)。

(5)运行在所有低功耗模式下:Wait, Stop, VLPR, VLPW, VLPS,LLS,VLLS{3,2,1}(6)能够从低功耗模式中唤醒MCU(7)配置中断:a.扫描结束中断或者超出范围中断b.TSI错误中断:电极板和VDD/VSS短路或者转换运行超时(8)补充温度和提供电压变化(9)在低功耗模式下,支持不需要外部晶体的操作,(10)每个电极电容量测量可以整合从1到4096次(11)可编程的电极振荡器和TSI参考振荡器可以实现模块灵敏度高,扫描时间短和功耗低的功能(12)在不需要外部硬件时,实现每个电极电容测量只需要使用一个引脚55.3 总述这部分是对TSI模块的总述。

下图给出了简化了的TSI模块结构图。

图55-1 触摸感觉输入结构图55.3.1 电极电容测量单元电极电容测量单元能感应一个TSI引脚的电容量变化和输出一个16位结果。

这个模块基于双振荡器架构。

其中一个振荡器和外部电极阵列连接,根据电极电容器震荡;而其他振荡器则根据内部参考电容器进行振荡。

在可配置的外部电极振荡器振荡期间,参考振荡器的周期计数值可以衡量引脚的电容量。

图55-2 TSI电容衡量单元结构图为了适应电极电容量的不同大小,电极振荡器使用一个可编程的电流源对引脚电容进行充电和放电,该电流源由SCANC[EXTCHRG]位进行选择。

飞思卡尔K60入门

一、飞思卡尔Kinetis功能特性

1、ARM发展史 2、ARMv7处理器分类 3、ARM Cortex-M4特性 4、飞思卡尔Kinetis家族介绍 5、K60内部资源介绍

山东大学 Kinetis培训

ARM发展史

ARM架构发展历程

山东大学 Kinetis培训

ARMv7处理器分类

ARMv7根据应用分类:

• 应用处理器(Cortex-A系列) Aplication Processor • 实时控制器(Cortex-R系列) Real-time Processor • 微控制器(Cortex-M系列) Micro Controller 山东大学 Kinetis培训

最快频率、最高性能、合理功耗 即

模拟比较器

开发环境

3通道

CW10.1、IAR、MDK

山东大学 Kinetis培训

软件应用

调试工具

开发环境

二、K60开发生态系统

其 他 支 持

山东大学 Kinetis培训

Kinetis开发环境

支持Kinetis开发的IDE(集成开发环境)目 前主要包括CodeWarrior10.1及以上版本, IAR6.1及以上版本和Keil MDK(即Keil for ARM)等。

山东大学 Kinetis培训

飞思卡尔Kinetis家族

Kinetis系列是由飞思卡尔推出的业界第一款基于ARM

Cortex-M4内核的混合信号微控制器,采用飞思卡尔创新的 90nm薄膜存储器(TFS)闪存技术,具有独特的Flex存储器

(可配置的内嵌 EEPROM)。

Kinetis 微控制器系列融合了最新的低功耗革新技术,具有 高性能、高精度的混合信号能力,宽广的互连性,人机接口和

k60在KEIL中的使用手册

K60是飞思卡尔公司的cortex m4系列CPU,目前技术较为新,市面上的开发板使用的芯片大部分是144pin的PK60X256VLQ100的样品,其主频正常使用为100MHz,其超频可以到达150作用。

下面我以KEIL MDK4.23和J-Link V8作为开发环境和下载器,下面是简单的使用手册(以图文形式向大家介绍)。

一、首先下载和安装KEIL MDK4.2.3地址:/download/product/选择MDK-ARM后,填写信息就可以直接下载。

二、安装省略啦,window下软件安装就是傻瓜式的了,只要会单机和双击就可以了,呵呵。

三、创建项目1.首先打开安装好的keil mdk,他的IDE采用的是keil4:如下图2.选择项目菜单Project,点击New uVision Project。

3.选择存储路径,写好项目名称test,点击保存。

4.选择CPU型号,我们这里使用的是飞思卡尔公司的MK60系列CPU,所以我们选择如下图所示。

5.点击ok,点击是。

出现如下图所示,其中startup_MK60DZ10.s为K60系列CPU的启动文件的汇编源代码。

6.设置J-LINK下载器,点击Flash中的Configure Flash Tool…如图所示。

(1)、Utilties选项卡中的Use Taget Driver for Flash Programming选择Cortex-M/R J-LINK/J-Trace。

(2)、Debug选项卡中的Use选择Cortex-M/R J-LINK/J-Trace。

(3)、C/C++选项卡中的Include Paths点击后面按钮。

添加K60头文件路径C:\Keil\ARM\INC\Freescale\Kinetis。

红色为安装目录。

7.下面我们新建个文件,点击File中的New,然后保存为main.c。

然后右键Source Group1添加TYS_system_k60.c和main.c文件到项目中。

K60-02节

K60系列的存储器空间地址映像(一)

地址范围 0x0000_0000~0x0FFF_FFFF 0x1000_0000~0x13FF_FFFF 大小 实际的物理对象 256MB 可编程flash和只读数据(包括一开始1024字节的异常中 断向量) 64MB 对MK60N256VLQ100芯片:未使用 对MK60X256VLQ100芯片:FlexNVM 对MK60N512VLQ100芯片:未使用 对MK60N256VMD100芯片:未使用 对MK60X256VLQ100芯片:FlexNVM 对MK60N512VMD100芯片:未使用

256

512 512

256

256 512

—

4 —

64

64 128

100

100 100

2.4 K60系列微控制器的存储器映像与编程结构

2.4.2 K60系列存储器映像 ARM Cortex-M4为32位处理器内核。内部的数据是32位 的,寄存器是32位的,存储器接口也是32位的。

CPU频 率 (MHz) 100 100 100 120 150 120 150 闪存 (KB) 256 512 256 512 512 1024 1024 FlexNV M (KB) — — 256 512 512 — — SRAM (KB) 64 128 64 128 128 128 128 FlexRA M (KB) — — 4 16 16 — — 100 LQFP 14× 14 + + + — — — — 104 BGA 8× 8 + + + — — — — 144 LQFP 20× 20 + + + + + + + 144 BGA 13× 13 + + + + + + + 196 BGA 15× 15 — — — + + + + 256 BGA 17× 17 — — — + + + +

k60介绍(中文)

第2章简介2.1 概要本章提供了Kinetis组合和K60系列产品的概述。

同时,本章提供了本文件所包涵设备的高水准的描述。

2.2 Kinetis组合Kinetis是低功耗可扩展和在工业上使用混合信号ARM®Cortex™-M4系列MCU的最好的组合。

第一部分介绍超过200引脚、外围设备和软件兼容性的5个MCU系列。

每个系列提供了优良的性能,与普通外设内存,内存映射,并提供内部和系列之间轻松迁移包和功能可扩展性。

Kinetis MCUs使用了飞思卡尔的新的90nm带有独特FlexMemory的薄膜存储器(TFS)闪存技术。

Kinetis系列MCU结合了最新的低功耗革新技术和高性能,高精密混合信号功能与连通,人机界面,安全及外设广泛。

Kinetis MCUs使用了飞思卡尔和ARM第三方合作伙伴的市场领先的捆绑模式。

表示低功耗混合信号USB 段LCD以太网加密和篡改检测DDR所有Kinetis系列都包涵强大的逻辑、通信和时序阵列和带有伴随着闪存大小和I/O数量的集成度等级的控制外围部件。

所有的kinetis系列包涵一下共同特征:· 内核:· ARM Cortex-M4内核提供1.25 DMIPS / MHz的DSP指令(浮点单元在kinetis系列可用)。

· 高达32位的DMA,同时尽可能减小CPU干预。

· 提供50MHz、72MHz和100MHz几种CPU频率(120MHz和150MHz在kinetis可用)。

· 超低功耗:· 10种低功耗操作模式通过优化外设执行和唤醒时间来延长电池寿命。

· 为了增加低功耗的灵活性,增加了低漏唤醒单元、低功耗定时器和低功耗RTC。

· 业界领先的快速换醒时间。

· 内存:· 从32 KB闪存/ 8 KB的RAM可扩展为1 MB闪存/128 KB的RAM。

同时使空白的独立闪存执行代码和固件更新。

基于K60的数字逻辑芯片测试仪设计

基于K60的数字逻辑芯片测试仪设计任玲芝;张光照;李哲文【摘要】针对数字逻辑芯片损坏时却无法观察的情况,采用K60控制器,配合液晶显示屏、矩阵按键和芯片检测电路等,设计了一款界面友好、操作简单,具有检测数字逻辑芯片功能的芯片测试仪.不仅能够检测整个芯片是否正常工作,若芯片有多路输入输出,还能够检测具体某一路输入输出的运行状况,这样即使某路输入输出不能正常使用,还可以使用其他路,提高了芯片的利用率.【期刊名称】《赤峰学院学报(自然科学版)》【年(卷),期】2018(034)008【总页数】3页(P108-110)【关键词】K60;数字逻辑芯片;液晶显示屏;矩阵按键【作者】任玲芝;张光照;李哲文【作者单位】巢湖学院机械与电子工程学院, 安徽巢湖 238000;巢湖学院机械与电子工程学院, 安徽巢湖 238000;巢湖学院机械与电子工程学院, 安徽巢湖238000【正文语种】中文【中图分类】TN606;TN790 引言在数字电子技术高速发展的今天,越来越多的芯片被制造生产出来,芯片的损坏率也越来越高.一个电路系统被设计出来,如果不知道芯片损坏的情况,去检查硬件电路系统是否合格,显然是一个费力不讨好的事情[1-5].本文依托巢湖学院数字电子技术实验室设计了一套能够自动检测常用的数字逻辑芯片是否损坏的芯片测试仪,并将待测芯片型号和测试结果通过TFT液晶显示屏显示出来,降低了学生的误判率,提高学生的实验效率.1 测试仪总体方案设计考虑到数字电子技术实验室里使用最多的是74系列芯片,本测试仪针对常用的74系列数字芯片进行测试[6-8].测试仪的工作原理是采用K60主控器向待测芯片的输入端引脚发出高低电平信号,经过待测芯片内部集成电路的逻辑运算,将运算结果输出到输出引脚,K60主控器读取待测芯片的输出引脚电平信号,根据待测芯片预期的逻辑功能判断逻辑运算结果是否正确,若结果正确,说明待测芯片完好,否则说明待测芯片损坏.数字逻辑芯片测试仪系统设计由五部分组成的:电源供电模块、K60核心控制模块[9]、待测芯片检测模块、按键输入模块、液晶显示模块.测试仪运行流程是:通过6*6按键输入模块输入待测芯片型号信息,K60主控制器读取按键模块,确定芯片型号信息后,配置待测芯片输入引脚的高低电平信号进行逻辑运算,读取待测芯片的输出引脚电平信号,判断逻辑运算结果是否符合该待测芯片的预期逻辑运算结果,从而确定该待测芯片是否损坏,将检测结果信息在液晶显示屏显示出来.数字逻辑芯片测试仪硬件组框图如图1所示.图1 数字逻辑芯片测试仪硬件框图2 测试仪硬件设计图2 测试仪整体电路原理图根据芯片测试仪的硬件框图设计硬件电路原理图,主要有K60主控制器最小系统电路、电源供电电路、按键输入电路、待测芯片检测电路和液晶显示接口电路.K60主控制器最小系统电路主要包括晶振电路、复位电路、JTAG下载电路、K60芯片短路保护电路和对外引脚扩展电路.由于本芯片测试仪中的控制器使用的是K60成品模块,在电路原理图中只需要设计出K60的控制引脚和数据引脚接口电路即可,测试仪整体电路原理图如图2所示.2.1 电源供电电路设计本测试仪电源供电电路需要5V和3.3V两种电压,5V电压主要给K60主控制器和待测芯片供电,3.3V电压给液晶显示屏供电.为了提高测试仪的便携性和电压的稳定性,选择7.2充电电池为总电源,经过LM2940三端稳压器稳定输出5V电压,再将其输入到AM1117-3.3稳压芯片,输出得到稳定的3.3V电压[10].图3 电源供电电路2.2 按键输入电路设计按键输入电路主要用于输入芯片型号,芯片型号对应了该芯片具体的逻辑功能,芯片型号输入主要由6*6矩阵按键和4个独立按键组成.6*6矩阵按键部分共有36个按键,分别对应着26个英文字母和0-9这10个数字,每个按键按下,对应一个特定的英文字符或数字,输入待测芯片具体型号.设计的4个独立按键中,其中一个按键用于输入待测芯片型号后,作为确认键使用,另外3个暂时未用,用于以后进一步升级测试仪扩展时备用.按键输入电路如图4所示.图4 按键输入电路2.3 待测芯片检测电路设计待测芯片检测电路主要用于放置不同引脚的逻辑芯片和检测不同的数字芯片逻辑功能是否正常,主要由芯片底座和芯片引脚选择开关组成[11-12].芯片底座用于放置待检测芯片,根据常用数字芯片引脚数目不同,本测试仪设计了14脚、16脚、18脚和20引脚四种引脚数量不同的芯片底座.芯片引脚选择开关主要为了用于接通芯片引脚,因为有些芯片引脚是空引脚,就不需要接通电路的,若芯片引脚需要连接电路,接通引脚开关,若不需要连接电路的引脚,断开对应的引脚开关.芯片底座与引脚选择开关连接,然后都与K60主控制器的IO口连接,K60发出控制逻辑信号给芯片输入引脚,再读回芯片逻辑运算后的值,便能够判断出芯片的好坏.待测芯片检测电路如图5所示.图5 待测芯片检测电路2.4 液晶显示接口电路液晶显示接口电路是K60控制液晶显示屏显示待测芯片型号、芯片的逻辑功能和芯片检测结果信息的连接电路.液晶显示屏采用1.44寸、128*128分辨率,具有8位数据总线传输模式,需要3.3V电压供电.K60主控制器的PTC0到PTC7接液晶显示屏的8位数据总线口,为读写数据的并行引脚,而PTC9到PTC13五个引脚分别是时钟、片选等引脚,其他的引脚为闲置引脚可以不使用.液晶显示接口电路如图6所示.图6 液晶显示接口电路3 测试仪软件程序设计根据测试仪硬件电路编写相应的软件程序来实现测试仪对数字逻辑芯片的检测、电平状态的采集与分析、按键扫描和显示等功能.软件程序总体共分为五个部分:首先,初始化K60主控器和液晶显示屏;第二,进行矩阵按键检测,通过6*6矩阵按键输入待测芯片具体型号,并将待测芯片型号和逻辑功能等信息实时显示在液晶屏上;第三,进行独立按键的检测,也就是输入芯片型号后通过独立按键确认是否需要执行待测芯片完好性检测程序,一旦按下确认键后,K60开始对待测芯片的完好性进行检测,之后并将检测结果显示在液晶屏上,至此,整个程序的流程到此结束.软件整体程序流程图如图7(a)所示.测试仪软件设计中最关键的部分是芯片检测程序设计.通过6*6矩阵按键输入芯片型号,按确认键后,K60控制器就立即启动芯片检测程序.由于待检测的芯片型号很多,因此必须要设计出各种芯片逻辑运算后的结果集,K60控制器根据具体芯片型号配置好检测电路中待测芯片输入引脚的电平信号,待测芯片自己进行逻辑运算后,将运算结果输出到输出引脚,K60读取输出电平信号后,再与结果集中的结果比较,若实时读取的电平信号与结果集中电平信号相同,则判定芯片完好,若比较结果不同,则判定芯片损坏,将芯片好坏信息显示在液晶显示屏上.芯片检测程序流程图如图7(b)所示.图7 测试仪软件程序流程图4 测试与验证使用Altium Designer软件绘制电路的PCB图,加工出电路板,焊接元器件,并将软件程序下载到K60控制器,对测试仪进行软硬件测试.本次测试的芯片有74LS00、74LS20、74LS86、74LS138、74LS151、74LS112、74LS74、74LS192 等. 若需要测试更多芯片,在软件程序中添加相应的代码即可.图8为测试仪软硬件测试结果,图8(a)是测试仪硬件电路板,图8(b)是液晶显示屏上显示的是4路二输入与非门74LS00芯片的检测结果,检测结果显示,该芯片的第一路、第二路、第三路共3路与非功能正常,只有第四路这1路与非功能损坏.图8 测试仪软硬件测试结果5 结束语进行数字电子技术实验时,经常会遇到数字逻辑芯片可能由于各种各样样的原因已损坏,但是使用者并不知情,总是在遇到其他问题之后,才可能会想起芯片是否损坏,这样耗时又耗力,从而耽误了大量的时间.本文针对该情况设计了一款数字逻辑芯片测试仪,解决实验前逻辑芯片的完好性测试工作,通过液晶显示屏能够直观的观察到芯片好坏,省时省力,操作简单,有利于教学过程的开展和实施,提高了实验教学效果.【相关文献】〔1〕刘艳,唐海贤,景昊,等.常用逻辑门芯片测试装置研究与设计[J].实验技术与管理,2017,34(1):94-97.〔2〕肖宝森.多功能数字芯片测试仪的设计与应用[J].实验技术与管理,2010,27(12):133-136. 〔3〕包本刚,刘坤,邹帅等.基于 FPGA/DSP 的数字芯片测试[J].仪表技术与传感器,2010(7):42-45. 〔4〕李天义,耿跃华,富坤等.一种新型数字芯片测试仪的设计与实现[J].自动化仪表,2014,35(11):60-63/67.〔5〕毛露露,王刚,秦玉伟.便携式数字芯片检测仪的设计[J].河南科学,2016,34(5):702-705. 〔6〕刘远鹏,胡惟文.集成电路芯片测试仪设计[J].传感器世界,2016(10):14-17.〔7〕唐颖,黄河.基于CPLD的新型数字集成芯片检测仪设计[J].仪表技术与传感器,2010(7):37-38/68.〔8〕孙韩,朱军.一种面向TTL集成电路的小型检测仪设计[J].办公自动化:学术版,2015(8):35-36. 〔9〕何林明,罗林.基于 Kinetis K60单片机的开发实验系统[J].通讯世界,2015(4):197-198. 〔10〕曹磊,程新华.飞思卡尔智能赛车电源模块的设计与制作[J].产生与科技论坛,2015,14(3):62-63.〔11〕刘艳,高茜,张斌,等.一种常用数字电路芯片功能检测系统[J].实验室研究与探索,2017,36(5):68-71.〔12〕王艳芳,张颖,赵二刚,等.数字电路芯片检测系统的研制与应用[J].实验室科学,2015,18(1):43-46.。

飞思卡尔K60入门资料课件

将JTAG调试器连接到计算 机,并下载和安装相应的 驱动程序。

打开Keil MDK-ARM软件 ,创建一个新项目,选择 正确的芯片型号(K60), 并配置项目属性,如工作 空间、工具链等。

使用串口通信线将开发板 与计算机连接起来,以便 在开发过程中进行调试和 数据传输。

使用Keil MDK-ARM软件 编写代码,并进行编译和 调试。

K60在图像处理中的应用

K60芯片具有高速的图像处理能力,可以用于实现各种图像处理算 法,如图像增强、目标检测、人脸识别等。

图像处理实例代码

提供一些基于K60芯片的图像处理实例代码,包括图像增强、目标 检测等。

通信系统实例

通信系统概述

通信系统是实现信息传输和交换的技术体系,包括无线通信、有 线通信、卫星通信等。

软件问题及解决方案

总结词

软件问题通常涉及到编程环境、编译错误、烧录程序等,需要检查软 件配置和代码错误。

编程环境配置

确保你使用的编程环境(如IAR Embedded Workbench、Keil uVision等)已正确配置,包括驱动程序安装、工具链设置等。

编译错误

检查代码是否有语法错误或逻辑错误,仔细阅读编译器给出的错误提 示,定位并修复问题。

K60在通信系统中的应用

K60芯片具有高速的通信接口和强大的数据处理能力,可以用于实 现各种通信系统,如无线通信网络、卫星通信系统等。

通信系统实例代码

提供一些基于K60芯片的通信系统实例代码,包括无线通信网络协 议栈的实现、卫星通信系统的数据处理等。

05

K60芯片常见问题及解决方案

硬件问题及解决方案

开发环境常见问题及解决方案

1. Keil MDK-ARM软件安装问题:确保从官方网 站下载正确的版本,并按照安装向导进行操作。 如果遇到问题,可以查阅Keil官方文档或寻求技 术支持。

K60(Rev6-Ch25-OSC)(中文)

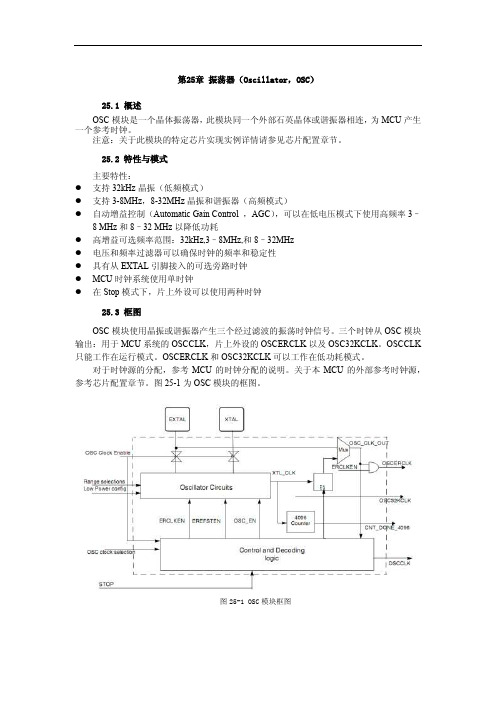

第25章振荡器(Oscillator,OSC)25.1 概述OSC模块是一个晶体振荡器,此模块同一个外部石英晶体或谐振器相连,为MCU产生一个参考时钟。

注意:关于此模块的特定芯片实现实例详情请参见芯片配置章节。

25.2 特性与模式主要特性:●支持32kHz晶振(低频模式)●支持3-8MHz,8-32MHz晶振和谐振器(高频模式)●自动增益控制(Automatic Gain Control ,AGC),可以在低电压模式下使用高频率3–8 MHz和8–32 MHz以降低功耗●高增益可选频率范围:32kHz,3–8MHz,和8–32MHz●电压和频率过滤器可以确保时钟的频率和稳定性●具有从EXTAL引脚接入的可选旁路时钟●MCU时钟系统使用单时钟●在Stop模式下,片上外设可以使用两种时钟25.3 框图OSC模块使用晶振或谐振器产生三个经过滤波的振荡时钟信号。

三个时钟从OSC模块输出:用于MCU系统的OSCCLK,片上外设的OSCERCLK以及OSC32KCLK。

OSCCLK 只能工作在运行模式。

OSCERCLK和OSC32KCLK可以工作在低功耗模式。

对于时钟源的分配,参考MCU的时钟分配的说明。

关于本MCU的外部参考时钟源,参考芯片配置章节。

图25-1为OSC模块的框图。

图25-1 OSC模块框图25.4 OSC信号说明25.5 外部晶振/谐振器连接晶振/谐振器频率的引用连接如表25-2所示。

当使用低频率,低功耗模式时,唯一的外部部件就是晶振或陶瓷谐振器本身。

在其它振荡器模式中还需要负载电容(Cx,Cy)和反25.6 外部时钟连接在外部时钟模式,引脚连接如图25-6所示。

注意:当GPIO替换功能配置成外部时钟连接时,XTAL可以用作GPIO。

25.7 存储器映射/寄存器定义一些振荡器模块寄存器位通常被复用到其他模块中,例如MCG或SIM。

25.7.1 OSC Control Register (OSC_CR)注意:在OSC被使能并且开始产生时钟之后,其它配置如低功耗和频率范围就不能被修改了。

k60

• • • • •

通用寄存器R0~R12 堆栈指针R13 连接寄存器R14(LR) 程序计数寄存器R15 特殊功能寄存器(程序状态字、中断、控 制)

• 串行外设接口(SPI,Serial Peripheral Interface) 是Freescale公司推出的一种同步串行通讯接口, 用于微处理器和外围扩展芯片之间的串行连接。 SPI全双工主--从连接,四线同步传输。从机,主 机(串行时钟)。主入从出 ,主出从如。低功耗 模式。选择从机:主机将该从机的选择线拉低。 • I2C:在硬件上,二线制的I2C串行总线使得各IC 只需最简单的连接,而且总线接口都集成在IC中, 不需另加总线接口电路。支持多主控。主机提供 时钟信号,每个设备有独立地址。采用了独特的 寻址约定,规定了起始信号后的第一个字节为寻 址字节,用来寻址被控器件,并规定数据传送方 向。半双工。

• 控制器局域网CAN(Controller Area Network):CAN网络上的任何一个节点均 可作为主节点主动地与其他节点交换数据; CAN网络节点的信息帧可以分出优先级, 这为有实时性要求的控制提供了方便; CAN的物理层及数据链路层有独特的设计 技术,使其在抗干扰以及错误检测等方面 的性能大大提高。

K60可选择的芯片类型

芯片类型 CPU频 率 (MHz) 100 100 100 100 100 100 引脚 数 封装 Flash容 量(KB) 程序空间 (KB) EEPRO M(KB) SRAM(K B) GPIO

MK60N256VLQ100 MK60X256VLQ100 MK60N512VLQ100 MK60N256VMD100 MK60X256VMD100 MK60N512VMD100

144 144 144 144 144 144

K60芯片NVIC模块中断相关寄存器配置以及应用举例

} }

如果需要使能 LPTMR 的中断,直接调用 enable_irq (85) 即可。

如果要在 NVIC 中关闭某个中断源,只需对中断使能清除寄存器中的对应位置位即可, 实现代码如下。

}

另外,对于一个完整的中断程序代码,用户还需编写中断服务程序代码以及定义中断 服务函数,并在 Vector.h 文件中声明自定义的中断服务函数,并将中断向量表中的宏定义 修改为此中断服务程序的函数名,指定中断服务程序的入口地址。

void default_isr(void); //默认的中断服务程序 extern void lptmr_isr(void); //自定义的终端服务程序

对于非优先级中断寄存器,如上面提到的 NVICISERx、NVICICERx、NVICSPRx、 NVICCPRx 以及 NVICABRx,组号的计算公式为 IRQ / 32,所以可以得到 LPTMR 的 NVIC 非优先级中断寄存器的组号为 85 / 32 = 2,从而得到 LPTMR 需要使用的非优先级中 断寄存器为 NVICISER2、 NVICICER2、 NVICISPR2、NVICICPR2、NVICIABR2。这些 寄存器都是 32 位的,所以对应于 LPTMR 的位号计算公式为 IRQ % 32,得到 85 % 32 = 21。 确定完了组号和位号,便得到了需要设置的 LPTMR 的非优先级中断控制寄存器及相应的 位为:NVICISER2[21]、 NVICICER2[21]、 NVICISPR2[21]、NVICICPR2[21]、 NVICIABR2[21]。

K60核心板说明与扩展板_SD-Ex-D_对接说明

K60核心板说明与扩展板(SDExD)对接说明 1、核心板引脚说明K60一共有100个GPIO口,还有其他为复用的非GPIO口,如USB、ADC 等引脚。

核心板引出了所有的GPIO和其他非K60最小系统的引脚。

具体的引脚如下。

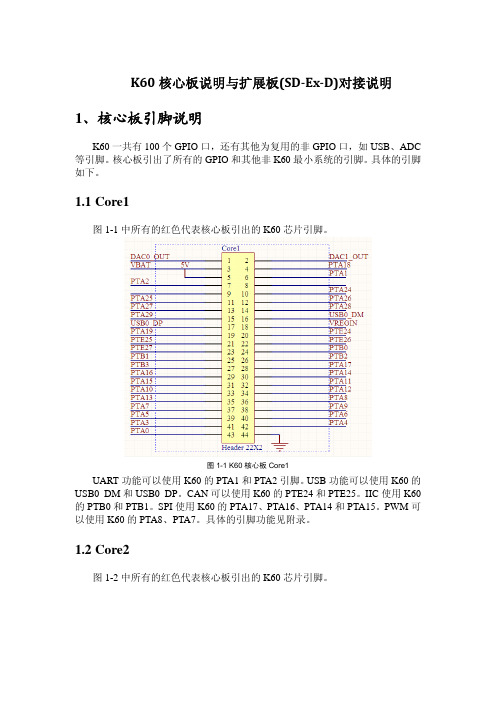

1.1 Core1图1-1中所有的红色代表核心板引出的K60芯片引脚。

图1-1 K60核心板Core1UART功能可以使用K60的PTA1和PTA2引脚。

USB功能可以使用K60的USB0_DM和USB0_DP。

CAN可以使用K60的PTE24和PTE25。

IIC使用K60的PTB0和PTB1。

SPI使用K60的PTA17、PTA16、PTA14和PTA15。

PWM可以使用K60的PTA8、PTA7。

具体的引脚功能见附录。

1.2 Core2图1-2中所有的红色代表核心板引出的K60芯片引脚。

图1-2 K60核心板Core2可以使用K60的ADC1_SE16和ADC0_SE16。

具体的引脚功能见附录。

1.3 Core3图1-3中所有的红色代表核心板引出的K60芯片引脚。

图1-3 K60核心板Core3具体的引脚功能见附录。

2、核心板与大板对接在设计电路时,考虑到与旧的扩展板兼容,做了如下设计,保证K60核心板与扩展板兼容。

以下图片中的蓝色表示大板的功能,红色代表核心板引出引脚。

2.1 Core1图2-1 Core1引脚定义2.2 Core2LCD使用K60的PTE可以实现,具体功能见参考代码。

图2-2 Core2引脚定义AD5和AD9分别接K60的ADC1_SE16和ADC0_SE16。

2.3 Core3可以使用K60的PTC口实现LED功能,具体实现见参考代码。

图2-3 Core3引脚定义3、附录:144引脚资源简明表3.1 硬件最小系统引脚K60N512VM100芯片电源类引脚,BGA封装22个,LQFP封装27个,其中BGA 封装的芯片有五个引脚未使用(A10、B10、C10、M5和L5)。

K60(Rev6-Ch04-Memory Map)(中文)

1. EzPort主机端口和DMA主机端口复用。

到AIPS-Lite外设桥和GPIO模块地址空间限制的访问权限受限于内核、DMA和EzPort。

2. ARM Conrtex-M4内核访问也包含调试接口。

4.2.1位带别名区

SRAM_U,AIPS-Lite和GPIO模块资源依附于Cortex-M4内核位带别名区。

处理器包含两个32MB位带别名区,与两个1MB的位带别名区相连。

每个32位的32MB空间有自己独立的位带别名区。

在混合区的32位写操作和位宽区的读写操作一样。

写到位带别名区的值的第0位有如下作用:

·写1到第0位是用于置位。

·写0到第0位是用于清零。

从混合区读数据:

·0x0000_0000是清零。

·0x0000_0001是置位。

图4-1 混合位宽映射

4.3 Flash存储映射

各种Flash存储和Flash寄存器位于不同的基址。

如下图所示。

图4-2 只包含可编程flash 存储映射

图4-3 包含FlexNVM 的存储映射

4.3.1 交替非易失性IRC 用户修剪说明

为防止自定义IRC 用户通过一些开发工具裁剪,系统保留了由以下非易失性位(4字节)。

在该位上可以储存工厂裁剪的交替IRC 裁剪信息。

如果想要覆盖出厂值,用户的软件必须加载新的值到MCG 裁剪寄存器。

4.4 SRAM 存储映射

片上RAM 分为SRAM_L 和SRAM_U 。

同时SRAM_L 和SRAM_U

是连续。

006K60与最小系统-戴敏

K60系列微控制器的存储器映像与编程结构

K60系列微控制器具有: IEEE 1588以太网 全速和高速USB 2.0 硬件加密和防窜改探测能力, 具有丰富的模拟、通信、定时和控制外设 256 KB~ 1MB闪存

第7页,共35页。

K60系列的模 块结构框图

1.内核模块

2.系统模块 3.存储模块

ADC/RTC/UART/SPI/I2S/SDHC/GPIO

第20页,共35页。

3)K60的硬件最小系统原理图

单片机内部虽然集成了很多电路,但仍旧不能独立运行,必须 要外连一些电路,才能使单片机运行起来。这种能使单片机工 作的最简电路,我们叫做单片机最小系统。

一般情况下,MCU的硬件最小系统由电源、晶振及复位等电路组成。 芯片要能工作,必须有电源与工作时钟。 复位电路则提供不掉电情况下MCU重新启动的手段。

第11页,共35页。

K60系列的存储器空间地址映像(二)

地址范围 0x4000_0000~0x4007_FFFF

大小

实际的物理对象

512KB 外设总线0的位寻址区(AIPS-Lite0)

0x4008_0000~0x400F_EFFF 508KB 外设总线1的位寻址区(AIPS-Lite1)

0x400F_F000~0x400F_FFFF 4KB 通用输入输出的位寻址区

L6

42

30

3.3V RTC模块的输入电源(可电池供电)

电源

VDDA、VSSA H5、H6 31、34

22、25

30.V3V、A/D模块的输入电源

VREFH、 VREFL

G5、G6 32、33

23、24

30.V3V、A/D模块的参考电压

飞思卡尔K60入门课件

K60芯片内置硬件浮点单元,支持浮点运算 和数字信号处理。

外设接口丰富

可扩展性

K60芯片集成了多种外设接口,如UART、 SPI、I2C等,方便开发者进行硬件连接和 通信。

K60芯片支持多种外设扩展,可以根据不同 的应用需求进行功能扩展。

02 K60开发环境搭建

开发环境概述

嵌入式系统开发环境

用于编写、编译、调试嵌入式系统程序的环境。

飞思卡尔官方网站和开发者社区提供了丰富的教程资源,从入门到进阶,涵盖 了K60微控制器的各种应用场景和开发技巧。

参与开源项目

开源项目

参与开源项目是学习K60的一种有效 方式,可以了解其他开发者是如何使 用K60进行开发的,并从中获取灵感 和学习经验。

贡献社区

通过参与开源项目,不仅可以学习到 其他人的开发经验,还可以将自己的 经验和技巧分享给社区,与其他开发 者共同进步。

电平;在读操作时,可以读取引脚的电平状态。

中断编程

中断概述

中断是一种常见的硬件机制,用于处理紧急事件或异常情况。在微控制器中,中断可以由 外部事件或内部事件触发,打断当前正在执行的程序,转而执行相应的中断处理程序。

中断配置

配置中断的触发方式、优先级和中断处理程序。在飞思卡尔K60微控制器中,可以通过编 程配置中断的属性。

连接调试接口

将调试器正确连接到K60开发板的调试接口上, 确保物理连接稳定。

ABCD

驱动安装

根据调试器型号,安装相应的驱动程序,以便于 与开发环境进行通信。

配置调试参数

在开发环境或调试软件中设置调试参数,如波特 率、数据位、停止位等,确保通信正常。

系统烧写

准备烧写文件

根据K60的硬件配置和开发 需求,准备相应的系统烧写

K60(Rev6-Ch53-I2S)(中文)

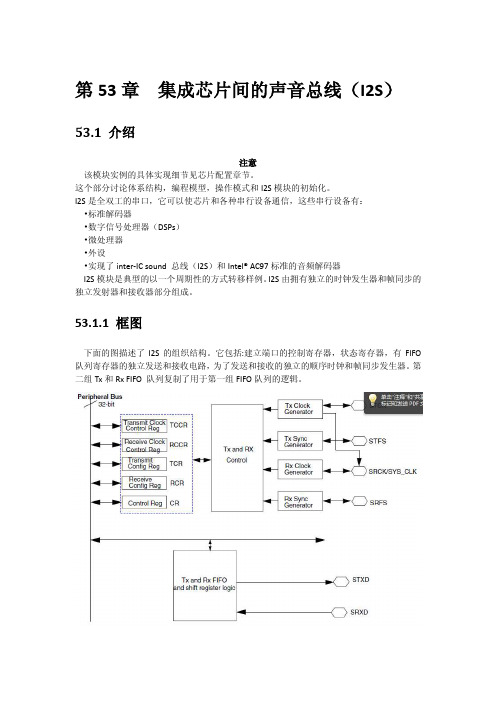

下面的图描述了 I2S 的组织结构。它包括:建立端口的控制寄存器,状态寄存器,有 FIFO 队列寄存器的独立发送和接收电路,为了发送和接收的独立的顺序时钟和帧同步发生器。第 二组 Tx 和 Rx FIFO 队列复制了用于第一组 FIFO 队列的逻辑。

图 53-1 面向用户的 I2S 框图

列可以用于网络模式从而为发送和接收提供两个独立的通道 •可编程数据接口模式,例如 I2S, lsb- and msb-aligned •可编程单词长度(8, 10, 12, 16, 18, 20, 22 or 24 位) •用于帧同步和时钟发生器的编程选项 •可编程的 I2S 模式(主,从,正常) •在 I2S 的主模式下过采样时钟作为 SRCK 的输出 •AC97 支持 •用于发送和接收部分的完全独立的时钟和帧同步选择。在 AC97 标准中时钟来自外部

53.1.2 特性

I2S 包含以下特性: •有独立或共享的内/外部时钟和帧同步的独立(异步)或共享(同步)的发送和接收部

分,在主或从模式下工作。 •使用帧同步的正常操作模式 •允许多个设备共享端口多大三十二个时段的网络操作模式 •无需同步帧的门控时钟操作模式 •两组 FIFO 发送和接收队列。四组 FIFO 队列中每组都是 15x32 位。两组 Tx/Rx FIFO 队

寄存器位的详细信息和字段功能以位顺序紧跟寄存器图表。

I2S 内存映射

绝 对 地 址 寄存器名

宽 度 访 问 复位值

段/页

(hex)

(位) 权限

4002_F000 I2S 发送数据寄存器 0(I2S0_TX0) 32

R/W 0000_0000h 53.3.1/

1693

4002_F004 I2S 发送数据寄存器 1(I2S0_TX1) 32

红米K60,同价位最优化配置,是否能焊门?

红米K60,同价位最优化配置,是否能焊门?红米K60搭载的处理器是骁龙8+Ge处理器,安兔兔跑分达到了1078956,在20轮WildLifeStressTest的压力测试下,红米K60的稳定性取得了99.2%的成绩,这应该要归功于手机内部进行了VC散热堆料。

在玩《原神》游戏时,在最高画质模式、25℃的室内环境下,游玩30分钟,平均帧率为59.32帧,整体游戏过程基本能稳定在60帧左右。

正面的最高温度为39.6℃,背面的最高温度为42.6℃。

红米K60采用小米和华星光电联合研发的国产2K柔性屏,由华星光电C6材质打造,整体参数非常的顶,526PPI、1400nit峰值亮度、12bit色深和1920HzPWM调光都是顶尖水平,3200×1440分辨率,支持120Hz刷新率、480Hz触控采样率,局部峰值亮度为1400尼特,而且还支持1920Hz的高频PWM调光,所以屏幕显示素质还是相当过硬的。

红米K60前置1600万像素美颜自拍摄像头,采用豪威OV16A1Q 传感器,后置6400万像素主摄+800万像素超广角+200万像素的微距三摄,红米K60却颠覆了人们的想象,直接用上了6400万像素的全球首款大光学格式的1.0微米6400万像素图像传感器——豪威OV64A。

红米K60通过自研算法、底层优化等,让相机启动、对焦、抓拍、成像,全流程加速,整个拍照过程干脆利落,非常适合抓拍。

带来画质增强、感知色彩、瞬间抓拍、智能场景优化等加持,并为用户带来“快拍相机”的影像体验。

红米K60内置5500mAh的单电芯电池,,支持67W有线快充,支持30W无线快充。

虽然30W无线快充功率不高,但是在两千元价位中很吃香,也是它的优势所在。

在细节方面,红米K60支持NFC、红外遥控,配置有X轴线性马达、1012+1016双立体声扬声器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1. 硬件最小系统引脚

K60N512VM100芯片电源类引脚,BGA封装22个,LQFP封装27个,其中BGA封装的芯片有五个引脚未使用(A10、B10、C10、M5和L5)。

芯片使用多组电源引脚分别为内部电压调节器、I/O引脚驱动、A/D转换电路等电路供电,内部电压调节器为内核和振荡器等供电。

为了电源稳定,MCU内部包含多组电源电路,同时给出多处电源引出脚,便于外接滤波电容。

为了电源平衡,MCU提供了内部相连的地的多处引出脚,供电路设计使用。

复位引脚RESET是一个专用引脚,内部含有上拉电阻。

空闲状态为高电平,低电平迫使芯片复位。

在写入器电路中,该引脚被连接到标准的10芯JTAG接口,以便写入器可以使MCU复位。

2.I/O端口资源类引脚

除去需要服务的引脚外,其它引脚可以为实际系统提供I/O服务。

芯片提供服务的引脚也可称为I/O端口资源类引脚。

MK60N512VMD100(144引脚BGA和LQFP封装)100个I/O引脚名、引脚号及功能描述。

许多引脚具有复用功能。

这些引脚在复位后,立即被配置为高阻状态,且为通用输入引脚,没有内部上拉电阻。

需要注意的是,为了避免来自浮空输入引脚额外的漏电流,应用程序中的复位初始化例程需尽快使能上拉或下拉,也可改变不常用引脚的方向为输出,以使该引脚不再浮空。

ADC、DAC和USB引脚,以下引脚是MK60N512VMD100单独列出来的。

除去需要服务的引脚外,其它引脚可以为实际系统提供I/O服务。

芯片提供服务的引脚也可称为I/O端口资源类引脚。

MK60N512VMD100(144引脚LQFP封装)的有多达100个I/O引脚。

其中A口26个,B口20个,C口20个,D口16个,E口18个,每个引脚均具有多个功能,详细情况请参见表2-表5。

表1 PTA口的26个引脚功能详述

表2 PTB口的20个引脚功能详述

表3 PTC口的20个引脚功能详述

表4 PTD口的16个引脚功能详述

表5 PTE口的18个引脚功能详述。