VHDL密码锁

四位数字密码锁的设计

EDA 课程设计报告书课题名称 四位数字密码锁的设计 姓 名学 号 院 系 专 业 指导教师年 月 日※※※※※※※※※ ※※※※ ※※※※※※※※※※※级学生EDA 课程设计设计任务及要求:(1)设计任务:本课程设计要求设计的数字密码锁密码为4位,由密码锁输入电路、码锁控制电路、密码锁处理电路、显示电路四大部分组成,将各电路组合起来,构成了一个完整的电子密码锁。

(2)设计要求:①、密码输入:每按一个数字键,就输入一个数值,且将在显示器上的最右上方显示出该数字,并将先前已经输入的数据依序左移一位。

②、数码清除:按下此键可以清除前面所有的输入值,清除成为“0000”。

③、密码修改:按下此键时将目前的数字设定成新的密码。

④、激活电锁:按下此键可将密码锁上锁,红色LED灯将闪烁一次。

⑤、解除电锁:按下此键会检查输入的密码是否正确,若绿色LED亮则表示密码正确,密码锁将解锁。

指导教师签名:年月日二、指导教师评语:指导教师签名:年月日三、成绩验收盖章年月日四位数字密码锁的设计1 设计目的随着人们生活水平的提高,如何实现家庭防盗这一问题也变的尤其的突出,传统的机械锁由于其构造简单,被撬的事件屡见不鲜,电子锁由于其保密性高,使用灵活性好,安全系数高,受到了广大用户的喜爱,电子密码锁的使用也体现了人们消费水平、保安意识和科技水平的提高,而且避免了携带甚至丢失钥匙的麻烦。

2 设计的主要内容和要求设计一个简单的数字电子密码锁,密码为 4 位。

要求具备如下功能:(1)如果输入数字键,第一个数字会从数码管的最右端开始显示,此后每按下一个数字键,数码管上的数字必须往左移动一格,以便将新的数字显示出来。

(2)本密码锁为四位密码锁,当输入的数字超过四个时,不会显示第四个以后的数字。

(3)按下密码清零键,清除所有输入的数字,清除成为“0000”,即做归零动作。

(4)按下解锁键,检查输入的密码是否正确,若解锁指示灯(绿色LED灯)闪烁一次,即表示密码正确(开锁)。

vhdl密码锁

VHDL实验报告数字密码锁专业:信息工程学号:姓名:2020年12月一、实验任务及设计要求一、安锁状态按下开关键SETUP,密码设置灯亮时,方可进行密码设置操作。

设置初始密码0~9(或二进制四位数),必要时能够改换。

再按SETUP键,密码有效。

二、开锁状态(1)按启动键(START)启动开锁程序,现在系统内部是初始状态。

(2)依次键入0~9(或二进制四位数)。

(3)按开门键(OPEN)预备开门。

假设按上述程序执行且拨号正确,那么开门指示灯A亮,假设按错密码或未按上述程序执行,那么按动开门键OPEN后,警报装置鸣叫,B灯亮。

(4)开锁处置事务完毕后,应将门关上,按SETUP键使系统从头进入安锁状态。

假设在报警状态,按SETUP键或START键不起作用,应按RESET键才能使系统进入安锁状态。

3、利用者如按错密码,可在按OPEN键之前,按RESET键从头启动开锁程序。

4、用层次化设计方式设计该电路,编写各个功能模块的程序。

5、仿真各功能模块,通过观看有关波形确认电路设计是不是正确。

6、完成电路设计后,用实验系统下载验证设计的正确性。

二、系统结构反馈信号图一系统原理图一、锁存器:用于实现设定密码(锁存器1)和输入密码锁存器2的存储。

二、比较器:用于将设定密码与输入密码相较较。

其中,CLK为外部输入的时钟信号。

假设输入密码正确,那么A灯亮;不然B灯亮。

同时比较器输出与CLK一样的信号,驱动蜂鸣器发出警报声。

3、开锁操纵器:当反馈信号下降沿来到时,开锁操纵输出低电平,用于在输入错误密码后,禁止再次安锁;当RESET脚位高电平常,开锁操纵输出高电平,打开与门,这时锁存器1使能端的转变受控于SETUP键,从头进入安锁状态。

4、LED显示:用于设定密码或输入密码的显示。

此项设计的目的是为了在下载演示时,能清楚地看到设置和输入的密码值。

二、硬件电路设计一、设密码模块设密码模块如以下图所示,包括复位键(RESET),密码设定选择键(SETUP),反馈信号(FD)和信号输出(CODE_OUT)和LED输出。

实验四 电子密码锁的设计

实验四电子密码锁的设计一、实验任务及要求设计一个通用电子密码锁,其具体功能要求如下:(1)数码输入:每按下一个数字健,就输入一个数值,并在显示器上的最右方显示出该数值,同时将先前输入的数据依序左移一个数字位置。

(2)数码清除:按下此键可清除前面所有的输入值,清除成为“0000”。

(3)密码更改:按下此键时会将目前的数字设定成新的密码。

(4)激活电锁:按下此键可将密码锁上锁。

(5)解除电锁:按下此键会检查输入的密码是否正确,密码正确即开锁。

二、设计原理1、接口设计根据系统功能,具体输入输出接口设计如图3-7-1所示。

LockKEYIN[11..0]ENLOCKCLKLED_DATA[15..0]RST图3-7-1电子密码锁输入输出接口图输入信号:CLK是1KHz的时钟信号,KEYIN[11..0]是模拟键盘输入信号,RST是清零输入信号。

输出信号:ENLOCK是上锁指示灯(点亮代表已上锁)。

LED_DATA[15..0]是密码显示输出,直接接在七段数码管上显示。

2、系统构成通用电子密码锁一般由三个部分组成:数字密码输入部分、密码锁控制部分和密码锁显示部分。

数字密码输入部分一般用键盘加防抖动电路和键盘译码电路组成。

这里结合SE-3实验箱,采用十二路开关来模拟0~9十个数字和加锁按钮、解锁按钮。

输入部分由输入译编码器组成,用四位信号来模拟十二个数字信号。

密码锁控制部分包括按键数据的缓冲存储电路,密码的清除、变更、存储、激活电锁电路,密码核对,解锁电路等。

该部分由加/解锁和密码输入两个进程组成。

密码锁显示模块由七段数码管译码器组成,将要显示的BCD码转换为数码管的七段显示码。

系统总体结构框图如图3-7-2所示。

图3-7-2电子密码器结构图3、VHDL参考程序如下:(1)密码输入电路:KEYBOARD.VHD--KEYBOARD.VHDLIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALL; ENTITYKEYBOARDISPORT(CLK:INSTD_LOGIC;KEYIN:INSTD_LOGIC_VECTOR(11DOWNTO0);DA TA_N:OUTSTD_LOGIC_VECTOR(3DOWNTO0);DA TA_F:OUTSTD_LOGIC_VECTOR(3DOWNTO0);FLAG_N:OUTSTD_LOGIC);ENDENTITYKEYBOARD; ARCHITECTUREARTOFKEYBOARDISSIGNALN,F:STD_LOGIC_VECTOR(3DOWNTO0); SIGNALFN:STD_LOGIC;BEGINDA TA_N<=N;DA TA_F<=F;FLAG_N<=FN;PROCESS(CLK,KEYIN)BEGINIFCLK'EVENTANDCLK='1'THENCASEKEYINISWHEN"100000000000"=>N<="0000";--0 WHEN"010*********"=>N<="0001";--1 WHEN"001000000000"=>N<="0010";--2 WHEN"000100000000"=>N<="0011";--3 WHEN"000010000000"=>N<="0100"; --4 WHEN"000001000000"=>N<="0101";--5 WHEN"000000100000"=>N<="0110";--6 WHEN"000000010000"=>N<="0111";--7 WHEN"000000001000"=>N<="1000";--8 WHEN"000000000100"=>N<="1001";--9 WHENOTHERS=>N<="1111";ENDCASE;ENDIF;IFCLK'EVENTANDCLK='1'THENCASEKEYINIS WHEN"000000000010"=>F<="1010";--*LOCK WHEN"000000000001"=>F<="0101";--#_UNLOCK WHENOTHERS=>F<="0000";ENDCASE;ENDIF;ENDPROCESS;FN<=NOT(N(3)ANDN(2)ANDN(1)ANDN(0)); ENDARCHITECTUREART;(2)密码锁控制电路:CTRL.VHDLIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALL; ENTITYCTRLISPORT(DATA_N:INSTD_LOGIC_VECTOR(3DOWNTO0); DA TA_F:INSTD_LOGIC_VECTOR(3DOWNTO0);FLAG_N:INSTD_LOGIC;CLK:INSTD_LOGIC;RST:INSTD_LOGIC;ENLOCK:OUTSTD_LOGIC;DA TA_BCD:OUTSTD_LOGIC_VECTOR(15DOWNTO0));ENDENTITYCTRL; ARCHITECTUREARTOFCTRLiSSIGNALACC,REG:STD_LOGIC_VECTOR(15DOWNTO0); SIGNALNC:STD_LOGIC_VECTOR(2DOWNTO0); SIGNALQA,QB:STD_LOGIC;BEGINPROCESS(FLAG_N,RST)ISBEGINIFRST='1'THENACC<="0000000000000000";NC<="000";ELSEIFFLAG_N'EVENTANDFLAG_N='1'THENIFNC<4THENACC<=ACC(11DOWNTO0)&DA TA_N;NC<=NC+1;ENDIF;ENDIF;ENDIF;ENDPROCESS;PROCESS(CLK,DATA_F,NC)ISBEGINIF(CLK'EVENTANDCLK='1')THENIFNC=4THENIF(DATA_F="1010")THENREG<=ACC;QA<='1';QB<='0';ELSIF(DATA_F="0101")THENIFREG=ACCORACC="1000100010001000"THENQA<='0';QB<='1';ENDIF;ENDIF;ENDIF;ENDIF;ENDPROCESS;ENLOCK<=QAANDNOTQB;DA TA_BCD<=ACC;ENDARCHITECTUREART;(3)总程序:LOCK.VHDLIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALL;ENTITYLOCKISPORT(CLK:INSTD_LOGIC;KEYIN:INSTD_LOGIC_VECTOR(11DOWNTO0);RST:INSTD_LOGIC;ENLOCK:OUTSTD_LOGIC;DA TA_BCD:OUTSTD_LOGIC_VECTOR(15DOWNTO0));END;ARCHITECTUREXOFLOCKISCOMPONENTKEYBOARDISPORT(CLK:INSTD_LOGIC;KEYIN:INSTD_LOGIC_VECTOR(11DOWNTO0);DA TA_N:OUTSTD_LOGIC_VECTOR(3DOWNTO0);DA TA_F:OUTSTD_LOGIC_VECTOR(3DOWNTO0);FLAG_N:OUTSTD_LOGIC);ENDCOMPONENT;COMPONENTCTRLISPORT(DATA_N:INSTD_LOGIC_VECTOR(3DOWNTO0);DA TA_F:INSTD_LOGIC_VECTOR(3DOWNTO0);FLAG_N:INSTD_LOGIC;CLK:INSTD_LOGIC;ENLOCK:OUTSTD_LOGIC;RST:INSTD_LOGIC;DA TA_BCD:OUTSTD_LOGIC_VECTOR(15DOWNTO0));ENDCOMPONENT;SIGNALDAT_N,DAT_F:STD_LOGIC_VECTOR(3DOWNTO0);SIGNALFLA_N:STD_LOGIC;BEGINU1:KEYBOARDPORTMAP(CLK,KEYIN,DAT_N,DA T_F,FLA_N);U2:CTRLPORTMAP(DAT_N,DA T_F,FLA_N,CLK,ENLOCK,RST,DATA_BCD);END;三、设计说明与建议1.用SE-3实验箱上的按键S1~SC作为输入信号,具体引脚分配建议:数字键KEYIN2~KEYIN11(36~41、45~48)、解锁键KEYIN0(34)、加锁键KEYIN1(35)、复位键(49)、时钟输入脚CLK(20)。

VHDL设计电子密码锁

( 六) 上市时间快,成本低。VHDL 语言描述快 捷,修改方 便,使 产 品 设 计 的 前 期 风 险 投 资 降 到 最 低,提高产品上市的速度,同时节省了人力。

三、电子密码锁的设计( 键盘和显示电路) 电子密码锁的设计将分成三个部分,键盘接口 电路的设计、密码锁的控制电路设计、输出七段显示 电路的设计。 ( 一) 键盘接口的设计 键盘上的每一个按键其实是一个开关电路,当 某键被按下时,该按键的接点会呈现逻辑 0 的状态, 反之,未被按下时则呈现逻辑 1 状态。扫描信号由 KY3 ~ KY0 进入键盘,变化顺序为 1110 →1101 → 1011 →0111→1110 的状态。每次扫描一排,依次的 周而复始。 若从 KX2 ~ KX0 读出皆为 1 时,代表该列没有 按键按下,则不进行按键编码的动作,反之,有按键 按下时,应将 KX2 ~ KX0 读出值送至译码电路. 且 将编码结果存储于寄存器中。 1. 时序产生电路———是用一个自由计数器来产 生各种需要的频率。 2. 键盘扫描电路———提供键盘扫描信号。 3. 弹跳消除电路———按键抖动会引起一次按键 被误读多次,为了避免这种情况的发生,该电路可以 在键闭合 稳 定 时 读 取 按 键 的 状 态,确 保 键 的 一 次 闭合。 4. 键盘译码电路———除了负责将键盘送出的数 据进行译码之外,另一任务是在译码同时,判断按下 的键盘是数字见还是功能键。 5. 键盘存储电路———因为次扫描会产生新的按 键数据,可能会覆盖前面数据,所以需要一个按键存 储电路,用移动寄存器构成。

一、引言 随着生产和科学技术的发展,复杂的逻辑系统 越来越广泛地运用于科学和工程实践当中。那么这 样一来,必然要求整个电路从设计规模和复杂程度 上有一个大幅度的提高而封装尺寸则尽量要求做到 微小化。为此,生产商必须采用少量的 IC 器件和面 积尽可能小的 PCB 板来研制高集成化的复杂系统。 但是,从设计的角度来看,以往采用的那种电原理图 的设计输入的门级描述方法却严重制约了产品的开 发能力。随着半导体技术的不断进步,现代电子产 品的复杂度也在日益加大,一个电子系统可能由数 万个中小规模通用集成电路构成,这就带来了体积 大、功耗大、可靠性差的问题,解决这一问题的有效 方法就 是 采 用 ASIC ( Application Specific Integrated Circuits) 芯片进行设计。 二、VHDL 的特点 可编程 ASIC 也称为可编程逻辑器件( Programmable Logic Device) 。可编程逻辑器件是 70 年代发 展起来的一种新型逻辑器件,当初主要用以解决数 字系统中各类存储问题,发展至今已经成为实现数 字系统的一种重要手段。可编程逻辑器件实现了设 计阶段的硬件仿真( Emulation) ,使得微电子设计实 现了早期集成和软硬件联合验证。设计者可以快速 地创建一个芯片设计的硬件模型,利用仿真软件将

14位数字密码锁两种设计方案

设计方案系统设计方案利用所学的电子技术知识和电子设计方法,设计出一个电子密码锁有以下两种基本方案可以选择:方案一:利用数字逻辑电路,运用各种门电路,计数器,触发器,锁存器,编/译码器等数字逻辑器件实现电子控制。

从而实现想要设计的电子密码锁的功能。

此方法设计简单,但硬件电路比较多,操作起来比较复杂。

方案二:使用MCS-51系列单片机为核心控制附加一些简单的外围电路,利用单片机的一个I/O端口组成4×4键盘作为输入电路,采用汇编语言编写程序来实现电子密码锁的各项功能,程序语言功能强大,调试较为简单。

具有很强的实用性。

设计方案选择综上提出的两种方案,方案一给出的采用数字逻辑电路的设计方法的好处就是设计简单,因为采用数字逻辑电路可以分成各个功能模块来设计,每个模块实现各自的一个功能。

这钟方法设计的密码锁电路大致包含:按键输入、密码核对、密码修改、开锁电路、错误提示电路等功能模块。

采用数字电路虽然设计简单但是操作繁琐,要运用很多数字逻辑器件,硬件电路复杂,而且可能会出现较多器件故障,同时难以检查和维护。

方案二提出的使用单片机为核心控制的方案,利用单片机丰富的I/O端口和灵活的编程设计,不但能实现密码锁的功能,而且控制准确性高,外围电路少硬件电路简单,方便灵活,调试简单不易出错,体积小成本低也利于现实中实现,具有较高的实际意义和实用价值。

这个设计方案的最关键的地方就在于编程,利用程序的执行来实现密码锁的基本功能,因此单片机方案还有较大活动空间,能在很大程度上扩展功能,方便对系统进行升级。

针对第一种方案:系统vhdl设计功能描述:假设设计的密码锁有7个数据输入键,分别用K1到K7表示;一个“确认键”(按一下确认键,密码锁内部就产生一个正脉冲),用CLK_AFFIRM表示;一个“重置和修改密码使能键”,用S/W 表示;一个开锁状态指示灯GREENLED;一个密码输入错误报警器REDLED.1.密码预置。

基于FPGA的电子密码锁设计

一、前言电子密码锁的使用体现了人们的消费水平、保安意识和科技水平的提高,而且避免了携带甚至丢失钥匙的麻烦。

目前设计密码锁的方法很多,例如传统的PCB板设计、用PLC设计或者单片机设计等等。

而用VHDL可以更加快速、灵活地设计出符合各种要求的密码锁,优于其他设计方法。

VHDL是一种符合IEEE标准的硬件描述语言,其最大的特点是借鉴高级程序语言的功能特性,对电路的行为与结构进行高度的抽象化、规范化的形式描述,并对设计的不同层次、不同领域的模拟验证与综合优化等处理,使设计过程延到高度自动化。

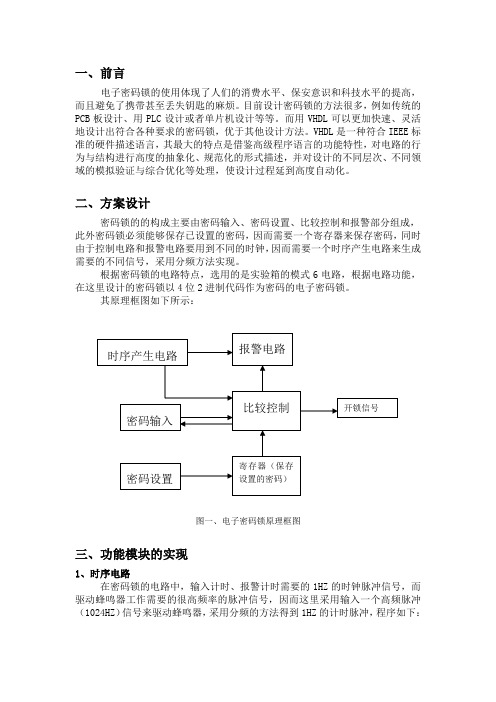

二、方案设计密码锁的的构成主要由密码输入、密码设置、比较控制和报警部分组成,此外密码锁必须能够保存已设置的密码,因而需要一个寄存器来保存密码,同时由于控制电路和报警电路要用到不同的时钟,因而需要一个时序产生电路来生成需要的不同信号,采用分频方法实现。

根据密码锁的电路特点,选用的是实验箱的模式6电路,根据电路功能,在这里设计的密码锁以4位2进制代码作为密码的电子密码锁。

其原理框图如下所示:图一、电子密码锁原理框图三、功能模块的实现1、时序电路在密码锁的电路中,输入计时、报警计时需要的1HZ的时钟脉冲信号,而驱动蜂鸣器工作需要的很高频率的脉冲信号,因而这里采用输入一个高频脉冲(1024HZ)信号来驱动蜂鸣器,采用分频的方法得到1HZ的计时脉冲,程序如下:process(clk_1k)variable cnt1:integer:=0;beginif rising_edge(clk_1k) thenif cnt1=512 thenclk_1<=not clk_1;cnt1:=0;else cnt1:=cnt1+1;end if;end if;end process;程序说明:clk_1k为输入的1024HZ高频脉冲,cnt为分频得到的1HZ计时脉冲。

2、密码设置为了安全性,密码锁必须能够重复的设定密码,在设定密码锁后,应该设置一个寄存器来存储设定的密码,程序如下:process(rst,password,enter_p) isbeginif rst='0' thenif enter_p='1' thenram<=password;en1<='1';end if;end if;end process;程序说明:rst低电平时所有的模块复位,只有密码设置模块工作;password为设置密码时的输入端,ram就是存储密码的寄存器;enter_p为在这里为密码设置使能端,高电平有效。

基于VHDL语言有限状态机的电子密码锁设计

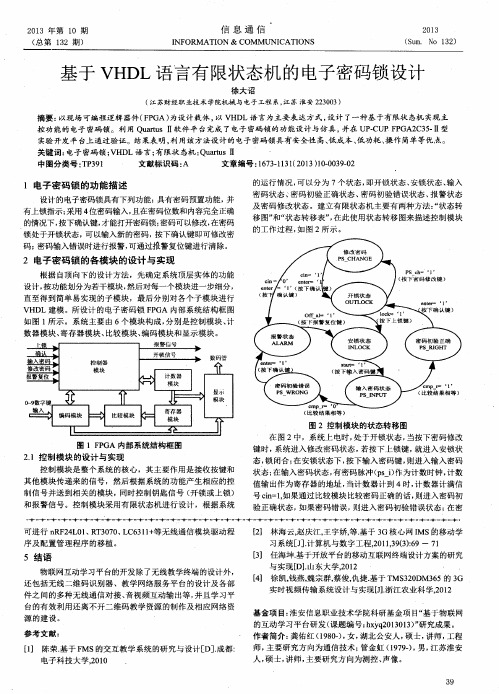

设计 , 按功能划分为若干模块, 然后对每一个模块进 一步细分, 直 至得 到简单 易实现 的子模块 ,最后分别对各个子模块进行 V HDL建模 。所设计的 电子密码锁 F P G A 内部系统结构框 图 如图 1 所示 。系统主要 由 6个模块构成 , 分别是控制模块、 计 数器模块 、 寄存器模块 、 比较模块 、 编码模块和显示模块 。

・密码脉冲 ( p s i ) 作为计数 时钟 , 计数

值 输 出作 为 寄 存 器 的地 址 , 当 计 数器 计 到 4时 , 计 数 器计 满 信 号c i n = l , 如 果 通 过 比较模 块 比较 密 码 正 确 的 话 , 则 进 入 密码 初 验正确状态 , 如果密码错误 , 则进入密码初验错误状态; 在 密

2 . 1控 制模 块 的设计 与 实现

控 制模 块是整个系统的核心,其主 要作 用是接 收按键 和 其 他模块传 递来的信 号,然后 根据 系统的功能产 生相 应的控 制 信号并送 到相 关的模块 ,同时控制钥匙信 号 ( 开锁或上锁) 和报警信号。控制模块采用有限状态机进行设计,根据系统

还包括无线二维码识别器、教学网络服务平台的设计及各部 件之间的多种无线通信对接、 音视频互动输 出等 , 并且学习平 台的有效利用还离不开二维码教学资源的制作及相应网络资

源的建设 。

[ 4 ] 徐凯, 钱燕, 魏宗群, 蔡俊 , 仇捷. 基于 T MS 3 2 0 D M3 6 5的 3 G 实时视频传输 系统 设计 与实现[ J ] . 浙江农业科学, 2 0 1 2 基金项 目: 淮安信息职业技术学院科研基 金项 目“ 基于物联网 的互动学习平 台研 发( 课题编号: h x y q 2 0 1 3 0 1 3 ) ” 研 究成果 。 作者简介: 龚佑红 ( 1 9 8 0 . ) , 女, 湖北公安人, 硕士 , 讲师 , 工程

eda课程设计数字密码锁

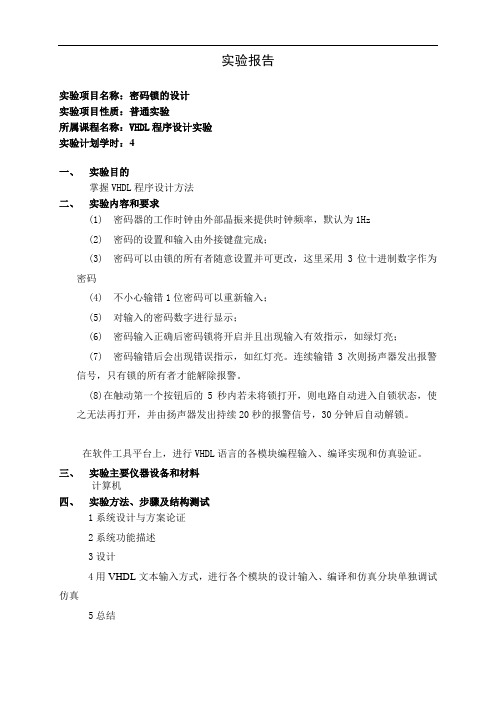

实验报告实验项目名称:密码锁的设计实验项目性质:普通实验所属课程名称:VHDL程序设计实验实验计划学时:4一、实验目的掌握VHDL程序设计方法二、实验内容和要求(1) 密码器的工作时钟由外部晶振来提供时钟频率,默认为1Hz(2) 密码的设置和输入由外接键盘完成;(3) 密码可以由锁的所有者随意设置并可更改,这里采用3位十进制数字作为密码(4) 不小心输错1位密码可以重新输入;(5) 对输入的密码数字进行显示;(6) 密码输入正确后密码锁将开启并且出现输入有效指示,如绿灯亮;(7) 密码输错后会出现错误指示,如红灯亮。

连续输错3次则扬声器发出报警信号,只有锁的所有者才能解除报警。

(8)在触动第一个按钮后的5秒内若未将锁打开,则电路自动进入自锁状态,使之无法再打开,并由扬声器发出持续20秒的报警信号,30分钟后自动解锁。

在软件工具平台上,进行VHDL语言的各模块编程输入、编译实现和仿真验证。

三、实验主要仪器设备和材料计算机四、实验方法、步骤及结构测试1系统设计与方案论证2系统功能描述3设计4用VHDL文本输入方式,进行各个模块的设计输入、编译和仿真分块单独调试仿真5总结一.设计1系统设计根据系统的设计要求,系统设计采用自顶向下的设计方法。

顶层设计采用原理图的设计方式和系统的整体组装,分别由控制模块、寄存器模块、比较器模块等部分组成。

即按照这三个组成模块定义相应的芯片引脚和输入输出的参数。

2模块功能系统主要由3个模块组成,分别是控制模块、寄存器模块、比较器模块。

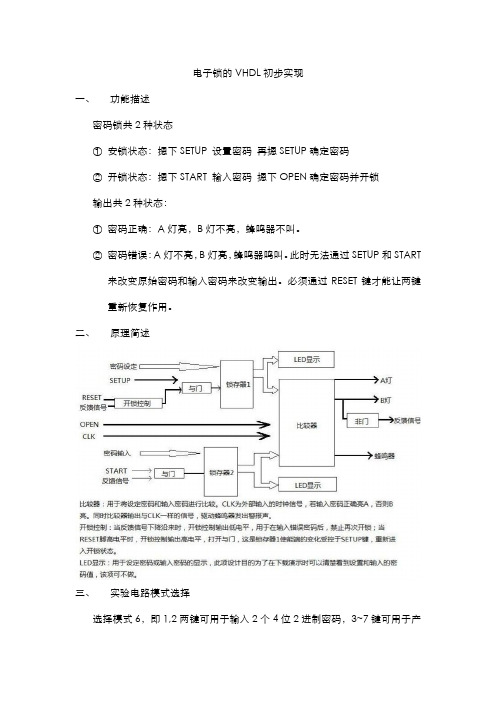

2.1 控制模块控制模块采用有限状态机设计,将系统分为7个状态,即开锁状态(outlock)、安锁状态(inlock)、输入密码状态(input)、密码初验正确状态(right)、密码初验错误状态(wrong)、报警状态(alarm)、修改密码状态(change)。

状态转移图如图2-2-1。

图2-2-1 状态转移图系统上电时,处于开锁状态,当输入修改密码xiu信号时,系统进入修改密码状态;若输入安锁lock信号,系统进入安锁状态,锁闭合:在安锁状态,输入输入密码start 信号,系统进入输入密码状态;在输入密码状态,如输入密码内容和长度均正确,进入密码初验正确状态,如果密码错误,进入密码初验错误状态;在密码初验正确状态,输入确认信号enter时,进入开锁状态,在开锁状态kai信号等于‘1’;在密码初验错误状态,输入确认信号enter时,进入报警状态;在报警状态。

密码锁的VHDL初步实现

电子锁的VHDL初步实现一、功能描述密码锁共2种状态①安锁状态:摁下SETUP 设置密码再摁SETUP确定密码②开锁状态:摁下START 输入密码摁下OPEN确定密码并开锁输出共2种状态:①密码正确:A灯亮,B灯不亮,蜂鸣器不叫。

②密码错误:A灯不亮,B灯亮,蜂鸣器鸣叫。

此时无法通过SETUP和START来改变原始密码和输入密码来改变输出。

必须通过RESET键才能让两键重新恢复作用。

二、原理简述三、实验电路模式选择选择模式6,即1,2两键可用于输入2个4位2进制密码,3~7键可用于产生持续的高电平或低电平,分别设置为SETUP,START,OPEN和RESET四个键,即VHDL硬件描述中使用高电平有效来驱动。

7段LED管7,8用于显示对应2,1两键的十六进制输入值。

LED灯1和2用于表示LEDA和LEDB。

四、源代码及设计思路顶层文件结构图:①开锁控制模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CTRL ISPORT(KEY_IN,FD_IN:IN STD_LOGIC;OUTPUT: OUT STD_LOGIC);END CTRL;ARCHITECTURE BEHAV OF CTRL ISBEGINPROCESS(KEY_IN,FD_IN)VARIABLE OUT_TEMP: STD_LOGIC;BEGINIF KEY_IN = '1' THEN OUT_TEMP := '1';ELSE OUT_TEMP := FD_IN;END IF;OUTPUT <= OUT_TEMP;END PROCESS;END BEHAV;模块设计思路:当RESET键置高电平时,应当输出高电平;当RESET键为低电平时,输出取决于反馈信号输入FD_IN的值。

此设计中默认高电平1为LED亮,又反馈信号为LED信号取反,可知有效的反馈信号应为FD_IN =’0’,并且此时应当锁死与门,故输出为0。

VHDL密码锁(6位串行输入).doc

VHDL密码锁(6位串行输入)《电子设计自动化》课程设计题目:数字密码锁电路(1.1)院(系)信息科学与工程学院专业 15通信工程届别班级学号姓名任课老师数字密码锁电路,难度系数1.1实验要求设计一个密码锁,有6位十进制数字密码,串行输入;能设置密码;有开锁和错误指示(LED);如果连续输错三次,则一刻钟内不能再开锁。

本设计的各个模块由相应的VHDL程序具体实现,并在Quartus Ⅱ9.0环境下进行了整体电路的模拟仿真,最终实现“密码锁设计”的要求。

实验设计要求6位串行输入,并且由于实验板输入键位的有限,还同时增加了输入密码与设置密码键位的重叠,使密码锁电路输入输出形成一个反馈,通过对输出的判断,让电路自动识别输入的数字是设置的密码还是输入的密码。

在程序初始载入实验板时,还要让密码锁的初始设置密码和输入密码相同,从而达到能够初始设置密码的逻辑要求。

同时因为实验板输出的LED灯有限,还要求设计的密码锁电路的显示能够在输入密码、设置密码和倒计时之间灵活智能选择,从而达到满足使用的要求。

密码锁在输入三次错误密码后需要开始一个一刻钟即900秒的倒计时,则需要设计一个逻辑电路使电路能够在输入和错误倒计时之间自由变化。

此为本实验设计的主要难点和创新。

目录1.系统设计 (4)2.单元电路设计 (7)3.软件设计 (12)4.系统测试 (23)5.结论 (24)6.参考文献 (24)7.附录 (25)8.其他 (26)系统设计设计要求:设计一个密码锁,有6位十进制数字密码,串行输入;能设置密码;有开锁和错误指示(LED);如果连续输错三次,则一刻钟内不能再开锁。

系统设计方案:先设计1.0难度的密码锁,此时不需要一刻钟计时模块。

该电路首先需要一个输入模块,由于实验板的限制,安排两个键位作为输入,分别实现6个密码位的选择和对确定位密码的输入,所以在输入模块之前,还需要通过计数器来分别得到两个输入;之后设计一个密码合成及选择模块,将得到的6个4位的密码相加得到一个24位的密码,方便之后的比较,同时需要在输入模块添加一个选择,分别确定此时的输入信息是设置密码还是输入密码;将得到的24位设置密码和输入密码分别放到一个确认模块,起到输入确认并且使初始信息清零的作用;最后将两个24位数据放入比较模块,确定密码锁的状态,状态的显示由LED灯实现;输出显示LED模块从输入模块之前接出,显示当前电路的输入;同时,在计数器之前需要加入消抖模块,使实验板能够稳定输入;在LED模块之前需要添加译码器,以输出正确显示。

VHDL电子密码锁

设计一个6位并行(或串行)电子密码锁,要求当输入的密码与锁内的密码一致时,,绿灯亮,开锁;当输入的密码与锁内的密码不一致时,红灯亮,不能开锁。

密码可由用户自行设置。

设计要求:1分析设计任务,拟定多种设计方案,根据实验条件,选定其中一种方案绘制系统框图和设计流程。

2设计相关电路并编写VHDL程序。

3对设计电路进行功能仿真,分析仿真波形。

4对设计电路要进行编程下载,记录结果。

5撰写设计报告一份。

设计方案(1)采用文本输入法,用一个源程序控制整个电路,然后利用顶层文件将它们综合起来,最终使其具有电子密码锁的功能。

(2)采用文本和原理图两种方法设计,密码锁的主体部分(包括密码设置、密码修改、密码检测、开锁电路、执行电路等部分。

)用文本设计法完成,当主体部分完成后,将其打包后,再用原理图输入法使各个部分综合起来。

由以上两种方案分析,方案(1)全部采用文本输入法,在顶层设计中比较杂,一旦出现错误,将不易更改,程序调试耗时会比较长。

方案(2)采用了文本和原理图两种方法进行设计,主体部分完成后,再用另一种方法设计译码部分,最后两部分综合,调试起来会比较方便。

综合以上原因,从实现难易,误差大小以及最终结果等各方面考虑,选择方案(2)来完成该实验。

根据方案(2)中密码锁的实现原理,本次设计方案可分为三个模块来实现其功能,即消抖电路、消抖同步电路、核心电路几个单元,在核心电路中又包括密码设置电路、密码输入电路、密码锁控制电路和密码锁显示电路四部分组成。

控制部分还需包含密码修改、密码检测、开锁电路、执行电路等部分。

分别用VHDL对其进行编程,实现消抖电路、消抖同步电路、核心电路等。

然后对其打包后,利用原理图输入法使各个部分综合起来。

系统结构消除抖动模块Library ieee;Use ieee.std_logic_1164.all; Entity fen isPort(clk:in std_logic;Cp :out std_logic);End fen;Architecture fen_arc of fen is BeginProcess(clk)Variable cnt:integer range 0 to 999; BeginIf clk'event and clk='1'thenIf cnt=9 thenCnt:=0;Cp<='1';ElseCnt:=cnt+1;Cp<='0';End if;End if;End process;End fen_arc;消抖同步模块library ieee;use ieee.std_logic_1164.all;entity xiaopro isport(a,clk2:in std_logic;b:out std_logic);end xiaopro;architecture xiao_arc of xiaopro is signal tmp1:std_logic;beginprocess(clk2,a)variable tmp3,tmp2:std_logic;beginif clk2'event and clk2='0'thentmp1<=a;tmp2:=tmp1;tmp3:=not tmp2;end if;b<=tmp1 and tmp3 and clk2;end process;end xiao_arc;逻辑功能模块Library ieee;Use ieee.std_logic_1164.all;Entity cornaa2 isPort(clk,k1,k0,clr,load:in std_logic;lt:inout std_logic;lamp:out std_logic_vector(5 downto 0);lf,alm:out std_logic);end cornaa2;architecture corn_arc of cornaa2 issignal shift,lock:std_logic_vector(5 downto 0); signal lam:std_logic_vector(5 downto 0); signal la:std_logic;beginprocess(clk,clr)beginIf clr='0'thenla<='0';elsif clk'event and clk='1' thenif load='0' thenla<='1';end if;end if;end process;process(clk,clr)variable a:integer range 0 to 6;beginIf clr='0' thenlam<="111111";Shift<="000000";a:=0;lt<='1';lf<='1';alm<='0';Elsif clk'event and clk='1'thenif la='1' thenif k1='0'thenlock<='1'&lock(5 downto 1);lam<='0'&lam(5 downto 1);elsif k0='0'thenlock<='0'&lock(5 downto 1);Lam<='0'&lam(5 downto 1);end if;elsif lt='1' thenif a/=6 thenif k1='0' thenShift<='1'&shift(5 downto 1);lam<='0'&lam(5 downto 1);a:=a+1;elsif k0='0' thenShift<='0'&shift(5 downto 1);lam<='0'&lam(5 downto 1);a:=a+1;end if;elsea:=0;if shift=lock thenlt<='0';elself<='0';alm<='1';end if;end if;end if;end if;end process;lamp<=lam;end corn_arc;密码锁的原理图。

VHDL专题—电子密码锁

VHDL专题--------电子密码锁一、设计要求:设计一个简单的数字电子密码锁,密码为4位。

功能:1、密码输入:每按下一个键,要求在数码管上显示,并依次左移;2、密码清除:清除密码输入,并将输入置为”0000”;3、密码修改:将当前输入设为新的密码;4、上锁和开锁。

二、电路组成:为达到以上功能,可将电子密码锁分为以下几个模块:1、键盘接口电路:键盘矩阵、键盘扫描、键盘消抖、键盘译码及按键存储。

2、电锁控制电路:数字按键输入、存储及清除。

功能按键的设计。

密码清除、修改与存储。

电锁的激活与解除。

3、输出显示电路BCD译码、动态扫描电路。

三、功能电路的设计:1、键盘接口电路:矩阵式键盘工作原理:矩阵式键盘是一种常见的输入装置,在计算机、电话、手机、微波炉等各工电子产品中被广泛应用。

如图所示为一3×4矩阵式键盘。

矩阵式键盘以行、列形式排列,图中为4行3列,键盘上的每一个按键盘其实是一个开关电路,当某键被按下时,该按键所对应的位置就呈现逻辑0的状态,键盘的扫描可以以行扫或列扫方式进行,图中为行扫方式,KEYR3—KEYR0为扫描信号,其中的某一位为0即扫描其中的一行,具体见表1-1.12键盘扫描信号KEYR3与第一行相连,KEYR2与第二行相连,依此类推。

很显然,扫描信号的变化顺序为:0111、1011、1101、1110,周而复始。

在扫描的过程中,当有键按下时,对应的键位就为逻辑0状态,从而从KEYC2..0读出的键值相应列为0.具体情况如表1-2所示:若从KEYC2..0读出的值全为1时,表示没有键被按下,则不进行按键的处理。

如果的键被按下,则将KEYC2..0读出的送至键盘译码电路进行译码。

表1-2 键盘扫描与其对应的键值的关系时序产生电路:在一个系统的设计中,往往需要多种时钟信号,最为方便的方法是利用一个自由计数器来产生各种需要的频率。

本电路需要:系统主时钟、消抖取样时钟和动态扫描时钟。

基于VHDL4位电子密码锁的设计

理工大学本科实验报告题目:基于VHDL 4位电子密码锁的设计课程名称:数字电路课程设计学院(系):电子信息与电气工程专业:电子英强班级:学生:学号:完成日期:2013.7.8成绩:2013 年7 月08 日题目:基于VHDL 4位电子密码锁的设计1 设计要求○1电子密码锁为4位8421BCD码,多于4位,密码只取前4位。

○2在输入密码错误,给出一个错误信号,有三次输入机会,若三次密码都输入错误,则给出一个报警信号,此后只能由密码管理员取消报警信号。

○3在输入密码正确的情况下,可以再次设定密码。

○4每次输入一个密码,将显示在7段数码管上,并依次左移。

○5每次输入密码的时候,按取消(cancel)键可以取消这次密码的输入,课重新输入4位密码。

2 设计分析及系统方案设计在实验室DE2开发板的条件下,考虑到key键只有4个,可以用switch开关来实现密码输入模块,用switch[9]~switch[0] 来实现数字9~0的输入,并通过译码模块将其转化为8421BCD码,由8421BCD码来驱动7段数码管作为密码锁的显示模块。

每按一个键,产生一个上升沿,给4个数码管做时钟,实现没输入一个数左移一位的效果。

为了实现密码输入多于4位,可以构造一个模为4的计数器来控制只取前4位密码。

共有三次输入密码的机会,可以构造一个模为3的计数器来控制。

密码比较模块:当按下确定键(yes)键,则将输入的密码和置密码进行比较。

密码输入模块:当输入密码正确时,再输入密码,利用重置密码键(set_psw)直接将其赋值给置的密码psw即可实现。

LED 显示模块,用来显示密码输入的正确与否。

若输入密码与置密码一致,则锁打开,输出一个高电平给LEDG ,绿灯亮,密码错误则输出一个高电平给LEDR ,红灯亮。

综合上述分析,本系统的硬件部分主要由密码锁输入译码模块、密码锁显示模块、密码锁控制模块、密码比较和重置模块和LED 显示模块五个部分组成。

vhdl密码锁

vhdl密码锁密码锁设计⼀、课题描述:⽤于模仿密码锁的⼯作过程。

完成密码锁的核⼼控制功能。

⼆、功能要求:设计⼀个密码锁,平时处于等待状态。

管理员可以设置或更该密码。

如果不预置密码,密码缺省为“999999”。

⽤户如果需要开锁,按相应的按键进⼊输⼊密码状态,输⼊6位密码,按下确定键后,若密码正确,锁打开,若密码错误,将提⽰密码错误,要求重新输⼊,三次输⼊都错误,将发出报警信号。

报警后,只有管理员作相应的处理才能停⽌报警。

⽤户输⼊密码时,若输⼊错误,在按下确定键之前,可以通过按取消键重新输⼊。

正确开锁后,⽤户处理完毕后,按下确定键,系统回到等待状态。

系统操作过程中,只要密码锁没有打开,如果60秒没有对系统操作,系统回到等待状态。

注意:输⼊按键信号时必须⼀个按键⼀个按键输⼊,不得6个按键⼀起输⼊。

三、设计流程:1.结构框图:①按键输⼊;②复位(设置缺省密码);③等待状态④⼯作状态⑤修改密码⑥提醒错误及报警⑦开锁⑧恢复等待2.模块设计:★控制模块:实现输⼊输出,实现等待⼯作的转换,实现开锁及报警;★⽐较模块:⽐较输⼊密码与正确密码★寄存模块:存放密码★计数及使能模块:(1)输⼊个数为6,多于⽆效⾃动忽略;(2)60s的空闲时间,⽆操作返回等待;(3)错误次数为3(4)进⼊⼯作状态,是能段即打开,直到进⼊等待。

四、具体实现:★控制模块:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity ctrl isport( change,vers,keysign : in std_logic;ok,cancel : in std_logic;clk : in std_logic;result : in std_logic;wt : in std_logic;enable : out std_logic);end ctrl;architecture ctrl_behave of ctrl issignal sec : integer range 0 to 60;beginprocess(clk)beginenable<='1';end if;if (wt='1' and result='1') thenenable<='0';sec<=0;end if;if (change='0' and vers='0' and keysign='0' and ok='0' and cancel='0') then sec<=sec+1; if (sec=59) thenenable<='0';sec<=0;end if;elsesec<=0;end if;end if;end process;end ctrl_behave;★⽐较模块:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity ver isport( dt1,dt2,dt3,dt4,dt5,dt6 : in std_logic_vector(3 downto 0); cd1,cd2,cd3,cd4,cd5,cd6 : in std_logic_vector(3 downto 0); vers : in std_logic;ready : in std_logic;clk : in std_logic;stopalarm : in std_logic;en : in std_logic;result : out std_logic;wrong : out std_logic;alarm : out std_logic);end ver;architecture ver_behave of ver issignal alarmnum : integer range 0 to 3;signal vering : std_logic;signal wronging : std_logic;beginprocess(clk)beginif (en='0') thenresult<='0';end if;if (stopalarm='1') thenalarmnum<=0;end if;if (wronging='1') thenwronging<='0';vering<='1';end if;if (alarmnum<3) thenalarm<='0';elsealarm<='1';end if;if (vers='1') thenvering<='1';end if;if (vering='1') thenif (ready='1') thenif (cd1=dt1 and cd2=dt2 and cd3=dt3 and cd4=dt4 and cd5=dt5 and cd6=dt6) then result<='1';elseresult<='0';wronging<='1';if (alarmnum<3) thenalarmnum<=alarmnum+1;end if;end if;vering<='0';end if;end if;elsif (clk'event and clk='0') thenif (wronging='1') thenwrong<='1';elsif (wronging='0') thenwrong<='0';end if;end if;end process;end ver_behave;★寄存模块:library ieee;entity code isport( dt1,dt2,dt3,dt4,dt5,dt6 : in std_logic_vector(3 downto 0);change : in std_logic;ready : in std_logic;ok : in std_logic;clk : in std_logic;result : in std_logic;reset : in std_logic;wt : out std_logic;cd1,cd2,cd3,cd4,cd5,cd6 : out std_logic_vector(3 downto 0) ); end code;architecture code_behave of code issignal alarmnum : integer range 0 to 3;signal changing : std_logic;signal changed : std_logic;signal wting : std_logic;beginprocess(clk)beginif (clk'event and clk='1') thenif (ok='1' and changing='0' and result='1') thenwting<='1';elsewting<='0';end if;if (reset='1') thencd1<="1001";cd2<="1001";cd3<="1001";cd4<="1001";cd5<="1001";cd6<="1001";end if;if (change='1') thenchanging<='1';end if;if (changing='1') thenif (ready='1') thenif (result='1') thencd1<=dt1;cd2<=dt2;end if;changing<='0';end if;end if;elsif (clk'event and clk='0') thenif (wting='1') thenwt<='1';elsewt<='0';end if;end if;end process;end code_behave;★计数及使能模块:1library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity keyboard isport( a3,a2,a1,a0 : in std_logic;a : out std_logic_vector(3 downto 0);k : in std_logic;keysign : out std_logic;clk : in std_logic);end keyboard;architecture keyboard_behave of keyboard is beginprocess(clk)beginif (clk'event and clk='0') thena(0)<=a0;keysign<=k;end if;end process;end keyboard_behave;2library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity keyin isport( en : in std_logic;clk : in std_logic;a : in std_logic_vector(3 downto 0);keysign : in std_logic;ok : in std_logic;cancel : in std_logic;ver : in std_logic;ready : out std_logic;dt1,dt2,dt3,dt4,dt5,dt6 : out std_logic_vector(3 downto 0) ); end keyin;architecture keyin_behave of keyin issignal count : integer range 0 to 7;signal cready : std_logic;beginprocess(en,clk,keysign)beginif (en='1') thenif (clk'event and clk='1') thenif (keysign='1' and count<6) thencount<=count+1;if (count=0) thenelsif (count=1) thendt2<=a;elsif (count=2) thendt3<=a;elsif (count=3) thendt4<=a;elsif (count=4) thendt5<=a;elsif (count=5) thendt6<=a;end if;end if;if (ver='1') thencount<=0;end if;if (cancel='1') thendt2<="1111";dt3<="1111";dt4<="1111";dt5<="1111";dt6<="1111";end if;if (ok='1') thencount<=0;cready<='1';elsecready<='0';end if;elsif (clk'event and clk='0') then if (cready='1') thenready<='1';elseready<='0';end if;end if;end process;end keyin_behave;‘※各个模块与设计存在出⼊,但基本要求都达到,主要是⼩组分⼯时,没有能完全按照模块分块设计※计数器模块分散开没有单独形成模块※具体信号意义见仿真Block图:五、仿真:Reset:重置(缺省)A:输⼊k:判断有效输⼊OK:确认Cancel:取消Ver:进⼊⼯作(⽐较)Change:修改密码Clk:时钟信号Result:开锁En-out:使能Wrong:报错Alarm:报警Stopalarm:停⽌操作(管理员使⽤)1.验证缺省密码为999999(reset键);2.验证输⼊错误取消输⼊,重新输⼊(cancel键);3.验证60秒⽆操作⾃动返回等待界⾯(en-out和result归零);4.验证有效按键“k”,只有k为⾼电平有效;5.验证⽤户操作完成,再次按ok键,⾃动返回等待键;6.验证输⼊密码错误发出提⽰信号,连续三次输⼊错误,发出报警信号,只有按下stopalarm才能停⽌。

EDA课程设计(基于VHDL语言的8位数字密码锁设计)

东华理工大学机械与电子工程学院基于VHDL语言的8位数字密码锁设计一、摘要:数字控制的电子密码锁已经广泛应用在办公室、公司、宾馆、小区住宅等场所。

EDA技术的应用引起了电子产品系统开发的革命性变革。

利用先进的EDA工具,基于硬件描述语言,可以进行系统级数字逻辑电路的设计。

本文简述了VHDL语言的功能及其特点,并以8位串行数字锁设计为例,介绍了在QUARTUS II 6.0开发软件下,利用VHDL硬件描述语言设计数字逻辑电路的过程和方法。

关键词: QUARTUS II 6.0 EDA 电子密码锁(电子设计自动化) VHDL语言语言设计串行密码锁硬件描述语言数字逻辑电路Based on VHDL language 8 digits combination lock design Digital control of electronic locks has widely used in office, companies, hotels, residential area and etc.EDA technology application caused a electronic product development system of the revolutionary transformation. Using advanced EDA tools, hardware based description language, can undertake system in digital logic circuit design. This paper describes the function and characteristics of VHDL language, and eight serial number lock design as an example, this paper introduces QUARTUS II 6.0 software development in of VHDLhardware design of digital logic circuit process and method.Keywords: QUARTUS II 6.0, EDA (electronic design automation), electronic locks and VHDL language, language design, serial, locks and hardware description language, digital logic circuit二、引言:电子密码锁系统主要由电子锁体、电子密匙等部分组成,一把电子密匙里能存放多组开锁密码,用户在使用过程中能够随时修改开锁密码,更新或配制钥匙里开锁密码。

VHDL数字密码锁课程设计

VHDL数字密码锁课程设计一、课程目标知识目标:1. 学生能理解VHDL语言的基本语法和程序结构,掌握数字密码锁的基本原理。

2. 学生能运用VHDL语言编写与数字密码锁相关的程序代码,实现基本功能。

3. 学生了解数字密码锁在实际工程中的应用,理解其重要性。

技能目标:1. 学生能运用所学知识,设计并实现一个简单的数字密码锁系统。

2. 学生通过实际操作,提高编程能力,培养解决实际问题的能力。

3. 学生能通过小组合作,提高团队协作和沟通能力。

情感态度价值观目标:1. 学生培养对电子设计及其编程的兴趣,激发创新意识。

2. 学生认识到科技发展对社会的重要性,增强社会责任感。

3. 学生在团队合作中,学会尊重他人,培养良好的沟通和协作精神。

课程性质:本课程为实践性课程,以培养学生的动手能力和实际编程技能为主。

学生特点:学生具备一定的电子基础和编程能力,对新鲜事物充满好奇心。

教学要求:教师需引导学生将理论知识与实际应用相结合,注重培养学生的实践能力和团队合作精神。

在教学过程中,将目标分解为具体的学习成果,以便于教学设计和评估。

二、教学内容1. 数字密码锁原理介绍:包括密码锁的工作机制、安全性分析等。

相关教材章节:第五章“数字密码锁设计原理”2. VHDL语言基础:回顾VHDL的基本语法、程序结构、数据类型和运算符等。

相关教材章节:第三章“VHDL语言基础”3. VHDL编程实践:a) 设计数字密码锁的实体和端口b) 编写行为描述和结构描述代码c) 仿真与调试相关教材章节:第四章“VHDL编程实例”和第六章“数字密码锁设计实例”4. 数字密码锁功能模块设计:a) 密码设置与修改b) 密码验证c) 锁定与解锁功能相关教材章节:第六章“数字密码锁功能模块设计”5. 数字密码锁系统集成与测试:a) 将各功能模块整合到一起,实现完整密码锁系统b) 进行系统测试,验证系统功能及性能相关教材章节:第七章“数字密码锁系统集成与测试”6. 课程项目实践:分组进行数字密码锁项目设计,培养学生的团队合作能力和实际操作技能。

(电子行业企业管理)吴超电子密码锁

一、设计思想本设计采用EDA技术和VHDL语言设计了一种按键输入密码并数码管回显,当输入正确密码时轰动绿灯亮、红灯熄灭表示开锁,而当输入错误密码时,红灯亮、绿灯熄灭表示关锁。

根据系统设计要求,系统设计采用自顶向下的设计方法。

1.基本原理在本实验中采用的是VHDL编程,通过文本编辑方式建立模块,通过原理图方式将生成的图形符号连接,然后再下载,进行硬件的仿真。

密码锁要达到的功能为:为达到密码锁的以上功能,可将电子密码锁分为以下几个模块:密码锁输入电路、密码锁控制电路、LED输出显示电路。

⑴、密码输入:每按下一个数字键,就输入一个数值,并在显示器上显示出该数值。

同时将先前输入的数据依次左移一个数字位置。

程序下载后系统进入原始状态(原始密码000000),按下键8发光二极管8(绿灯)亮、法官二极管7(红灯)灭。

当要重新设置密码时,直接输入自己想要设置的密码并按下键8,持续5S,数码管8由0变为1,此时7段数码管1、2、3、4、5、6对应显示新设置的密码。

当要输入密码时,按下键7,先将密码清零,再随机输入一组6位密码,假如密码正确,发光二极管8(绿灯)立即亮;反之如不正确,等待5S,发光二极管7(红灯)亮并由蜂鸣器发出20S的报警信号。

⑵、密码清除:按下清除键可清除前面所有的输入值,清除成为“0000”。

⑶、密码更改:按下更改键可将目前数据设定为新的密码。

⑷、密码上锁:按下上锁键可将密码锁上锁。

⑸、密码解除:按下解除键首先检查输入的密码是否正确,密码正确即解锁。

2.设计框图为达到密码锁的以上功能,可将电子密码锁分为以下几个模块:密码锁输入电路、密码锁控制电路、LED 输出显示电路。

和报警电路等四部分组成顶层设计采用原理图设计方式,系统的整体组装设计原理图如图1所示。

图1 系统整体组装设计原理图二、设计步骤和调试过程1、模块设计和相应模块代码 (1)分频由于要产生5秒、20秒的计时信号,故对系统时钟clk_1k 进行分频来得到1Hz 的时钟clk 。

基于VHDL的数字密码锁设计

河南机电高等专科学校《职业技术培训》结课大作业基于VHDL的数字密码锁设计姓名:专业班级:学号:任课教师:时间:成绩:基于VHDL的数字密码锁设计医电08级1班任课教师:摘要:本文要紧介绍运用删,技术设计数字密码锁统分解为假设干子系统,而且进一步细划为假设干模块,然后用硬件描述语言VHDL来设计这些模块,而且别离进行软件和硬的仿真。

仿真结果说明:该数字密码锁能够校验3位十进制数密码,且能够预置密码,显示输入密码,具有输入错误指示有效指示等相应的状态指示。

该密码锁体积小,功耗低,操作简单,不怕掉电,保护和升级都十分方便,具有较好的应用前景。

关键词:QUARlrIIS II;VHDL;数字密码锁目录1. 概述 ....................................................................错误!未定义书签。

2. 设计要求 ............................................................错误!未定义书签。

3. 整体设计 ............................................................错误!未定义书签。

4. 各单元电路的设计和实现 ................................错误!未定义书签。

5. 功能仿真及其结果 ............................................错误!未定义书签。

6. 编译、下载及调试 ............................................错误!未定义书签。

7. 总结与展望 ........................................................错误!未定义书签。

参考文献..................................................................错误!未定义书签。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子与信息工程学院

EDA课程设计与实现报告(2011 —2012 学年第一学期)

班级:____________

学号:_________________

姓名:_______________

指导教师: ____

2011 年9 月

测试代码及仿真图

1.输入密码打开电子锁

res <='0','1' after 10 ns,'0' after 20 ns;

user <='0';

admin <='0';

clear <='0';

chgcode <='0';

enter <='0','1' after 180 ns,'0' after 190 ns,

'1' after 250 ns,'0' after 260 ns;

key1 <='0','1' after 100 ns,'0' after 110 ns,

'1' after 120 ns,'0' after 130 ns,

'1' after 140 ns,'0' after 150 ns,

'1' after 160 ns,'0' after 170 ns;

key2 <='0';

仿真结果为:

3.clear 清除键测试代码

res <='0','1' after 10 ns,'0' after 20 ns;

user <='0';

admin <='0';

chgcode <='0';

clear <='0','1' after 140 ns,'0' after 150 ns;

enter <='0','1' after 220 ns,'0' after 230 ns;

key1 <='0','1' after 100 ns,'0' after 110 ns,

'1' after 160 ns,'0' after 170 ns,

'1' after 180 ns,'0' after 190 ns,

'1' after 200 ns,'0' after 210 ns;

key2 <='0','1' after 120 ns,'0' after 130 ns;

4.管理员修改用户密码,新密码为1010

res <='0','1' after 10 ns,'0' after 20 ns;

user <='0','1' after 240 ns,'0' after 250 ns;

admin <='0','1' after 100 ns,'0' after 110 ns;

clear <='0';

chgcode <='0','1' after 220 ns,'0' after 230 ns;

enter <='0','1' after 200 ns,'0' after 210 ns,

'1' after 340 ns,'0' after 350 ns,

'1' after 440 ns,'0' after 450 ns,

'1' after 540 ns,'0' after 550 ns,

'1' after 630 ns,'0' after 640 ns;

key1 <='0','1' after 260 ns,'0' after 270 ns,

'1' after 280 ns,'0' after 290 ns,

'1' after 300 ns,'0' after 310 ns,

'1' after 320 ns,'0' after 330 ns,

'1' after 360 ns,'0' after 370 ns,

'1' after 400 ns,'0' after 410 ns,

'1' after 460 ns,'0' after 470 ns,

'1' after 500 ns,'0' after 510 ns,

'1' after 560 ns,'0' after 570 ns,

'1' after 600 ns,'0' after 610 ns;

key2 <='0','1' after 120 ns,'0' after 130 ns,

'1' after 140 ns,'0' after 150 ns,

'1' after 160 ns,'0' after 170 ns,

'1' after 180 ns,'0' after 190 ns,

'1' after 380 ns,'0' after 390 ns,

'1' after 420 ns,'0' after 430 ns,

'1' after 480 ns,'0' after 490 ns,

'1' after 520 ns,'0' after 530 ns,

'1' after 580 ns,'0' after 590 ns,

'1' after 620 ns,'0' after 630 ns;仿真结果为:

'1' after 460 ns,'0' after 470 ns,

'1' after 480 ns,'0' after 490 ns,

'1' after 500 ns,'0' after 510 ns; 仿真结果为:。