简单cpu(CPU ASIC)

ASIC与CPU、GPU、FPGA区别?

ASIC与CPU、GPU、FPGA区别?继4月初联发科宣布扩大ASIC产品阵线,推出业内首个7nm 56G PAM4 SerDes IP之后,4月24日,在联发科深圳办公室,联发科举行了一场小型的媒体会,联发科副总经理暨智能设备事业群总经理游人杰及联发科智能显示暨客制化芯片事业部行销处处长彭建凯首次揭秘了联发科的ASIC业务。

什么是ASIC芯片?近年随着以比特币为代表的虚拟货币市场的火爆,催生了一大批生产“挖掘”虚拟货币设备的“矿机”厂商,其中最为知名的要属比特大陆了。

而比特大陆之所以能够在矿机市场异军突起,则主要得益于其自主设计的针对比特币矿机的ASIC芯片。

因为相对于CPU、GPU来说,采用专用的ASIC芯片来“挖矿”更具效率。

以比特大陆的Antminer S9矿机为例,其内部集成了189个ASIC芯片(BM1387),而且采用的是台积电16nm FinFET制程。

同样,目前主流的矿机厂商都采用的是定制的ASIC芯片。

这也使得ASIC芯片开始被大众所熟知。

但是ASIC芯片并不仅仅能被用于“挖矿”,还被用于包括人工智能在内等众多领域。

那么什么才是ASIC芯片?它与我们常见的CPU、GPU等通用型芯片相比又有何不同?早在1981年3月,Sinclair公司推出了一款8位个人电脑ZX81,其所采用的Z80处理器则被认为是最早的ASIC原型。

实际上ASIC是Application-Specific In te grated Circuit(应用型专用集成电路)的缩写,是一种专用芯片,是为了某种特定的需求而专门定制的芯片的统称。

比如专用的音频、视频处理器,同时目前很多专用的AI芯片业可以看作是ASIC 的一种。

与CPU、GPU、FPGA相比如何?CPU与GPU都是我们常见的通用型芯片,它们在各自领域都可以高效地完成任务,但当同样应用于通用基础计算领域时,设计架构的差异直接导致了两种芯片性能的差异。

CPU作为通用处理器,除了满足计算要求,为了更好的响应人机交互的应用,它要能处理复杂的条件和分支,以及任务之间的同步协调,所以芯片上需要很多空间来进行分支预测与优化(control),保存各种状态(cache)以降低任务切换时的延时。

CPU和异构计算芯片GPU-FPGA-ASIC基础教程

CPU 和异构计算芯片GPU/FPGA/ASIC 基础教程

随着互联网用户的快速增长,数据体量的急剧膨胀,数据中心对计算的需求也在迅猛上涨。

诸如深度学习在线预测、直播中的视频转码、图片压缩解压缩以及HTTPS 加密等各类应用对计算的需求已远远超出了传统CPU 处理器的能力所及。

摩尔定律失效的今天,关注新成员(GPU\FPGA\ASIC)为数据中心带来的体系架构变革,为业务配上一台动力十足的发动机。

1 异构计算:WHY

明明CPU 用的好好的,为什幺我们要考虑异构计算芯片呢?

随着互联网用户的快速增长,数据体量的急剧膨胀,数据中心对计算的需求也在迅猛上涨。

诸如深度学习在线预测、直播中的视频转码、图片压缩解压缩以及HTTPS 加密等各类应用对计算的需求已远远超出了传统CPU 处理器的能力所及。

历史上,受益于半导体技术的持续演进,计算机体系结构的吞吐量和系统性能不断提高,处理器的性能每18 个月就能翻倍(众所周知的摩尔定律),使得处理器的性能可以满足应用软件的需求。

但是,近几年半导体技术改进。

ASIC、NP、X86、RISC、DSP 、ARM、单片机几种常见技术介绍

RISC微处理器不仅精简了指令系统,采用超标量和超流水线结构;它们的指令数目只有几十条,却大大增强了并行处理能力。如:1987年Sun

Microsystem公司推出的SPARC芯片就是一种超标量结构的RISC处理器。而SGI公司推出的MIPS处理器则采用超流水线结构,这些RISC处理器在构建并行精简指令系统多处理机中起着核心的作用。

(2)程序和数据空间分开,可以同时访问指令和数据;

(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问;

(4)具有低开销或无开销循环及跳转的硬件支持;

(5)快速的中断处理和硬件I/O支持;

● 分级存储器组织: NP存储器一般包含多种不同性能的存储结构,对数据进行分类存储以适应不同的应用目的。

● 高速I/O接口:

NP具有丰富的高速I/O接口,包括物理链路接口、交换接口、存储器接口、PCI总线接口等。通过内部高速总线连接在一起,提供很强的硬件并行处理能力。

现代ASIC常包含整个32-bit处理器,类似ROM、RAM、EEPROM、Flash的存储单元和其他模块.

这样的ASIC常被称为SoC(片上系统)。

FPGA是ASIC的近亲,一般通过原理图、VHDL对数字系统建模,运用EDA软件仿真、综合,生成基于一些标准库的网络表,配置到芯片即可使用。它与ASIC的区别是用户不需要介入芯片的布局布线和工艺问题,而且可以随时改变其逻辑功能,使用灵活。

针对滤波、相关、矩阵运算等需要大量乘和累加运算的特点,DSP的算术单元的乘法器和加法器,可以在一个时钟周期内完成相乘、累加两个运算。近年出现的某些DSP如ADSP2106X、DSP96000系列DSP可以同时进行乘、加、减运算,大大加快了FFT的蝶形运算速度。

电脑的大脑CPU

电脑的大脑CPU(中央处理器)CPU是中央处理单元(Central Processing Unit)的缩写,它可以被简称做微处理器(Microprocessor),不过经常被人们直接称为处理器(processor)。

不要因为这些简称而忽视它的作用,CPU是计算机的核心,其重要性好比大脑对于人一样,因为它负责处理、运算计算机内部的所有数据,而主板芯片组则更像是心脏,它控制着数据的交换。

CPU的种类决定了你使用的操作系统和相应的软件。

CPU主要由运算器、控制器、寄存器组和内部总线等构成,是电脑的核心,再配上储存器、输入/输出接口和系统总线组成为完整的电脑。

CPU的基本结构、功能及参数CPU主要由运算器、控制器、寄存器组和内部总线等构成。

寄存器组用于在指令执行过后存放操作数和中间数据,由运算器完成指令所规定的运算及操作。

CPU主要的性能指标有:1.主频主频也叫时钟频率,单位是MHz(或GHz),用来表示CPU的运算、处理数据的速度。

CPU的主频=外频×倍频系数。

很多人认为主频就决定着CPU的运行速度,这不仅是个片面的,而且对于服务器来讲,这个认识也出现了偏差。

至今,没有一条确定的公式能够实现主频和实际的运算速度两者之间的数值关系,即使是两大处理器厂家Intel和AMD,在这点上也存在着很大的争议,我们从Intel的产品的发展趋势,可以看出Intel很注重加强自身主频的发展。

像其他的处理器厂家,有人曾经拿过一块1G的全美达处理器来做比较,它的运行效率相当于2 G的Intel处理器。

所以,CPU的主频与CPU实际的运算能力是没有直接关系的,主频表示在CPU内数字脉冲信号震荡的速度。

在Intel的处理器产品中,我们也可以看到这样的例子:1 GHz Itanium芯片能够表现得差不多跟2.66 GHz Xeon/Opteron一样快,或是1.5 GHz Itanium 2大约跟4 GHz Xeon/Opteron一样快。

采用 CPU,ASIC,FPGA和NP网络处理器的网络交换机体系结构的比较

通用CPU,ASIC,FPGA和NP网络处理器这四种网络交换机体系结构的详细比较分析使用NP+ASIC的体系设计方式是最为完美的选择。

使用ASIC芯片高速处理各种传统的业务,如二层交换、三层路由、ACL、QoS以及组播处理等等,满足核心交换机对于交换机处理性能的需求;而利用NP实现各种非传统或未成熟的业务,根据需要灵活支持IPV6、Load Balancing、VPN、NAT、IDS、策略路由、MPLS、防火墙等多种业务功能,满足核心交换机对于业务按需叠加的需求……多层交换体系结构的引入有效地提高了局域网的速度,对多层交换体系结构排队模型、交换实施和交换结构等方面的了解,可以更深刻地认识到局域网交换机在性能上的提高。

首先明确几个基本概念:排队模型交换结构是指数据从一个端点到达另一个端点的“高速路”,排队是一种用于控制拥塞的缓冲机制,当交换结构出现拥塞时,会在很大程度上直接影响交换机的性能,所以进行拥塞管理是非常有必要的。

在多个端口争用同一个端口时就需要拥塞管理,对信息包进行排队处理。

排队可以采用动态缓冲区排队或固定缓冲区排队,其中动态缓冲区排队时缓冲区长度为固定增量(如每次64K字节),可以更有效地利用缓冲区资源;而固定缓冲区排序时缓冲区的长度是固定的,这样缓冲区的使用效率不高,但比定制控制器(custom conollers)成本低。

排队可以在交换结构的输入端口进行,即输入排队,也可在交换结构的输出端口进行,即输出排队。

在输入排队时,信息包在进入端口处得到缓冲,最高可将吞吐量减少60%,但会造成线路端阻塞;在输出排队时缓冲区设在输出端口,无线路阻塞,但在流量高峰期间会造成缓冲区溢出。

交换实施交换实施用来说明交换决策的地点和方式:是在本地还是在中央地点,是最长匹配还是准确匹配。

交换决策的地点是中央地点时,就是集中交换。

集中交换采用集中发送表,针对交换和识别提供集中控制,为达到实施的快速处理,查询由ASIC完成,集中交换可以执行第2层或第3层查询。

ASIC芯片设计流程探究及其开发实践

ASIC芯片设计流程探究及其开发实践ASIC(Application-Specific Integrated Circuit)芯片是指按照特定应用需求设计和定制的硅片电路,也被称为定制集成电路。

ASIC芯片设计的目的是为了满足特定应用场景的需求,具有性能优异、功耗低、集成度高、可靠性强等特点。

ASIC芯片的设计流程和普通集成电路的设计流程相比,更加复杂和繁琐。

本文将从ASIC芯片设计的流程探究和开发实践出发,详细了解ASIC芯片设计的过程和实际应用。

一、 ASIC芯片设计流程探究ASIC芯片设计流程一般分为以下几个阶段:1. 需求分析:需求分析阶段主要是充分理解应用场景和需求,明确ASIC芯片的功能、性能、功耗、可靠性等指标。

在需求分析阶段,需要确保需求明确和完整,并建立好基本的开发规划。

2. 概念设计:概念设计阶段主要是根据需求建立ASIC芯片的形态和体系结构,并进行初步的仿真分析和评估。

在概念设计阶段,需要充分考虑芯片的结构图、电路原理图、逻辑设计等方面内容。

3. 逻辑设计:逻辑设计阶段主要是针对芯片的逻辑电路进行设计和优化,包括信号缓存、时序电路、控制器等。

在逻辑设计阶段,需要结合芯片结构进行仿真计算,并进行性能优化和需求调整。

4. 物理设计:物理设计阶段主要是根据逻辑电路图进行器件布局,包括栅极、源漏区域、金属线路等。

在物理设计阶段,需要根据制造工艺和特定应用场景进行微调和优化。

5. 验证测试:验证测试阶段主要是对ASIC芯片进行功能验证和性能测试,包括环境适应性测试、可靠性测试、温度测试等。

在验证测试阶段,需要充分考虑市场需求和投入产出比等方面内容。

6. 授权生产:授权生产阶段主要是将ASIC芯片的设计文件和制造工艺交给制造厂家进行批量生产。

在授权生产阶段,需要充分考虑品质控制和成本控制等方面问题。

二、ASIC芯片设计开发实践ASIC芯片的设计开发实践存在着以下几个难点:1. 设计周期长:ASIC芯片开发需要经历多个阶段复杂的设计过程,设计周期长、成本较高、风险较大。

asic芯片竞争格局分析

主要厂商及产品特点

英特尔

作为全球最大的半导体公司之一,英特尔在ASIC芯片领 域拥有广泛的产品线和市场份额。其产品线包括服务器、 桌面和移动设备等领域的芯片。

AMD

作为计算机处理器领域的领导者之一,AMD在ASIC芯片 领域拥有广泛的产品线和市场份额。其产品线包括服务器 、桌面和移动设备等领域的芯片。

asic芯片竞争格局分析

汇报人:文小库 2023-12-20

目录

• asic芯片市场概述 • asic芯片市场竞争格局 • asic芯片技术发展趋势 • asic芯片市场机遇与挑战 • asic芯片行业发展趋势预测

01

asic芯片市场概述

asic芯片定义与特点

ASIC芯片定义

ASIC芯片(Application-Specific Integrated Circuit)是专用集成电 路,为特定应用定制的集成电路。

标准化与规范化

推动行业标准化和规范化,促进产业链协同 发展。

未来技术发展方向预测

01

5G与物联网技术融 合

将ASIC芯片应用于5G和物联网 领域,实现更高效、更智能的通 信和数据处理。

02

人工智能与机器学 习应用

将ASIC芯片应用于人工智能和机 器学习领域,提高计算效率和性 能。

03

生物医学与健康领 域应用

市场竞争激烈

03

随着ASIC芯片市场的不断发展,竞争也日益激烈,厂商需要不

断提高产品性能、降低成本以保持竞争优势。

应对策略建议

加强技术研发

加大研发投入,提高技术水平 和设计能力,不断推出高性能 、低成本的ASIC芯片产品。

拓展应用领域

积极拓展ASIC芯片在人工智 能、物联网等领域的应用,扩

什么是ASIC架构-精华文章

[周报全文]ASIC芯片驱动综合安全作者:网络世界记者边歆综合安全防护包括防病毒、防垃圾邮件、Web内容过滤等功能,对安全设备的性能提出了很高的要求,而经过改进的ASIC芯片开始承担这些重任。

ASIC(专用集成电路)通过把指令或计算逻辑固化到芯片中,获得了很高的处理能力,因而具有性能优势,被广泛应用于各种安全产品中。

但ASIC的缺点也同样明显,它的灵活性和扩展性不够、开发费用高、开发周期长(一般耗时接近2年)。

由于ASIC存在的缺点,在UTM这种集成多种功能的设备中很少看到ASIC的身影。

不过这种情况在2006年发生了变化。

ASIC扛起性能大旗目前在市场上有一种观点,认为ASIC架构不能把网关杀毒、垃圾邮件过滤、网络监控等功能做到芯片一级,因此ASIC架构不是UTM的理想选择,x86架构才是UTM的方向。

对此,凹凸科技公司系统经理房立财表示,“不能把杀毒、邮件过滤等功能全部放到芯片一级”的说法是对的,但这不能说明ASIC架构的UTM就无法提供高速杀毒、垃圾邮件过滤、内容过滤等功能。

这种说法的论据是正确的,但结论有失偏颇。

ASIC架构不能缺少CPU在探讨x86和ASIC架构之前,首先要搞清楚这两种架构的概念。

其实,关于UTM的ASIC架构和x86架构的概念是较模糊的,是不是全部采用ASIC芯片才是ASIC架构,全部采用x86芯片才是x86架构?实际情况不是这样的。

房立财说:“UTM的ASIC架构体现在两个方面。

一方面,UTM的平台是基于ASIC芯片;另一方面,在内容处理时采用ASIC芯片作为加速器。

凹凸科技认为,如果UTM的平台是基于ASIC芯片的,则称其为ASIC架构。

如果UTM的平台基于x86,则是x86架构。

不过在ASIC架构的UTM中,依然有通用CPU存在。

”CPU在ASIC架构UTM中是必不可少的。

CPU所发挥的作用是:很复杂的应用层逻辑,要用CPU 处理。

例如有新的P2P协议需要编入ASIC芯片,就需要CPU进行处理。

FPGA、CPU、GPU、ASIC性能对比

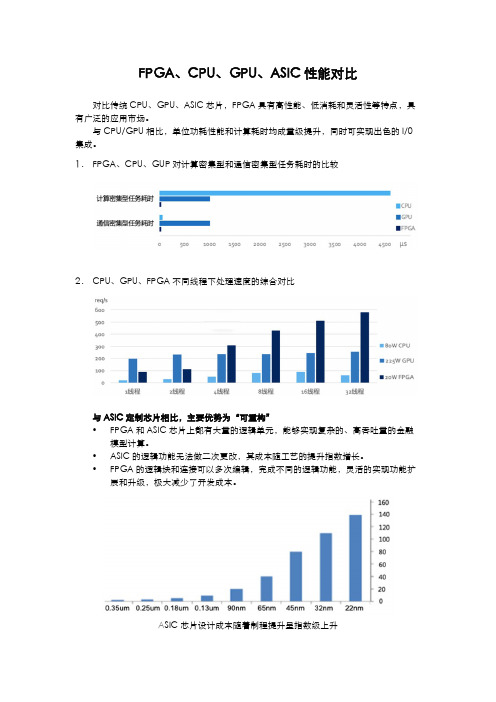

FPGA、CPU、GPU、ASIC性能对比对比传统CPU、GPU、ASIC芯片,FPGA具有高性能、低消耗和灵活性等特点,具有广泛的应用市场。

与CPU/GPU相比,单位功耗性能和计算耗时均成量级提升,同时可实现出色的I/0集成。

1.FPGA、CPU、GUP对计算密集型和通信密集型任务耗时的比较

2.CPU、GPU、FPGA不同线程下处理速度的综合对比

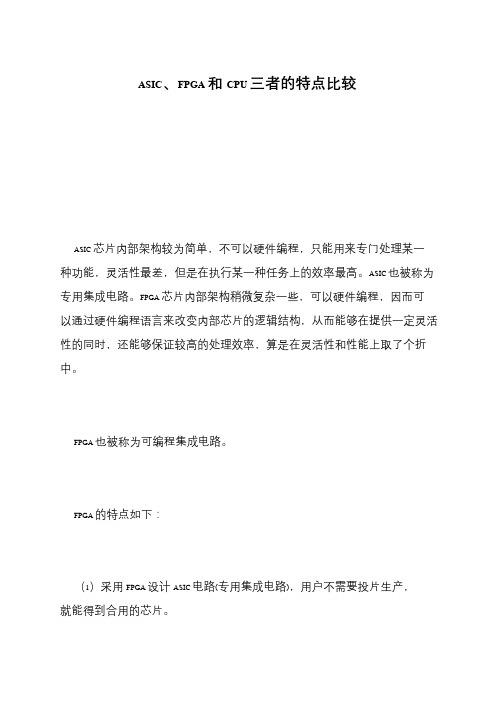

与ASIC定制芯片相比,主要优势为“可重构”

•FPGA和ASIC芯片上都有大量的逻辑单元,能够实现复杂的、高吞吐量的金融模型计算。

•ASIC的逻辑功能无法做二次更改,其成本随工艺的提升指数增长。

•FPGA的逻辑块和连接可以多次编辑,完成不同的逻辑功能,灵活的实现功能扩展和升级,极大减少了开发成本。

A SIC芯片设计成本随着制程提升呈指数级上升。

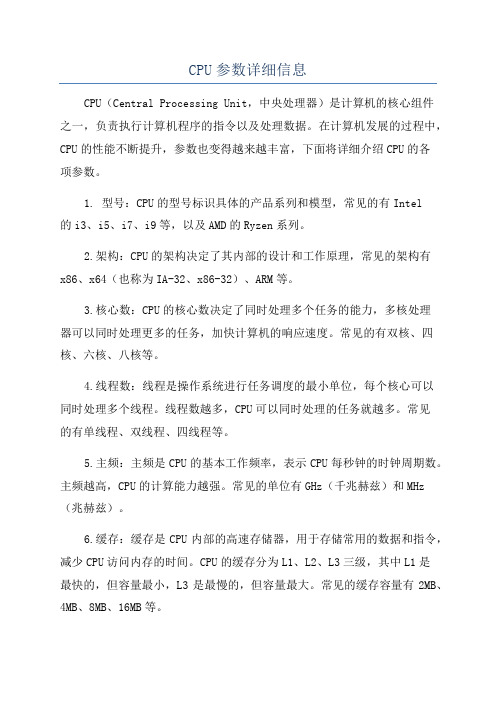

ASIC、FPGA和CPU三者的特点比较

ASIC、FPGA 和CPU 三者的特点比较

ASIC 芯片内部架构较为简单,不可以硬件编程,只能用来专门处理某一种功能,灵活性最差,但是在执行某一种任务上的效率最高。

ASIC 也被称为专用集成电路。

FPGA 芯片内部架构稍微复杂一些,可以硬件编程,因而可以通过硬件编程语言来改变内部芯片的逻辑结构,从而能够在提供一定灵活性的同时,还能够保证较高的处理效率,算是在灵活性和性能上取了个折中。

FPGA 也被称为可编程集成电路。

FPGA 的特点如下:

(1)采用FPGA 设计ASIC 电路(专用集成电路),用户不需要投片生产,就能得到合用的芯片。

CPU参数详细信息

CPU参数详细信息CPU(Central Processing Unit,中央处理器)是计算机的核心组件之一,负责执行计算机程序的指令以及处理数据。

在计算机发展的过程中,CPU的性能不断提升,参数也变得越来越丰富,下面将详细介绍CPU的各项参数。

1. 型号:CPU的型号标识具体的产品系列和模型,常见的有Intel的i3、i5、i7、i9等,以及AMD的Ryzen系列。

2.架构:CPU的架构决定了其内部的设计和工作原理,常见的架构有x86、x64(也称为IA-32、x86-32)、ARM等。

3.核心数:CPU的核心数决定了同时处理多个任务的能力,多核处理器可以同时处理更多的任务,加快计算机的响应速度。

常见的有双核、四核、六核、八核等。

4.线程数:线程是操作系统进行任务调度的最小单位,每个核心可以同时处理多个线程。

线程数越多,CPU可以同时处理的任务就越多。

常见的有单线程、双线程、四线程等。

5.主频:主频是CPU的基本工作频率,表示CPU每秒钟的时钟周期数。

主频越高,CPU的计算能力越强。

常见的单位有GHz(千兆赫兹)和MHz (兆赫兹)。

6.缓存:缓存是CPU内部的高速存储器,用于存储常用的数据和指令,减少CPU访问内存的时间。

CPU的缓存分为L1、L2、L3三级,其中L1是最快的,但容量最小,L3是最慢的,但容量最大。

常见的缓存容量有2MB、4MB、8MB、16MB等。

7. 制程工艺:制程工艺是指CPU芯片制造过程中的各项技术参数,如晶体管的尺寸、绝缘层的厚度等。

制程工艺的改进可以提高芯片的性能和能效,常见的制程工艺有14nm、10nm、7nm等。

8.压缩率:压缩率是指CPU执行算术和逻辑操作时对数据进行压缩的能力。

高压缩率可以减少数据传输的带宽和存储空间,提高计算效率。

压缩率常见的有1:2、1:3、1:4等。

9.支持的指令集:指令集是CPU能够识别和执行的指令的集合,不同的指令集可以支持不同的操作和计算方式。

IC名词解释

IC名词解释1、什么是MRAM?MARM(Magnetic Random Access Memory) 是一种非挥发性的磁性随机存储器。

它拥有静态随机存储器(SRAM)的高速读取写入能力,以及动态随机存储器(DRAM)的高集成度,而且基本上可以无限次地重复写入。

2、光刻:IC生产的主要工艺手段,指用光技术在晶圆上刻蚀电路。

3、芯片:我们通常所说的"芯片"是指集成电路,它是微电子技术的主要产品。

微电子技术涉及的行业很多,包括化工、光电技术、半导体材料、精密设备制造、软件等,其中又以集成电路技术为核心,包括集成电路的设计、制造。

4、CPU :CPU( Central Processing Unit )中央处理器。

CPU是计算机的心脏,包括运算部件和控制部件,是完成各种运算和控制的核心,也是决定计算机性能的最重要的部件。

主要的参数是工作的主频和一次传送或处理的数据的位数。

5、IT:IT(Information Technology)信息技术。

指以计算机为基础的能采集、存储、处理、管理和传输信息的技术。

6、CSP:CSP(Chip Scale Package)芯片级封装。

CSP 封装是最新一代的内存芯片封装技术。

CSP 封装可以让芯片面积与封装面积之比超过1:1.14,已经相当接近1:1的理想情况,绝对尺寸也仅有32平方毫米,约为普通的BGA的1/3,仅仅相当于TSOP内存芯片面积的1/6。

与BGA封装相比,同等空间下CSP封装可以将存储容量提高三倍。

7、芯片组:主芯片的类型或具体型号8、存储器:专门用于保存数据信息的IC。

9、逻辑电路:以二进制为原理的数字电路。

10、IC封装:指把硅片上的电路管脚用导线接引到外部接头处,以便与其它器件连接。

11、IC工艺线宽:线宽:4微米、1微米、0.6微米、0.35微米、0.25微米、0.18微米、0.15微米、0.13微米、0.11微米等,是指IC生产工艺可达到的最小导线宽度,是IC工艺先进水平的主要指标。

asic 芯片

asic 芯片ASIC芯片(Application-Specific Integrated Circuit)是一类专用集成电路芯片,也称为定制芯片。

相比于通用集成电路(如处理器、存储器等),ASIC芯片是根据特定的应用需求而设计的,因此能够提供更高的性能和更低的功耗。

ASIC芯片在各个领域都得到广泛应用,包括通信、计算机、工业控制、汽车、医疗等。

下面将从设计流程、应用案例和未来发展趋势三个方面来介绍ASIC芯片。

首先是ASIC芯片的设计流程。

ASIC芯片的设计是一个复杂的过程,通常分为前端设计和后端设计两个阶段。

前端设计主要包括功能设计、电路设计和逻辑验证。

功能设计是根据需求规格书确定芯片的功能模块和接口,并进行功能分析;电路设计则是根据功能要求,设计电路的结构和参数,如时钟、存储器、逻辑门等;逻辑验证是通过仿真和验证工具对设计进行全面测试,以确保功能的正确性。

后端设计主要包括物理设计、布局设计和版图设计。

物理设计是将逻辑电路映射到实际的物理器件,进行数电转换、时序优化等操作;布局设计则是确定各个电路模块的位置和相互连接方式;版图设计则是将布局设计结果转化为最终的芯片版图。

完成设计后,还需要进行流片和封装测试。

流片是指将版图发送给芯片制造企业,进行样片生产;封装测试则是将芯片封装为最终的芯片模块,并经过各种测试和验收,确保芯片的可靠性和稳定性。

其次是ASIC芯片的应用案例。

ASIC芯片广泛应用于各个领域,以下以通信和计算机领域为例介绍两个典型的应用案例。

在通信领域,ASIC芯片被广泛用于移动通信设备中,如手机、路由器和基站等。

它们能够提供高效的信号处理、数据传输和接口控制功能,满足不同通信标准和需求。

例如,LTE芯片可以实现高速无线数据传输,提供更快的网络连接速度;而基站芯片能够实现大规模的无线通信覆盖,提供更好的通信服务质量。

在计算机领域,ASIC芯片被广泛用于数据中心和云计算设备中。

它们能够提供高性能的计算、存储和网络功能,满足大规模数据处理和分析的需求。

CPU的功能组成及性能参数

CPU的功能组成及性能参数CPU(中央处理器)是一台计算机中最重要的部件之一,它负责执行计算机指令并控制计算机的操作。

CPU的功能组成和性能参数有许多,下面将详细介绍。

一、功能组成:1. 控制单元(Control Unit):控制单元负责解析和执行计算机指令。

它包括指令寄存器、程序计数器和指令译码器等组成部分。

控制单元根据指令的要求发出相关的控制信号,使CPU中的其他部件工作。

2. 算术逻辑单元(Arithmetic Logic Unit, ALU):算术逻辑单元是执行计算和逻辑操作的核心部件。

它包括加法器、逻辑门和运算控制电路等,用于执行算术运算(加法、减法等)和逻辑运算(与、或、非等)。

3. 寄存器(Register):寄存器是存储器件,用于保存临时数据和指令。

常见的寄存器包括累加器(用于存储计算结果)、通用寄存器(存储临时数据)和程序计数器(存储当前指令地址)等。

4. 缓存(Cache):缓存是位于CPU和主存之间的一级高速存储器。

它能够暂时存储最常用的数据和指令,以加快CPU对这些数据和指令的访问速度。

5. 数据总线(Data Bus):数据总线是CPU内部用于传送数据的通道。

它负责将数据从一个部件传送到另一个部件。

数据总线的宽度决定了CPU能够同时传送的数据位数,也就是数据的带宽。

6. 地址总线(Address Bus):地址总线是CPU内部用于传送地址的通道。

它负责将计算机内存的地址传送给主存储器,以便读取或写入数据。

7. 控制总线(Control Bus):控制总线是CPU内部用于传送控制信号的通道。

它负责将控制信号传送到相关的部件,以使它们按照指令要求工作。

二、性能参数:1. 主频(Clock Speed):主频指的是CPU的振荡频率,也被称为时钟频率。

它表示CPU每秒钟执行指令的次数,常用单位是赫兹(Hz)。

主频越高,CPU的工作速度越快。

2. IPC(Instructions Per Cycle):IPC表示每个时钟周期内执行的指令数。

ASIC芯片简介演示

AI领域对计算性能需求苛刻,ASIC芯片可 针对AI算法进行优化,实现高性能、低功 耗的AI计算。

自动驾驶

数据中心

自动驾驶系统需处理大量传感器数据, ASIC芯片可满足实时处理需求,确保驾驶 安全。

数据中心对服务器性能和功耗要求严格, ASIC芯片可提高服务器性能,降低能耗, 节约成本。

02

ASIC芯片设计流程

矢量处理技术

支持矢量运算,加速图像处理、科学计算等领域的应用。

先进封装技术

2.5D/3D封装技术

01

将多个芯片或模块在垂直方向上堆叠,实现更高集成度的封装

。

硅通孔技术

02

利用硅通孔技术实现芯片内部的高密度互连,提高信号传输速

度和封装密度。

扇出型封装技术

03

采用扇出型布线结构,增加封装I/O密度,提高芯片与外界的互

需求分析

01

02

03

功能定义

明确芯片需要实现的功能 和性能指标,包括处理速 度、功耗、接口规范等。

市场调研

了解目标市场需求和竞品 分析,为设计决策提供依 据。

可行性分析评ຫໍສະໝຸດ 技术可行性、成本效 益和风险,确定项目可行 性。

架构设计

总体架构设计

确定芯片的整体结构,包 括处理器核、内存层次、 外设接口等。

连能力。

可靠性设计技术

容错设计技术

通过冗余设计、错误检测与纠正等手段,提高芯片在故障情况下的 可靠性。

抗辐射加固技术

采用特殊材料和电路设计,增强芯片对辐射环境的适应性,确保在 恶劣环境下的正常工作。

热设计技术

优化芯片的热设计,降低热阻,提高散热效率,确保芯片在高温环境 下的稳定运行。

04

四种算力基础

四种算力基础1. 什么是算力算力是指计算机系统或设备在单位时间内完成的计算任务数量,也可以理解为计算能力的度量。

在计算机领域,算力通常用于衡量计算机的性能和效率。

2. CPU算力CPU(中央处理器)是计算机系统的核心组件之一,负责执行计算任务和控制计算机的各个部件。

CPU的算力主要取决于其时钟频率、核心数量和架构等因素。

2.1 时钟频率时钟频率是CPU每秒钟执行的时钟周期数,通常以赫兹(Hz)为单位表示。

时钟频率越高,CPU每秒钟能够执行的指令越多,算力也就越强。

2.2 核心数量CPU的核心数量指的是CPU中集成的处理单元数量。

多核CPU能够同时执行多个任务,因此具有更高的并行计算能力和更强的算力。

2.3 架构CPU的架构决定了其在执行指令时的效率和性能。

不同的架构有不同的优化方式和特性,对算力的影响也不同。

3. GPU算力GPU(图形处理器)是专门用于处理图形和图像的硬件设备,也可以用于进行通用计算。

相比于CPU,GPU具有更多的核心和更高的并行计算能力,因此在某些计算密集型任务中具有更强的算力。

GPU的算力主要取决于其核心数量、核心频率和架构等因素。

与CPU不同,GPU的核心数量通常远远超过CPU,可以同时处理大量的数据和计算任务,从而提供更高的算力。

4. FPGA算力FPGA(现场可编程门阵列)是一种灵活可编程的硬件设备,可以根据需要重新配置其电路结构,从而实现不同的计算任务。

FPGA具有与ASIC(专用集成电路)相媲美的性能和效率,并且能够在不同的应用场景中灵活应用。

FPGA的算力主要取决于其逻辑单元数量、时钟频率和电路结构等因素。

与CPU和GPU不同,FPGA的电路结构可以根据具体需求进行定制和优化,因此可以提供高度定制化的算力解决方案。

5. ASIC算力ASIC(专用集成电路)是专门为特定应用设计和制造的集成电路,具有非常高的性能和效率。

ASIC的算力主要取决于其电路结构和设计优化。

ASIC实验报告(8位CPU的设计)

ASIC设计实验报告学院:电子工程学院学号:2014*******姓名:***指导老师:***2014年11月13日一、实验目的:通过对ASIC实验课的学习,应当学会以下几点:1.熟悉Linux操作系统的应用环境,基本命令行的应用,以及对vi编辑器熟练应用。

2.熟练掌握Verilog编程语言,包括基本组合逻辑电路的实现方法,基本时序逻辑电路的实现方法,怎样使用预定义的库文件,利用always块实现组合逻辑电路的方法已经着重了解assign与always 两种组合逻辑电路实现方法之间的区别,深入了解阻塞赋值与非阻塞赋值的概念以及应用的差别,有限状态机(FSM)实现复杂时序逻辑的方法,以及学会在Linux 系统环境当中应用Synopsys工具VCS进行仿真。

3.熟悉电路设计当中的层次化、结构化的设计方法。

4.熟悉CPU当中有哪些模块组成,模块之间的关系,以及其基本的工作原理。

5.学会利用汇编语言设计程序,注意代码规范性要求。

二、实验要求:按照实验指导书上的要求即:CPU各个模块的Verilog语言代码的编写、编译及仿真正确,并在规定的时间内完成。

要求对CPU进行语言级系统仿真结果正确之后,利用该实验当中采用的八个汇编关键字,编写一个能够实现某种功能的小程序。

然后对其中的控制器电路进行综合,并检查Timing 和Power,进行门级仿真。

三、实验内容:设计一个8位RISC_CPU 系统。

(RISC: Reduced Instruction Set Computer),它是一种八十年代才出现的CPU,与一般的CPU相比,不仅只是简化了指令系统,而且通过简化指令系统使计算机的结构更加简单合理,从而提高了运算速度。

从实现的方法上,它的时序控制信号部件使用了硬布线逻辑,而不是采用微程序控制方式,故产生控制序列的速度要快的多,因为省去了读取微指令的时间。

此CPU所具有的功能有:(1)取指令:当程序已在存储器中时,首先根据程序入口地址取出一条程序,为此要发出指令地址及控制信号。

asic芯片

asic芯片ASIC芯片是一种应用特定集成电路(Application Specific Integrated Circuit)的缩写,它是一种专门设计用于特定应用的集成电路。

与通用的微处理器不同,ASIC芯片被特别设计用于特定的应用领域,具有更高的性能和更低的功耗。

ASIC芯片的应用领域非常广泛,包括通信、计算机、工业控制、汽车电子、医疗设备、消费电子等。

在通信领域,ASIC芯片可以用于设计各种通信设备,如路由器、交换机、基站等。

在计算机领域,ASIC芯片可以用于设计高性能的图形处理器、加密芯片、数据中心芯片等。

在工业控制领域,ASIC芯片可以用于设计各种工业自动化设备,如PLC控制器、传感器接口芯片等。

在汽车电子领域,ASIC芯片可以用于设计车载电子系统,如车载音响、车载导航等。

在医疗设备领域,ASIC芯片可以用于设计各种医疗设备,如心电图仪、血糖监测仪等。

在消费电子领域,ASIC芯片可以用于设计各种消费电子产品,如智能手机、平板电脑等。

ASIC芯片相比通用微处理器具有以下优势:1. 高性能:ASIC芯片可以根据特定应用的需求进行定制设计,因此可以实现更高的性能。

相比通用微处理器,ASIC芯片在执行特定任务时具有更高的处理能力和更高的运算速度。

2. 低功耗:ASIC芯片可以根据特定应用的需求进行精确的优化设计,可以减少功耗。

相比通用微处理器,ASIC芯片在执行相同任务时具有更低的功耗。

3. 小尺寸:由于ASIC芯片是专门为特定应用而设计的,可以进行紧凑的集成设计,因此在尺寸上比通用微处理器更小。

4. 低成本:由于ASIC芯片是专门为特定应用而设计的,可以根据需求进行大规模生产,从而降低成本。

相比通用微处理器,ASIC芯片在相同性能要求下具有更低的成本。

虽然ASIC芯片具有以上优势,但也存在一些挑战:1. 设计复杂性:ASIC芯片的设计复杂性较高,需要专门的工程师进行设计和验证。

设计过程需要投入大量的时间和资源。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验目的

通过实验了解CPU基本信息,运行方式

实验原理:

中央处理器的工作原理就在于在机器周期的每一个时钟周期内,完成本周期对应信号的控制。

而本次设计的简单的CPU也一样,其核心的部分就在Tstep所控制对应的周期中,读入输出总线上的指令,分析输入的指令并对寄存器,数据总线以及加(减)法器的各个控制输入输出端口信号进行控制。

从而达到存储寄存器,进行加减法,进行总线操作的功能。

下面简述CPU的框架:

(1)寄存器

寄存器是用于存放CPU工作中所需要用到的数据的部分。

它有一个16位的数据输入端口,接在总线上。

一个一位控制端口,用于控制寄存器的工作与否。

当控制信号为高时,寄存器从输入端口输入数据。

另外有一个16位的数据输出端口。

当然寄存器也需要时钟信号来驱动工作。

(2)模为4的计数器

本CPU有4条指令,经分析可知每条指令所需要的时钟周期均小于等于四,所以设计一个模为4的计数器来控制CPU的时序。

它的驱动为系统统一的时钟,而它的输出则作为控制部分的时钟信号输入。

(3)38译码器

用于译码输入的指令,从而产生控制寄存器的信号。

(4)控制部分

这个部分是CPU的核心部分,它包含所有的控制逻辑,能够通过改变输出信号而达到控制周围模块的结果。

本程序之中,控制部分还包括了一个加(减)法器。

二.实验程序

module proc(DIN,Resetn,clock,Run,Done,Buswires);

input[15:0] DIN;

input Resetn;

input clock;

input Run;

output Done;

output Buswires;

reg [15:0]Buswires;

reg[0:0] IRin;

reg[0:7] Rin;

reg[0:7] Rout;

reg DINout;

reg Done;

reg Ain;

reg Gin;

reg AddSub;

reg[15:0] Sum;

wire [1:0] Tstep_Q;

wire [8:0]IR;

wire [2:0]I;

wire[7:0] Xreg;

wire[7:0] Yreg;

wire[15:0] R0;

wire[15:0] R1;

wire[15:0] R2;

wire[15:0] R3;

wire[15:0] R4;

wire[15:0] R5;

wire[15:0] R6;

wire[15:0] R7;

wire[15:0] A;

wire[15:0] G;

wire[1:10] select;

wire clear=Resetn|Done|(~Run&~Tstep_Q[0]&~Tstep_Q[1]); upcount Tstep(clear,clock,Tstep_Q);

assign I=IR[8:6];

dec3to8 decX(IR[5:3],1'b1,Xreg);

dec3to8 decY(IR[2:0],1'b1,Yreg);

always @(Tstep_Q or I or Xreg or Yreg)

begin

Done=1'b0;

Ain=1'b0;

Gin=1'b0;

Gout=1'b0;

AddSub=1'b0;

DINout=1'b0;

IRin=1'b0;

Rout=8'b0;

Rin=8'b0;

case(Tstep_Q)

2'b00:

begin

IRin=1'b1;

end

2'b01:

3'b000: begin

Rout=Yreg; Rin=Xreg; Done=1'b1; end

3'b001: begin DINout=1; Rin=Xreg; Done=1'b1; end default: begin

Rout=Xreg; Ain=1'b1; end endcase

2'b10:

case(I)

3'b010: begin

Rout=Yreg; Gin=1'b1; end

3'b011: begin

Rout=Yreg; Gin=1'b1; AddSub=1'b1; end default:; endcase

2'b11:

case(I)

3'b010,3'b011: begin

Gout=1'b1; Rin=Xreg; Done=1'b1;

end

default:;

endcase

endcase

end

regn reg_o(Buswires,Rin[0],clock,R0);

regn reg_1(Buswires,Rin[1],clock,R1);

regn reg_2(Buswires,Rin[2],clock,R2);

regn reg_3(Buswires,Rin[3],clock,R3);

regn reg_4(Buswires,Rin[4],clock,R4);

regn reg_5(Buswires,Rin[5],clock,R5);

regn reg_6(Buswires,Rin[6],clock,R6);

regn reg_7(Buswires,Rin[7],clock,R7);

regn reg_A(Buswires,Ain,clock,A);

regn reg_IR(DIN[15:7],IRin,clock,IR);

always @(AddSub,A,Buswires)

begin

if(!AddSub)

Sum=A+Buswires;

else

Sum=A-Buswires;

end

regn reg_G(Sum,Gin,clock,G);

assign select={Rout,Gout,DINout};

always @(select,R0,R1,R2,R3,R4,R5,R6,R7,G,DIN) begin

if(select==10'b1000000000)

Buswires=R0;

else if(select==10'b010*******)

Buswires=R1;

else if(select==10'b0010000000)

Buswires=R2;

else if(select==10'b0001000000)

Buswires=R3;

else if(select==10'b0000100000)

Buswires=R4;

else if(select==10'b0000010000)

Buswires=R5;

else if(select==10'b0000001000)

Buswires=R6;

else if(select==10'b0000000100)

Buswires=R7;

else if(select==10'b0000000010)

Buswires=G;

else

Buswires=DIN;

end

endmodule

实验图像

1.第一个时钟周期,Resetn为0,故整个计算机为清零。

2.第二个时钟周期,也就是第一个机器周期,Resetn为1,Run为1,计算机开始工作,

DIN输入为2000,IR中读入指令为八进制的100,左边第一位为1,表示执行mvi 指令,这个指令的意思就是把下一周期内DIN上的16位数据读入寄存器0中。

Done 为1,表示完成了该指令。

3.第三个时钟,即第二个机器周期。

DIN上出现的数据是0005,可见BusWires上出

现了0005,并且编号为0的寄存器也存入了数据0005。

4.DIN变为0400,IR中读入的指令为八进制的010,意思就是把编号为0的寄存器里

面的数据通过总线存放到寄存器1中。

而且其本身的数值不变。

5.执行010指令,所以寄存器1的数据更新为0005。

Done变为1.

6.DIN变为4080,IR读入201,意思就是把寄存器0与1中的数据相加之后存如寄存

器0中。

由信号图可以看出寄存器G,A都有更新数据。

并且寄存器0中的数据变为000A。

7.DIN变为6000,IR读入300,意即寄存器0中的数据与本身相减,由后可看到寄存

器0,G,A中的数据均更新为0了。

实验过程及分析

出2000。

符合波形图上RUN第一个高电平的波形图。

输出如图所示为0005。

符合波形图上Run第二个低电平波形图。

出如图所示为0005。

符合波形图上Run第三个高电平波形图。

出如图所示为000A。

符合波形图Run第4个较长低电平波形图。

如图所示为8080。

符合波形图上Run第4个较长低电平第二个clock波形图。

如图所示为000A。

符合波形图上Run第四个高电平波形图。

最后结束演示的2张示意图。