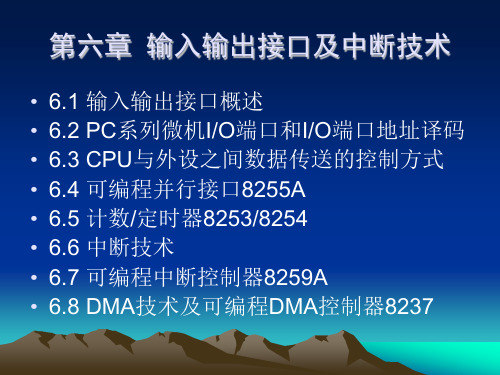

大学计算机微机原理第6章输入输出及中断技术

合集下载

《微机原理与接口技术》课件——第6章输入输出及中断系统

பைடு நூலகம்

CB

AB

DB

CPU

数据端口

状态端口

I/O

设

备

译

码

控制端口

图7.3 I/O接口的基本结构

I/O接口

5、I/O端口的编址 微机系统中,I/O端口的编址方式分为统一编址和独立编址两大类。在Intel 80x86系列微机中,采用独立编址方式。 (1). I/O端口的统一编址方式 统一编址又称存储器映象编址(Memory-mapping Address Coding),就是将I/O端口看成是存储器空间的一个组成部分,按照存储器单元的编址方法统一编排地址号,每个I/O端口占用一个地址。这样,CPU对I/O端口的输入/输出操作如同对存储单元的读/写操作一样,对存储器的各种寻址方式也同样适用于I/O端口。

DB

输

出

设

备

&

数据

地址

译码器

数据端口

译码输出

地址总线

DB

状态端口

译码输出

状态

寄存器

BUSY

+5 V

锁

存

器

Q

D

数据总线DB

来自CPU

选通信号

ACK

WR

IO

/

M

R

&

RD

IO

/

M

图7.9 查询式输出的接口电路

(2)程序中断的输入/输出方式 该方式借助于CPU响应外部中断请求的能力,实现输入输出的控制。简单地说,就是外设将准备就绪的信号转换成有效的中断请求信号通知给CPU,CPU响应中断后,在中断服务子程序中执行I/O指令,进行数据传送。 查询传送方式是由CPU来查询外设的状态,CPU处于主动地位,而外设处于被动地位。中断传送方式则是由外设主动向CPU发出请求,等候CPU处理,在没有发出请求时,CPU和外设都可以独立进行各自的工作。

006_微机原理-输入输出系统与中断技术_1

判断 Y

ቤተ መጻሕፍቲ ባይዱ数据交换

6.1.4 程序查询传送方式

开始

否

开始

初始化

测试数据 是否准备好

初始化 否

是 输入一个字节或字到CPU

外设是否准备好?

是

输出一个字节或字到外设

对数据进行处理 传送到内存缓冲区 操作完成否? 处理缓冲区中数据

操作完成否? 后续处理 查询方式输出过程流程图

后续处理 查询方式输入过程流程图

单向三态缓冲

3 4 7 8 13 14 17 18 11 1 D1 D2 D3 D4 D5 D6 D7 D8 CLK CLR 74LS273 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 2 5 6 9 12 15 16 19

双向三态缓冲

3 4 7 8 13 14 17 18 11 1 2 5 6 9 12 15 16 19

6.1.2 I/O端口

数据端口:数据端口是用来存放外设送往CPU的数据或CPU要输出

到外设去的数据。这些数据是主机和外设之间交换的最基本的信息,

长度一般为1个字节或字,数据端口主要起数据缓冲的作用。 状态端口:状态端口是用来指示外设的当前状态。每种状态用1位 表示,每个外设可以有几个状态位,它们可由CPU读取,以测试或 检查外设的状态,决定程序的流程。 控制端口:它用来存放CPU向接口发出的各种命令和控制字,以便 控制接口或设备的动作。常见的命令信息位有启动位、停止位、允 许中断位等。接口芯片不同,控制字的格式和内容是各不相同的, 常见的控制字有方式选择控制字,操作命令字等。

数字←→模拟 并行←→串行 电压←→电流 弱电←→强电 …………

6.1.1 概述- I/O接口电路的基本功能

高校电子信息类-微机原理-第六章输入输出接口与中断

6.2 CPU与外设数据传送方式

• (1)程序传送-无条件传送(或同步传送)

• 无条件传送:在规定时间内,定时同步传送数据。适用于对开关

、继电器等简单外设状态控制

RD

2021年4月1日星期四

9 自动化科学与电气工程学院 School of Automation Science and Electrical Engineering

2021年4月1日星期四

2 自动化科学与电气工程学院 School of Automation Science and Electrical Engineering

Microcomputer : Principle and Interface

6.1 输入输出接口概述

• I/O接口的主要功能

– (1)对输入输出数据进行缓冲和锁存,输出接口有锁存环节, 输入接口有缓冲环节

Microcomputer : Principle and Interface

6.1 输入输出接口概述

存储单元

存储地址空间

I/O 端口

I/O 地址空间

2021年4月1日星期四

I/O 端口和存储器单独编址

7 自动化科学与电气工程学院 School of Automation Science and Electrical Engineering

Microcomputer : Principle and Interface

6.1 输入输出接口概述

I/O 端口

I/O 地址空间

存储单元

存储器地址空间

整个地址空间

I/O 端口和存储器统一编址

2021年4月1日星期四

6 自动化科学与电气工程学院 School of Automation Science and Electrical Engineering

• (1)程序传送-无条件传送(或同步传送)

• 无条件传送:在规定时间内,定时同步传送数据。适用于对开关

、继电器等简单外设状态控制

RD

2021年4月1日星期四

9 自动化科学与电气工程学院 School of Automation Science and Electrical Engineering

2021年4月1日星期四

2 自动化科学与电气工程学院 School of Automation Science and Electrical Engineering

Microcomputer : Principle and Interface

6.1 输入输出接口概述

• I/O接口的主要功能

– (1)对输入输出数据进行缓冲和锁存,输出接口有锁存环节, 输入接口有缓冲环节

Microcomputer : Principle and Interface

6.1 输入输出接口概述

存储单元

存储地址空间

I/O 端口

I/O 地址空间

2021年4月1日星期四

I/O 端口和存储器单独编址

7 自动化科学与电气工程学院 School of Automation Science and Electrical Engineering

Microcomputer : Principle and Interface

6.1 输入输出接口概述

I/O 端口

I/O 地址空间

存储单元

存储器地址空间

整个地址空间

I/O 端口和存储器统一编址

2021年4月1日星期四

6 自动化科学与电气工程学院 School of Automation Science and Electrical Engineering

【微机原理】第6章. 输入与输出中断

其连接示意图如图6.1所示.

CPU对外设的输入输出操作类似于存储器的读写操作,即 I/O—读/写;但外设与存储器有许多不同点。其比较如表 6.1所示.

接口电路(即可编程接口芯片)种类很多,它的显著特点 是可编程性,即可以通过编程来 规定其功能及操作参数。

二、接口电路的基本结构

接口电路的基本结构同它传送的信息种类 有关。信息可分 为3类:数据信息;状态信息;控制信息。

目录

6.2 CPU与外设之间数据传送的方式

本节将以8086/8088为例,来说明CPU与外设之间数据 传送 的方式。为了实现CPU与外设之间的数据传送,通常采用 以下3 种I/O传送方式。 一、程序传送

程序传送是指CPU与外设间的数据交换在程序控制 (即IN 或OUT指令控制)下进行。

(一) 无条件传送(又称同步传送) 这种传送方式只对固定的外设(如开关、继电器、7

(三) 控制信息 它用于控制外设的启动或停止。接口电路基本结构及其连接如图

6.2所示。接口电路根据传送不同信息的需要,其基本结构安排有一 些特点。

(1) 3种信息(数据、状态、控制)的性质不同,应通过不 同的端口分别传送。如数据输入/输出寄存器(缓冲器)、状态 寄存器与命令控制寄存器各占一个端口,每个端口都有自己的 端口地址,故能用不同的端口地址来区分不同性质的信息。

段显 示器、机械式传感器等简单外设)在规定的时间用IN或 OUT指

一般,这些外设随时做好了数据传送的准备,而无须检测其状态。

这里先要弄清有关输入缓冲与输出锁存的基本概念。

输入数据时,因简单外设输入数据的保持时间相对于CPU的接收速

度来说较长,故输入数据通常不用加锁存器来锁存,而直接使用三态

缓冲器与CPU数据总线相连即可。

CPU对外设的输入输出操作类似于存储器的读写操作,即 I/O—读/写;但外设与存储器有许多不同点。其比较如表 6.1所示.

接口电路(即可编程接口芯片)种类很多,它的显著特点 是可编程性,即可以通过编程来 规定其功能及操作参数。

二、接口电路的基本结构

接口电路的基本结构同它传送的信息种类 有关。信息可分 为3类:数据信息;状态信息;控制信息。

目录

6.2 CPU与外设之间数据传送的方式

本节将以8086/8088为例,来说明CPU与外设之间数据 传送 的方式。为了实现CPU与外设之间的数据传送,通常采用 以下3 种I/O传送方式。 一、程序传送

程序传送是指CPU与外设间的数据交换在程序控制 (即IN 或OUT指令控制)下进行。

(一) 无条件传送(又称同步传送) 这种传送方式只对固定的外设(如开关、继电器、7

(三) 控制信息 它用于控制外设的启动或停止。接口电路基本结构及其连接如图

6.2所示。接口电路根据传送不同信息的需要,其基本结构安排有一 些特点。

(1) 3种信息(数据、状态、控制)的性质不同,应通过不 同的端口分别传送。如数据输入/输出寄存器(缓冲器)、状态 寄存器与命令控制寄存器各占一个端口,每个端口都有自己的 端口地址,故能用不同的端口地址来区分不同性质的信息。

段显 示器、机械式传感器等简单外设)在规定的时间用IN或 OUT指

一般,这些外设随时做好了数据传送的准备,而无须检测其状态。

这里先要弄清有关输入缓冲与输出锁存的基本概念。

输入数据时,因简单外设输入数据的保持时间相对于CPU的接收速

度来说较长,故输入数据通常不用加锁存器来锁存,而直接使用三态

缓冲器与CPU数据总线相连即可。

微型计算机原理及应用:第6章 输入输出和中断技术

——可寻址的端口号为0~65535(FFFFH)

•端口地址小于或等于FFH(255),可以用立即数表示端口地址 IN AL, 42H (8位) 或 IN AX,42H (16位) OUT 43H, AL (8位) 或 OUT 43,AX (16位)

6.1.4 简单的I/O接口

1. 三态缓冲.

用三态门组成,只有当CPU选通时,才允许相应的设备与CPU进 行信息传递.P225-P226

4.DMA传送:在DMAC的控制下,外设直接和存储器(也可外设与外设,存储

器与存储器之间)进行数据传送,而不必经过CPU ,传送速度基 本取决于外设与存储器的速度,从而传送效率大大提高。

6.3 中断技术

6.3.1中断及中断处理过程

中断最初是作为处理器与外部设备交换信息的一种控制方式提出的。由此,最 初的中断全部是对外部设备而言的,称为外部中断或硬件中断。

DMA方式是一种由专门的硬件电路执行I/O的数据传送方式,它 可以让外设接口直接与内存进行高速的数据传送,而不必经过 CPU。这种专门的硬件电路称为DMA控制器,简称DMAC

DMAC的功能

▪ (1)外设通过DMA控制器向CPU提出DMA申请。 ▪ (2)DMA控制器接受外设的DMA请求,取得总线控制权。 ▪ (3)总线载决逻辑对总线申请进行载决,把总线控制权交给

由于不查询外设状态,接口电路不需要状态寄存器

输入方式 IN AL, 0A0H

输出方式 OUT 0A1H, AL

A0 CE

A1

例:采用同步传送系统

(二)查询(条件)传送 适用于CPU与外设异步工作的情况。 在执行输入输出前,要先查询接口中状态寄存器的状态。 输入时,状态寄存器的状态指示要输入的数据是否已经准备就绪 输出时,状态寄存器的状态指示输出设备是否空闲

•端口地址小于或等于FFH(255),可以用立即数表示端口地址 IN AL, 42H (8位) 或 IN AX,42H (16位) OUT 43H, AL (8位) 或 OUT 43,AX (16位)

6.1.4 简单的I/O接口

1. 三态缓冲.

用三态门组成,只有当CPU选通时,才允许相应的设备与CPU进 行信息传递.P225-P226

4.DMA传送:在DMAC的控制下,外设直接和存储器(也可外设与外设,存储

器与存储器之间)进行数据传送,而不必经过CPU ,传送速度基 本取决于外设与存储器的速度,从而传送效率大大提高。

6.3 中断技术

6.3.1中断及中断处理过程

中断最初是作为处理器与外部设备交换信息的一种控制方式提出的。由此,最 初的中断全部是对外部设备而言的,称为外部中断或硬件中断。

DMA方式是一种由专门的硬件电路执行I/O的数据传送方式,它 可以让外设接口直接与内存进行高速的数据传送,而不必经过 CPU。这种专门的硬件电路称为DMA控制器,简称DMAC

DMAC的功能

▪ (1)外设通过DMA控制器向CPU提出DMA申请。 ▪ (2)DMA控制器接受外设的DMA请求,取得总线控制权。 ▪ (3)总线载决逻辑对总线申请进行载决,把总线控制权交给

由于不查询外设状态,接口电路不需要状态寄存器

输入方式 IN AL, 0A0H

输出方式 OUT 0A1H, AL

A0 CE

A1

例:采用同步传送系统

(二)查询(条件)传送 适用于CPU与外设异步工作的情况。 在执行输入输出前,要先查询接口中状态寄存器的状态。 输入时,状态寄存器的状态指示要输入的数据是否已经准备就绪 输出时,状态寄存器的状态指示输出设备是否空闲

微机原理与接口技术-第6章-输入输出与中断技术(1)教材

当设备处于空闲状态或者外设数据准备好时,接口向CPU发 出中断请求信号,CPU收到申请后及时响应接口的中断请求, 暂停执行主程序,转入执行I/O操作程序(中断服务子程序), 完成数据传输之后再返回到主程序继续执行,这种数据传送 方式称为中断方式。

31

中断传送流程图

优点:

实时性好 处理迅速

缺点:

1A3

74LS244

1A4

2A1

2A2

≥1

1G 2A3 2G 2A4

+5V K1 K2 K3 K4 K5 K6 K7 K8

43

NEXT: GOON:

MOV DX, 0FFC1H IN AL, DX TEST AL, 0FFH JZ GOON … MOV AX, BX ADD AX, CX …

44

测试K3的状态,K3断开时转到Label处执行,程序段如 下: TEST AL, 4 JNZ Label ……

不适用于 大量数据 的高速传输

执行主程序 输入/输出指令

执行主程序 一条指令执行结束

有中断请求? 否

执行主程序

是 中断响应

中断处理,执行数据输入/输出

中断返回

32

程序控制下的输入输出方式

无条件传送方式、程序查询传送方式和中断传送方式在数据 传送过程中,CPU从内存读出数据,再输出到外部设备,因 此,这三种方式被统称为程序控制下的输入输出方式 (Programmed input and output),简称PIO方式。

25

6.3.1 无条件传送方式

又称为同步方式,适合简单外设的数据输入输出。 常用外设:开关、继电器、步进电机、发光二极管等。 优点:控制程序简单,软、硬件开销都少。

26

31

中断传送流程图

优点:

实时性好 处理迅速

缺点:

1A3

74LS244

1A4

2A1

2A2

≥1

1G 2A3 2G 2A4

+5V K1 K2 K3 K4 K5 K6 K7 K8

43

NEXT: GOON:

MOV DX, 0FFC1H IN AL, DX TEST AL, 0FFH JZ GOON … MOV AX, BX ADD AX, CX …

44

测试K3的状态,K3断开时转到Label处执行,程序段如 下: TEST AL, 4 JNZ Label ……

不适用于 大量数据 的高速传输

执行主程序 输入/输出指令

执行主程序 一条指令执行结束

有中断请求? 否

执行主程序

是 中断响应

中断处理,执行数据输入/输出

中断返回

32

程序控制下的输入输出方式

无条件传送方式、程序查询传送方式和中断传送方式在数据 传送过程中,CPU从内存读出数据,再输出到外部设备,因 此,这三种方式被统称为程序控制下的输入输出方式 (Programmed input and output),简称PIO方式。

25

6.3.1 无条件传送方式

又称为同步方式,适合简单外设的数据输入输出。 常用外设:开关、继电器、步进电机、发光二极管等。 优点:控制程序简单,软、硬件开销都少。

26

微机原理课件 第6章 输入输出和中断

输入输出接口

基本内容: I/O接口概念;I/O接口应用背景; CPU与I/O设备间的信号种类;I/O端口的寻址 方式;I/O三种传输方式:程序查询方式,程序中 断方式,DMA方式 基本要求: 理解I/O接口的作用和一般结构;掌 握I/O的编址方式和I/O传输方式的三种方式; 重点内容: I/O接口信号种类;I/O编址方式; 三种传输方式; 难点内容: 三种传输方式

外设已处于“就绪”状态,寻址数据口。 是输入,通过输入指令从数据端口读入数据 是输出,通过输出指令向数据端口输出数据 特点:工作可靠,适用面宽,但传送效率低

2、 查询传送方式

1)查询式输入

息 )

输 出 设 备

CPU

D7~0

数 据 缓 冲 器

D7~0

地址线

地址译 码电路

数 输 据 入 锁 D7~0 设 存 备 器 状态信息 (Ready)

2、 查询传 送方式

当系统中有多 个外设时查询 方式如何工作 ?

1号外设 准备就绪?

否

是

对1号外设服务

2号外设 准备就绪?

否

是

对2号外设服务

3号外设 准备就绪?

否

是

对3号外设服务

2、 查询传送方式

优点:

接口电路和程序设计都较为简单,容易实现。

缺点:

CPU、外设不能并行工作,CPU的效率低,外设 得不到及时响应。 适用场合: 这种传送方式适用于一般工作速度较慢的外设, 特别是外设数量不多,实时性要求不高的场合。

查询输入方式

2、 查询传送方式

例:设有某输入接口,状态口地址83H,数据口地址 80H,当状态口的D7为1时,数据准备好。试编写查寻 式输入一个数据的程序;

POLL: IN AL,83H TEST AL,80H ;检查状态位D7

基本内容: I/O接口概念;I/O接口应用背景; CPU与I/O设备间的信号种类;I/O端口的寻址 方式;I/O三种传输方式:程序查询方式,程序中 断方式,DMA方式 基本要求: 理解I/O接口的作用和一般结构;掌 握I/O的编址方式和I/O传输方式的三种方式; 重点内容: I/O接口信号种类;I/O编址方式; 三种传输方式; 难点内容: 三种传输方式

外设已处于“就绪”状态,寻址数据口。 是输入,通过输入指令从数据端口读入数据 是输出,通过输出指令向数据端口输出数据 特点:工作可靠,适用面宽,但传送效率低

2、 查询传送方式

1)查询式输入

息 )

输 出 设 备

CPU

D7~0

数 据 缓 冲 器

D7~0

地址线

地址译 码电路

数 输 据 入 锁 D7~0 设 存 备 器 状态信息 (Ready)

2、 查询传 送方式

当系统中有多 个外设时查询 方式如何工作 ?

1号外设 准备就绪?

否

是

对1号外设服务

2号外设 准备就绪?

否

是

对2号外设服务

3号外设 准备就绪?

否

是

对3号外设服务

2、 查询传送方式

优点:

接口电路和程序设计都较为简单,容易实现。

缺点:

CPU、外设不能并行工作,CPU的效率低,外设 得不到及时响应。 适用场合: 这种传送方式适用于一般工作速度较慢的外设, 特别是外设数量不多,实时性要求不高的场合。

查询输入方式

2、 查询传送方式

例:设有某输入接口,状态口地址83H,数据口地址 80H,当状态口的D7为1时,数据准备好。试编写查寻 式输入一个数据的程序;

POLL: IN AL,83H TEST AL,80H ;检查状态位D7

微型计算机原理与接口技术-第6章输入输出与中断技术ppt课件

四、简单的输出接口举例

锁存器:由D触发器构成〔具有锁存功能〕

通常一个器件包含8个D触发器

常用芯片:

74LS273

74LS273

S

74LS374

S CP Di Qi 0 X X0 1 ↑ 11 1 ↑ 00

D0~D7

A0

A1

▪ ▪

&

▪

A7

IOW

≥

A8 A9

▪& ▪ ▪

A15

74LS273

与

非

用于存储器芯片选通

门

A15 与

~

非

用于I/O芯片选通

A12

门

IO/M

8088最小方式下的原理图

READY RESET

8284A

CLK READY RESET ALE

A19 ~A8 AD7~AD0

8088

+5V

MN/MX DEN DT/R

IO/M

WR RD HOLD HLDA INTR

INTA

存

储

地址 锁存储器

A0 ~ A19

器

8282 地址总线〔20根〕

系

〔三片〕

统

D0 ~ D7 收发器 8286 数据总线〔8根〕 〔一片〕

控制总线

I/O 接 口

节

6.2 简单接口电路

一、 接口电路的根本构造

译码

AB

电路

CPU DB

控制

CB

逻辑

数据输入存放器 (or 三态门)

数据输出存放器 (锁存器)

形状存放器 (or 三态门)

符号 ’8’ ’9’ ’A’ ’B’ ’C’ ’D’ ’E’ ’F’

微机原理PPT 第六章 输入输出接口和中断技术(1)

5)DMAC向I/O设备发出DMA应答信号(DACK);

6)DMAC进行一个字节的传送;

7)完成设定的字节数据传送,CPU恢复对系统总线

的控制。

6.4 中断技术 一、 中断源与中断识别

1.中断源

A. 外设中断 ; B. 指令中断; C. 程序性中断; D. 硬件故障中断

2.中断识别

中断识别的目的是要形成该中断源的中断服务程序的入口 地址,以便CPU将此地址置入CS:IP寄存器,从而实现程序的 转移。

主 片ICW3:OUT 21H,14H

从片1 ICW3 :OUT 0A1H,04H 从片2 ICW3 :OUT 2B1H,02H

级联方式中断请求及响应过程:

主片请求:与非级联一致。

主片响应:收到第一个INTA后,对级联的IR请求, 则从CAS线送出该IR编码; 在第二个INTA返回 中断类型号。 从片请求:与非级联一致,但其INT送到主片,服 从主片的请求规则。 从片响应:通过CAS线译码,选中时在收到第二个 INTA后,返回中断类型号。

INTR 电平触发, 用8259A作为中断接口芯片

属性:硬件、可屏蔽、向量。

2. 不可屏蔽中断

中断请求:中断请求的信号送到CPU的NMI引脚 中断类型号:固定为2 CPU不需要进行中断识别,直接处理中断 属性:硬件、不可屏蔽、向量 NMI由0跳变到1以后要维持至少4个连续的处理 器时钟周期的高电平才被识别 NMI由1跳变到0以后要维持至少4个连续的处理 器时钟周期的低电平,新的NMI中断才能被识别

二、 接口功能 返回外设状态的功能 ; 数据缓冲功能; 信号转换功能; 设备选择功能; 数据宽度与数据格式转换功能;

6.2 简单接口电路 一、接口电路的基本结构

微机系统与接口:第六章 输入输出与中断

第六章 输入输出与中断

6.2 CPU与外设数据传送方式

❖ 程序

START: MOV DL,0F8H

;D4=1,启动

MOV AX,SEG DSTOR

MOV ES,AX

LEA DI,DSTOR

AGAIN: MOV AL,DL

AND AL,0EFH

状态端口 译码输出

第六章 输入输出与中断

6.2 CPU与外设数据传送方式

❖ 查询输入方式程序:

POOL:

IN AL,STATUS_PORT TEST AL,80H JE POOL

IN AL,DATA _PORT

;读状态口 ;设状态信息在D7位 ;READY=0,未准备好,

继续查询

;准备好,读数据

第六章 输入输出与中断

➢ (一)无条件传送(同步传送)

✓ 对象:简单的外设,如开关、继电器、7段显示器等。 ✓ 指令:IN ,OUT ✓ 数据量:少

至输出设备的数 据

锁存器 CE

AB

M/IO

端口地址 译码

&

WR

三态 缓冲器

CE

来自输入设备的数据

&

RD

第六章 输入输出与中断

6.2 CPU与外设数据传送方式

❖ 例:同步传送数据采集系统

6.2 CPU与外设数据传送方式

❖ 3、例:一个采用查询方式的数据采集系统

DB

CPU

8 bits

03 02

A/D

READY D4模拟信号8 bits04

D0,D1,D2

UA0

MUX

UA7

…..

采集要求: 1、初始化 2、停止A/D转换 3、启动转换,查READY状态 4、若READY=1,则从 03 口读数 5、设置下一通道和内存单元

第06章输入输出接口及中断技术X课件

3.控制信息 控制信息是CPU通过接口传送给外设的,CPU通过发送控制信息设置外设(包括接口)的工作模式、控制外设的工作。如外设的启动信号和停止信号就是常见的控制信息。实际上,控制信息往往随着外设的具体工作原理不同而含义不同。

CPU通过接口和外设交换信息时,只能用输入指令(IN)和输出指令 (OUT)传送数据, 所以状态信息、控制信息也是被作为数据信息来传送的,即把状态信息作为一种输入数据,而把控制信息作为一种输出数据,这样,状态信息和控制信息也通过数据总线来传送。但在接口中,这三种信息是在不同的寄存器中分别存放的。 即通过端口来访问以上的信息

小 结

返回

二、端口(PORT)

I/O端口:是指I/O接口中存放数据信息、状态信息和控制信息,CPU可以读/写的一组寄存器或特定电路,被称为I/O端口。 一般接口通常有数据端口、控制端口、状态端口 数据端口:(I、O) 输入数据端口(I):保存外设给CPU的数据 输出数据端口(O):保存CPU给外设的数据 状态端口:(I) 存放I/O设备或接口本身的工作状态信息 控制端口:(O) 存放CPU给外设或接口电路的命令

2. 状态信息 状态信息作为CPU与外设之间交换数据时的联络信息,反映了当前外设所处的工作状态,是外设通过接口送往CPU的。CPU通过对外设状态信号的读取,可得知输入设备的数据是否准备好、输出设备是否空闲等情况。对于输入设备,一般用准备好(READY)信号的高低来表明待输入的数据是否准备就绪;对于输出设备,则用忙(BUSY)信号的高低表示输出设备是否处于空闲状态,如为空闲状态,则可接收CPU输出的信息,否则CPU要暂停送数。因此,状态信息能够保障CPU与外设正确地进行数据交换。

6.1.1I/O接口电路的功能和必要性

一、I/O接口要解决的问题 速度匹配(Buffer):键盘0.5s,打印机几十ms, 软盘500KB/S,硬盘100MB/S 信号电平和驱动能力(电平转换器、驱动器) 信号形式匹配(A/D、D/A) 信息格式(字节流、块、数据包、帧) 时序匹配(定时关系) 总线隔离(三态门)

微机原理第六章 输入输出和中断技术 part 2 (2)

回复断点和硬件现场

中断处理的一般过程

6.4.3 8088/8086中断系统

8086/8088为每个中断源分配 一个中断类型码(中断向量码),其取值范围为 0~255,实际可处理56种中断。其中包括软件中断,系统占用的中断,已经开放 给用户使用的中断。所有中断又可分为两大类:内部中断和外部中断。

内部中断

6.4.2 中断处理的一般过程

1. 中断请求 2. 中断源识别及中断判优 3. 中断响应 4. 中断处理(服务) 5. 中断返回

1. 中断请求 ➢ INTR中断请求信号应保持到中断被处理为止 ➢ CPU响应中断后,中断请求信号应及时撤销

2. 中断源识别 ➢ 软件判优:由软件来安排中断源的优先级别。顺序查询中断请求,先查询的

➢ (4)能向存储器或外设发出读/写命令。 ➢ (5)能决定传送的字节数,并判断DMA传送是否结束。 ➢ (6)在DMA过程结束后,能向CPU发出DMA结束信号,将总线控制权交

还给CPU。

2. DMA控制器的工作过程 ➢ (1)当外设准备好,可以进行DMA传送时,外设向DMA控制器发出

“DMA传送请求”信号DRQ ➢ (2)DMA控制器收到请求后,向CPU发出“总线请求”信号HOLD ➢ (3)CPU在完成当前总线周期后会立即发出HLDA信号,对HOLD信号进

➢ (2)单步中断——1型中断,标志寄存器中有一位陷阱标志TF。 ➢ (3)断点中断——3型中断,专用于设置断点的指令INT 3,用于程序中设

置断点来调试程序。

➢ (4)溢出中断——4型中断,在算数指令的执行过程发出溢出 ➢ (5)用户自定义的软件中断——n型中断,执行中断指令INT n引起内部中

断。

需要时,CPU回到原来被中断的地方继续执行自己的程序。 优点: ➢ CPU效率高,实时性好 缺点 ➢ 程序编制相对较为复杂

中断处理的一般过程

6.4.3 8088/8086中断系统

8086/8088为每个中断源分配 一个中断类型码(中断向量码),其取值范围为 0~255,实际可处理56种中断。其中包括软件中断,系统占用的中断,已经开放 给用户使用的中断。所有中断又可分为两大类:内部中断和外部中断。

内部中断

6.4.2 中断处理的一般过程

1. 中断请求 2. 中断源识别及中断判优 3. 中断响应 4. 中断处理(服务) 5. 中断返回

1. 中断请求 ➢ INTR中断请求信号应保持到中断被处理为止 ➢ CPU响应中断后,中断请求信号应及时撤销

2. 中断源识别 ➢ 软件判优:由软件来安排中断源的优先级别。顺序查询中断请求,先查询的

➢ (4)能向存储器或外设发出读/写命令。 ➢ (5)能决定传送的字节数,并判断DMA传送是否结束。 ➢ (6)在DMA过程结束后,能向CPU发出DMA结束信号,将总线控制权交

还给CPU。

2. DMA控制器的工作过程 ➢ (1)当外设准备好,可以进行DMA传送时,外设向DMA控制器发出

“DMA传送请求”信号DRQ ➢ (2)DMA控制器收到请求后,向CPU发出“总线请求”信号HOLD ➢ (3)CPU在完成当前总线周期后会立即发出HLDA信号,对HOLD信号进

➢ (2)单步中断——1型中断,标志寄存器中有一位陷阱标志TF。 ➢ (3)断点中断——3型中断,专用于设置断点的指令INT 3,用于程序中设

置断点来调试程序。

➢ (4)溢出中断——4型中断,在算数指令的执行过程发出溢出 ➢ (5)用户自定义的软件中断——n型中断,执行中断指令INT n引起内部中

断。

需要时,CPU回到原来被中断的地方继续执行自己的程序。 优点: ➢ CPU效率高,实时性好 缺点 ➢ 程序编制相对较为复杂

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

教材p238

P238图

27

四、锁存器接口

通常由D触发器构成; 特点:

具有对数据的锁存能力; 不具备对数据的控制能力

28

常用锁存器芯片

74LS273

8D触发器,不具备数据的控制能力

P240图

74LS373

含三态的8D触发器,具有对数据的控制能力。 既可以做输入接口,也可以做输出接口。

速度匹配(Buffer) 信号的驱动能力(电平转换器、驱动器) 信号形式和电平的匹配(A/D、D/A) 信息格式(字节流、块、数据包、帧) 时序匹配(定时关系) 总线隔离(三态门)

5

接口的功能

数据的缓冲与暂存 信号电平与类型的转换 增加信号的驱动能力 对外设进行监测、控制与管理,中断处理

内存:

1MB

端口:

64K个

编址方式:

与内存统一编址 独立编址

10

端口与内存的统一编址

特点:

指令及控制信号统一; 内存地址资源减少

00000H

F0000H FFFFFH

内存 地址 960KB

I/O地址 64KB

11

端口的独立编址

特点:

内存地址资源充分利用 能够应用于端口的指令

Rx8

a b c d e f g D+5V K0~K3 P

符号 ’0’ ’1’ ’2’ ’3’ ’4’ ’5’ ’6’ ’7’

形状

7段码 .gfedcba

00111111 00000110

01011011 01001111 01100110 01101101 01111101 00000111

符号 ’8’ ’9’ ’A’

6

二、I/O端口

数据端口 端口 状态端口

控制端口

7

I/O端口

I/O接

DB

口

数据

CPU

状态

外设

控制

8

接口和端口

接口1

接口2

接口N

端口 1 端口 2

┅

端口 1

端口 1

端口 编址

端口

┅

端口

2

2

┅

┅

端口 m

端口 m

端口 m

端口地址=芯片地址(高位地址)+片内地址

9

三、I/O端口的编址方式

8086/8088的寻址能力:

较少

00000H

FFFFFH 0000H

FFFFH

内存 地址

I/O 地址

12

端口的寻址

8088/8086寻址端口数:

64K个

寻址端口的信号:

IOR、IOW A15 ~ A0

13

8088/8086的I/O端口编址

采用I/O独立编址方式(但地址线与存储器共用) 地址线上的地址信号用IO/M来区分 I/O操作只使用20根地址线中的16根:A15~A0 可寻址的I/O端口数为64K(65536)个 I/O地址范围为0~FFFFH IBM PC只使用了1024个I/O地址(0~3FFH)

18

I/O地址译码例

译码电路图:

接口芯片

IOR

& IOW

A1

A0

A11

A10

A18

≥1

CE

A3

A2

&

A9

A7

┇

A4

19

§6.2 简单接口电路

20

掌握:

接口电路的分类及特点; 两类简单接口芯片的应用

21

一、接口的基本构成

译码

AB

电路

DB

控制

CB

逻辑

数据输入寄存器 (or 三态门)

数据输出寄存器 (锁存器)

D7

译码

IOW

器

≥1

A6~A4 A7

& 74GLS138

1

G2A Y0

A3 A2 A1 A0

IOR

G2B C Y1 B A

≥1

7D4L0S2Q730 | Q1 D7 Q2

Q3 Q4 CP Q5 Q6 Q7

7406 反相器

D0 7O4L1S24I41

D1 O2 I2 D2 O3 I3

D3

O4 I4 E1

’B’ ’C’ ’D’ ’E’ ’F’

形状

7段码 .gfedcba

01111111 01100111

01110111 01111100 00111001 01011110 01111001 01110001

I/O接口综合应用例 —— 程序段

……

Seg7 DB 3FH,06H,

GO: IN AL, 0F1H

按传输信息的类型分类:

数字接口 模拟接口

按传输信息的方式分类:

并行接口 串行接口

24

接口特点

输入接口:

要求对数据具有控制能力 常用三态门实现

输出接口:

要求对数据具有锁存能力 常用锁存器实现

25

三、三态门接口

高电平、低电平、高阻态

26

74LS244

含8个三态门的集成电路芯片 在外设具有数据保持能力时用来输入接口 74LS244应用例

29

I/O接口综合应用例

根据开关状态在7段数码管上显示数字或符号 设输出接口的地址为F0H 设输入接口地址为F1H 当开关的状态分别为0000~1111时,在7段

数码管上对应显示’0’~’F’

7段数码管图见教材p242

30

F0H = 1111 0000

A0

F1H = 1111 0001

D0~

5BH,4FH,66H,6DH, 7DH,07H,7FH,67H,77H,

14

四、I/O地址的译码

目的: 确定端口的地址 参加译码的信号: IOR,IOW,高位地址信号 OUT指令将使总线的IOW信号有效 IN指令将使总线的IOR信号有效

15

I/O译码的地址信号

当接口只有一个端口时,16位地址线一般应 全部参与译码,译码输出直接选择该端口;

当接口具有多个端口时,则16位地址线的高 位参与译码(决定接口的基地址),而低位 则用于确定要访问哪一个端口。

16

I/O地址译码例

某外设接口有4个端口,地址为2F0H—— 2F3H,由A15~A2译码得到,而A1、A0用 来区分接口中的4个端口。试画该接口与系 统的连接图。

17

I/O地址译码例

地址范围:

A11

××××001011110000 ××××001011110011

任意状态

片内地址

图中不接入

第6章

输入输出及中断技术

1

主要内容

基本概念

输入输出系统 I/O接口和端口 端口的编址方式

简单接口芯片及其应用 基本输入输出方法 中断的基本概念及工作过程

2

§6.1 输入输出系统

3

了解和掌握:

接口的基本功能 端口的概念 端口的编址方式 I/O地址译码

4

一、I/O接口

接口要解决的问题

状态寄存器 (or 三态门)

命令寄存器

数据线

状态线 控制线

22

接口的基本构成

数据输入/输出寄存器

暂存输入/输出的数据

命令寄存器

存放控制命令

设定接口功能、工作参数和工作方式。

状态寄存器

保存外设当前状态,以供CPU读取。

23

二、接口的类型及特点

按传输信息的方向分类:

输入接口 输出接口

P238图

27

四、锁存器接口

通常由D触发器构成; 特点:

具有对数据的锁存能力; 不具备对数据的控制能力

28

常用锁存器芯片

74LS273

8D触发器,不具备数据的控制能力

P240图

74LS373

含三态的8D触发器,具有对数据的控制能力。 既可以做输入接口,也可以做输出接口。

速度匹配(Buffer) 信号的驱动能力(电平转换器、驱动器) 信号形式和电平的匹配(A/D、D/A) 信息格式(字节流、块、数据包、帧) 时序匹配(定时关系) 总线隔离(三态门)

5

接口的功能

数据的缓冲与暂存 信号电平与类型的转换 增加信号的驱动能力 对外设进行监测、控制与管理,中断处理

内存:

1MB

端口:

64K个

编址方式:

与内存统一编址 独立编址

10

端口与内存的统一编址

特点:

指令及控制信号统一; 内存地址资源减少

00000H

F0000H FFFFFH

内存 地址 960KB

I/O地址 64KB

11

端口的独立编址

特点:

内存地址资源充分利用 能够应用于端口的指令

Rx8

a b c d e f g D+5V K0~K3 P

符号 ’0’ ’1’ ’2’ ’3’ ’4’ ’5’ ’6’ ’7’

形状

7段码 .gfedcba

00111111 00000110

01011011 01001111 01100110 01101101 01111101 00000111

符号 ’8’ ’9’ ’A’

6

二、I/O端口

数据端口 端口 状态端口

控制端口

7

I/O端口

I/O接

DB

口

数据

CPU

状态

外设

控制

8

接口和端口

接口1

接口2

接口N

端口 1 端口 2

┅

端口 1

端口 1

端口 编址

端口

┅

端口

2

2

┅

┅

端口 m

端口 m

端口 m

端口地址=芯片地址(高位地址)+片内地址

9

三、I/O端口的编址方式

8086/8088的寻址能力:

较少

00000H

FFFFFH 0000H

FFFFH

内存 地址

I/O 地址

12

端口的寻址

8088/8086寻址端口数:

64K个

寻址端口的信号:

IOR、IOW A15 ~ A0

13

8088/8086的I/O端口编址

采用I/O独立编址方式(但地址线与存储器共用) 地址线上的地址信号用IO/M来区分 I/O操作只使用20根地址线中的16根:A15~A0 可寻址的I/O端口数为64K(65536)个 I/O地址范围为0~FFFFH IBM PC只使用了1024个I/O地址(0~3FFH)

18

I/O地址译码例

译码电路图:

接口芯片

IOR

& IOW

A1

A0

A11

A10

A18

≥1

CE

A3

A2

&

A9

A7

┇

A4

19

§6.2 简单接口电路

20

掌握:

接口电路的分类及特点; 两类简单接口芯片的应用

21

一、接口的基本构成

译码

AB

电路

DB

控制

CB

逻辑

数据输入寄存器 (or 三态门)

数据输出寄存器 (锁存器)

D7

译码

IOW

器

≥1

A6~A4 A7

& 74GLS138

1

G2A Y0

A3 A2 A1 A0

IOR

G2B C Y1 B A

≥1

7D4L0S2Q730 | Q1 D7 Q2

Q3 Q4 CP Q5 Q6 Q7

7406 反相器

D0 7O4L1S24I41

D1 O2 I2 D2 O3 I3

D3

O4 I4 E1

’B’ ’C’ ’D’ ’E’ ’F’

形状

7段码 .gfedcba

01111111 01100111

01110111 01111100 00111001 01011110 01111001 01110001

I/O接口综合应用例 —— 程序段

……

Seg7 DB 3FH,06H,

GO: IN AL, 0F1H

按传输信息的类型分类:

数字接口 模拟接口

按传输信息的方式分类:

并行接口 串行接口

24

接口特点

输入接口:

要求对数据具有控制能力 常用三态门实现

输出接口:

要求对数据具有锁存能力 常用锁存器实现

25

三、三态门接口

高电平、低电平、高阻态

26

74LS244

含8个三态门的集成电路芯片 在外设具有数据保持能力时用来输入接口 74LS244应用例

29

I/O接口综合应用例

根据开关状态在7段数码管上显示数字或符号 设输出接口的地址为F0H 设输入接口地址为F1H 当开关的状态分别为0000~1111时,在7段

数码管上对应显示’0’~’F’

7段数码管图见教材p242

30

F0H = 1111 0000

A0

F1H = 1111 0001

D0~

5BH,4FH,66H,6DH, 7DH,07H,7FH,67H,77H,

14

四、I/O地址的译码

目的: 确定端口的地址 参加译码的信号: IOR,IOW,高位地址信号 OUT指令将使总线的IOW信号有效 IN指令将使总线的IOR信号有效

15

I/O译码的地址信号

当接口只有一个端口时,16位地址线一般应 全部参与译码,译码输出直接选择该端口;

当接口具有多个端口时,则16位地址线的高 位参与译码(决定接口的基地址),而低位 则用于确定要访问哪一个端口。

16

I/O地址译码例

某外设接口有4个端口,地址为2F0H—— 2F3H,由A15~A2译码得到,而A1、A0用 来区分接口中的4个端口。试画该接口与系 统的连接图。

17

I/O地址译码例

地址范围:

A11

××××001011110000 ××××001011110011

任意状态

片内地址

图中不接入

第6章

输入输出及中断技术

1

主要内容

基本概念

输入输出系统 I/O接口和端口 端口的编址方式

简单接口芯片及其应用 基本输入输出方法 中断的基本概念及工作过程

2

§6.1 输入输出系统

3

了解和掌握:

接口的基本功能 端口的概念 端口的编址方式 I/O地址译码

4

一、I/O接口

接口要解决的问题

状态寄存器 (or 三态门)

命令寄存器

数据线

状态线 控制线

22

接口的基本构成

数据输入/输出寄存器

暂存输入/输出的数据

命令寄存器

存放控制命令

设定接口功能、工作参数和工作方式。

状态寄存器

保存外设当前状态,以供CPU读取。

23

二、接口的类型及特点

按传输信息的方向分类:

输入接口 输出接口