sdf文件的产生方法

VCS使用SDF文件进行后仿反标

VCS使用SDF文件进行后仿反标版本控制系统(Version Control System,VCS)是一种用于管理和控制源代码或其他文件的软件工具。

它能够跟踪文件的变化、协调多个开发者的工作、恢复文件的历史版本等。

SDF文件(Standard Delay Format)是一种工业界常用的电路后仿文件格式,用于描述电路的时序关系和时延信息,通常用于电路仿真和布线分析。

在VCS中,使用SDF文件进行后仿反标是一种常见的应用场景,用于验证电路的时序性能和功能正确性。

下面将介绍如何使用SDF文件进行后仿反标。

首先,在VCS中建立项目并导入设计文件和SDF文件。

设计文件通常为硬件描述语言(HDL)的源代码,如Verilog或VHDL。

SDF文件包含了电路的时序信息,如时钟周期、信号延迟等。

将这两者导入到VCS项目中后,就可以开始后仿反标的工作。

接着,设置仿真参数。

根据需要,可以设置仿真时间、时钟周期、仿真精度等参数。

保证仿真参数能够覆盖电路的所有工作状态。

然后,编译和仿真设计文件。

使用VCS工具进行编译,将设计文件翻译成仿真器所能识别的模拟电路。

编译生成仿真器可执行文件后,使用该文件进行电路仿真。

在仿真过程中,仿真器会根据设计文件和仿真参数模拟电路的运行,并生成波形图和仿真结果。

在仿真过程中,VCS会根据SDF文件中的时序信息对电路进行时序分析。

SDF文件定义了电路中的各个时钟域、时钟周期、时序路径等信息。

VCS会根据这些信息检测电路中的时序违例,如时序不符、信号延迟不满足等。

若仿真结果与SDF文件中定义的时序信息相符,则说明电路的时序性能正常。

如果存在时序违例,可以根据VCS提供的时序分析报告定位问题,例如指明违例路径、具体时钟域等。

除了时序分析,SDF文件还可以用于布线分析。

根据SDF文件中的时序信息,布线工具可以优化电路的布线方案,以减小信号延迟、提高电路性能。

总结来说,使用SDF文件进行后仿反标时,需要将设计文件和SDF文件导入VCS项目中,并设置仿真参数。

VCS使用SDF文件进行后仿反标

VCS使用SDF文件进行后仿反标版本控制系统(VCS)是一种记录和管理软件开发过程中文件变化的系统。

它可以帮助开发团队协同工作,跟踪和修改文件以及解决潜在的冲突。

SDF文件是一种标准的后仿反标文件,用于描述软件系统的架构和设计。

下面将介绍如何使用VCS进行SDF文件的后仿反标。

首先,选择适合你需求的VCS工具。

常用的VCS工具有Git、Subversion、Mercurial等。

这些工具都有相应的客户端和服务器端软件,你需要在本地安装客户端,然后将代码库(repository)创建在服务器端。

下一步是创建代码库。

通常,每个项目都有一个代码库来管理代码的版本和变化。

你可以使用VCS工具的命令来创建代码库,例如使用Git可以使用"git init"命令。

将现有的SDF文件添加到代码库中。

将文件复制到代码库的目录中,并使用VCS工具的命令将文件添加到版本控制系统中。

例如,使用Git可以使用"git add"命令来添加文件。

查看版本历史。

在版本控制系统中可以查看文件的不同版本和历史更改记录。

使用VCS工具的命令来查看历史记录,例如使用Git可以使用"git log"命令。

回滚和恢复文件。

如果你对文件进行了错误的更改,可以使用VCS工具来回滚文件到之前的版本。

使用VCS工具的命令来回滚文件,例如使用Git可以使用"git revert"命令。

分支和合并。

在软件开发过程中,通常会创建分支来进行独立的开发工作,然后将分支合并到主分支中。

你可以使用VCS工具的命令创建和切换分支,例如使用Git可以使用"git branch"和"git checkout"命令。

解决冲突。

当多个人同时修改同一个文件时,可能会发生冲突。

VCS工具提供了解决冲突的功能,可以帮助开发人员协调不同版本的更改。

使用VCS工具的命令来解决冲突,例如使用Git可以使用"git merge"命令。

118.PT生成SDF

118.PT⽣成SDF

1. 想让pt吐出的sdf在进⾏setup和hold检查时⽤$setuphold函数;

⽽在recovery和remove检查时⽤$recrem函数

答:-include RECREM

2. neg value

答:⾸先,SETUP和HOLD这两个时序描述符不⽀持负值,如果限制值是负值的话,仿真⼯具会直接当成0处理

其次,SETUPHOLD这个时序描述符,是SETUP和HOLD两者的联合,并且⽀持负值,如果限制值是负值的话,当仿真⼯具使能了负值检查时,会进⾏负值的时序检查,否则也会当成0处理

然后,我们再讨论这个问题。

⼯具直接把负值当成0处理,是⼀种更悲观的处理⽅式,在时序不紧张的情况下,倒是影响不太⼤。

如果时序相对很紧张,就可能出现很多TIMING VIOLATIONS。

所以,到底关⼼不关⼼这个问题,就要看设计的时序情况了

最后,提出⼀种使⽤SETUPHOLD时序描述符,描述SDF⽂件的⽅法。

write_sdf -version 3.0 -include SETUPHOLD -context verilog xx.sdf

Note:vcs⼯具使能负值时序检查的参数是+neg_tchk

3. 检查

如果⽆法写出来RECOVERY和REMOVAL,再请察看library中是如何定义recovery和removal的时序曲线类型的,关键字:timing_type。

五款信号完整性仿真分析工具

SI五款信号完整性仿真工具介绍(一)Ansoft公司的仿真工具现在的高速电路设计已经达到GHz的水平,高速PCB设计要求从三维设计理论出发对过孔、封装和布线进行综合设计来解决信号完整性问题。

高速PCB设计要求中国工程师必须具备电磁场的理论基础,必须懂得利用麦克斯韦尔方程来分析PCB设计过程中遇到的电磁场问题。

目前,Ansoft公司的仿真工具能够从三维场求解的角度出发,对PCB设计的信号完整性问题进行动态仿真。

Ansoft的信号完整性工具采用一个仿真可解决全部设计问题:SIwave是一种创新的工具,它尤其适于解决现在高速PCB和复杂IC封装中普遍存在的电源输送和信号完整性问题。

该工具采用基于混合、全波及有限元技术的新颖方法,它允许工程师们特性化同步开关噪声、电源散射和地散射、谐振、反射以及引线条和电源/地平面之间的耦合。

该工具采用一个仿真方案解决整个设计问题,缩短了设计时间。

它可分析复杂的线路设计,该设计由多重、任意形状的电源和接地层,以及任何数量的过孔和信号引线条构成。

仿真结果采用先进的3D图形方式显示,它还可产生等效电路模型,使商业用户能够长期采用全波技术,而不必一定使用专有仿真器。

(二)SPECCTRAQuestCadence的工具采用Sun的电源层分析模块:Cadence Design Systems的SpecctraQuest PCB信号完整性套件中的电源完整性模块据称能让工程师在高速PCB设计中更好地控制电源层分析和共模EMI。

该产品是由一份与Sun Microsystems公司签署的开发协议而来的,Sun最初研制该项技术是为了解决母板上的电源问题。

有了这种新模块,用户就可根据系统要求来算出电源层的目标阻抗;然后基于板上的器件考虑去耦合要求,Shah表示,向导程序能帮助用户确定其设计所要求的去耦合电容的数目和类型;选择一组去耦合电容并放置在板上之后,用户就可运行一个仿真程序,通过分析结果来发现问题所在。

门级仿真经验(SDF反标及其工作原理)

门级仿真经验(SDF反标及其工作原理)在数字电路的设计和实现过程中,仿真技术是一个不可或缺的环节。

门级仿真是一种常用的仿真方法,它可以对数字逻辑电路的功能进行验证和分析。

在门级仿真中,使用标准延迟格式(SDF)模型进行仿真,以获得更加准确的结果。

SDF反标是指将延迟信息从高层次的设计(例如RTL)传递到低层次的设计(例如门级)的过程。

它的目的是将每个门的延迟信息准确地传递下去,以确保在实际硬件实现中的时序关系得到正确的处理。

SDF模型的工作原理是基于时钟驱动的概念。

在数字电路中,时钟信号是最基本的输入信号之一,它决定了数字电路中各个时刻的操作。

SDF 模型通过引入时钟约束来描述每个门的时序行为,通过时钟延迟来描述信号的传播延迟。

SDF模型将信号分为两类:同步信号和非同步信号。

同步信号是与时钟信号同步的信号,例如时钟沿信号和时钟心跳信号。

非同步信号是与时钟信号无关的信号,例如数据输入信号和数据输出信号。

SDF模型通过将时钟信号和非同步信号相互组合起来,描述了整个电路的时序行为。

在进行SDF反标时,首先需要根据设计中的门级电路提取出门的时延信息。

这可以通过一些EDA工具进行,例如PrimeTime和Synopsys等。

提取出的时延信息包括门延迟、时钟延迟和数据传输延迟等。

然后将提取出的时延信息与设计中的组合逻辑电路关联起来,形成SDF文件。

SDF文件中包含了每个门的延迟信息,以及输入和输出信号之间的传输延迟。

最后,使用SDF文件进行仿真。

在仿真过程中,将SDF文件与设计电路进行联合仿真,以验证设计的功能和时序关系。

仿真结果将根据SDF文件中的时延信息进行计算,从而获得更加准确的仿真结果。

总之,SDF反标是门级仿真中的一个重要步骤,它通过引入时钟驱动的SDF模型,准确地传递门级电路的延迟信息,从而实现对设计功能和时序关系的验证。

在实际的数字逻辑电路设计中,掌握SDF反标的方法和原理对于确保设计质量和时序正确性非常重要。

sdf解释

1 sdf文件的内容1.1 表头部分示例:(DELAYFILE(SDFVERSION "2.1")(DESIGN "sj_maf")(DATE "07/25/2005 16:24:43")(VENDOR "Altera")(PROGRAM "Quartus II")(VERSION "Version 4.2 Build 178 01/19/2005 Service Pack 1 SJ Full Version") (DIVIDER .)(VOLTAGE 4.75 : 4.75 : 4.75)(TEMPERATURE 85 : 85 : 85)(TIMESCALE 1 ps)解释:SDFVERSION:表示此SDF部分遵循哪一个版本的SDF标准所产生的,在1.0版本中SDFVERSION是一定必要的,其后所接的QSTRING(引号内的部分)可以省略。

2.1版以后的版本SDFVERSION和QSTRING都可以省略。

DESIGN:表示产生timing数据的设计名称。

DATE:表示产生SDF文件的时间。

PROGRAM:表示产生SDF文件的工具。

VERSION:表示产生SDF文件的工具的版本。

DIVIDER:表示此SDF文件中用来分隔层次式架构的分隔符,一般使用(/)或者(.),缺省是(.)。

VOLTAGE:表示此SDF中三种状态(best、normal、worst)下的电压值,在上例中仅提出了normal state,所以三种电压值皆相同。

PROCESS:表示此SDF文件中三种状态(best、normal、worst)数值所乘上的上例中仅提出了normal state,所以三种状态下的factor值皆相同。

TEMPERATURE:表示此SDF文件中三种状态(best、normal、worst多少。

sdf文件 化学结构式

sdf文件化学结构式SDF文件(Structure-Data File)是一种用于存储化学结构信息的文件格式。

它是由Tripos公司开发的一种标准格式,被广泛应用于药物设计、分子建模等领域。

SDF文件能够包含分子的结构式、化学信息和物理属性等多种数据。

SDF文件使用ASCII码进行存储,通过行间的特定分隔符来将不同的数据字段区分开。

一般来说,SDF文件的第一行指定了分子的总数,后续的行则是描述每个分子的具体信息。

每个分子的信息通常由多个行组成,其中包括结构式、分子的化学名称、物理性质数据等。

而结构式一般被编码为连接表达式(Connectivity Table)。

在SDF文件中,结构式是以连接表达式的形式表示的。

连接表达式是一种图形表示法,通过原子和键的连接关系来表示分子的结构。

在连接表达式中,原子用原子符号表示,键用数字表示,并通过原子之间的连接关系来表示分子的结构。

SDF文件除了结构式外,还可以包含分子的属性信息。

这些属性信息可以是分子的化学式、分子量、沸点、熔点等相关化学信息,也可以是分子的药物活性、毒性等药理学信息。

这些属性信息对于药物研发和分子模拟等研究具有重要意义。

SDF文件的使用非常广泛。

在药物研发领域,研究人员可以通过SDF文件存储和管理大量的药物分子信息。

在分子模拟领域,SDF文件可以用于描述和导入目标分子的结构信息,从而进行分子对接和药效预测等研究。

此外,在数据库和化学信息系统中,SDF文件也被广泛应用于存储和交换化学信息。

总结:SDF文件是一种用于存储化学结构信息的文件格式,它能够存储分子的结构式、化学信息和物理属性等多种数据。

通过连接表达式表示分子的结构,SDF文件在药物研发、分子模拟和化学信息系统中有广泛的应用。

Modelsim的功能仿真和时序仿真

FPGA 设计流程包括设计输入,仿真,综合,生成,板级验证等很多阶段。

在整个设计流程中,完成设计输入并成功进行编译仅能说明设计符合一定的语法规范,并不能说明设计功能的正确性,这时就需要通过仿真对设计进行验证。

在FPGA 设计中,仿真一般分为功能仿真(前仿真)和时序仿真(后仿真)。

功能仿真又叫逻辑仿真,是指在不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证;而时序仿真是在布局布线后进行,它与特定的器件有关,又包含了器件和布线的延时信息,主要验证程序在目标器件中的时序关系。

在有些开发环境中,如Xilinx ISE 中,除了上述的两种基本仿真外,还包括综合后仿真,转换(post-translate)仿真,映射后(post-map)仿真等,这样做完每一步都可进行仿真验证,从而保证设计的正确性。

ModelSim 是Mentor Graphics 子公司MentorTechnology 的产品,是当今最通用的FPGA 仿真器之一。

ModelSim 功能强大,它支持FPGA 设计的各个阶段的仿真,不仅支持VHDL 仿真,Verilog仿真,而且支持VHDL 和Verilog 混合仿真。

它不仅能做仿真,还能够对程序进行调试,测试代码覆盖率,对波形进行比较等。

ModelSim 有很多版本,像ModelSim/SE 是首要版本,除此之外还有ModelSim/XE 和Model Sim/AE,分别是为Xilinx公司和Altera 公司提供的OEM 版,其中已包含各公司的库文件,故用特定公司OEM 版进行仿真时就不需编译该公司的库了。

用ModelSim 进行功能仿真进行功能仿真首先要检查设计的语法是否正确;其次检查代码是否达到设计的功能要求。

下文主要介绍仿真步骤和测试激励的加载。

仿真步骤(1)建立库并映射库到物理目录因为用ModelSim 进行仿真是建立在仿真库的基础上的(此处进行的是功能仿真,因而不用编译特定厂商的库),所以首先要建立库并把库映射到实际的物理路径。

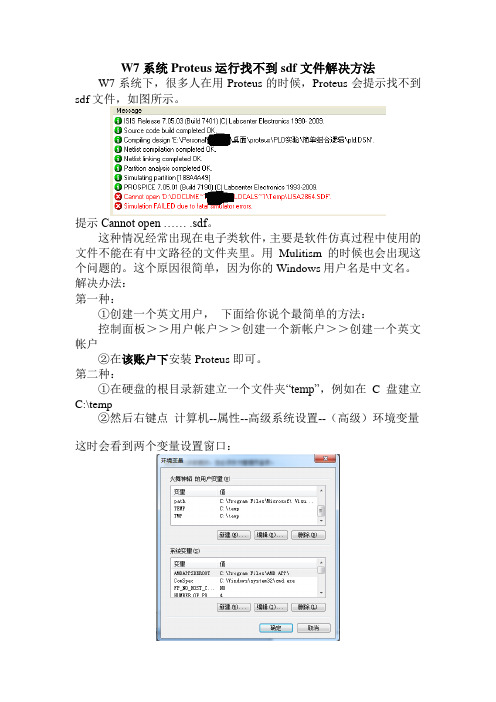

W7系统Proteus运行找不到sdf文件解决方法

W7系统Proteus运行找不到sdf文件解决方法W7系统下,很多人在用Proteus的时候,Proteus会提示找不到sdf文件,如图所示。

提示Cannot open …… .sdf。

这种情况经常出现在电子类软件,主要是软件仿真过程中使用的文件不能在有中文路径的文件夹里。

用Mulitism的时候也会出现这个问题的。

这个原因很简单,因为你的Windows用户名是中文名。

解决办法:

第一种:

①创建一个英文用户,下面给你说个最简单的方法:

控制面板>>用户帐户>>创建一个新帐户>>创建一个英文帐户

②在该账户下安装Proteus即可。

第二种:

①在硬盘的根目录新建立一个文件夹“temp”,例如在C盘建立C:\temp

②然后右键点计算机--属性--高级系统设置--(高级)环境变量这时会看到两个变量设置窗口:

一个是你自己的变量,一个是系统变量。

然后修改当前用户的变量(就是上面的窗口里的):

①找到变量TEMP 编辑为你刚才新建的目录(例如C:\temp).

②找到变量TMP 编辑为你刚才新建的目录(例如C:\temp). 如果没有就新建一个。

然后确定就可以了。

成功展示:。

sdf文件的formal电荷

sdf文件的formal电荷摘要:一、前言二、sdf 文件简介1.sdf 文件的定义2.sdf 文件的作用三、formal 电荷的概念1.formal 电荷的定义2.formal 电荷与物质性质的关系四、sdf 文件中的formal 电荷1.sdf 文件中formal 电荷的存储方式2.sdf 文件中formal 电荷的计算方法五、formal 电荷在sdf 文件中的应用1.用于分子间相互作用力的计算2.用于分子性质的预测六、总结正文:一、前言SDF(Solvent Description File)文件是用于描述分子间相互作用力的文件格式,广泛应用于分子模拟领域。

在sdf 文件中,formal 电荷是一个重要的参数,用于描述分子中各种原子的电荷性质。

本文将详细介绍sdf 文件中的formal 电荷。

二、sdf 文件简介1.sdf 文件的定义SDF 文件是一种用于描述分子间相互作用力的文件格式,可以存储分子的结构、电荷、相互作用能等信息。

SDF 文件是MOPAC(Molecular Orbital Package)软件的默认输出格式,也可以被其他分子模拟软件所读取。

2.sdf 文件的作用SDF 文件的主要作用是存储分子模拟所需的各种信息,包括分子的结构、电荷、相互作用能等,以便在进行分子模拟时使用。

通过SDF 文件,研究人员可以方便地共享和交流分子模拟结果,提高模拟的效率和准确性。

三、formal 电荷的概念1.formal 电荷的定义Formal 电荷是一种用于描述分子中各种原子的电荷性质的参数。

在分子中,每个原子都具有一定的电荷,这些电荷可以分为两部分:实际电荷和formal 电荷。

实际电荷是原子在分子中的净电荷,而formal 电荷则是用于描述原子电荷性质的一种参数,通常用于分子模拟中。

2.formal 电荷与物质性质的关系Formal 电荷与物质的许多性质密切相关。

例如,分子的几何形状、键长、键角等性质都与原子的formal 电荷有关。

SDF和Spef文件详解

External definition例子

*1:索引的名 I:输入 O:输出 B:双向端口

Internal definition

内部定义是描述内部连线 的寄生参数信息。有两种 基本的格式:D_NET和 R_NET

节点

* 5426 :连接cell*14214和*14212 *5290 *16 *5266 *5116都是与*5426连接的线

*D_NET表明5426线是采用D_NET模式计算的。*5426是 net索引,0.899466是该net上的总电容值(包括串扰电容、 负载电容或者可能包括pin电容(取决于再DESIGN_FLOW 中是否设置了PIN_CAP))。

*CONN表明段连接关系。*I表明内部的pin(*P代表的是port), *14212:D代表的是实例*14212的D pin,I代表他是*5426的负 载,*C代表的是pin的坐标,*D代表的是驱动单元,*O代表的 是*5426的驱动。

Y变化所需要的 延时,上升为 101ps,下降为 90ps

SPEF

Standard parasitic extraction format(SPEF) 功能:以ASCII exchange format描述设计的C,R ,L

产生和作用如图所示

Net model

distributed net(D_NET)model Reduced net(R_NET)model Lumped capacitance model

*CAP代表的是电容部分。有两部分组成:1~4是线间的串 扰电容;5是*5426与地之间的电容。

*RES代表的是电阻部分。

• 指定延时是单元延时信息

• ABSOLUTE:表明后续指定的值可以完全代替原值,若是 INCREMENT:代表在原值上加上指定的值。

第21章 verilog SDF时序标注

SDF标注工具

用系统任务$sdf_annotate标注SDF时序信息。 可以交互式界面调用这个任务,或在源代码中调任务。

$sdf_annotate ("sdf_file", [module_instance, "config_file"," log_file", "mtm_spec", "scale_factors"," scale_type"]); 1. 2. 3. 4. sdf_file:SDF文件的绝对或相对路径 module_instance:标注范围。缺省为调用$sdf_annotate所在的范围 config_file:配置文件的绝对或相对路径。缺省使用预设的设置。 Log_file :日志文件名,缺省为 sdf.log 。可以用 +sdf_verbose 选项生成一个日志 文件。 5. Mtm_spec :选择标注的时序值,可以是 {MINIMUM , TYPICAL , MAXIMUM , TOOL_CONTROL} 之一。缺省为 TOOL_CONTROL( 命令行选项 ) 。这个参数覆盖 配置文件中MTM关键字。 6. Scale_factors:min:typ:max格式的比例因子,缺省为1.0:1.0:1.0。这个参数覆盖 配置文件SCALE_FACTORS关键字。 7. Scale_type:选择比例因子;可以是{FROM_MINIMUM, FROM_TYPICAL, FROM_MAXIMUM, FROM_MTM}之一。缺省为FROM_MTM。这个参数覆盖配置 文件中SCALE_TYPE关键字。 注意:除sdf_file的所有参数可以忽略。sdf_file可以是任意名字,然后在运行时使用 命令行选项+sdf_file选项指定一个sdf_file。

空间分布函数sdf

空间分布函数sdf空间分布函数(Spatial Distribution Function, SDF)是描述材料或物质分布的一个重要指标。

简单来说,SDF就是用数学的方式描述物质在空间上的分布情况。

这个指标可以应用在很多领域,比如材料科学、生物学、计算机图形学等等。

下面将就SDF的概念、计算方法和应用进行详细的介绍。

1. SDF的概念SDF是一种用来描述物质在空间中分布的函数,通俗地说,就是用数学的方式描述物质在空间上的密度、分布等情况。

SDF是由坐标轴上的位置来定义的,比如二维平面上一个点的SDF值就是该点所代表的位置的密度或者分布程度。

在三维空间中,一个点的SDF值就是该点所代表的位置的密度、分布等信息的集合。

SDF通常使用函数表达式来表示,它可以用来在空间上进行建模、计算或者控制。

2. SDF的计算方法SDF的计算方法通常是通过采样技术来实现。

其基本思想就是在空间中任选一个点,然后计算出该点周围一定范围内的物质密度或分布,进而以该点处的物质密度或分布作为该点的SDF值。

在二维平面上,可以采用像素值或者网格点值作为SDF值,而在三维空间中,通常采用体素或者网格点值作为SDF值。

在实际计算中,SDF的计算方法通常是执行以下步骤:1)空间采样:选择一系列采样点或区域,这些采样点或区域可以是任意的形状和大小。

2)物质密度或分布计算:对于每个采样点或采样区域,计算其周围的物质密度或分布情况。

这可以通过各种方法来实现,比如计算距离、平均值或者概率。

3) SDF值计算:基于计算出来的物质密度或分布情况,计算该点或区域的SDF值。

4)数据存储:将计算出来的SDF值保存到内存或者磁盘中,以备后续使用。

3. SDF的应用SDF在计算机图形学中有广泛的应用,比如它可以用来构建多边形网格、计算光线与物体表面交点、进行渲染等。

SDF还可以在许多其他领域中得到应用,比如生物医学研究中用于脑部图像分析、材料科学中用于设计和优化材料的分子结构等。

sdf文件的formal电荷

sdf文件的formal电荷

SDF文件是指Structure-Data File,是一种常用的化学结构数据格式。

在SDF文件中,通常没有直接给出原子的形式电荷(formal charge)信息。

正式电荷是指原子上电子的数目与原子上与原子核结合的电子的数目之间的差异。

要计算正式电荷,需要知道原子的电子数目和结构。

可以从SDF文件中的其他信息推测出原子的形式电荷。

一种方法是使用软件工具,如化学信息软件或分子编辑器,可以读取SDF文件并计算出原子的形式电荷。

另外,某些化学数据库也可能提供了SDF文件中原子的形式电荷数据。

用户也可以使用量子化学计算方法,如从头算方法或密度泛函理论等,通过计算得到原子的形式电荷。

总之,在一般的SDF文件中,不包含原子的形式电荷信息,需要通过其他方式获得。

DC学习(11)综合产生的文件

DC学习(11)综合产⽣的⽂件⼀:综合产⽣的⽂件 前⾯也讲了⼀些综合后的需要进⾏的⼀些⼯作,这⾥就集中讲⼀下DC完成综合了,产⽣了⼀些⽂件,我们就要查看它⽣成的⽹表和信息,下⾯就来介绍DC综合完成之后要进⾏哪些⼯作:也就是说,DC⼀般完成综合后,主要⽣成.ddc、.def、.v和.sdc,.sdf格式的⽂件(当然还有各种报告和log).sdc⽂件:write_sdc -version 1.7 filename.sdc 标准延时约束⽂件: ⾥⾯都是⼀些约束,⽤来给后端的布局布线提供参考。

Scan_def.def⽂件:DFT、形式验证可能⽤到 ⾥⾯包含的是⼀些扫描链的布局信息,需要注意的是,必须在⽣成ddc⽹表⽂件之前⽣成.def(也就先⽣成.def⽂件),以便将def⽂件包含在ddc⽂件中。

.sdf、.v⽂件:write_sdf -version 2.1 filename.sdf; write -f verilog -hierarchy output filename.v标准延时格式和⽹表格式⽂件,⽤于后仿真。

下⾯是输出(⽣成)⽂件的⼀些命令:1:综合⽹表的处理: 完成综合并通过时序等的分析后,我们需要把设计和约束以某种格式存储好,作为后端⼯具的输⼊。

把设计以VHDL或Verilog格式存档时,需要去掉或避免⽂件中有assign指令,因为该指令会使⾮Synopsys公司的⼯具在读⼊⽂件时产⽣问题。

该指令也可能会在反标( back-annotation)流程中产⽣问题。

此外,要保证⽹表中没有特别的字符。

例如,写出⽹表时,有时⽹表中会有反斜线符号“\”,对于这个符号,不同的⼯具有不⼀样的理解。

·assign:多端⼝连线(multiple port nets)会在⽹表中⽤assign指令表⽰,如下图所⽰: 上⾯的设计中有冗余的端⼝(包括内部端⼝,⼜称层次引脚)。

如果我们将设计展开(flatten), DC可能把它们优化掉,即去掉这些端⼝。

使用ChemDraw与ChemFinder创建组合化学库

使用ChemDraw与ChemFinder创建组合化学库作者:Jesse Gordon公司:CambridgeSoft Corporation期刊号:20。

4CHEMDRAW与CHEMFINDER的COMBINING FUNCTIONALITY功能可以创建组合化学库并可对其中每种物质的性质做出初步预测,这篇文章将介绍以下内容:1.在ChemDraw中展开化学结构的通式(generic structure)2.将展开的结构式以SDF格式导出3.将SDF导入到ChemFinder中作为本地化学数据库4.使用ChemFinder为每个结构式计算化学性质和名称5.创建含有更多组合元素的化学结构通式6.将新创建的SDF导入到ChemDraw/Excel中7.使用ChemDraw/Excel为每个结构式计算化学性质和名称这篇文章使用ChemDraw/Excel的工作环境为Microsoft Excel 2003,Windows XP系统;您当然也可以在Microsoft Excel 2007以及Windows7系统中使用此功能。

这里我们选用ChemBioDraw Ultra 12及ChemBioFinder Ultra12对数据进行处理。

但ChemDraw Ultra与Pro版本也提供上文所述的“展开结构通式(Expand Generic Structure)”功能,要注意的是ChemDraw Std没有此功能。

还需注意ChemDraw/Excel功能也有限制,如ChemDraw Ultra有此功能,但ChemDraw Pro没有此功能。

详细的功能说明,请参阅用户手册。

1.在ChemDraw中展开化学结构的通式让我们从一个简单的化学结构通式开始,如下图所示,可以展开成12个结构式未展开的结构通式我们的目标是用展开的12个结构创建一个化学数据库,预测他们的沸点及熔点并进行对比。

我们还将为这12个结构命名。

首先我们使用ChemDraw的“Expand Generic Structure”功能,可以将上图的通式展开为下图所示的12个结构式:展开的结构通式在ChemDraw中,可以为每个结构式计算熔点,沸点并为其分配一个系统名,但只能对每个结构式逐个执行这些操作.而我们的目的是将上述步骤一次性完成。

gazebo sdf collision 摩擦力

Gazebo SDF Collision 摩擦力摩擦力是物体相互接触时产生的阻力,它在物理学中扮演着重要的角色。

在仿真环境中,准确地模拟摩擦力对于实现真实世界的物体交互和运动非常关键。

Gazebo是一个广泛使用的开源机器人仿真软件,它允许用户通过SDF(Simulation Description Format)文件定义并模拟复杂的机器人系统。

Gazebo提供了强大的工具和功能来模拟摩擦力,以使仿真更加真实和准确。

在Gazebo中,物体之间的碰撞是通过collision元素来定义的。

collision元素允许用户指定碰撞体的形状、大小和位置。

但是,如果没有正确定义摩擦力,碰撞体之间的物理交互可能会变得不准确。

因此,Gazebo提供了一种以SDF文件定义摩擦力的简单而强大的方法。

在SDF文件中,可以通过给collision元素添加以下元素来定义摩擦力:1.friction 元素:用于定义静摩擦系数和动摩擦系数。

静摩擦系数是当物体处于静止状态时产生的摩擦力,而动摩擦系数是当物体处于运动状态时产生的摩擦力。

这些系数对于准确模拟物体之间的摩擦力非常重要。

2.friction_anchor 元素:用于定义摩擦锚点在碰撞体中的位置。

摩擦锚点是用来计算碰撞体间摩擦力的参考点。

通过设置摩擦锚点的位置,可以影响模拟中物体之间的摩擦力分布。

利用这些元素,用户可以在SDF文件中定义不同物体之间的摩擦力。

例如,当模拟两个金属物体之间的碰撞时,可以设置较高的静摩擦系数和动摩擦系数,以模拟金属物体之间的高摩擦力。

而在模拟一个冰球在冰面上滑动时,可以设置较低的静摩擦系数和动摩擦系数,以模拟冰面上的低摩擦力。

Gazebo还提供了强大的摩擦力控制工具,以便用户可以根据需要自定义摩擦力模型。

用户可以编写自定义插件来修改摩擦力模型,以实现更高级的仿真需求。

这使得在Gazebo中模拟各种摩擦力行为成为可能,从而更好地模拟真实世界中物体之间的摩擦力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(CELLTYPE "MX21D1A")

(INSTANCE a0208a_fpga_ctrl\/U245)

(DELAY

(ABSOLUTE

(IOPATH A YN (0.306678:0.306678:0.322323) (0.374293:0.393043:0.399604))

/////////////////////////pearl.cmd///////////////////////////////////////////////////////////

LogFile ./pearl.log

SetGroundNode GND

SetPowerNode VDD

set_operating_conditions -process 1.0 -voltage 5.0 -temperature 125.0

set_voltage_threshold 10 90

readtlf /export/home/tlf/lib_core_xxxx.tlf

.......

///////////////////////////////////////////////////////////////////////

2.使用cadence tools pearl 将xxxx.wscr(synopsys format)------->xxxx.gcf(cadence delayformat)

(2): 使用pearl运行脚本

////////////////////////////////////////

在terminal中输入:

pearl -cc -tcl pearl.cmd -l run.log

///////////////////////////////////////

注意:lib_core_xxxx.tlf lib_pad_xxxx.tlf由流片厂家提供,如果没有找厂家要

set_false_path -from [get_pins por_module/por]

set_input_delay -clock ringosc 12 [get_ports pin_a]

set_output_delay -clock ringosc 28 [get_ports pin_b]

(INTERCONNECT U288/PAD CTRL0 (0.000000:0.000000:0.000000) (0.000000:0.000000:0.000000))

.........................................

..........................................

create_clock [get_pins ring_module/ringosc] -name ringosc -period 40 -waveform {0 20}

create_clock [get_ports VON_IN_in] -period 400 -waveform {0 200}

)

)

)

.............

/////////////////////////////////////////////////

肯定有单元信息

--------------Title:gcf----------------------------

--------------data:2008.1.23-----------------------

--------------假设我们现在用一个xxxx.v的rtl文件----

---------------------------------------------------

set_clock_uncertainty \

set_clock_latency \

set_dont_touch_network \

set_fix_multiple_port_nets \

set_wire_load_model \

read_dc_script -effort_level high xxxx.wscr

write_gcf xxxx.gcf

////////////////////////////////////////////////////////////////////////////////////////////

xxxx.v是综合一个的门级网表

3.在se 中导入xxxx.gcf文件

(1):input lib.lef

(2):input xxxx.v

(3):input xxxx.gcf

(4):input xxxx.def

...............

(n):output xxxx.gds2 & xxxx.sdf

set_local_link_library \

set_fix_multiple_port_nets \

set_scan_configuration \

set_ideal_network \

set_switching_activity }

(TIMESCALE 1ns)

(CELL

(CELLTYPE "xxxxx")

(INSTANCE)

(ELAY

(ABSOLUTE

(INTERCONNECT U287/PAD CTRL1 (0.000000:0.000000:0.000000) (0.000000:0.000000:0.000000))

xxxx.sdf 文件格式如下:

////////////////////////////////////////////////

(DELAYFILE

(SDFVERSION "2.1")

(DESIGN "xxxx")

(DATE "November 28, 2006 16:53:0")

////////////////////////////////////////////////////////////////////

xxxx.wscr文件如以下文件格式:

/////////////////////////////////////////////////////////////////////////////////////////

(VENDOR "")

(PROGRAM "PEARL")

(VERSION "PEARL 5.1-p058")

(DIVIDER /)

(VOLTAGE 5.000:5.000:5.000)

(PROCESS "1.000:1.000:1.000")

(TEMPERATURE 125.000:125.000:125.000)

--------------请用记事本打开-----------------------

---------------------------------------------------

1.在dc综合结束时,使用以下命令产生xxxx.wscr文件。

write_script -format dcsh -output xxxx.wscr

xxxx.gcf 文件用于cadence se P&R

///////////////////////////////////////////////

(1):编辑一个转换脚本pearl.cmd

//////////////////////////////////////////////////////////////////////////////////////////////

(IOPATH B YN (0.335283:0.353517:0.353517) (0.373138:0.386991:0.387034))

(IOPATH S YN (0.582179:0.691204:0.794927) (0.590671:0.659827:0.725619))

readtlf /export/home/tlf/lib_pad_xxxx.tlf

ReadVerilog /export/home/dc_outputs/xxxx.v

TopLevelCell xxxx

set dc_shell_ignored_command_list {\