第20章习题1-门电路和组合逻辑电路

门电路及组合逻辑电路ppt课件.ppt

用四位自然二进制码中的前十个码字来表示十进制数码, 因各位的权值依次为8、4、2、1,故称8421码。

2421码的权值依次为2、4、2、1;余3码由8421码加0011 得到;格雷码是一种循环码,其特点是任何相邻的两个码字, 仅有一位代码不同,其它位相同。

即:(5555)10=5×103 +5×102+5×101+5×100 又如:(209.04)10= 2×102 +0×101+9×100+0×10-1+4 ×10-2

(1)数制:二进制

数码为:0、1;基数是2。 运算规律:逢二进一,即:1+1=10。 二进制数的权展开式: 如:(101.01)2= 1×22 +0×21+1×20+0×2-1+1 ×2-2

A

&

B

≥1 &

C

&

D

(a) 与或非门的构成

A

FB C

& ≥1 F

D

(b) 与或非门的符号

F AB CD

4、异或

异或是一种二变量逻辑运算,当两个变量取值相同时, 逻辑函数值为0;当两个变量取值不同时,逻辑函数值为1。

异或的逻辑表达式为: L A B

“异或”真值

表 输入

输出

A

B

L

A

=1

0

0

0

0

常用 BCD 码

十进制数 8421 码 余 3 码 格雷码 2421 码

0

0000 0011 0000 0000

1

0001 0100 0001 0001

2

0010 0101 0011 0010

(完整版)第20章习题1-门电路与组合逻辑电路

第20章习题 门电路和组合逻辑电路S10101B为实现图逻辑表达式的功能,请将TTL 电路多余输入端C 进行处理(只需一种处理方法),Y 1的C 端应接 ,Y 2的C 端应接 ,解:接地、悬空S10203G在F = AB +CD 的真值表中,F =1的状态有( )。

A. 2个 B. 4个 C. 3个 D. 7个 解:DS10203N某与非门有A 、B 、C 三个输入变量,当B =1时,其输出为( )。

A. 0 B. 1 C. AC D. AC 解:CS10204B在数字电路中,晶体管的工作状态为( )。

A. 饱和 B. 放大 C. 饱和或放大 D. 饱和或截止 解:DS10204I逻辑电路如图所示,其逻辑函数式为( )。

A. B A B A +B. AB B A +C. B A B A +D. A AB + 解:CS10204N已知F =AB +CD ,选出下列可以肯定使F = 0的情况( )。

A. A = 0,BC = 1 B. B = C = 1 C. C = 1,D = 0 D. AB = 0,CD = 0 解:DS10110B三态门电路的三种可能的输出状态是 , , 。

解:逻辑1、逻辑0、高阻态1&B1&≥1逻辑图和输入A ,B 的波形如图所示,分析当输出F 为“1”的时刻应是( )。

A. t 1B. t 2C. t 3解:AS10211I图示逻辑电路的逻辑式为( )。

A. F =A B AB +B. B A AB F =C. F =()A B AB + 解:BS10212I逻辑电路如图所示,其功能相当于一个( )。

A. 门B. 与非门C. 异或门 解:CS10216B图示逻辑电路的逻辑式为( )。

A. F =A B +A BB. F =AB AB +C. F =AB +A B 解:CS10217B逻辑图如图(a )所示,输入A 、B 的波形如图(b ),试分析在t 1瞬间输出F 为( )。

电工学第20章门电路和组合逻辑电路

将输入变量所有的取值下对应的输出值找出来,列成表格, 王

即可得到逻辑状态表。

亚

军

制

作

电 工

20.2 基本门电路及其组合

学

I

电 子

一、逻辑电路的基本概念

技

术 部

4 逻辑函数

分 如果以逻辑运算中的逻辑变量作为输入,以运算结果作为输

出,当输入变量的取值确定后,输出的取值便随之而定。因

此,输出与输入是一种函数关系。这种函数关系称为逻辑函

技

术 部

1 二极管与门电路

分 • 与门逻辑状态表

AB

Y AB

Y

00

0

10

0

01

0

11

1

哈

• 与门逻辑符号

理 工

A

大

Y

学

B

王

• 与门逻辑函数式

亚 军

Y = A B

制 作

电 工

20.2 基本门电路及其组合

学

I

电 子

二、分立元器件基本逻辑门电路

技

术 部

2 二极管或门电路

分 • 或逻辑:在决定某一事件的各种条件中,只要有一个或一

Y1 Y2

与非门

哈

理

工

或非门

大

学

王 亚 军 制 作

电 工

20.3 TTL门电路

学

I

电 子

一、TTL与非门电路

1 TTL74系列与非门逻辑电路

技

术 部

+5 V

分

R1

R2

R4

T3

A B

T1

T2

D3

哈

Y

理 工

大

(完整版)第20章习题1-门电路与组合逻辑电路

第20章习题 门电路和组合逻辑电路S10101B为实现图逻辑表达式的功能,请将TTL 电路多余输入端C 进行处理(只需一种处理方法),Y 1的C 端应接 ,Y 2的C 端应接 ,解:接地、悬空S10203G在F = AB +CD 的真值表中,F =1的状态有( )。

A. 2个 B. 4个 C. 3个 D. 7个 解:DS10203N某与非门有A 、B 、C 三个输入变量,当B =1时,其输出为( )。

A. 0 B. 1 C. AC D. AC 解:CS10204B在数字电路中,晶体管的工作状态为( )。

A. 饱和 B. 放大 C. 饱和或放大 D. 饱和或截止 解:DS10204I逻辑电路如图所示,其逻辑函数式为( )。

A. B A B A +B. AB B A +C. B A B A +D. A AB + 解:CS10204N已知F =AB +CD ,选出下列可以肯定使F = 0的情况( )。

A. A = 0,BC = 1 B. B = C = 1 C. C = 1,D = 0 D. AB = 0,CD = 0 解:DS10110B三态门电路的三种可能的输出状态是 , , 。

解:逻辑1、逻辑0、高阻态1&B1&≥1逻辑图和输入A ,B 的波形如图所示,分析当输出F 为“1”的时刻应是( )。

A. t 1B. t 2C. t 3解:AS10211I图示逻辑电路的逻辑式为( )。

A. F =A B AB +B. B A AB F =C. F =()A B AB + 解:BS10212I逻辑电路如图所示,其功能相当于一个( )。

A. 门B. 与非门C. 异或门 解:CS10216B图示逻辑电路的逻辑式为( )。

A. F =A B +A BB. F =AB AB +C. F =AB +A B 解:CS10217B逻辑图如图(a )所示,输入A 、B 的波形如图(b ),试分析在t 1瞬间输出F 为( )。

电工学习题2014_下册

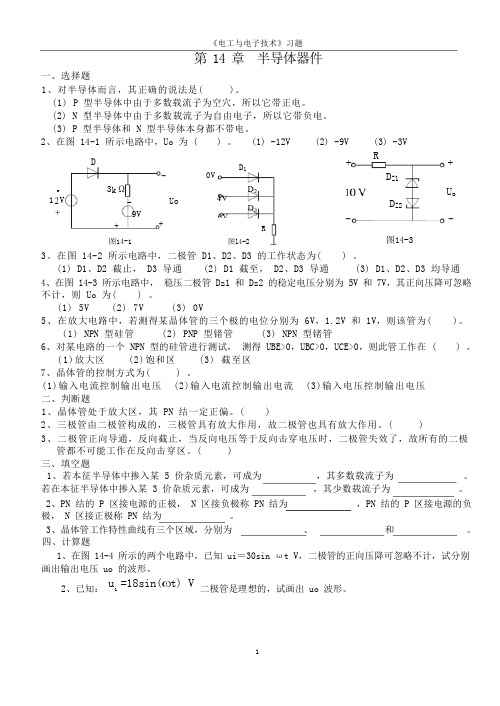

第 14 章半导体器件一、选择题1、对半导体而言,其正确的说法是( )。

(1) P 型半导体中由于多数载流子为空穴,所以它带正电。

(2) N 型半导体中由于多数载流子为自由电子,所以它带负电。

(3) P 型半导体和 N 型半导体本身都不带电。

2、在图 14-1 所示电路中,Uo 为 ( ) 。

(1) -12V (2) -9V (3) -3VR- 0V D Z11V 3kΩ-9VUo DZ2U o + + R- -图14-1 图14-2 图14-33、在图 14-2 所示电路中,二极管 D1、D2、D3 的工作状态为( ) 。

(1) D1、D2 截止, D3 导通 (2) D1 截至, D2、D3 导通 (3) D1、D2、D3 均导通4、在图 14-3 所示电路中,稳压二极管 Dz1 和 Dz2 的稳定电压分别为 5V 和 7V,其正向压降可忽略不计,则 Uo 为( ) 。

(1) 5V (2) 7V (3) 0V5、在放大电路中,若测得某晶体管的三个极的电位分别为 6V,1.2V 和 1V,则该管为( )。

(1) NPN 型硅管 (2) PNP 型锗管 (3) NPN 型锗管6、对某电路的一个 NPN 型的硅管进行测试,测得 UBE>0,UBC>0,UCE>0,则此管工作在 ( ) 。

(1)放大区 (2)饱和区 (3) 截至区7、晶体管的控制方式为( ) 。

(1)输入电流控制输出电压 (2)输入电流控制输出电流 (3)输入电压控制输出电压二、判断题1、晶体管处于放大区,其 PN 结一定正偏。

( )2、三极管由二极管构成的,三极管具有放大作用,故二极管也具有放大作用。

( )3、二极管正向导通,反向截止,当反向电压等于反向击穿电压时,二极管失效了,故所有的二极管都不可能工作在反向击穿区。

( )三、填空题1、若本征半导体中掺入某 5 价杂质元素,可成为,其多数载流子为。

若在本征半导体中掺入某 3 价杂质元素,可成为,其少数载流子为。

第二十章 门电路和组合逻辑电路

回主页 总目录 章目录 上一页 下一页 退出

20.1 脉冲信号

在数字电路中,信号(电压和电流)是脉冲的. 在数字电路中,信号(电压和电流)是脉冲的. 脉冲是一种跃变信号,并且持续时间短暂. 脉冲是一种跃变信号,并且持续时间短暂. 是一种跃变信号

矩形波

尖顶波

回主页 总目录 章目录 上一页 下一页 退出

20.1 脉冲信号

以矩形波为例说明脉冲信号波形的一些参数

0.9A A 0.1A tr tf

脉冲幅度 A:脉冲信号变化的最大值. :脉冲信号变化的最大值. 从脉冲幅度的10%上升到 上升到90%所 脉冲上升时间 tr :从脉冲幅度的 上升到 所 需的时间. 需的时间. 从脉冲幅度的90%下降到 下降到10%所 脉冲下降时间 tf :从脉冲幅度的 下降到 所 需的时间. 需的时间.

回主页 总目录 章目录 上一页 下一页 退出

20.1 脉冲信号

0.9A 0.5A 0.1A tr T tf tp A

从上升沿的脉冲幅度的50%到下降沿 脉冲宽度 tp:从上升沿的脉冲幅度的 到下降沿 的脉冲幅度的50%所需的时间. 所需的时间. 的脉冲幅度的 所需的时间 脉冲周期 T:周期性脉冲信号相邻两个上升沿(或 :周期性脉冲信号相邻两个上升沿( 下降沿)的脉冲幅度的10%两点之间的时间间隔. 下降沿)的脉冲幅度的 两点之间的时间间隔. 两点之间的时间间隔 单位时间的脉冲数. 脉冲频率 f :单位时间的脉冲数.

讲课4学时,习题1学时. 讲课4学时,习题1学时.

回主页 总目录 章目录 上一页 下一页 退出

模拟信号: 模拟信号:电信号在时间上或数值上是连续变化 如温度和速度. 的,如温度和速度. 模拟电路:处理模拟信号的电路. 模拟电路:处理模拟信号的电路. 数字信号: 数字信号:电信号在时间上和数值上都是不连续 变化的,即所谓离散的,如尖顶波,矩形波. 变化的,即所谓离散的,如尖顶波,矩形波. 数字电路:处理数字信号的电路. 数字电路:处理数字信号的电路.

电工学20章题库组合逻辑电路+答案

5、表示组合逻辑电路逻辑功能的方法主要有:

、

状态。

。

、

及

卡诺图四种。 6 、 根 据 反 演 规 则, 直接 写 出 函 数 F = A + BC + CD 的 反 函 数 (不 必 化 简 ), F = _________。 7、函数 F = A + AB + A(C + D) ,利用反演规则直接写出其反函数(不必化简)为 F = ___________________________。 8、CMOS 或非门不用的多余输入端的处理方法有:____________________。

15、 F = AB + AC + BC 的最小项表达式为 F=__________________________。

16、一般 TTL 门和 CMOS 门相比,

门的带负载能力强,

门的工作速度快。

17、四位二进制数输出的编码器应有__________个编码输入。

18、由 n 个变量构成的任意一个最小项,有

D、同或门

3、TTL 与非门多余输入端的处理方法,下列说法不正确的是__________。

A.接地

B.接电源电压

C.悬空

D.并联使用

4、 F = AB + C 的最小项表达式为__________。

A、 F = ABC + ABC

B、 F = ABC + ABC + ABC

C、 F = ABC + ABC + ABC + ABC + ABC

D、Y=Σm(1,3,5,6)

为______________。

22、TTL 与非门的多余输入端悬空时,相当于输入______电平。

习题册参考答案-《数字电路基础(第二版)习题册》-A05-3097.docx

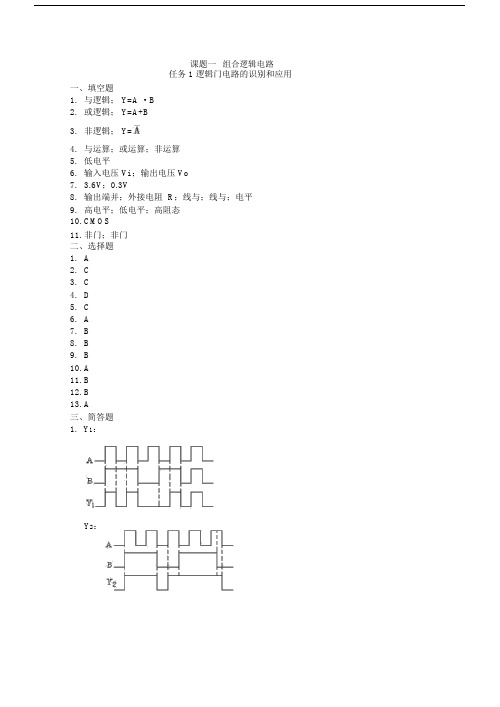

课题一组合逻辑电路任务 1 逻辑门电路的识别和应用一、填空题1.与逻辑; Y=A ·B2.或逻辑; Y=A+B3.非逻辑; Y=4.与运算;或运算;非运算5.低电平6.输入电压 Vi ;输出电压 Vo7. 3.6V;0.3V8.输出端并;外接电阻 R;线与;线与;电平9.高电平;低电平;高阻态10.CMOS11.非门;非门二、选择题1. A2. C3. C4. D5. C6. A7. B8. B9. B10.A11.B12.B13.A三、简答题1. Y1:Y2:2.真值表逻辑函数式Y=ABC 3.真值表逻辑表达式Y1=ABY2=Y3= A+B逻辑符号4.5.任务 2 组合逻辑电路的分析和设计一、填空题1.高电平;低电平2.输入逻辑变量的各种可能取值;相应的函数值排列在一起3.逻辑变量;与;或;非4.两输入信号;异或门电路5.代数;卡诺图6.A+B+C ;A;A7.( 1) n; n;(2)原变量;反变量;一;一8.与或式; 1; 09.组合逻辑电路;组合电路;时序逻辑电路;时序电路10.该时刻的输入信号;先前的状态二、选择题1. D2. C3. C4. A5. A三、判断题1.×2.√3.√4.√5.×6.√7.×四、简答题1.略2.( 1) Y=A+ B(2)Y=AB + A B(3)Y=ABC+A + B +C+D=A + B +C+D3. (1)Y=A B C+ABC+ABC+ABC= A C+AC(2) Y= A CD+A B D + D+ACDAB(3)Y=C+ AB+AB4.状态表逻辑功能:相同出1,不同出 0逻辑图5.( a)逻辑函数式Y=AB+ A B真值表逻辑功能:相同出1,不同出 0(b)逻辑函数式 Y=AB+BC+AC真值表逻辑功能:少数服从多数电路,即三人表决器。

6.Y=A ABC +B ABC +C ABC判不一致电路,输入不同,输出为1,;输入相同,输出为0。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第20章习题 门电路和组合逻辑电路S10101B为实现图逻辑表达式的功能,请将TTL 电路多余输入端C 进行处理(只需一种处理方法),Y 1的C 端应接,Y 2的C 端应接 ,解:接地、悬空S10203G在F = AB +CD 的真值表中,F =1的状态有( )。

A. 2个 B. 4个C. 3个D. 7个解:DS10203N某与非门有A 、B 、C 三个输入变量,当B =1时,其输出为( )。

A. 0 B. 1C. ACD. AC解:CS10204B在数字电路中,晶体管的工作状态为( )。

A. 饱和 B. 放大C. 饱和或放大D. 饱和或截止解:DS10204I逻辑电路如图所示,其逻辑函数式为( )。

A. B A B A +B. AB B A +1&Y1&≥1C. B A B A +D. A AB +解:CS10204N已知F =AB +CD ,选出下列可以肯定使F = 0的情况( )。

A. A = 0,BC = 1B. B = C = 1C. C = 1,D = 0D. AB = 0,CD = 0解:DS10110B三态门电路的三种可能的输出状态是 , , 。

解:逻辑1、逻辑0、高阻态S10214B逻辑图和输入A ,B 的波形如图所示,分析当输出F 为“1”的时刻应是( )。

A. t 1B. t 2C. t 3解:A S10211I图示逻辑电路的逻辑式为( )。

A. F =A B AB + B. B A AB F =C. F =()A B AB +解:B S10212I逻辑电路如图所示,其功能相当于一个( )。

A. 门B. 与非门C. 异或门 解:CS10216B图示逻辑电路的逻辑式为( )。

A. F =A B +A BB. F =AB AB +C. F =AB +A B 解:CS10217B逻辑图如图(a )所示,输入A 、B 的波形如图(b ),试分析在t 1瞬间输出F 为( )。

A. “1”B. “0”C. 不定 解:B S10218B图示逻辑符号的逻辑状态表为( )。

A.B.C.解:BABFA BFABF0 0 0 0 0 0 0 0 1 0 1 0 0 1 1 0 1 1 1 0 0 1 0 1 1 0 1 11111111S10219B逻辑图和输入A的波形如图所示,输出F的波形为( )。

解:(b)S10220B图示逻辑符号的状态表为( )。

A. B. C.解:CS10221B逻辑图和输入A,B的波形如图所示,分析当输出F为“1”的时刻,应是( )。

A.t1B.t2C.t3解:AS10225B逻辑门电路的逻辑符号如图所示,能实现F=AB逻辑功能的是( )。

解:(a)S10214I逻辑图和输入A,B的波形如图所示,分析当输出F为""0的时刻应是( )。

A.t1A B FA B F A B F 000000001 010011011 100101101 111111110B. t2C. t3解:C S10217I图示逻辑电路的逻辑式为( )。

A. C AB F +=B. C B A F )(+=C. C AB F +=解:A S10221I逻辑图和输入A ,B 的波形如图所示,分析当输出F 为“0”的时刻应是( )。

A. t 1B. t 2C. t 3解:C S10222I逻辑图和输入A ,B 的波形如图所示,分析当输出F 为“0”的时刻应是( )。

A. t 1B. t 2C. t 3解:BS10226B三态输出“与非”门电路的输出比正常的“与非”门电路多一个状态是( )。

A. 高电平 B. 低电平C. 高阻解:CS10229B逻辑图和输入A ,B 的波形如图所示,分析当输出F 为“1”的时刻应是( )。

A. t 1B.t 2 C.t 3解:CS10209B逻辑符号如图所示,其中表示“与非”门的是( )。

解:(d )S10210B“异或”门的逻辑式为( )。

A. F =AB +ABB. F =AB +ABC. F =AB AB +解:CS10223I图示逻辑电路的逻辑式为( )。

A. )(C B A F ⋅= B. )(C B A F +=C. BC A F +=解:AS10401I已知各逻辑门输入A 、B 和输出F 的波形如下图所示,要求写出F 的逻辑表达式,并画出逻辑电路。

解S10503B写出如图所示电路的输出函数Y 的表达式,并分析逻辑功能。

解:逻辑函数Y 的表达式ABC Y =1CB A ABC C B A ABC C B A ABC ABC C ABC B ABC A CY BY AY Y +=+++=++=++=++=)()(111列出真值表:A B CYA B CY0 0 0 1 1 0 0 0 0 0 1 0 1 0 1 0 0 1 0 0 1 1 0 0 0 1 11 1 11Y = 1,否则Y = 0。

即该电路具有“判一致”的逻辑功能。

S10504B证明图(a )、(b )两电路具有相同的逻辑功能。

解:图(a )逻辑函数Y 的表达式B A B A Y +=图(b )逻辑函数Y 的表达式BA B A B B B A B A A A B A B A Y +=+++=++=))((可见,两电路具有“异或”的逻辑功能。

S10505G为提高报警信号的可靠性,在有关部位安置了3个同类型的危险报警器,只有当3个危险报警器中至少有两个指示危险时,才实现关机操作。

试画出具有该功能的逻辑电路。

解:在危急情况下,报警信号A 、B 、C 为高电平1,且当输出状态F 为高电平1时,设备应关机。

其真值表如下:由真值表可写出“与或”表达式:ABC BC A C B A C AB L +++=化简为:AC BC AB L ++= 逻辑图,如下图所示。

或者:用与非门AC BC AB L ++==AC BC AB ++=AC BC AB ⋅⋅其逻辑电路略。

S10504N某设备有开关A 、B 、C ,要求:只有开关A 接通的条件下,开关B 才能接通;开关C 只有在开关B 接通的条件下才能接通。

违反这一规程,则发出报警信号。

设计一个由“与非门”组成的能实现这一功能的报警控制电路。

解:由题意可知,该报警电路的输入变量是三个开关A 、B 、C 的状态,设开关接通用1表示,开关断开用0表示;设该电路的输出报警信号为F ,F 为1表示报警,F 为0表示不报警。

可列出真值表:根据真值表做出卡诺图如下图(a )所示。

利用卡诺图对逻辑函数进行化简,得到最简逻辑表达式:C B B A C B B A F ⋅=+=根据逻辑表达式画出逻辑图,就得到题目所要求的控制电路如图(b )所示。

S10405G可否将“与非门”、“或非门”、“异或门”当做“反相器”使用如果可以,其输入端应如何处理并画出电路图。

C B AL0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 10 0 0 1 0 1 1 1A B CF0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 10 1 1 1 0 1 0 0解:如右图所示。

组合逻辑电路的设计步骤为:(1) ;(2) ;(3)简化和变换逻辑表达式,从而画出逻辑图。

解:⑴由电路的功能要求,列出真值表;(2)由真值表写出逻辑表达式;S11102B分析组合逻辑电路的步骤为:(1) ;(2) ;(3) ;(4)根据真值表和逻辑表达对逻辑电路进行分析,最后确定其功能。

解:由逻辑图写出个输出端逻辑表达式、化简和变换各逻辑表达式、列出真值表S11102I如图所示逻辑图,逻辑表达式1F = ;F = 。

解:01101==⋅⋅=A F ;B B F F =+=1S11201I如图所示逻辑电路其逻辑表达式为( )。

A. B A Y +=B. ))((B A B A Y +⋅=C. ()B A Y ⋅=D. ()()B A B A Y +⋅⋅=解:D组合逻辑电路任何时刻的输出信号与该时刻的输入信号( ),与电路原来所处的状态( )。

A. 无关,无关B. 无关,有关C. 有关,无关D. 有关,有关解:CS11202I半加器的本位和输出端的逻辑关系是( )。

A. 与非B. 或非C. 与或非D. 异或解:D已知CD ABC F +=选出下列可以肯定使0=F 的情况是( )。

A. 1,0==BC AB. 1,1==C BC. 0,1==D CD. 1,1==D BCE. 0,1==CD AB 解:DS11203N图示为一简单的编码器,其中E 、F 、G 是一般信号,A 、B 是输出量,为二进制代码变量。

今令 AB = 10 ,则输入的信号为1的是( )。

A. EB. FC. G 解:BS11301B编码器,译码器,数据选择器都属于组合逻辑电路。

( )解:√S11301N全加器的输出不仅取决于输入,同时还取决于相邻低位的进位,因此说全加器属于时序逻辑电路。

( )解:×S11302B用二进制代码表示某一信息称为编码。

反之把二进制代码所表示的信息翻译出来称为译码。

( ) 解:√S11302G在下列电路中,试问哪些电路能实现B A Y ⊕=的逻辑关系解:A.√、B.×、C.×S11102G一个三变量排队电路,在同一时刻只有一个变量输出,若同时有两个或两个以上变量为1时,则按A 、B 、C 的优先顺序通过,若F A =1表示A 通过,F B 、F C 为1表示B 、C 通过,F A 、F B 、F C 为0时表示其不通过,则表示变量A 、B 、C 通过的表达式:F A = ,F B = ,F C = 。

解:A 、B A 、C B AS11213B半加器逻辑符号如图所示,当A “0”,B “0”时,C 和S 分别为( )。

A. 0=C 、1=SB. 1=C 、0=SC. 0=C 、0=S解:CS11218B半加器的逻辑图如下,指出它的逻辑式为( )。

A. B A S ⊕=、AB C =B. B A B A S +=、B A C =C. B A S ⊕=、AB C =解:AS11219B 全加器逻辑符号如图所示,当A i =“1”,B i =“1”,C i-1=“1”时,C i 和S i 分别为( )。

A. C i = 1 、S i = 0B. C i = 0 、S i = 1C. C i = 1 、S i = 1解:CS11207B全加器逻辑符号如图所示,当A i =“1”,B i =“1”,C i-1=“0”时,C i 和S i 分别为( )。

A. C i = 0、S i =0 B. C i =1、S i =1C. C i =1、S i =0解:CS11206B半加器逻辑符号如图所示,当A “1”,B “1”时,C 和S 分别为( )。