晶振layout规则

pcb layout 基本规则

pcb layout 基本规则1.CLK(包括DDR-CLK)基本走线要求: 1. clk 部分不可过其它线, Via不超过两个. 2. 不可跨切割,零件两Pad 间不能穿线. 3. Crystal 正面不可过线,反面尽量不过线.. 4. Differential Pair 用最小间距平行走线.且同层5 clk 与高速信号线(1394,usb 等)间距要大于50mil.2. VGA:基本走线要求: 1. RED、GREEN、BLUE 必须绕在一起,视情况包GND. R.G.B 不要跨切割。

2 HSYNC、VSYNC 必须绕在一起, 视情况包GND.3. LAN:基本走线要求 1.同一组线,必须绕在一起。

2 Net: RX,TX:必须differential pair 绕线4.1394:基本走线要求: 1. Differential pair 绕线,同层,平行,不要跨切割. 2.同一组线,必须绕在一起。

3 与高速信号线间距不小于50mil5. USB:基本走线要求: 1 Differential pair 绕线,同层,平行,不要跨切割. 2 同一组线,必须绕在一起6. CPU-NB (AGTL):基本走线要求: 1. 同组同层或同组不同层走线,绕线须同组绕在一起 2. 绕线时,同一NET 间距不小于四倍线寛 3. NET 长度要加入CPU & NB 的包装长度. 4. STB N/P(+/-) DifferentialPair 绕线 5 VIA 类型为VIA267. CPU-SB:基本走线要求: 1. 同一组线,必须绕在一起. 2 pull up 电阻,必须靠近CPU8. NB-DDR:基本走线要求:1.阻尼电阻和终端电阻(排阻)NET: MD & MA & DQS & DQM 不能共享. 2.同组同层走线,采用四倍间距绕线.9. NB-AGP:基本走线要求: 1.同组同层或同组不同层走线,绕线须同组绕在一起 2.绕线时,同一NET 间距不小于四倍线寛 3.STB +/- Differential Pair 绕线. 4 在constraint area 尽量按guide lauout .10. NB-SB:基本走线要求: 1 走在一起,不要跨切割线. 2.绕线时,同一NET 间距不小于四倍线寛11. IDE:基本走线要求: 1.同组同层, 绕线须同组绕在一起. 2.绕线时,同一NET 间距不小于四倍线寛12. PCI:基。

电子基础知识-晶振

一、晶振晶振在电路板中随处可见,只要用到处理器的地方就必定有晶振的存在,即使没有外部晶振,芯片内部也有晶振。

1、晶振概述晶振一般指晶体振荡器。

晶体振荡器是指从一块石英晶体上按一定方位角切下薄片(简称为晶片),石英晶体谐振器,简称为石英晶体或晶体、晶振;而在封装内部添加IC组成振荡电路的晶体元件称为晶体振荡器。

其产品一般用金属外壳封装,也有用玻璃壳、陶瓷或塑料封装的。

2、晶振的工作原理石英晶体振荡器是利用石英晶体的压电效应制成的一种谐振器件,它的基本构成大致是:从一块石英晶体上按一定方位角切下薄片,在它的两个对应面上涂敷银层作为电极,在每个电极上各焊一根引线接到管脚上,再加上封装外壳就构成了石英晶体谐振器,简称为石英晶体或晶体、晶振。

其产品一般用金属外壳封装,也有用玻璃壳、陶瓷或塑料封装的。

若在石英晶体的两个电极上加一电场,晶片就会产生机械变形。

反之,若在晶片的两侧施加机械压力,则在晶片相应的方向上将产生电场,这种物理现象称为压电效应。

如果在晶片的两极上加交变电压,晶片就会产生机械振动,同时晶片的机械振动又会产生交变电场。

在一般情况下,晶片机械振动的振幅和交变电场的振幅非常微小,但当外加交变电压的频率为某一特定值时,振幅明显加大,比其他频率下的振幅大得多,这种现象称为压电谐振,它与LC回路的谐振现象十分相似。

它的谐振频率与晶片的切割方式、几何形状、尺寸等有关。

当晶体不振动时,可把它看成一个平板电容器称为静电电容C,它的大小与晶片的几何尺寸、电极面积有关,一般约几个pF到几十pF。

当晶体振荡时,机械振动的惯性可用电感L来等效。

一般L的值为几十mH到几百mH。

晶片的弹性可用电容C来等效,C的值很小,一般只有0.0002~0.1pF。

晶片振动时因摩擦而造成的损耗用R来等效,它的数值约为100Ω。

由于晶片的等效电感很大,而C很小,R也小,因此回路的品质因数Q很大,可达1000~10000。

加上晶片本身的谐振频率基本上只与晶片的切割方式、几何形状、尺寸有关,而且可以做得精确,因此利用石英谐振器组成的振荡电路可获得很高的频率稳定度。

Allegro Layout注意事项

Allegro Layout 注意事项:一、导入结构图,网络表。

根据要求画出限制区域ROUTE KEEPIN, PACKAGE KEEPIN,(一般为OUTLINE内缩40mil),PACKAGE KEEPOTU,ROUTE KEEPOUT(螺絲孔至少外扩20 mils); 晶振,电感等特殊器件的MOAT区。

二、布局,摆元器件。

设置W/S 走线规则三、画出板边ANTI ETCH,在ROUTE KEEPIN之内每一层画20MIL的环板GND Shape(电源层Shape板边比GND层内缩40 MIL)四、布线1、特殊信号走线:泛指CLOCK、LAN、AUDIO 等信号(此区块的处理请一次性完成,不要留杂线)A、进出CHIP(集成电路芯片) 的TRACE要干净平顺B、进出Connector 时要每一颗EMI零件顺序走过C、Connector的零件区内走线,Placement净空(只出不进)2、高速信号走线:泛指FSB、DDR、等信号A、表层走线尽量短,绕等长时以内层为主。

B、走线需注意不可跨PLANE ,不可进入大电流的电感、MOS区及其它电路区块(MOAT)C、走高速线区块时,顺手把附近的杂线,POWER、GND VIA 引出D、请看Guideline 处理走线(避免设置时的失误)3、BGA走线注意事项:A、BGA走线一律往外走(如需内翻时请先告知),走线预留十字电源通道。

BGA中以区块走线的方式,非其本身的信号不要进入。

B、当BGA的TRACE 在经过特殊信号处理,及BUS线处理等过程后整个BGA已完成2/3的走线时,可将剩余的所有TRACE引出BGA,以完成BGA区域处理。

C、BGA走线清完后,请CHECK 于GND PLANE 的BGA区,CHECK PLANE是否过于破碎、导通不足,请调整OK4、CLK信号走线:A、CLK 信号必须用规定的层面和线宽走线、长度符合要求,走线时应少打VIA(一个网络信号一般不多于2个)、少换层,不能跨PLANEB、CLK信号输出先接Damping电阻(阻抗匹配),再接电容(滤除噪声),再由电容接出C、CLK线要尽量远离板边(>300MIL),应避免在SLOT槽、BGA等重要组件中走线D、CLK Generator下方要净空,下方通常每层会铺GND SHAPE,并打GND VIA,CLK Generator的GND PIN可以内引接到SHAPE上,5、SHAPE 注意事项:A、板上大电流信号的SHAPE (例如:+VBAT、+VAC_IN、、、等),此为进入板内的主电源,线宽要足够大,请尽量保持SHAPE 宽度,如有其它信号在上面打VIA,注意VIA方向,不要使SHAPE 在VOID 后过于破碎,影响信号导通。

Layout设计规范A1.3

Layout 规则Note1: Added “10: CF卡LAYOUT要求” 2003-09-27Added “11:PCB板的标号字体规定” 2004-04-161.导线宽度及间距:1)走线宽度可分为以下几种:⑴300mil(或以上):适用于20A(或以下)电源线,控制线。

⑵200mil(或以上):10A⑶150mil(或以上):5A⑷100mil(或以上):2A⑸75mil(或以上):1A⑹50mil(或以上):500mA⑺25mil(或以上):适用于200mA(或以下)电源线,控制线或重要信号线如BUS信号(ISA BACKPLANE)RS-485,USB的外接信号或易受干扰信号。

⑻15mil(或以上):适用于100mA(或以下)控制信号或重要信号如POWERGOOD信号,RESET信号,CLOCK信号,BUS信号(PCI BACKPLANE),易受干扰信号等.⑼10mil(或以上):适用于周边之信号,BUS信号(COMPACT PCI)一般信号或过双线之走线。

⑽8mil:适用于高密度走线,或过三线的走线。

⑾6mil 5mil:适用于高密度走线。

具体应用参见相应DESIGN GUIDE或由主管决定。

⑿高密度脚位之零件,其电源讯号走线宽度至少应与其电源接脚的PAD同宽。

2)3W规则:走线间的距离间隔(走线中心间的距离)是单一走线宽度的二倍。

对于时钟线,差分对,视频,音频复位线及其它系统关键线强制使用3W。

对于差分对,走线对内部间距为1W。

对于导线间存在过孔的情况,应增加包括通孔在内的环状区域。

2.焊盘与孔径1)焊盘直径应比孔径大14mil以上(最好大于20 mil以上):2)多层板的电源层和地线层的隔离盘至少大于40mil,且越大越好。

3)焊盘直径应尽量大:有效散热、抗震动。

4)安装孔应尽量以焊盘的形式给出孔位和孔径。

5)导通孔焊盘应尽可能大。

一般主板导通孔孔径为12mil焊盘直径为24mil;I/O卡孔径为15mil焊盘直径为30mil。

LAYOUT设计一般规则

1. 一般规则1.1 PCB板上预划分数字、模拟、DAA信号布线区域。

1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。

1.3 高速数字信号走线尽量短。

1.4敏感模拟信号走线尽量短。

1.5 合理分配电源和地。

1.6 DGND、AGND、实地分开。

1.7 电源及临界信号走线使用宽线。

1.8 数字电路放置於并行总线/串行DTE接口附近,DAA电路放置於电话线接口附近。

2. 元器件放置2.1 在系统电路原理图中:a) 划分数字、模拟、DAA电路及其相关电路;b) 在各个电路中划分数字、模拟、混合数字/模拟元器件;c) 注意各IC芯片电源和信号引脚的定位。

2.2 初步划分数字、模拟、DAA电路在PCB板上的布线区域(一般比例2/1/1),数字、模拟元器件及其相应走线尽量远离并限定在各自的布线区域内。

Note:当DAA电路占较大比重时,会有较多控制/状态信号走线穿越其布线区域,可根据当地规则限定做调整,如元器件间距、高压抑制、电流限制等。

2.3 初步划分完毕后,从Connector和Jack开始放置元器件:a) Connector和Jack周围留出插件的位置;b) 元器件周围留出电源和地走线的空间;c) Socket周围留出相应插件的位置。

2.4 首先放置混合型元器件(如Modem器件、A/D、D/A转换芯片等):a) 确定元器件放置方向,尽量使数字信号及模拟信号引脚朝向各自布线区域;b) 将元器件放置在数字和模拟信号布线区域的交界处。

2.5 放置所有的模拟器件:a) 放置模拟电路元器件,包括DAA电路;b) 模拟器件相互靠近且放置在PCB上包含TXA1、TXA2、RIN、VC、VREF信号走线的一面;c) TXA1、TXA2、RIN、VC、VREF信号走线周围避免放置高噪声元器件;d) 对於串行DTE模块,DTE EIA/TIA-232-E系列接口信号的接收/驱动器尽量靠近Connector并远离高频时钟信号走线,以减少/避免每条线上增加的噪声抑制器件,如电容等阻流圈和。

晶振layout规则

晶振layout规则晶振是电子设备中常用的一种元器件,它在许多电路中起着关键的作用。

晶振layout规则是指在电路设计中布局晶振时需要遵守的一些规定。

本文将介绍晶振layout规则的相关内容,以帮助读者更好地理解和应用晶振。

一、晶振的作用和原理晶振是一种产生稳定频率信号的元器件,常用于时钟电路中。

它通过电学效应将电能转换为机械振动,进而产生稳定的频率信号。

晶振的频率和谐振器件的结构有关,一般由石英晶体等材料制成。

二、晶振layout规则的意义晶振layout规则是为了保证晶振在电路中能够正常工作而制定的。

在进行晶振布局时,需要考虑以下几个方面的因素:1. 尽量减少电路中的干扰:晶振是一种高灵敏度的元器件,容易受到外界电磁干扰的影响。

因此,在布局时应尽量远离其他可能产生干扰的元件,如大功率器件、高频信号源等。

2. 保持稳定的地线:地线是电路中的参考点,对晶振的工作稳定性有着重要影响。

在布局时,应尽量保持地线的连续性和稳定性,避免出现地线回流或地线干扰的情况。

3. 保持信号线的短距离:晶振的信号线是将频率信号传输到其他电路的关键部分。

为了保证信号的准确传输,应尽量使信号线的长度尽可能短,并避免与其他信号线或电源线交叉。

4. 保持合适的阻抗匹配:晶振的输出阻抗是与其他电路连接的关键。

为了保证信号的准确传输,应保持晶振输出端的阻抗与其他电路的输入阻抗匹配。

三、晶振layout规则的具体要求1. 布局时应尽量减少晶振与其他元件之间的距离,以减少干扰。

2. 布局时应尽量保持晶振与地线之间的距离,以提高地线的稳定性。

3. 布局时应尽量缩短晶振信号线的长度,以保证信号的准确传输。

4. 布局时应保持晶振输出端的阻抗与其他电路的输入阻抗匹配。

5. 布局时应尽量避免晶振与其他高频信号源或大功率器件的相互干扰。

6. 布局时应尽量避免晶振信号线与其他信号线或电源线的交叉,以减少互相干扰。

7. 布局时应尽量保持晶振与其他元件之间的物理隔离,以减少干扰。

layout注意事项

Layout注意问题一:ESD 器件由于ESD器件选择和摆放位置同具体的产品相关,下面是一些通用规则:1.让元器件尽量远离板边。

2.敏感线(Reset,PBINT)走板内层不要太靠近板边;RTC部分电路不要靠近板边。

3.可能的话,PCB四周保留一圈露铜的地线。

4. ESD器件接地良好,直接(通过VIA)连接到地平面。

5. 受保护的信号线保证先通过ESD器件,路径尽量短。

二:天线13MHz泄漏,会导致其谐波所在的Channel: Chan5, Chan70,Chan521、586、651、716、781、846等灵敏度明显下降;13MHz相关线需要充分屏蔽。

一般FPC和LCDM离天线较近,容易产生干扰,对FPC上的线需要采取滤波(RC 滤波)措施和屏蔽FPC,并可靠接地。

靠近天线部分的板上线(不管什么类型)尽量要走到内层或采取一定的屏蔽措施,来降低其辐射。

(板内的其他信号可能耦合到走在表层的信号线上,产生辐射干扰。

)三.LCD注意FPC连接器的信号定义:音频信号线最好两边有地线保护;音频信号线与电平变换频繁的信号线要有足够间距;FPC上的时钟信号及其他电平变换频繁的信号要有地线保护减少EMI影响;LCD的数据线格式是否和BB芯片匹配?例如i80或M68在时序上要求不一致等问题。

设计中对LCM 上的JPEG IC时钟信号的频率,幅值要满足需求。

如果时钟幅度不够可能导致JPEG不工作或不正常;注意Camera的输入时钟对Preview的影响,通常较高的Preview刷新帧数要求时钟频率高。

布局上,升压电路远离天线;音频器件和音频走线;给Camera供电的LDO靠近Camera放置;主板上Hall器件的位置要恰当,不能对应上盖LCD屏的位置,否则上盖的磁铁不能正对着Hall器件。

四.音频设计PCB布局音频器件远离天线、RF、数字部分,防止天线辐射对音频器件(音频功放等)的干扰;如果靠的很近,应该考虑使用屏蔽罩。

LAYOUT以及选点规则

LAYOUT以及選點規則前言今日電子產品愈輕薄短小,PCB之設計布線也愈趨複雜困難。

除需兼顧功能性與安全性外,更需可生產及可測試。

茲就可測性之需求提供規則供設計布線工程師參考,如能注意之,省㆘可觀之治具製作費用並增進測試之可靠性與治具之使用壽命。

可取用之規則1. 雖然有雙面治具,但最好將被測點放在同㆒面。

2. 被測點優先順序:A.測點(Component Lead)B.零件腳(Testpad) C.貫穿孔(Via)3. 兩被測點或被測點與預鑽孔之㆗心距不得小於0.050"(1.27mm)。

以大於0.100"(2.54mm)為佳,其次是0.075"(1.905mm)。

4. 被測點應離其附近零件(位於同㆒面者)至少0.100",如為高於3m/m零件,則應至少間距0.120"。

5. 被測點應平均分布於PCB表面,避免局部密度過高。

6. 被測點直徑最好能不小於0.035"(0.9mm),如在㆖針板,則最好不小於0.040"(1.00mm),形狀以正方形較佳(可測面積較圓形增加21%)。

小於0.030"之被測點需額外加工,以導正目標。

7. 被測點的Pad及Via不應有防焊漆(Solder Mask)。

8. 被測點應離板邊或折邊至少0.100"。

9. PCB厚度至少要0.062"(1.35mm),厚度少於此值之PCB容易板彎,需特殊處理。

10. 定位孔(Tooling Hole)直徑最好為0.125"(.3.175mm)或.16"(.3.9mm)。

其公差應在"+0.002"/-0.001"。

其位置應在PCB 之對角。

11. 被測點至定位孔位置公差應為+/-0.002"。

12. 避免將被測點置於SMT零件㆖,非但可測面積太小,不可靠,而且容易傷害零件。

LAYOUT设计一般规则PDF

1. 一般规则1.1 PCB板上预划分数字、模拟、DAA信号布线区域。

1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。

1.3 高速数字信号走线尽量短。

1.4 敏感模拟信号走线尽量短。

1.5 合理分配电源和地。

1.6 DGND、AGND、实地分开。

1.7 电源及临界信号走线使用宽线。

1.8 数字电路放置於并行总线/串行DTE接口附近DAA电路放置於电话线接口附近。

2. 元器件放置2.1 在系统电路原理图中a 划分数字、模拟、DAA电路及其相关电路b 在各个电路中划分数字、模拟、混合数字/模拟元器件c 注意各IC芯片电源和信号引脚的定位。

2.2 初步划分数字、模拟、DAA电路在PCB板上的布线区域一般比例2/1/1数字、模拟元器件及其相应走线尽量远离并限定在各自的布线区域内。

Note:当DAA电路占较大比重时会有较多控制/状态信号走线穿越其布线区域可根据当地规则限定做调整如元器件间距、高压抑制、电流限制等。

2.3 初步划分完毕后从Connector和Jack开始放置元器件 a Connector和Jack周围留出插件的位置b 元器件周围留出电源和地走线的空间 c Socket周围留出相应插件的位置。

2.4 首先放置混合型元器件如Modem器件、A/D、D/A转换芯片等a 确定元器件放置方向尽量使数字信号及模拟信号引脚朝向各自布线区域b 将元器件放置在数字和模拟信号布线区域的交界处。

2.5 放置所有的模拟器件a 放置模拟电路元器件包括DAA电路 b 模拟器件相互靠近且放置在PCB上包含TXA1、TXA2、RIN、VC、VREF信号走线的一面c TXA1、TXA2、RIN、VC、VREF信号走线周围避免放置高噪声元器件d 对於串行DTE模块DTE EIA/TIA-232-E 系列接口信号的接收/驱动器尽量靠近Connector并远离高频时钟信号走线以减少/避免每条线上增加的噪声抑制器件如电容等阻流圈和。

LAYOUT规范

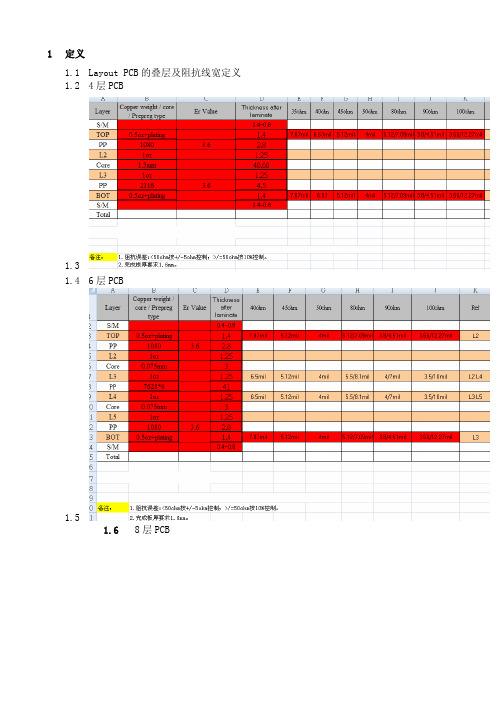

1定义1.1Layout PCB的叠层及阻抗线宽定义1.24层PCB1.31.46层PCB1.51.68层PCB1.7.2要求2.1设计流程:2.1.1 评审通过后的原理图2.1.2 网表2.1.3 PCB 架构(外形尺寸,螺丝孔,定位孔及禁布区)2.1.4 如有增加新器件,需提供新的封装资料(PCB FOOTPRINT)2.1.5 根据单板结构图或对应的标准板框, 创建PCB设计文件2.1.6 布局及布线2.1.7 工艺设计要求2.1.8 设计评审2.2元件的布局:2.2.1创建网络表2.2.1.1 网络表是原理图与PCB的接口文件,PCB设计人员应根据所用的原理图和PCB设计工具的特性,选用正确的网络表格式,创建符合要求的网络表。

2.2.1.2 创建网络表的过程中,应根据原理图设计工具的特性,积极协助原理图设计者排除错误。

保证网络表的正确性和完整性。

2.2.1.3 确定器件的封装(PCB FOOTPRINT).2.2.1.4 创建PCB板 根据单板结构图或对应的标准板框, 创建PCB设计文件;注意正确选定单板坐标原点的位置,原点的设置原则:单板右边和下边的延长线交汇点。

板框四周倒圆角,倒角半径5mm。

特殊情况参考结构设计要求。

2.2.2 布局前设置2.2.2.1 根据结构图设置板框尺寸,按结构要素布置安装孔、接插件等需要定位的器件,并给这些器件赋予不可移动属性。

按工艺设计规范的要求进行尺寸标注。

2.2.2.2 根据结构图和生产加工时所须的夹持边设置印制板的禁止布线区、禁止布局区域。

根据某些元件的特殊要求,设置禁止布线区。

2.2.2.3 综合考虑PCB性能和加工的效率选择加工流程。

加工工艺的优选顺序为:元件面单面贴装——元件面贴、插混装(元件面插装焊接面贴装一次波峰成型)——双面贴装——元件面贴插混装、焊接面贴装。

2.3 布局规则2.3.1遵照“先大后小,先难后易”的布置原则,即重要的单元电路、核心元器件应当优先布局.2.3.2 布局中应参考原理框图,根据单板的主信号流向规律安排主要元器件.2.3.3 布局应尽量满足以下要求:总的连线尽可能短,关键信号线最短;高电压、大电流信号与小电流,低电压的弱信号完全分开;模拟信号与数字信号分开;高频信号与低频信号分开;高频元器件的间隔要充分.2.3.4 相同结构电路部分,尽可能采用“对称式”标准布局;2.3.5 按照均匀分布、重心平衡、版面美观的标准优化布局;2.3.6 器件布局栅格的设置,一般IC器件布局时,格点应为50 mil,小型表面安装器件,如表面贴装元件布局时,格点设置应不少于10mil。

LAYOUT设计一般规则

1. 一般规则1.1 PCB板上预划分数字、模拟、DAA信号布线区域。

1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。

1.3 高速数字信号走线尽量短。

1.4敏感模拟信号走线尽量短。

1.5 合理分配电源和地。

1.6 DGND、AGND、实地分开。

1.7 电源及临界信号走线使用宽线。

1.8 数字电路放置於并行总线/串行DTE接口附近,DAA电路放置於电话线接口附近。

2. 元器件放置2.1 在系统电路原理图中:a) 划分数字、模拟、DAA电路及其相关电路;b) 在各个电路中划分数字、模拟、混合数字/模拟元器件;c) 注意各IC芯片电源和信号引脚的定位。

2.2 初步划分数字、模拟、DAA电路在PCB板上的布线区域(一般比例2/1/1),数字、模拟元器件及其相应走线尽量远离并限定在各自的布线区域内。

Note:当DAA电路占较大比重时,会有较多控制/状态信号走线穿越其布线区域,可根据当地规则限定做调整,如元器件间距、高压抑制、电流限制等。

2.3 初步划分完毕后,从Conne ctor和Jack开始放置元器件:a) Connec tor和J ack周围留出插件的位置;b) 元器件周围留出电源和地走线的空间;c) Socket周围留出相应插件的位置。

2.4 首先放置混合型元器件(如Modem器件、A/D、D/A转换芯片等):a) 确定元器件放置方向,尽量使数字信号及模拟信号引脚朝向各自布线区域;b) 将元器件放置在数字和模拟信号布线区域的交界处。

2.5 放置所有的模拟器件:a) 放置模拟电路元器件,包括DAA电路;b) 模拟器件相互靠近且放置在PCB上包含TXA1、TXA2、RIN、VC、VREF信号走线的一面;c) TXA1、TXA2、RIN、VC、VREF信号走线周围避免放置高噪声元器件;d) 对於串行DT E模块,DTE EIA/TIA-232-E系列接口信号的接收/驱动器尽量靠近Conn ector并远离高频时钟信号走线,以减少/避免每条线上增加的噪声抑制器件,如电容等阻流圈和。

晶振布线规则和注意事项

晶振布线规则和注意事项

晶振,在板子上看上去一个不起眼的小器件,但是在数字电路里,就像是整个电路的心脏。

数字电路的所有工作都离不开时钟,晶振的好坏,晶振电路设计的好坏,会影响到整个系统的稳定性。

所以说晶振是智能硬件的“心脏”。

晶振下布线时该注意什么

1、不要过大电流的线,也不要走频率比较高的信号线,也不要走易受干扰或易干扰其他的信号线。

第三层可以走线,第二层尽量不要走线。

保证晶振有一个与芯片最短距离的地相连。

2、晶振布线易犯的错误预防

问题是这样的,板子上面RF信号解码的时候出错了,始终无法正确响应RF信号线。

仔细检查发现晶振下方有SPI的走线,而且是在内层布线,由于SPI信号的频率很高,因此耦合到了RF解码芯片上去了,由于时钟线总是出问题,RF数据总是被解码芯片忽略掉。

对于这个问题呢,检查晶振的有几条:

1)确认晶振和连接的IC被地线包围,单片机或者IC的地需要直接和外部的地相连。

2)要确认晶振的地和模块其他地需要区分开,并确认模块其他的地与晶振的工作无关。

3)电容和晶振要尽可能靠近IC和单片机,晶振,IC(单片机)和电容必须在板子的同一面。

4)确认不能有其他的信号线靠近晶振和晶振附近的。

Layout规范设计(268条)

PCB布线与布局 增大线路间的距离是减小电容耦合的最好办法

PCB布线与布局

在正式布线之前,首要的一点是将线路分类。主要的分类方法是按功率电平来进行,以 每30dB功率电平分成若干组

PCB布线与布局

不同分类的导线应分别捆扎,分开敷设。对相邻类的导线,在采取屏蔽或扭绞等措施后 也可归在一起。分类敷设的线束间的最小距离是50~75mm

64

PCB布线与布局

多层板:电源层和地层要相邻。高速信号应临近接地面,非关键信号则布放为靠近电源 面。

65

PCB布线与布局 电源:当电路需要多个电源供给时,用接地分离每个电源。

66

PCB布线与布局

过孔:高速信号时,过孔产生1-4nH的电感和0.3-0.8pF的电容。因此,高速通道的过孔 要尽可能最小。确保高速平行线的过孔数一致。

PCB布线与布局

字地在母板的接地处接地,电源在系统接地点附近单点汇接,如电源电压一致,模拟和 数字电路的电源在电源入口单点汇接,如电源电压不一致,在两电源较近处并一1~2nf的

电容,给两电源间的信号返回电流提供通路

PCB布线与布局 当高速、中速和低速数字电路混用时,在印制板上要给它们分配不同的布局区域 PCB布线与布局 对低电平模拟电路和数字逻辑电路要尽可能地分离 PCB布线与布局 多层印制板设计时电源平面应靠近接地平面,并且安排在接地平面之下。 PCB布线与布局 多层印制板设计时布线层应安排与整块金属平面相邻

远离、地线隔开。

PCB布线与布局 晶振要尽量靠近IC,且布线要较粗

PCB布线与布局 晶振外壳接地

PCB布线与布局 时钟布线经连接器输出时,连接器上的插针要在时钟线插针周围布满接地插针

让模拟和数字电路分别拥有自己的电源和地线通路,在可能的情况下,应尽量加宽这两 PCB布线与布局 部分电路的电源与地线或采用分开的电源层与接地层,以便减小电源与地线回路的阻

[电子工程] 10年老司机倾囊相授,贴片晶振的PCB layout需要注意哪些

![[电子工程] 10年老司机倾囊相授,贴片晶振的PCB layout需要注意哪些](https://img.taocdn.com/s3/m/223d868c856a561252d36f7a.png)

10年老司机倾囊相授,贴片晶振的PCB layout需要注意哪些?晶振有两个比较重要的参数,频偏和温偏,单位都是PPM,通俗说,晶振的标称频率不是一直稳定的,某些环境下晶振频率会有误差,误差越大,电路稳定性越差,甚至电路无法正常工作。

所以在PCB设计时,晶振的layout显得尤其的重要,有如下几点需要注意。

✔两个匹配电容尽量靠近晶振摆放。

✔晶振由石英晶体构成,容易受外力撞击或跌落的影响,所以在布局时,最好不要放在PCB边缘,尽量靠近芯片摆放。

✔晶振的走线需要用GND保护好,并且远离敏感信号如RF、CLK信号以及高速信号。

✔在一些晶振的PCB设计中,相邻层挖空(净空)或者同一层和相邻层均净空处理,第三层需要有完整的地平面,这么做的原因是维持负载电容的恒定。

晶振负载电容的计算公式是:CL=C1*C2/(C1+C2)+Cic+CpCic为集成电路内部电容,Cp为PCB板的寄生电容,寄生电容过大,将会导致负载电容偏大,从而引起晶振频偏,这个时候减小匹配电容C1和C2可能会有所改善,但这也是治标不治本的措施。

晶振相邻层挖空是如何控制寄生电容Cp的呢?电容的物理公式是:C=εS/4πKd,即晶振焊盘与邻近地平面之间的面积S 和距离d均会影响寄生电容大小,因为面积S是不变的,所以影响寄生电容的因素只剩下距离d,通过挖空晶振同一层的地和相邻层的地,可以增大晶振焊盘与地平面之间的距离,来达到减小寄生电容的效果。

电容容值和物理量之间的关系简单画了一个图示,如下一个4层板,晶振放在Top层,将Top层和相邻层净空之后,晶振相对于地平面(L3),相比较没有净空之前,这个距离d是增大的,即寄生电容会减小。

晶振的L1和L2层均净空处理✔晶振的摆放需要远离热源,因为高温也会影响晶振频偏。

我们知道晶振附近相邻地挖空处理,一方面是为了维持负载电容恒定,另一方面很大原因是隔绝热传导,避免周围的PMIC或者其他发热体的热透过铜皮传导到晶振,导致频偏,故意净空不铺铜,以隔绝热的传递。

PCB LAYOUT 设计规范

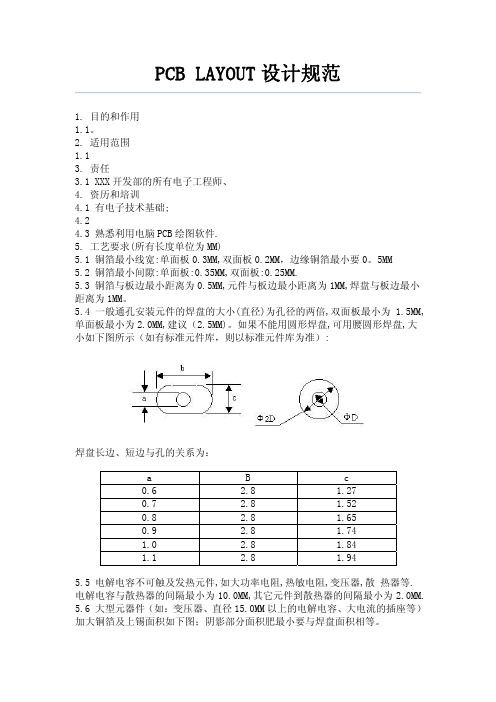

PCB LAYOUT设计规范1. 目的和作用1.1。

2. 适用范围1.13. 责任3.1 XXX开发部的所有电子工程师、4. 资历和培训4.1 有电子技术基础;4.24.3 熟悉利用电脑PCB绘图软件.5. 工艺要求(所有长度单位为MM)5.1 铜箔最小线宽:单面板0.3MM,双面板0.2MM,边缘铜箔最小要0。

5MM5.2 铜箔最小间隙:单面板:0.35MM,双面板:0.25MM.5.3 铜箔与板边最小距离为0.5MM,元件与板边最小距离为1MM,焊盘与板边最小距离为1MM。

5.4 一般通孔安装元件的焊盘的大小(直径)为孔径的两倍,双面板最小为 1.5MM,单面板最小为2.0MM,建议(2.5MM)。

如果不能用圆形焊盘,可用腰圆形焊盘,大小如下图所示(如有标准元件库,则以标准元件库为准):焊盘长边、短边与孔的关系为:a B c0.6 2.8 1.270.7 2.8 1.520.8 2.8 1.650.9 2.8 1.741.02.8 1.841.12.8 1.945.5 电解电容不可触及发热元件,如大功率电阻,热敏电阻,变压器,散 热器等.电解电容与散热器的间隔最小为10.0MM,其它元件到散热器的间隔最小为2.0MM.5.6 大型元器件(如:变压器、直径15.0MM以上的电解电容、大电流的插座等)加大铜箔及上锡面积如下图;阴影部分面积肥最小要与焊盘面积相等。

5.7 螺丝孔半径5.0MM内不能有铜箔(除要求接地外)及元件.(或按结构图要求).5.8 上锡位不能有丝印油.5.9 焊盘中心距小于2.5MM的,该相邻的焊盘周边要有丝印油包裹,丝印油宽度为0.2MM(建议0.5MM).5.10 跳线不要放在IC下面或马达、电位器以及其它大体积金属外壳的元件下.5.11 在大面积PCB设计中(大约超过500CM2以上),为防止过锡炉时PCB板弯曲,应在PCB板中间留一条5至10MM宽的空隙不放元器件(可走线),以用来在过锡炉时加上防止PCB板弯曲的压条,如下图的阴影区:5.12 每一粒三极管必须在丝印上标出e,c,b脚.5.13 需要过锡炉后才焊的元件,焊盘要开走锡位,方向与过锡方向相反,宽度视孔的大小为0.5MM到1.0MM。

射频部分layout注意事项[重点]

![射频部分layout注意事项[重点]](https://img.taocdn.com/s3/m/c28e650ba200a6c30c22590102020740be1ecdaf.png)

射频部分layout注意事项就前阶段我们layout出现的问题,我对射频部分layout注意事项做了整理。

请大家补充,定下来后,作为以后射频部分layout和检查原则。

1,元器件布局做stacking时就需考虑好结构件和主要元器件的布局,例如I/O连接器,SIM卡,电池连接器,T卡,camera,speaker,receiver,射频部分,基带部分,GSM天线部分,蓝牙天线部分,手机电视天线部分。

这些部分位置的摆放除了从ID,MD方面考虑,还需要考虑到相互之间的影响。

MTK方案中SIM卡,按键都容易受到GSM天线干扰,需要尽量远离GSM天线。

GSM天线区域,蓝牙天线区域和手机电视天线区域都需要一个合适的区域。

GSM若做PIFA天线,需要500mm2的面积,天线离主板需要5mm以上高度,天线底下不能有I/O连接器,T卡,speaker之类器件,否则高度只能按底下器件到天线高度算;若做monopole,天线空间需要30mm×10mm,主板上该区域的地需挖空,天线与主板投影面不能有金属。

speaker,receiver易受到天线干扰,产生TDMA noise,需要考虑它们和天线的相对位置。

电池连接器到PA电源也需较短。

Stacking给出的射频部分屏蔽罩位置,射频部分能够作为一个合适整体放下射频部分到基带部分的IQ线,26MHZ信号线,控制线要走得尽量短,尽量顺。

射频部分布局,需要理顺FEM到tranceiver的RX接收线,tranceiver 到PA的TX 发射线,PA到FEM或者ASM的TX发射线。

电源网络滤波小电容应尽量靠近芯片管脚,减少引线电感。

其他元器件摆放,按照就近,顺便原则。

元器件的摆放还需考虑限高,除了考虑结构上的限高,屏蔽罩高度也会限制器件的摆放。

目前两件式的屏蔽罩高度是1.8mm,一件式的高度是1.6mm,在射频屏蔽罩里面的器件高度都需在这个范围以内。

若靠近屏蔽罩的周围,或者在屏蔽罩的筋上,高度会更受限制。

SMT电子元件PCBlayout规范

目前我司使用YAMAHA品牌的贴片机.其尺寸加工能力为最大:L460XW413最小:L50XW50

SMT工艺生产最佳尺寸:宽(200mm~250mm)×长(250mm~350mm)×厚(1.6mm-3mm) 3:厚度设计.我司贴片机可接受厚度在0.5-5mm以内.若PCB板上只有集成电路. 小功率晶体管.电阻.电容.等小功率元器件.在没有较强的负荷振动条件下.使用厚度

为1.6mm.PCB板尺寸控制在L460mmXW413mm以内即可.有负荷振动条件下.要根

据振动条件缩小PCB尺寸.仍可使用1.6mm的PCB板.板宽较大或者无法支撑时.应选 择2-3mm的PCB板.当PCB尺寸小于L50XW50时.必须采用拼版方式.

PCB定位孔和工艺边设计规范

元件大小:5.0×3.2

1.4mm 2.2mm

1.0mm 1.2mm

此类元件焊盘偏大.易出现焊接 后偏移.焊盘偏小易出现空焊。

HANSONG

SIM卡焊盘设计标准 pitch=2.53mm

1.7mm 此类元件焊盘偏小,易导致焊 点强度不够。

1.5mm

8.43mm

HANSONG

(ADI系列板对板连接器,PITCH=0.4mm)

0.22mm

0.9mm 元件大小 3.0mm

Body:5.6×2.0mm

Outline:5.6×3.8mm

此类元件焊盘间距偏小于推荐值或 者焊盘偏大,容易出现短路; 0.5mm

connector

HANSONG

SOP IC焊盘设计标准 Pitch=0.65

0.25mm

HANSONG

1.45mm

元件大小 Body:9.8×6.2mm

layout检查注意总结

Layout 检查注意总结点个人一些layout PCB 总结,如有忽略或者不当可以自行思考。

1、晶体、晶振布局和走线要求器件表层内层都需要净空区,时钟走线立体包地好,下方绝不允许电源走线、敏感走线等2、EMI 器件的位置使用ESD 器件要靠近输入端摆放,而不是靠近保护器件摆放,以快速吸收静电波峰,使之释放瞬间静电到地。

注意ESD 器件接地端必须尽快下到主地,减少静电回路。

注意ESD 器件参数中的开启电压、击穿电压、钳位电压适用电压电路,注意高速信号上的ESD 器件的结电容要求。

注意有些TVS 管是兼容抗浪涌的,多查datasheet 的参数。

一些线路上串1K 电阻也会对静电有一定防护效果,希望看到的朋友注意这点。

3、高速信号走线要求和注意点高速信号必须做等长和等效阻抗处理,等长的要求根据平台要求而定,比如高通平台要求MIPI 高速差分走线组内不超0.7mm,组间不超 1.4mm,阻抗要求100欧。

避免隔层有大电源和敏感走线(比如DCDC、audio、clk),要求立体包地。

4、DCDC 电源走线宽度和要求电源走线要求满足电流宽度要求,比如VBAT 起来瞬间电流最大达到2A 多,要保持余量就会要求走线满足3A(3mm 宽)。

DCDC 电源走线靠近敏感线或者高速线时,如果中间只隔了一根底线,建议隔开宽点,中间底线多打孔到主地。

每条电压一定要注意最大电流大小,需要线宽达到要求。

5、敏感线音频走线、时钟走线要求立体包地,避免和大电源隔层交叉,音频器件远离天线、RF、数字信号。

喇叭走线保证15mil 以上线宽。

MIC 和耳机信号的一些滤波电容靠近输入端摆放,减少噪声输入。

注意IQ 差分走线包地处理,避免和CLK,射频输出线平行。

特别注意平台要求的一些信号线的电容靠近芯片摆放,接地端下主地要求,必须严格执行。

6、射频走线要求、天线走线要求首先要注意RF 输出要原理RF 输入。

发射端匹配电路靠近主芯片一端,接收端匹配电路靠近LAN 端或FEM 一端。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

晶振layout规则

晶振(Crystal)是一种电子元件,用于提供精确的时钟信号,使电路能够准确地执行各种功能。

在PCB设计中,晶振layout(布局)的规则非常重要,因为如果晶振layout不良,将导致系统时钟信号不稳定,从而影响整个电路的可靠性和性能。

以下是晶振layout的一些规则和建议:

1. 将晶振置于尽可能接近芯片的位置,并确保晶振的引脚间距符合芯片引脚的标准间距。

2. 晶振的两个引脚必须通过贴片电容器连接到地面和电源。

这些电容器应放置在晶振的附近,并且应该越接近晶振越好。

3. 晶振的布局应该避免与高速信号线和电源线发生交叉。

这些线会产生电磁干扰(EMI),从而导致晶振信号不稳定。

4. 晶振应该远离任何电磁干扰源,如变压器、电机和高频电磁场等。

5. PCB中必须使用地面平面或地面层来提供良好的地面引用。

地面平面应该尽可能接近晶振,以确保晶振引脚连通到地面。

6. 对于需要使用多个晶振的设计,应该将它们分别布置在不同的地方,并确保它们的布局相互独立,以避免相互干扰。

总之,良好的晶振layout设计可以提高电路的可靠性和性能,但需要注意诸多细节和规则。

因此,设计人员应该仔细考虑这些规则,以确保他们的设计正确无误。

- 1 -。