2010级硕士模拟集成电路分析与设计期末复习题-解答

《集成电路测试》期末复习题库【附答案】

《集成电路测试》期末复习题库【附答案】《集成电路测试》期末复习题库【附答案】(试题按章节分类)【填空】1、切筋成型其实是两道⼯序:切筋和打弯,通常同时完成。

2、对SMT装配来讲,尤其是⾼引脚数⽬框架和微细间距框架器件,⼀个突出的问题是引脚的⾮共⾯性。

3、打码⽅法有多种,其中最常⽤的是印码:包括油墨印码(ink marking)和激光印码(Laser Marking)两种。

4、在完成打码⼯序后,所有器件都要100%进⾏测试。

这些测试包括⼀般的⽬检、⽼化试验和最终的产品测试。

5、对于连续⽣产流程,元件的包装形式应该⽅便拾取,且不需作调整就能够应⽤到⾃动贴⽚机上。

【选择】1、⽓密性封装是指完全能够防⽌污染物(液体或固体)的侵⼊和腐蚀的封装形式,通常⽤作芯⽚封装的材料中,能达到所谓⽓密性封装的只有:⾦属、陶瓷和玻璃2、⾦属封装现有的封装形式⼀般包括平台插⼊式⾦属封装、腔体插⼊式⾦属封装、扁平式⾦属封装和圆形⾦属封装等。

3、根据所使⽤材料的不同,元器件封装主要分为⾦属封装、陶瓷封装和塑料封装三种类型。

4、⾦属封装由于在最严酷的使⽤条件下具有杰出的可靠性⽽被⼴泛⽤于军事和民⽤领域。

【讨论】1、各向异性材料、各向同性材料的区别是什么?所有物理性质在不同⽅向是⼀样的是各向同性材料,⼤部分物理性质在不同⽅向是不⼀样的是各向异性材料。

2、除氧化铝外,其他陶瓷封装材料有哪些?氮化铝、碳化硅、氧化铍、玻璃陶瓷、钻⽯等材料。

【填空】6、⾦属与玻璃之间⼀般黏着性不佳。

7、控制玻璃在⾦属表⾯的湿润能⼒是形成稳定粘结最重要的技术。

8、玻璃密封材料的选择应与⾦属材料的种类配合。

9、酚醛树脂、硅胶等热硬化型塑胶为塑料封装最主要的材料。

【选择】5、塑料封装具有低成本、薄型化、⼯艺较为简单、适合⾃动化⽣产等优点。

6、玻璃密封的主要缺点是:强度低、脆性⾼。

7、通孔插装式安装器件⼜分为以下⼏种:(1)塑料双列直插式封装:(2)单列直插式封装(3)塑料针栅封装8、去溢料⽅法:机械喷沙、碱性电解法、化学浸泡+⾼压⽔喷法。

集成电路设计基础期末考试复习题

集成电路设计基础期末考试复习题1. 摩尔定律的内容:单位⾯积芯⽚上所能容纳的器件数量,每12-18个⽉翻⼀番。

2. 摩尔定律得以保持的途径:特征尺⼨不断缩⼩、增⼤芯⽚⾯积及单元结构的改进。

3. 图形的加⼯是通过光刻和刻蚀⼯艺完成的。

4. 在场区中,防⽌出现寄⽣沟道的措施:⾜够厚的场氧化层、场区注硼、合理的版图。

5. 形成SOI材料的三种主要技术:注氧隔离技术、键合减薄技术、智能剥离技术。

6. 实际的多路器和逆多路器中输⼊和输出⼀般是多位信息,如果对m个n位数据进⾏选择,则需要n位m选⼀多路器。

7. 在氧化层上形成所需要的图形的步骤:甩胶、曝光、显影、刻蚀、去胶。

8. 版图设计规则可以⽤两种形式给出:微⽶规则和⼊规则。

9. 常规CMOS结构的闩锁效应严重地影响电路的可靠性,解决闩锁效应最有效的办法是开发多晶硅技术。

10. 要实现四选⼀多路器,应该⽤2位⼆进制变量组成4个控制信号,控制4个数据的选择。

11. 摩尔分析了集成电路迅速发展的原因,他指出集成度的提⾼主要是三⽅⾯的贡献:特征尺⼨不断缩⼩、芯⽚⾯积不断增⼤、器件和电路结构的不断改进。

12. 缩⼩特征尺⼨的⽬的:使集成电路继续遵循摩尔定律提⾼集成密度;提⾼集成度可以使电⼦设备体积更⼩、速度更⾼、功耗更低;降低单位功能电路的成本,提⾼产品的性能/价格⽐,使产品更具竞争⼒。

13. N阱CMOS主要⼯艺步骤:衬底硅⽚的选择T制作n阱⼧场区氧化⼧制作硅栅⼧形成源、漏区T形成⾦属互连线。

14. 解决双极型晶体管纵向按⽐例缩⼩问题的最佳⽅案之⼀,就是采⽤多晶硅发射极结构,避免发射区离⼦注⼊对硅表⾯的损伤。

15. n输⼊与⾮门设计考虑,根据直流特性设计:Kr=KN/KP=n 3/2;根据瞬态特性设计:Kr=KN/KP=n 。

n输⼊或⾮门设计考虑,根据直流特性设计:Kr=KN/KP=n -3/2;根据瞬态特性设计:Kr= Kr=KN/KP=1/ n.16. CE等⽐例缩⼩定律要求器件的所有⼏何尺⼨,包括横向和纵向尺⼨,都缩⼩k倍;衬底掺杂浓度增⼤K倍;电源电压下降K倍。

《电路分析》课程期末考试卷(A)参考答案

《电路分析》课程期末考试卷(A )参考答案一、填空题 (10分,每空1分)1. (2010)D =( )B = ( )H = ( )8421BCD 答案:(111 1101 1010)B = (7DA )H = (0010 0000 0001 0000)8421BCD2. 仓库门上装了两把暗锁,A 、B 两位保管员各管一把锁的钥匙,必须二人同时开锁才能进库。

这种逻辑关系为 。

答案:与逻辑3. 逻辑函数式F=AB+AC 的对偶式为 ,最小项表达式为∑=m F ( )。

答案:))((C A B A FD++=∑=m F (5,6,7)2.逻辑函数D AC CD A C AB D C ABD ABC F ''''''+++++=的最简与或式是 。

答案:'D A +4. 从结构上看,时序逻辑电路的基本单元是 。

答案:触发器5. JK 触发器特征方程为 。

答案:Q K JQ ''+6.A/D 转换的一般步骤为:取样,保持, ,编码。

答案:量化二、选择题 (10分,每题1分)1. 计算机键盘上有101个键,若用二进制代码进行编码,至少应为( )位。

A) 6 B) 7 C) 8 D) 51 答案:B2. 在函数F=AB+CD 的真值表中,F=1的状态有( )个。

A) 2 B) 4 C) 6 D) 7 答案:D3. 为实现“线与”逻辑功能,应选用( )。

A) 与非门 B) 与门 C) 集电极开路(OC )门 D) 三态门答案:C 4. 图1所示逻辑电路为( )。

A) “与非”门 B) “与”门C)“或”门D) “或非”门ABC图1答案:A5. 在下列逻辑部件中,属于组合逻辑电路的是()。

A) 计数器B) 数据选择器C) 寄存器D) 触发器答案:B6. 已知某触发器的时钟CP,异步置0端为R D,异步置1端为S D,控制输入端V i和输出Q的波形如图2所示,根据波形可判断这个触发器是()。

集成电路期末考试知识点答案

集成电路期末考试知识点答案-------------------------------------------1------------------------------------------------1、哪一年在哪儿发明了晶体管?发明人哪一年获得了诺贝尔奖?1947贝尔实验室肖克来波拉坦巴丁发明了晶体管1956获诺贝尔奖2、世界上第一片集成电路是哪一年在哪儿制造出来的?发明人哪一年为此获得诺贝尔奖?Jack kilby 德州仪器公司1958年发明2000获诺贝尔奖3、什么是晶圆?晶圆的材料是什么?晶圆是指硅半导体集成电路制作所用的硅晶片,材料是硅4、目前主流集成电路设计特征尺寸已经达到多少?预计2016 年能实现量产的特征尺寸是多少?主流0.18um 22nm5、晶圆的度量单位是什么?当前主流晶圆的尺寸是多少?英寸12英寸6、摩尔是哪个公司的创始人?什么是摩尔定律?英特尔芯片上晶体管数每隔18个月增加一倍7、什么是SoC?英文全拼是什么?片上系统 System On Chip8、说出Foundry、Fabless 和Chipless 的中文含义。

代工无生产线无芯片9、一套掩模一般只能生产多少个晶圆?1000个晶圆10、什么是有生产线集成电路设计?电路设计在工艺制造单位内部的设计部门进行11、什么是集成电路的一体化(IDM)实现模式?设计制造和封装都集中在半导体生产厂家内进行12、什么是集成电路的无生产线(Fabless)设计模式?只设计电路而没有生产线13、一个工艺设计文件(PDK)包含哪些内容?器件的SPICE参数、版图设计用的层次定义、设计规则和晶体管电阻电容等器件以及通孔焊盘等基本结构版图,与设计工具关联的设计规则检查、参数提取、版图电路图对照用的文件。

14、设计单位拿到PDK 文件后要做什么工作?利用CAD/EDA工具进行电路设计仿真等一系列操作最终生成以GDS-II格式保存的版图文件,然后发给代工单位。

模拟集成电路设计考核试卷

B.乘法器

C.除法器

D.微分器

12.以下哪种放大器配置的输入阻抗最高?()

A.共源

B.共栅

C.差分

D.电压跟随器

13.在模拟集成电路中,以下哪个参数影响放大器的热噪声?()

A.电流

B.电压

C.频率

D.温度

14.以下哪个组件在模拟集成电路中用于调节电压?()

A.运算放大器

B.电压比较器

C.电压基准

D.电流镜

15.关于电流镜的描述,列哪项是正确的?()

A.提供电流增益

B.用于电压放大

C.用于电流采样

D.仅用于数字电路

16.以下哪种类型的反馈在放大器设计中可以稳定增益?()

A.电压反馈

B.电流反馈

C.负反馈

D.正反馈

17.在模拟集成电路设计中,以下哪个参数影响放大器的功率消耗?()

A.增益

B.驱动能力

A.功能测试

B.性能测试

C.热测试

D.安全测试

二、多选题(本题共20小题,每小题1.5分,共30分,在每小题给出的四个选项中,至少有一项是符合题目要求的)

1.模拟集成电路设计时,以下哪些因素会影响MOSFET的阈值电压?()

A.栅极长度

B.源漏间距

C.主体区掺杂浓度

D.温度

2.以下哪些是模拟集成电路中常见的噪声来源?()

A.增益带宽积

B.开环增益

C.输入阻抗

D.输出阻抗

9.在模拟集成电路中,下列哪个部分通常用于实现模拟开关的功能?()

A. MOSFET

B.二极管

C.晶体管

D.运算放大器

10.以下哪种类型的滤波器在模拟信号处理中用于去除高频噪声?()

(完整版)集成电路设计复习题及解答

集成电路设计复习题绪论1.画出集成电路设计与制造的主要流程框架。

2.集成电路分类情况如何?集成电路设计1.层次化、结构化设计概念,集成电路设计域和设计层次2.什么是集成电路设计?集成电路设计流程。

(三个设计步骤:系统功能设计逻辑和电路设计版图设计)3.模拟电路和数字电路设计各自的特点和流程4.版图验证和检查包括哪些内容?如何实现?5.版图设计规则的概念,主要内容以及表示方法。

为什么需要指定版图设计规则?6.集成电路设计方法分类?(全定制、半定制、PLD)7.标准单元/门阵列的概念,优点/缺点,设计流程8.PLD设计方法的特点,FPGA/CPLD的概念9.试述门阵列和标准单元设计方法的概念和它们之间的异同点。

10.标准单元库中的单元的主要描述形式有哪些?分别在IC设计的什么阶段应用?11.集成电路的可测性设计是指什么?Soc设计复习题1.什么是SoC?2.SoC设计的发展趋势及面临的挑战?3.SoC设计的特点?4.SoC设计与传统的ASIC设计最大的不同是什么?5.什么是软硬件协同设计?6.常用的可测性设计方法有哪些?7. IP的基本概念和IP分类8.什么是可综合RTL代码?9.么是同步电路,什么是异步电路,各有什么特点?10.逻辑综合的概念。

11.什么是触发器的建立时间(Setup Time),试画图进行说明。

12.什么是触发器的保持时间(Hold Time),试画图进行说明。

13. 什么是验证,什么是测试,两者有何区别?14.试画图简要说明扫描测试原理。

绪论1、 画出集成电路设计与制造的主要流程框架。

2、集成电路分类情况如何?集成电路设计1. 层次化、结构化设计概念,集成电路设计域和设计层次分层分级设计和模块化设计.将一个复杂的集成电路系统的设计问题分解为复杂性较低的设计级别,⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎧⎪⎪⎪⎪⎩⎪⎪⎪⎪⎨⎧⎩⎨⎧⎩⎨⎧⎪⎪⎪⎪⎩⎪⎪⎪⎪⎨⎧⎪⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎪⎨⎧⎩⎨⎧⎪⎪⎪⎪⎩⎪⎪⎪⎪⎨⎧⎩⎨⎧⎪⎩⎪⎨⎧按应用领域分类数字模拟混合电路非线性电路线性电路模拟电路时序逻辑电路组合逻辑电路数字电路按功能分类GSI ULSI VLSI LSI MSI SSI 按规模分类薄膜混合集成电路厚膜混合集成电路混合集成电路B iCMOS B iMOS 型B iMOS CMOS NMOS PMOS 型MOS双极型单片集成电路按结构分类集成电路这个级别可以再分解到复杂性更低的设计级别;这样的分解一直继续到使最终的设计级别的复杂性足够低,也就是说,能相当容易地由这一级设计出的单元逐级组织起复杂的系统。

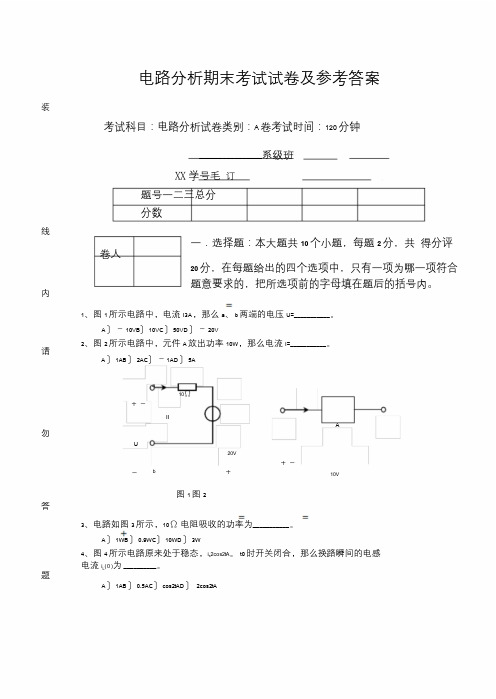

电路分析期末考试试卷与参考答案

电路分析期末考试试卷及参考答案装考试科目:电路分析试卷类别:A卷考试时间:120分钟________________系级班XX学号毛订题号一二三总分分数线一.选择题:本大题共10个小题,每题2分,共得分评卷人20分,在每题给出的四个选项中,只有一项为哪一项符合题意要求的,把所选项前的字母填在题后的括号内。

内1、图1所示电路中,电流I3A,那么a、b两端的电压U=___________。

A〕-10VB〕10VC〕50VD〕-20V请2、图2所示电路中,元件A放出功率10W,那么电流I=___________。

A〕1AB〕2AC〕-1AD〕5Aa10Ω+-IIA勿U20V- b ++-10V图1图2答3、电路如图3所示,10Ω电阻吸收的功率为___________。

A〕1WB〕0.9WC〕10WD〕3W4、图4所示电路原来处于稳态,i s2cos2tA。

t0时开关闭合,那么换路瞬间的电感题电流i L(0)为__________。

A〕1AB〕0.5AC〕cos2tAD〕2cos2tA-1-2Ω+1Ai s S12V 10Ω2H+2Ωt=0i L-9V-图4图35、一个2A的电流源对初始储能为0的0.1F电容充电5秒钟后,那么该电容获得的能量为__________。

A〕50JB〕500JC〕100JD〕0J6、某电路的阻抗为Z10j5,那么该电路的导纳Y的实部为__________。

A〕0.2SB〕0.08SC〕0.04SD〕0.1S7、假设RLC串联电路的谐振频率为f01000Hz,那么当频率为900Hz的正弦电压源鼓励时,该电路呈__________。

A〕阻性B〕感性C〕容性D〕不能确定8、图8所示二端网络的功率因数为__________。

A〕0B〕1C〕-0.707D〕0.7079、图9所示电路已处于稳态,t0时开关翻开,那么电感电压的初始值u L(0)为_________。

10A〕-25VB〕25VC〕0VD〕V7S2Ω+t=012Ωj6Ω++u L3H10V5Ωu-j18Ω-i L--图8图910、图10所示二端网络的戴维南等效支路的参数为__________。

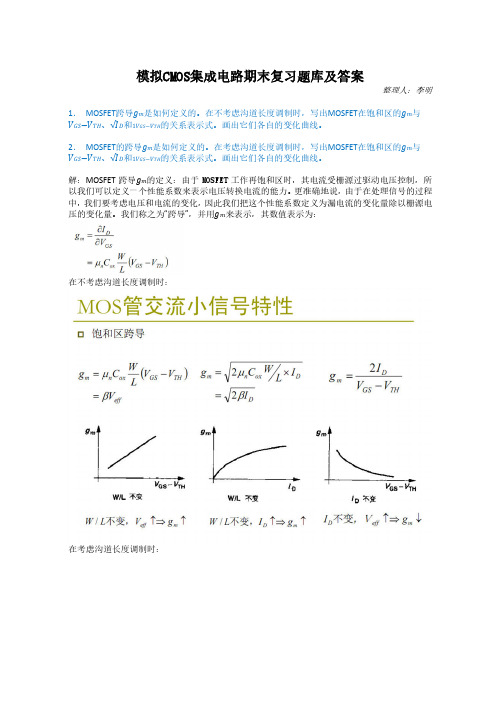

模拟CMOS集成电路复习题库及解答

模拟CMOS集成电路期末复习题库及答案整理人:李明1.MOSFET跨导g m是如何定义的。

在不考虑沟道长度调制时,写出MOSFET在饱和区的g m与V GS−V TH、√I D和1V GS−V TH的关系表示式。

画出它们各自的变化曲线。

2.MOSFET的跨导g m是如何定义的。

在考虑沟道长度调制时,写出MOSFET在饱和区的g m与V GS−V TH、√I D和1V GS−V TH的关系表示式。

画出它们各自的变化曲线。

解:MOSFET跨导g m的定义:由于MOSFET工作再饱和区时,其电流受栅源过驱动电压控制,所以我们可以定义一个性能系数来表示电压转换电流的能力。

更准确地说,由于在处理信号的过程中,我们要考虑电压和电流的变化,因此我们把这个性能系数定义为漏电流的变化量除以栅源电压的变化量。

我们称之为“跨导”,并用g m来表示,其数值表示为:在不考虑沟道长度调制时:在考虑沟道长度调制时:3.画出考虑体效应和沟道长度调制效应后的MOSFET小信号等效电路。

写出r o和g mb的定义,并由此定义推出r o和g mb表示式。

解:4.画出由NMOS和PMOS二极管作负载的MOSFET共源级电路图。

对其中NMOS二极管负载共源级电路,推出忽略沟道长度调制效应后的增益表示式,分析说明器件尺寸和偏置电流对增益的影响。

对PMOS二极管负载的共源级电路,对其增益表示式作出与上同样的分析。

5.画出MOS共源共栅级电路的电路图和其对应的小信号等效电路图。

并推出此共源共栅级电路的电压增益和输出电阻表示式。

解:6.画出带源极负反馈电阻的以电阻作负载的MOS共源级电路的电路图和其对应的小信号等效电路图。

写出此电路的等效跨导定义式,并由此推出在不考虑沟道长度调制和体效应情况下的小信号电压增益表示式。

画出其漏电流和跨导随V in的变化曲线图。

7.画出带源极负反馈电阻的以电阻作负载的MOS共源级电路的电路图和其对应的小信号等效电路图。

模拟集成电路设计期末试卷

(2)

2、画出差动对的输入输出特性曲线(ΔID~ΔVin)。

要求:(1)标出曲线中关键转折点和极限点的坐标;

(2)由图分析:通过什么措施可以使差动对的线性度更好。

解:

其中, ,增大ISS或减小W/L,可使电路的线性更好。

四.简答((每题7分,共21分))

1、“MOS器件即使没有传输电流也可能导通”,这种说法正确么?为什么?

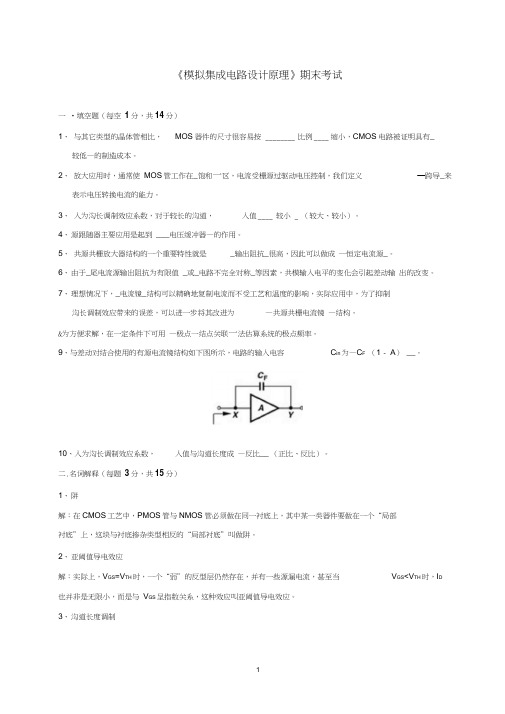

《模拟集成电路设计原理》期末考试

一.填空题(每空1分,共14分)

1、与其它类型的晶体管相比,MOS器件的尺寸很容易按____比例____缩小,CMOS电路被证明具有_较低__的制造成本。

2、放大应用时,通常使MOS管工作在_饱和_区,电流受栅源过驱动电压控制,我们定义_跨导_来表示电压转换电流的能力。

4、(9分)画出下图共源极高频模型的小信号等效电路,并利用小信号模型精确推导系统的极点频率。

解:(1)I3=I4=50μA,I5=I6=200μA,I7=500μA

(2)γ=0:VP=0.368V

γ=0.45V-1:VTH1(VP=0.368V)=0.78V,VP1=0.288V;VTH2(VP1=0.288V)=0.764V,VP2=0.304;VTH3(VP2=0.304V)=0.767V,VP3=0.301;VTH4(VP3=0.301V)=0.766V,VP4=0.302;VTH5(VP4=0.302V)=0.766V,VP4=0.302…….所以VP≈0.302V

解:可能。当 时,器件工作在深线性区,此时虽然足够的VGS可以满足器件的导通条件,但是VDS很小,以至于没有传输电流

五.分析计算题(共34分)

(下列题目中使用教材表2.1所列的器件数据,所有器件尺寸都是有效值,单位均为微米。)

《模拟集成电路设计原理》期末考试试卷及答案

《软件工程基础训练》实训报告在倒入酒的方法中,首先判断当前酒量是否已经达到酒杯的容量。

如果是,则提示酒杯已满;如果不是,则将倒入的酒量加到当前酒量上。

实现一个方法,用于从酒杯中倒出酒。

该方法接受一个参数,表示要倒出的酒量。

在倒出酒的方法中,首先判断当前酒量是否大于等于要倒出的酒量。

如果是,则将当前酒量减去要倒出的酒量;如果不是,则提示酒量不足。

实现一个方法,用于获取当前酒量。

在获取酒量的方法中,直接返回当前酒量的值。

2.1.3程序流程图图 12.1.4设计代码package wmx;import java.io.BufferedReader;import java.io.IOException;import java.io.InputStreamReader;import java.util.StringTokenizer;public class Main1 {}}}}2.1.5代码运行截图图 22.2第二阶段2.2.1需求分析明确问题定义:首先需要明确问题的背景和涉及的实体,例如旅行者、手电筒、桥等。

同时,需要确定问题的目标,即如何让所有人尽快过桥。

确定约束条件:根据问题的描述,我们知道有一些约束条件,例如每个人过桥的速度不同,手电筒不能扔掉,只能两个人同时过桥等。

这些约束条件将影响解决方案的设计。

分析时间需求:由于目标是尽快让所有人过桥,因此需要分析每个人过桥所需的时间。

这将影响如何分配手电筒和如何安排过桥的顺序。

制定策略:基于上述分析,需要制定一个有效的策略来最大化过桥的速度。

这可能涉及到如何分配手电筒,如何安排过桥的顺序,以及如何返回等。

评估和优化:最后,需要对所制定的策略进行评估和优化。

这可能涉及到对策略的模拟、测试和比较,以便找到最优的解决方案。

2.2.2设计思路这是一个经典的过桥问题,通常称为“蒙提霍尔问题”。

在这个问题中,目标是让所有人尽快过桥。

根据题目的条件,每个人单独过桥的时间是已知的,但是两个人一起过桥的时间是较慢的那个人所需的时间。

集成电路期末试题及答案

集成电路期末试题及答案Michael Chen2022年1月10日第一部分:选择题1. 集成电路是指()A. 多个电路板连接在一起B. 多个电子元件连接在一起C. 多个电气设备连接在一起D. 多个电子器件集成在一起答案:D2. 集成电路的分类依据是()A. 外部尺寸B. 工作原理C. 制造工艺D. 功耗大小答案:C3. 集成电路的封装形式包括()A. DIPB. SIPC. QFPD. 以上都是E. 以上都不是答案:D4. CMOS是指()A. 生物科学中的一种病毒B. 一种通信协议C. 一种数字电路设计技术D. 一种模拟电路设计技术答案:C5. 集成电路的发展趋势是()A. 更小封装B. 更低功耗C. 更高速度D. 以上都是答案:D第二部分:填空题1. 集成电路的最早应用是在(电子计算机)中。

2. 集成电路制造工艺的重要步骤包括薄膜沉积、光刻和(蚀刻)。

3. 集成电路的数字功耗由(开关功耗)和(短路功耗)组成。

4. 集成电路的封装形式除了DIP、SIP、QFP外,还有(BGA)。

5. 集成电路的发展史上的一个重要里程碑是第一个微处理器(Intel 4004)的发布。

第三部分:简答题1. 请简要解释集成电路的概念,并举例说明。

答:集成电路是将多个电子器件(如晶体管、电容器等)集成在一个芯片上的电路。

通过微影工艺在芯片上形成电路连接,实现各种电路功能。

例如,常见的操作放大器、时钟芯片、存储器等都是利用集成电路技术制造的。

2. 请介绍集成电路制造工艺中的薄膜沉积步骤。

答:薄膜沉积是集成电路制造工艺中的重要步骤之一。

它通过在芯片表面上沉积一层薄膜,为后续工艺提供基础。

常用的薄膜沉积工艺包括物理气相沉积(PVD)和化学气相沉积(CVD)。

PVD是通过物理方法将金属或其它物质蒸发或溅射到芯片表面形成薄膜;CVD则是通过化学反应使气相中的化合物在芯片表面沉积。

薄膜沉积可以实现金属导线、绝缘层等结构的形成,为后续的光刻、蚀刻工艺提供基础。

模拟集成电路设计期末试卷word精品

《模拟集成电路设计原理》期末考试一•填空题(每空1分,共14分)1、与其它类型的晶体管相比,MOS器件的尺寸很容易按________ 比例____ 缩小,CMOS电路被证明具有_较低—的制造成本。

2、放大应用时,通常使MOS管工作在_饱和一区,电流受栅源过驱动电压控制,我们定义—跨导_来表示电压转换电流的能力。

3、入为沟长调制效应系数,对于较长的沟道,入值____ 较小 _ (较大、较小)。

4、源跟随器主要应用是起到___电压缓冲器—的作用。

5、共源共栅放大器结构的一个重要特性就是_输出阻抗_很高,因此可以做成―恒定电流源_。

6、由于_尾电流源输出阻抗为有限值_或_电路不完全对称_等因素,共模输入电平的变化会引起差动输出的改变。

7、理想情况下,_电流镜_结构可以精确地复制电流而不受工艺和温度的影响,实际应用中,为了抑制沟长调制效应带来的误差,可以进一步将其改进为—共源共栅电流镜—结构。

&为方便求解,在一定条件下可用—极点一结点关联一法估算系统的极点频率。

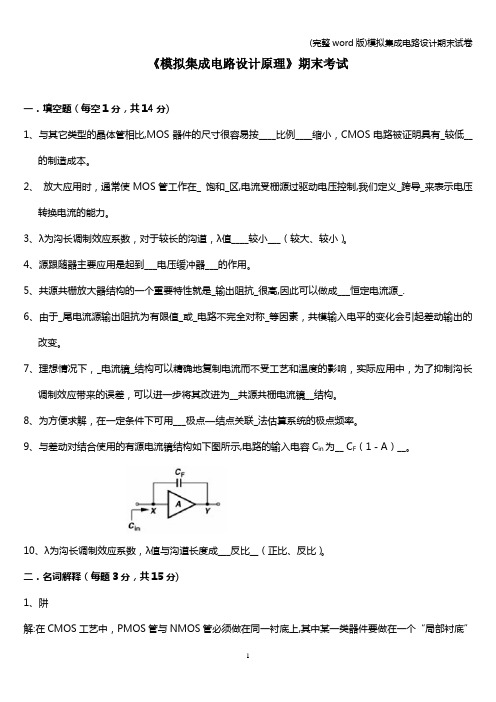

9、与差动对结合使用的有源电流镜结构如下图所示,电路的输入电容C in为—C F(1 - A)__。

10、入为沟长调制效应系数,入值与沟道长度成—反比__ (正比、反比)。

二.名词解释(每题3分,共15分)1、阱解:在CMOS工艺中,PMOS管与NMOS管必须做在同一衬底上,其中某一类器件要做在一个“局部衬底”上,这块与衬底掺杂类型相反的“局部衬底”叫做阱。

2、亚阈值导电效应解:实际上,V GS=V TH时,一个“弱”的反型层仍然存在,并有一些源漏电流,甚至当V GS<V TH时,I D也并非是无限小,而是与V GS呈指数关系,这种效应叫亚阈值导电效应。

3、沟道长度调制解:当栅与漏之间的电压增大时,实际的反型沟道长度逐渐减小,也就是说, 这种效应称为沟道长度调制。

4、等效跨导Gm6、N 阱:解:CMOS 工艺中,PMOS 管与NMOS 管必须做在同一衬底上,若衬底为 P 型,贝U PMOS 管要做在个N 型的“局部衬底”上,这块与衬底掺杂类型相反的N 型“局部衬底”叫做 N 阱。

模拟集成电路试题

模拟集成电路试题一、单项选择题(每题2分,共20分)1. 在模拟集成电路设计中,以下哪种器件不是基本的构成元件?A. 晶体管B. 电阻C. 电容D. 电感2. 运算放大器的差分输入电压是指:A. 同相输入端与反相输入端之间的电压差B. 同相输入端与输出端之间的电压差C. 反相输入端与输出端之间的电压差D. 输出端与地之间的电压差3. 以下哪个参数不是模拟集成电路中的噪声参数?A. 噪声功率谱密度B. 噪声电压C. 噪声电流D. 增益带宽积4. 在模拟集成电路中,电流源的主要作用是什么?A. 提供稳定的电流B. 提供稳定的电压C. 作为信号的放大器D. 作为信号的滤波器5. 模拟集成电路中的反馈通常用于:A. 增加增益B. 减少增益C. 增加稳定性D. 减少稳定性6. 以下哪个不是模拟集成电路中的放大器类型?A. 共发射极放大器B. 共基极放大器C. 共集电极放大器D. 共栅极放大器7. 在模拟集成电路设计中,温度补偿的目的是什么?A. 增加电路的增益B. 减少电路的功耗C. 保持电路性能在不同温度下稳定D. 提高电路的响应速度8. 模拟集成电路中的带宽通常指的是:A. 电路可以处理的最高频率B. 电路可以处理的最低频率C. 电路可以处理的最大电流D. 电路可以处理的最大电压9. 以下哪个参数不是模拟集成电路中的失真参数?A. 谐波失真B. 互调失真C. 相位失真D. 增益10. 在模拟集成电路中,电源电压的变化对电路性能的影响主要体现在:A. 增益的变化B. 功耗的变化C. 频率响应的变化D. 以上都是二、填空题(每题2分,共20分)1. 模拟集成电路中的______放大器通常用于实现高输入阻抗和低输出阻抗。

2. 在模拟集成电路中,为了减少噪声,常常使用______作为输入级。

3. 模拟集成电路中的______效应是指由于温度变化引起的参数变化。

4. 模拟集成电路中的______是指电路对不同频率信号的响应能力。

集成模拟考试题及答案

集成模拟考试题及答案# 集成模拟考试题及答案一、选择题1. 在模拟电路中,以下哪个元件不是基本的模拟元件?A. 电阻B. 电容C. 电感D. 逻辑门答案:D2. 以下哪个不是数字信号的特点?A. 离散性B. 确定性C. 连续性D. 随机性答案:C3. 在数字电路设计中,以下哪个不是常用的逻辑门?A. AND门B. OR门C. XOR门D. NOT门答案:D(NOT门是最基本的逻辑门之一)二、填空题1. 模拟信号具有______和______的特点。

2. 数字信号的传输方式主要有______和______。

答案:1. 连续性,不确定性2. 并行传输,串行传输三、简答题1. 简述模拟信号与数字信号的区别。

答案:模拟信号是连续变化的信号,可以表示任何连续的波形,如声音、温度等。

数字信号则是离散的,它表示的是一系列离散的值,通常用二进制数表示。

模拟信号与数字信号的主要区别在于模拟信号是连续的,而数字信号是离散的。

四、计算题1. 假设有一个RC电路,其中R=1kΩ,C=1μF,求该电路的充电时间常数τ。

答案:充电时间常数τ由公式τ=RC计算得出,代入数值得到τ=1kΩ*1μF=1秒。

五、论述题1. 论述数字电路与模拟电路在现代电子系统中各自的优势和应用场景。

答案:数字电路的优势在于其处理速度快,可靠性高,易于实现大规模集成,适合用于计算机、通信设备等需要高速处理和精确控制的场合。

模拟电路则在处理连续信号方面具有优势,如音频放大、信号调制解调等,它们在需要模拟信号处理的场合中不可或缺。

结束语:本次集成模拟考试题涵盖了模拟与数字电路的基本概念、特点、区别及其应用场景,旨在帮助考生全面复习和掌握相关知识点。

希望考生能够通过本次模拟考试,加深对电路基础知识的理解,为实际应用打下坚实的基础。

(完整word版)模拟集成电路设计期末试卷

《模拟集成电路设计原理》期末考试一.填空题(每空1分,共14分)1、与其它类型的晶体管相比,MOS器件的尺寸很容易按____比例____缩小,CMOS电路被证明具有_较低__的制造成本。

2、放大应用时,通常使MOS管工作在_ 饱和_区,电流受栅源过驱动电压控制,我们定义_跨导_来表示电压转换电流的能力。

3、λ为沟长调制效应系数,对于较长的沟道,λ值____较小___(较大、较小)。

4、源跟随器主要应用是起到___电压缓冲器___的作用。

5、共源共栅放大器结构的一个重要特性就是_输出阻抗_很高,因此可以做成___恒定电流源_.6、由于_尾电流源输出阻抗为有限值_或_电路不完全对称_等因素,共模输入电平的变化会引起差动输出的改变。

7、理想情况下,_电流镜_结构可以精确地复制电流而不受工艺和温度的影响,实际应用中,为了抑制沟长调制效应带来的误差,可以进一步将其改进为__共源共栅电流镜__结构。

8、为方便求解,在一定条件下可用___极点—结点关联_法估算系统的极点频率。

9、与差动对结合使用的有源电流镜结构如下图所示,电路的输入电容C in为__ C F(1-A)__。

10、λ为沟长调制效应系数,λ值与沟道长度成___反比__(正比、反比)。

二.名词解释(每题3分,共15分)1、阱解:在CMOS工艺中,PMOS管与NMOS管必须做在同一衬底上,其中某一类器件要做在一个“局部衬底”上,这块与衬底掺杂类型相反的“局部衬底”叫做阱。

2、亚阈值导电效应解:实际上,V GS =V TH 时,一个“弱”的反型层仍然存在,并有一些源漏电流,甚至当V GS <V TH 时,I D 也并非是无限小,而是与V GS 呈指数关系,这种效应叫亚阈值导电效应。

3、沟道长度调制解:当栅与漏之间的电压增大时,实际的反型沟道长度逐渐减小,也就是说,L 实际上是V DS 的函数,这种效应称为沟道长度调制。

4、等效跨导Gm解:对于某种具体的电路结构,定义inDV I ∂∂为电路的等效跨导,来表示输入电压转换成输出电流的能力 5、米勒定理解:如果将图(a )的电路转换成图(b )的电路,则Z 1=Z/(1-A V ),Z 2=Z/(1—A V -1),其中A V =V Y /V X .这种现象可总结为米勒定理。

2010级硕士模拟集成电路分析与设计期末复习题-解答

2010级研究生《模拟集成电路分析与设计》复习自己的解答一、Questions :1.What is the problem of simple differential circuit? How to solve this problem?Answer: If V in, CM is low output will be clipped. Solve method: use differential pair.2.Describe advantages and drawbacks of differential signals comparing with single-ended signal. Answer: Advantages: Higher immunity to environment noise(对环境噪声更具抗干扰能力); Reduce coupled noise in transmission line(减少相邻信号线传输时受的干扰); Reject supply noise; Increase output voltage swing;Simpler biasing;Higher linearityDrawbacks: occupy twice areas3. Why analog design needed in Optical Receivers?Answer: High frequency signals are not suitable for transmitting over long distance in the traditional cable due to the severe interference and considerable attenuation because of the limited bandwidth of the cable. In this case, the electrical high frequency signals are converted into the optical signals first by the laser diode, then these optic signals are transmitted by an optical fiber, which has extremely wide band and very low loss. In the other end, the optical signals are converted into electrical signals again by the photodiode.书(中)P3;(英)P4 4. Which two figures play most important role in technology nodes scaling down? Please describe in detail.Answer: Minimum channel length often represents the technology nodes. Oxide thickness often affects the threshold voltage and the power supply.5. If there is a small mismatch between M1 and M2, how do the parameters of the transistorsaffect the common mode rejection ratio (CMRR) of a differential pair?(中)P1016. Write the input pole of the circuit in Fig. 1.Answer: The input pole: ωin =1/[R S (1+A)C F ]7. When both NMOS and PMOS devices are needed to be placed on one chip, what is needed? Answer: N-Well or P-Well is needed.8. What is the problem for the circuit in Fig. 2? Any suggestions to solve it?Answer: Small-signal drain current of M1 is “wasted”. Solve method: Use differential pair with active current mirror to combine the small-signal current together.)arg ()21(242121e l too not is mismatch if R g g g g R g g g g A A CMRR SS m mmmSSm m m m DMCM DM DM +∆≈∆++==--9. Among the output noise and the input-referred noise, which one is more popular to be used inthe circuit simulation? Why?Answer: Since the output noise depends on the gain, it is hard to fairly compare the effects of noise of different circuits because of the different gain. Therefore, the input-referred noise is more popular to be used in the circuit simulation.10. Refer to Fig. 3, what benefits do we have for using cascode structure in current source? And any drawbacks?Answer: Advantages: Largely reduce the change so that V Y is more close to V X , and hence I out more closely track I REF.Drawbacks: Cost higher voltage headroom.11. Can we use the statistical value of noise amplititude ? If the answer is no, then what weusually use when considering the noise in circuit systems? Explain the reason.Answer: No. Because the statistical value of noise amplitude over time domain is zero. Fortunately the statistical value of power overall time domain is not zero. So we usually incorporate average power of a random signal in circuit analysis. 12. Explain why use diode-connected for M1 in Fig. 4 Answer: Diode-connected to ensure M1 always in saturation.13. Describe the steps for calculating the loop gain of a feedback system. And calculate LG in Fig. 5 following the steps.Answer: Step 1: Set the main input to zero; Step 2: Break the loop at some point;Step 3: Inject a test signal in the “right direction”;Step 4: Follow the signal around the loop;Fig.1Fig. 3Fig. 2)(0=⎰∞dt t xStep 5: Obtain the value that returns to the break point;Step 6: The negative of the transfer function derived is the loop gain;14. What is CMRR? Write down the definition of it. Answer: Common mode rejection ratio (共模抑制比):Where gm denotes the mean value: gm=(gm1+gm2)/215. Write the input and output pole of the circuit in Fig. 6, ignoring the effect of C Gs and R S on C out . Answer: Low frequency gain:Using Miller’ Theorem:Therefore, the input pole is:If not consider the effect of R s and C GS on C out , Using Miller’ Theorem again:The output pole can be written as:16. Plot a diagram of a simple PLL and explain the working principle of it in short.Answer:Phase detector (PD) compares the phases of V out and Vin, generating an error signal; Low-pass filter (LPF) transfer the error wave to a dc level to the oscillator; The dc level can control the output frequency by VCO;In this way, the frequency and phase of V out can be locked to Vin.17. What is Power spectral density (PSD)? Use the expression and the plot to show it.Answer:(书)表示在每个频率上信号具有的功率大小。

模拟集成电路试题及答案

模拟集成电路试题及答案一、选择题1. 在模拟集成电路设计中,以下哪个因素不是影响电路性能的主要因素?A. 晶体管的尺寸B. 电源电压C. 温度D. 电路的布局答案:D2. 以下哪个不是模拟集成电路中的放大器类型?A. 共射放大器B. 共基放大器C. 共栅放大器D. 差分放大器答案:C二、填空题1. 在模拟集成电路中,________是用来减少晶体管的热噪声。

答案:晶体管的尺寸2. 模拟集成电路设计中,________是一种常用的信号处理方法。

答案:反馈三、简答题1. 简述模拟集成电路中使用差分放大器的优点。

答案:差分放大器的优点包括:- 提高了信号的共模抑制比(CMRR)。

- 减少了温度漂移。

- 增强了电路的稳定性。

2. 解释模拟集成电路中反馈的概念及其作用。

答案:反馈是指将放大器输出的一部分信号以某种方式返回到输入端。

反馈的作用包括:- 稳定放大器的增益。

- 减少非线性失真。

- 提高电路的带宽。

四、计算题1. 给定一个共射放大器,其基极电阻Rb=1kΩ,集电极电流Ic=2mA,求集电极电压Vc。

答案:首先计算集电极电阻Rc的值,Rc = Vcc / Ic,假设Vcc为5V,则Rc = 5V / 0.002A = 2.5kΩ。

然后计算Vc,Vc = Vcc - Ic * Rc= 5V - 0.002A * 2.5kΩ = 2.5V。

2. 假设一个差分放大器的差模增益为Ad,共模增益为Ac,求差模增益与共模增益的比值。

答案:差模增益与共模增益的比值即共模抑制比(CMRR),CMRR = Ad / Ac。

五、论述题1. 论述模拟集成电路设计中,如何通过电路设计来减少噪声和干扰。

答案:在模拟集成电路设计中,减少噪声和干扰的方法包括:- 使用低噪声元件。

- 优化电源管理,确保电源稳定性。

- 采用适当的布局和布线技术,减少电磁干扰。

- 使用屏蔽和接地技术来减少外部噪声的影响。

- 应用适当的信号处理技术,如滤波和信号隔离。

2010级硕士模拟集成电路分析与设计期末复习题-解答-推荐下载

2010级研究生《模拟集成电路分析与设计》复习自己的解答一、Questions :1.What is the problem of simple differential circuit? How to solve this problem?Answer: If V in, CM is low output will be clipped. Solve method: use differential pair.2.Describe advantages and drawbacks of differential signals comparing with single-ended signal.Answer: Advantages: Higher immunity to environment noise(对环境噪声更具抗干扰能力);Reduce coupled noise in transmission line(减少相邻信号线传输时受的干扰);Reject supply noise; Increase output voltage swing; Simpler biasing; Higher linearityDrawbacks: occupy twice areas3. Why analog design needed in Optical Receivers?Answer: High frequency signals are not suitable for transmitting over long distance in the traditional cable due to the severe interference and considerable attenuation because of the limited bandwidth of the cable. In this case, the electrical high frequency signals are converted into the optical signals first by the laser diode, then these optic signals are transmitted by an optical fiber, which has extremely wide band and very low loss. In the other end, the optical signals are converted into electrical signals again by the photodiode.书(中)P3;(英)P44. Which two figures play most important role in technology nodes scaling down? Please describe in detail.Answer: Minimum channel length often represents the technology nodes. Oxide thickness often affects the threshold voltage and the power supply.5. If there is a small mismatch between M1 and M2, how do the parameters of the transistorsaffect the common mode rejection ratio (CMRR) of a differential pair?(中)P1016. Write the input pole of the circuit in Fig. 1.Answer: The input pole: ωin =1/[R S (1+A)C F ]7. When both NMOS and PMOS devices are needed to be placed on one chip, what is needed?Answer: N-Well or P-Well is needed.8. What is the problem for the circuit in Fig. 2? Any suggestions to solve it?Answer: Small-signal drain current of M1 is “wasted”. Solve method: Use differential pair with active current mirror to combine the small-signal current together.)arg ()21(242121e l too not is mismatch if R g g g g R g g g g A A CMRR SS m mm m SS m m m m DM CM DM DM +∆≈∆++==--9. Among the output noise and the input-referred noise, which one is more popular to be used inthe circuit simulation? Why?Answer: Since the output noise depends on the gain, it is hard to fairly compare the effects ofnoise of different circuits because of the different gain. Therefore, the input-referred noise ismore popular to be used in the circuit simulation.10. Refer to Fig. 3, what benefits do we have for using cascode structure in current source? And any drawbacks?Answer: Advantages: Largely reduce the change so that V Y is more close to V X , and hence I out more closely track I REF.Drawbacks: Cost higher voltage headroom.11. Can we use the statistical value of noise amplititude ? If the answer is no, then what weusually use when considering the noise in circuit systems? Explain the reason. Answer:the statistical value of power overall time domain is not zero. So we usually incorporate averagepower of a random signal in circuit analysis.12. Explain why use diode-connected for M1 in Fig. 4Answer: Diode-connected to ensure M1 always in saturation.13. Describe the steps for calculating the loop gain of a feedback system. Andcalculate LG in Fig. 5 following the steps.Answer: Step 1: Set the main input to zero;Step 2: Break the loop at some point;Step 3: Inject a test signal in the “right direction”; Step 4: Follow the signal around the loop;Fig.1Fig. 3Fig. 20)(0=⎰∞dt t xStep 5: Obtain the value that returns to the break point; Step 6: The negative of the transfer function derived is the loop gain;14. What is CMRR? Write down the definition of it.Answer: Common mode rejection ratio (共模抑制比):Where gm denotes the mean value: gm=(gm1+gm2)/215. Write the input and output pole of the circuit in Fig. 6, ignoring the effect of C Gs and R S on C out .Answer: Low frequency gain:Using Miller’ Theorem: Therefore, the input pole is: If not consider the effect of R s and C GS on C out , Using Miller’ Theorem again: The output pole can be written as: 16. Plot a diagram of a simple PLL and explain the working principle of it in short.Answer:Phase detector (PD) compares the phases of Vout and Vin, generating an error signal;Low-pass filter (LPF) transfer the error wave to a dc level to the oscillator;The dc level can control the output frequency by VCO;In this way, the frequency and phase of Vout can be locked to Vin.17. What is Power spectral density (PSD)? Use the expression and the plot to show it.Answer:(书)表示在每个频率上信号具有的功率大小。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2010级研究生《模拟集成电路分析与设计》复习自己的解答一、Questions :1.What is the problem of simple differential circuit? How to solve this problem?Answer: If V in, CM is low output will be clipped. Solve method: use differential pair.2.Describe advantages and drawbacks of differential signals comparing with single-ended signal. Answer: Advantages: Higher immunity to environment noise(对环境噪声更具抗干扰能力); Reduce coupled noise in transmission line(减少相邻信号线传输时受的干扰); Reject supply noise; Increase output voltage swing;Simpler biasing;Higher linearityDrawbacks: occupy twice areas3. Why analog design needed in Optical Receivers?Answer: High frequency signals are not suitable for transmitting over long distance in the traditional cable due to the severe interference and considerable attenuation because of the limited bandwidth of the cable. In this case, the electrical high frequency signals are converted into the optical signals first by the laser diode, then these optic signals are transmitted by an optical fiber, which has extremely wide band and very low loss. In the other end, the optical signals are converted into electrical signals again by the photodiode.书(中)P3;(英)P4 4. Which two figures play most important role in technology nodes scaling down? Please describe in detail.Answer: Minimum channel length often represents the technology nodes. Oxide thickness often affects the threshold voltage and the power supply.5. If there is a small mismatch between M1 and M2, how do the parameters of the transistorsaffect the common mode rejection ratio (CMRR) of a differential pair?(中)P1016. Write the input pole of the circuit in Fig. 1.Answer: The input pole: ωin =1/[R S (1+A)C F ]7. When both NMOS and PMOS devices are needed to be placed on one chip, what is needed? Answer: N-Well or P-Well is needed.8. What is the problem for the circuit in Fig. 2? Any suggestions to solve it?Answer: Small-signal drain current of M1 is “wasted”. Solve method: Use differential pair with active current mirror to combine the small-signal current together.)arg ()21(242121e l too not is mismatch if R g g g g R g g g g A A CMRR SS m mmmSSm m m m DMCM DM DM +∆≈∆++==--9. Among the output noise and the input-referred noise, which one is more popular to be used inthe circuit simulation? Why?Answer: Since the output noise depends on the gain, it is hard to fairly compare the effects of noise of different circuits because of the different gain. Therefore, the input-referred noise is more popular to be used in the circuit simulation.10. Refer to Fig. 3, what benefits do we have for using cascode structure in current source? And any drawbacks?Answer: Advantages: Largely reduce the change so that V Y is more close to V X , and hence I out more closely track I REF.Drawbacks: Cost higher voltage headroom.11. Can we use the statistical value of noise amplititude ? If the answer is no, then what weusually use when considering the noise in circuit systems? Explain the reason.Answer: No. Because the statistical value of noise amplitude over time domain is zero. Fortunately the statistical value of power overall time domain is not zero. So we usually incorporate average power of a random signal in circuit analysis. 12. Explain why use diode-connected for M1 in Fig. 4 Answer: Diode-connected to ensure M1 always in saturation.13. Describe the steps for calculating the loop gain of a feedback system. And calculate LG in Fig. 5 following the steps.Answer: Step 1: Set the main input to zero; Step 2: Break the loop at some point;Step 3: Inject a test signal in the “right direction”;Step 4: Follow the signal around the loop;Fig.1Fig. 3Fig. 2)(0=⎰∞dt t xStep 5: Obtain the value that returns to the break point;Step 6: The negative of the transfer function derived is the loop gain;14. What is CMRR? Write down the definition of it. Answer: Common mode rejection ratio (共模抑制比):Where gm denotes the mean value: gm=(gm1+gm2)/215. Write the input and output pole of the circuit in Fig. 6, ignoring the effect of C Gs and R S on C out . Answer: Low frequency gain:Using Miller’ Theorem:Therefore, the input pole is:If not consider the effect of R s and C GS on C out , Using Miller’ Theorem again:The output pole can be written as:16. Plot a diagram of a simple PLL and explain the working principle of it in short.Answer:Phase detector (PD) compares the phases of V out and Vin, generating an error signal; Low-pass filter (LPF) transfer the error wave to a dc level to the oscillator; The dc level can control the output frequency by VCO;In this way, the frequency and phase of V out can be locked to Vin.17. What is Power spectral density (PSD)? Use the expression and the plot to show it.Answer:(书)表示在每个频率上信号具有的功率大小。