集成电路测试论文

集成电路综述论文

集成电路的过去、现在和未来摘要:本文简要介绍了集成电路的发展历史、发展现状和发展前景。

着重介绍了集成电路技术在一些领域的应用和我国集成电路产业的现状和发展。

关键词:集成电路技术应用电子信息技术一、发展历史集成电路的发明和应用是人类20世纪科技发展史上一颗最为璀璨的明珠。

50多年来,集成电路不仅给经济繁荣、社会进步和国家安全等方面带来了巨大成功,而且改变了人们的生产、生活和思维方式。

当前集成电路已是无处不有、无时不在。

她已经成为人类文明不可缺乏的重要内容。

1949年12月23日,美国贝尔实验室的肖克莱、巴丁和布拉顿三人研究小组发现了晶体管效应,并在此基础上制出了世界上第一枚锗点接触晶体管,从此开创了人类大规模利用半导体的新时代。

两年后肖克莱首次提出了晶体管理论。

1953年出现了锗合金晶体管,1955年又出现了扩散基区锗合金晶体管。

1957年美国仙童公司利用硅晶片上热生长二氧化硅工艺制造出世界上第一只硅平面晶体管。

从此,硅成为人类利用半导体材料的主要角色。

1958年美国德州仪器公司青年工程师基尔比制作出世界上第一块集成电路。

1960年初美国仙童公司的诺依思制造出第一块实用化的集成电路芯片。

集成电路的发明为人类开创了微电子时代的新纪元。

在此后的五十多年里,集成电路技术发展迅速,至今,半导体领域中获得过诺贝尔物理奖的发明创造已有5项。

晶体管由于其广泛的用途而被迅速投入工业生产,“硅谷”成为世界集成电路的策源地,并由此向世界多个国家和地区辐射:上世纪60年代向西欧辐射,70年代向日本转移,80年代又向韩国、我国台湾和新加坡转移。

至上世纪90年代,集成电路产业已成为一个高度国际化的产业。

发展现状简介集成电路具有多种特点,如其体积小、质量轻、功能齐全、可靠性高、安装方便、频率特性好、专用性强以及元器件的性能参数比较一致,对称性好。

目前最先进的集成电路是微处理器或多核处理器的“核心”,可以控制电脑、手机到数字微波炉的一切。

【完整版】集成电路塑封自动上料机机架部件设计及性能试验_毕业论文设计

摘要本课题结合纵向科研项目“集成电路塑封自动上料机研制”研究需要,首先进行了课题总体技术方案设计,然后进行了集成电路芯片塑料封装自动上料系统的机架部件结构设计及性能试验方案的拟定。

自动上料系统的研制实现了集成电路塑封的自动化,该系统适用于DIP、QFP、SOP、TO等系列集成电路芯片的塑封生产,可显著提高生产效率及产品质量。

自动上料系统主要由料片传送部件、料片自动排片部件、工控机系统、传感检测系统及上料机机架部件等组成。

上料机机架部件采用钣金结构制造,结构简单且使用方便。

上料机机架部件作为上料机一个重要的基础结构部件,起到支撑工作台、安装和保护电子设备内部各种电路单元、电气元器件等重要元件的作用。

关键词:集成电路,塑封,上料,自动化,机架部件ABSTRACTBased on the longitudinal research topic “IC Plastic automatic feeding machine” research needs, firstly the issue of the overall technical program was designed, then the IC chip plastic packages automatic feeding system on the rack components was designed and the performance was tested. An automatic leader system was designed that realized automation for plastic package of integrated circuit. The system can be applied to the plastic package for DIP、QFP、SOP and TO series integrated circuits. The production efficiency and the product quality would be improved greatly. The system consists mainly of transmission components, materials unit automatic film parts, industrial computer systems, sensing detection system and the rack components and so on. The rack components of the automatic feeding machine was made by Sheet-metal structure, the structure is simple and easy to use. The rack components as an important infrastructure components of the feeding machine, it play a role in supporting workstations, installation and protection of electronic equipment within various circuit modules, electrical components and other important components.Key words: Integrated circuit, Plastic package, Load, Automation, Rack components目录摘要 (I)ABSTRACT (II)第一章绪论 (1)1.1课题研究的现状及发展趋势 (1)1.2课题研究的基本内容 (2)1.3课题研究的意义和价值 (2)第二章集成电路封装概述 (4)2.1 集成电路 (4)2.1.1 概念 (4)2.1.2 类型 (4)2.1.3 集成电路在我国的发展状况 (5)2.2 集成电路封装 (5)2.2.1 封装的发展 (5)2.2.2 塑料封装 (7)2.2.3 环境因素对封装的影响 (7)2.3 封装设备 (9)2.3.1 集成电路芯片塑料封装设备 (9)2.3.2 国内外集成电路塑封设备的概况 (10)2.4 机电一体化系统(产品)的设计 (10)第三章上料机系统设计 (12)3.1 系统总体设计 (12)3.1.1集成电路塑封上料的技术要求及其指标 (12)3.1.2系统组成及工作过程 (12)3.1.3系统特点 (14)3.2上料机机架部件结构设计 (14)3.2.1机架部件设计准则 (14)3.2.2机架部件结构设计 (15)3.3性能试验方案拟定 (17)第四章结论与展望 (20)参考文献 (21)致谢 (22)第一章绪论1.1课题研究的现状及发展趋势集成电路(IC)是现代信息产业和信息社会的基础,是改造和提升我国传统产业的核心技术。

集成电路专业公开发过的论文摘要参考

集成电路专业公开发过的论文摘要参考集成电路专业是电子工程的一个重要分支,在现代电子技术发展中发挥着至关重要的作用。

以下是一些公开发过的集成电路专业论文的摘要,希望能够给读者提供一些参考和启示。

论文一:基于图像处理技术的集成电路缺陷检测该论文旨在通过图像处理技术,实现对集成电路制造过程中可能存在的缺陷进行高效、精准的检测。

其中,研究人员首先对待检测的集成电路样品进行图像采集和预处理,之后通过图像分割、形态学处理等方法,得到集成电路的纹理特征和周边信息;接着,研究人员结合机器学习算法,对图像特征进行训练,并建立了一套自适应的缺陷检测模型,该模型可以根据不同物理特性的缺陷进行分类检测。

最终,实验结果表明,该方法可以高效地检测出所有缺陷,并具有较高的准确率和鲁棒性。

论文二:集成电路中时钟树设计优化该论文针对时钟树在集成电路设计中的重要性,研究了一种基于最短路径算法的时钟树设计方法,并将其在FPGA芯片的设计中进行了验证。

研究人员首先通过全局路径搜索,得到了传输时钟所需的最短路径,然后利用具有流动性的O(1)时钟基准树来构建大型时钟树,并利用所提出的动态调度算法实现了布图。

最后,以Xilinx Virtex-6系列FPGA芯片为例验证了该方法的有效性和性能。

结果表明,该时钟树设计方法能够提高系统时钟频率,减少功耗,并且实现的时钟延迟在一个可接受的范围内。

论文三:基于ICM方法的真实时间温度补偿电路设计该论文通过Intelligent Compensation Method (ICM)算法,提出了一种适应环境温度变化的实时温度补偿电路设计方法,该方法较好地解决了温度变化对集成电路的影响。

该方法的设计流程具有非常高的仿真准确率和强鲁棒性,通过对多组不同情况下的温度测试数据进行仿真分析,可以得出该方法的设计误差率和热滞后现象均比传统方法更低。

最终,实验结果表明,该设计方法可以有效地提高真实时间系统的可靠性和鲁棒性。

超大规模集成电路论文

课程论文(超大规模集成电路设计)题目基于CPLD的曼彻斯特编解码器设计专业学生姓名学号得分基于CPLD的曼彻斯特编解码器设计引言虽然计算机通信的方法和手段多种多样,但都必须依靠数据通信技术。

数据通信就是将数据信号加到数据传输信道上进行传输,并在接收点将原始发送的数据正确地恢复过来。

由于计算机产生的一般都是数字信号,因此计算机之间的通信实际上都属于数据通信。

曼彻斯特码编解码器是1553B总线接口中不可缺少的重要组成部分,曼彻斯特码编解码器设计的好坏直接影响总线接口的性能,在数控测井系统和无线监控等领域,曼彻斯特码编解码器都有广泛应用。

1 数据通信系统结构图1所示是数据通信系统的基本构成。

在计算机通信中,通信双方传递的信息必须进行量化并以某种形式进行编码后才能进行传输。

机内信号不论采用哪一种编码方法,它们的基本信号都是脉冲信号,为了减少信号在传输媒质上的通信带宽限制,以及噪音、衰减、时延等影响,也由于同步技术的需要,操作时都需要对简单的脉冲信号进行一些不同的变换,以适合传输的需要。

这样就会产生许多不同的代码,通常有不归零电平(NRZ-L)码,逢“1”反转(NRZ-1)码,曼彻斯特码和差分曼彻斯特等。

图2所示是部分编码方式的波形图。

由图2可知,不归零码的制码原理是用负电平表示“0”,正电平表示“1”,其缺点是难以分辨一位的结束和另一位的开始;发送方和接收方必须有时钟同步;若信号中“0”或“1”连续出现,信号直流分量将累加,这样就容易产生传播错误。

曼彻斯特码(Manchester)的原理是每一位中间都有一个跳变,从低跳到高表示“0”,从高跳到低表示“1”。

这种编码方式克服了NRZ码的不足。

每位中间的跳变即可作为数据,又可作为时钟,因而能够自同步。

曼彻斯特编码特点是每传输一位数据都对应一次跳变,因而利于同步信号的提取,而且直流分量恒定不变。

缺点是数据编码后,脉冲频率为数据传输速度的2倍。

差分曼彻斯特码(Differential Manchester)的原理是每一位中间都有一个跳变,每位开始时有跳变表示“0”,无跳变表示“1”。

半导体集成电路可靠性测试及数据处理

寿命分布的参数估计是基本的可靠性数据处理方法,我们回顾并讨论了可靠

性寿命分布参数估计的各种常用方法。最佳线性无偏估计以次序统计量理论以及 高斯-马尔可夫定理为出发点,是一种高精度且有效的可靠性寿命分布参数估计 方法。然而,它只能应用于样本总数比较小的场合并且不能应用于I型截尾数据。

极大似然估计法是另一种具有良好性质的参数估计方法。我们通过对各种参数估

However,BLUE is applicable at small sample sizes and cannot be applied on type I censored datasets.The maximum likelihood estimation(MLE)is another parameter estimation method with several good properties.The perfect correlation between MLE and BLUE in our study makes it possible to use MLE instead of BLUE for reliability parameter estimations.

半导体集成电路的哥靠性测试及数据处理还有很多工作需要进行。希望我们 的研究对于国内半导体集成电路产业以及半导体集成电路可靠性工作的发展有 一定的帮助。

关键词:晶圆级可靠性,加速寿命试验,威卸尔分布,极大似然估计 中图分类号:TBll4.3

半导体集成电路可靠性测试发数据处理

II

Abstmct

Abstract

半导体集成电路口J靠件测试发数据处理

一————————————————————.——! ! ——————————————————————————————.———一 ———__—————————————●___———————————————————_——__●-_———_—————————————一

模拟集成电路论文

我国未来集成电路发展模式思考张媛媛1230440115(湖南工学院电气与新新工程学院衡阳 421002)【摘要】目前,正处于集成电路产业的发展、投资规模、产业结构、技术水平都发生巨大变革阶段,我国集成电路产业的发展面临更加严峻的,挑战。

推动这一产业的发展关系到国家信息安全和国家主权。

因而需要关注以下几点:集成电路产业的发展趋势;我国集成电路的发展状况;我国集成电路面临的机遇与展望。

【abstract】Nowadays,we are in the development of IC industry ,the scale of investment,industrial structure,technological level of great change,of china’s IC industry face more severe challenge.How to deal with the new pattern of development of the industry .we must pay more attention the following points:the development trend of integrated circuit industry;development of china’s intrgrated circuit;the opportunities and prospect of china’s integrated circuit.【关键词】集成,挑战,发展【Keywords】Integrated Circuit;challenge ;development1、引言目前,以集成电路为核心的电子信息产业产业超过了以汽车、石油、钢铁为代表的传统工业成为第一大产业、成为改造和拉动传统产业迈向数字时代的将达引擎和雄厚的基石。

2、集成电路产业的发展趋势集成电路发展的总趋势是革新工艺、提高集成度和速度。

集成电路封装工艺(毕业学术论文设计)

集成电路封装工艺(毕业学术论文设计)本文旨在介绍集成电路封装工艺的重要性和研究背景,以及阐述本论文的目的和结构安排。

集成电路是现代电子技术中的关键组成部分,其封装工艺对于保护集成电路的完整性和性能至关重要。

随着集成电路的不断发展,封装工艺的研究和优化变得越发重要。

本论文旨在研究集成电路封装工艺的相关技术和方法,以提高封装工艺的效率和可靠性。

本论文的结构安排如下:引言:介绍集成电路封装工艺的重要性和研究背景,说明本论文的目的和结构安排。

相关工艺:介绍集成电路封装工艺的基本概念和技术,包括封装材料、封装方法等。

封装工艺优化:探讨封装工艺中存在的问题和挑战,并提出相应的优化策略和方法。

实验与结果:介绍针对集成电路封装工艺的实验设计和实验结果分析,验证优化策略的有效性。

结论:总结论文的主要研究内容、取得的成果以及未来可能的研究方向。

希望通过本论文的研究,能够对集成电路封装工艺的优化和发展提供有益的参考和指导。

本文详细介绍集成电路封装工艺的定义、组成和基本流程,包括设计、布局、封装材料选择、封装技术等内容。

集成电路封装工艺是将裸露的集成电路芯片封装在一个外部封装材料中,以提供保护和连接功能的一种技术。

它是集成电路制造过程中不可或缺的一环。

封装工艺的组成部分包括设计、布局、封装材料选择和封装技术。

设计集成电路封装工艺的设计阶段涉及到确定芯片封装的物理特性和封装类型。

封装设计需要考虑到芯片的尺寸、引脚数量、电气性能、散热需求等因素。

布局封装布局是将芯片和周围器件的引脚连接起来的过程。

在布局阶段,需要精确安排引脚的位置和间距,以确保信号传输效果和封装可靠性。

封装材料选择在选择封装材料时,需要考虑到材料的导热性能、机械强度、耐化学性等因素。

常用的封装材料包括塑料、陶瓷和金属等。

封装技术封装技术涉及到将芯片与封装材料进行物理连接的过程。

常见的封装技术包括焊接、黏贴、球栅阵列(BGA)等。

集成电路封装工艺的基本流程包括设计、布局、材料选择和封装技术。

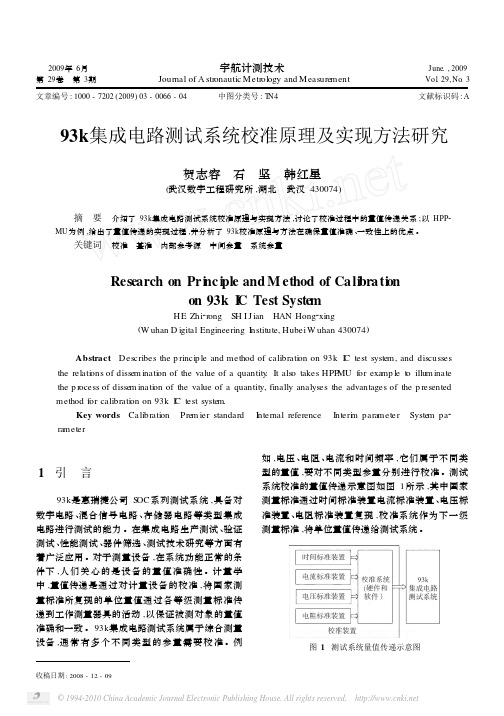

93k集成电路测试系统校准原理及实现方法研究

作者简介 :贺志容 ( 1980—) ,女 ,工程 师 ,主要研究领域:微电子计量与 测试 。 通讯地址 :武汉市洪山区珞瑜路 718 号 (430074) 电话 : 027 - 87533046 E2mail: hzr_hust@163. com

[ 1 ] 贺志容 ,沈森祖 ,韩宏星 ,等. 93000集成电路测试系统 检定方法研究 [ C ]. 2007计量与测试学术交流会论文 集 , 2007: 187~189.

[ 2 ] Verigy coporation, N IST Traceable Calibration, Verigy V93000 Service Guide.

完整的溯源校准的新型集成电路测试系统 [ 3 ] 。 在系统的长期运行过程中 ,由于测试系统内部

组成元器件性能的微小变化 ,温度 、湿度等外部因 素的影响 ,系统的量值会产生漂移 ,若不对这种漂 移做出修正 ,漂移的累积会严重降低系统精度 。校 准过程中如果不能对量值进行更新修正 ,系统精度 会逐步降低 。内部参考源校准时首先对内部参考 源进行校准 ,并自动更新系统基准量 ,使其误差趋 于零 ,消除了各种因素对基准量值造成的影响 ; 自 动校准的过程利用已经校准合格的基准量对系统 中间量直至系统参量进行校准 ,并产生修正值 ,在 测试过程中引用 ,消除了各种因素对系统参量造成 的影响 ,使测量结果的产生都能依据最新校准的修 正模式 ,保证了测试系统的精度 。

图 6 参考电压校准示意图

图 7 参考电阻校准示意图

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

集成电路的发展 论文【范本模板】

论文题目:集成电路的发展学院: 班级:姓名:学号:集成电路的发展摘要集成电路不仅在工、民用电子设备如收录机、电视机、计算机等方面得到广泛的应用,同时在军事、通讯、遥控等方面也得到广泛的应用。

用集成电路来装配电子设备,其装配密度比晶体管可提高几十倍至几千倍,设备的稳定工作时间也可大大提高。

在当今这信息化的社会中,集成电路已成为各行各业实现信息化、智能化的基础。

无论是在军事还是民用上,它已起着不可替代的作用。

本文试论由集成电路的发展史到未来发展趋势。

关键词:集成电路发展史未来发展趋势晶体管MOS1、集成电路概述所谓集成电路(IC),就是在一块极小的硅单晶片上,利用半导体工艺制作上许多晶体二极管、三极管及电阻、电容等元件,并连接成完成特定电子技术功能的电子电路.从外观上看,它已成为一个不可分割的完整器件,集成电路在体积、重量、耗电、寿命、可靠性及电性能方面远远优于晶体管元件组成的电路,目前为止已广泛应用于电子设备、仪器仪表及电视机、录像机等电子设备中。

2、集成电路发展史1) 发现和研究半导体效应1833-第一次记录了半导体效应1874-发现半导体点接触整流效应1901—场效应半导体器件概念申请专利1931-出版《半导体电子理论》1940-p-n结的发现1947年12月16日-“触点式”晶体管的发明1948—结型晶体管的诞生1952—贝尔实验室授权晶体管技术2)“集成电路”的发明1958—杰克·基尔比(Jack Kilby)展示了“固态电路"1959-平面工艺的发明导致了单片集成电路的发明3)金属氧化物半导体(MOS)和互补型金属氧化物半导体(CMOS)的发明1960-制成首个金属氧化半导体(MOS)绝缘栅场效应晶体管1963—发明互补型MOS电路结构4)集成电路工业进入发展期1963—开发标准逻辑集成电路系列1964—混合微型电路达产量高峰1964-第一块商用MOS集成电路诞生1964-第一个广泛应用的模拟集成电路诞生1965-适合于系统集成的封装设计1965-只读型存储是第一个专用存储IC存储1966-为高速存储开发的半导体RSMs1968-集成了数据转换功能的电流源集成电路1968—为集成电路开发的硅栅技术1969—肖特基势垒二极管让TTL存储器的速度加倍1970—MOS动态随机存取存储器(DRAM)与磁芯存储器价格相近1971—微处理器将CPU功能浓缩进单个芯片1974-数字显示式手表是第一块片上系统(SoC)集成电路1978-(可程序化行列逻辑)用户可编程逻辑器件诞生1979-单片数字信号处理器诞生3、集成电路未来发展趋势及新技术3。

模拟电路之集成电路论文

集成运放集成电路是一种将“管”和“路”紧密结合的器件,它以半导体单晶硅为芯片,采用专门的制造工艺,把晶体管、场效应管、二极管电阻和电容等元件及他们之间的连线所组成的完整电路制作在一起,是指具有特定的功能。

集成放大电路最初多用于各种模拟信号的运算(如比例、求和、求差、积分、微分……)上,故被称为运算放大电路,简称集成运放。

集成运放广泛用于模拟信号的处理和产生电路之中,因其高性能低价位,在大多数情况下,已经取代了分立元件放大电路。

从本质上看,集成运放是一种高性能的直接耦合放大电路。

并且它种类繁多。

按供电方式可将运放分为双模供电和单模供电,在双模供电中又分正、负电源对成型和不对称型供电。

按照集成运算放大器的参数可分为通用性和特殊型两类,通用型运放用于无特殊要求的电路中,其性能指标的数值范围如表1所示,少数运放可能超出表中数值范围。

特殊性运放可分通用型运算放大器、高阻型运算放大器、低温漂型运算放大器、高速型运算放大器、低功耗型运算放大器、高压大功率型运算放大器。

表1。

通用型运算放大器就是以通用为目的而设计的。

这类器件的主要特点是价格低廉、产品量大面广,其性能指标能适合于一般性使用。

例mA741(单运放)、LM358(双运放)、LM324(四运放)及以场效应管为输入级的LF356都属于此种。

它们是目前应用最为广泛的集成运算放大器。

这类集成运算放大器的特点是差模输入阻抗非常高,输入偏置电流非常小,一般rid>(109~1012)W,IIB为几皮安到几十皮安。

实现这些指标的主要措施是利用场效应管高输入阻抗的特点,用场效应管组成运算放大器的差分输入级。

用FET作输入级,不仅输入阻抗高,输入偏置电流低,而且具有高速、宽带和低噪声等优点,但输入失调电压较大。

常见的集成器件有LF356、LF355、LF347(四运放)及更高输入阻抗的CA3130、CA3140等。

在精密仪器、弱信号检测等自动控制仪表中,总是希望运算放大器的失调电压要小且不随温度的变化而变化。

《集成电路技术与发展综述》课程论文

集成电路技术的现状与发展趋势摘要:1958年美国德克萨斯仪器公司发明全球第一块集成电路后,随着硅平面技术的发展,20世纪60年代先后发明双极型和MOS型两种重要电路,创造了一个前所未有的具有极强渗透力和旺盛生命力的新兴产业——集成电路产业。

关键词:集成电路,晶体管,发展状况集成电路现在已经是工业界,商业界所必不可少的‘家伙’了,最具盛名的就是苹果公司的产品,包括iMac,iPhone,iPad,等等,其产品的精髓就在于其内置的高水平集成电路技术,如果你要说是他们的设计出众的话,我就要插一句了,如果没有高端的技术,任你的设计再怎么好看,你能再那么好看的产品上实现众多智能化的功能吗?而Macbook Air就是领先业界好几年的产品,同样的设计几乎所有公司能请设计师搞出来,为什么苹果就能在同时做出产品来?所以体积小,集成度高的电路板技术的设计与制造,现今已成为所有智能化产业所必不可少的核心技术。

自打2005年谷歌收购Android和2007年iPhone和iOS问世,移动设备智能化到达了一个井喷的时代,至今,移动设备芯片已经能与当年的电脑相当,如高通的snapdragon 800系列,苹果的A7处理器,还有国产的MTK,以及显卡巨头Tegra,设备的制造技术已经达到22nm 级的工艺水平,而原有的PC和笔记本处理器在Intel和AMD两大公司的发展下也都到达了惊人的高水平阶段,尤其是Intel的E系列,民用的i系列,几乎是现在旗舰电脑的标配。

而正是这些高性能集成芯片的高速发展,与之匹配大规模集成电路技术也在节节提升,出现了现在超级本,iPad Air等小巧精致但性能优越的产品。

我国的集成电路技术经过30年的发展,我国已初步形成了设计、芯片制造和封测三业并举、较为协调的发展格局,产业链基本形成。

2001年我国设计业、芯片制造业、封测业的销售额分别为11亿元、27.2亿元、161.1亿元,分别占全年总销售额的5.6%、13.6%、80.8%,产业结构不尽合理。

集成电路芯片封装测

2 0 0 8 级毕业生毕业设计(论文)设计课题:集成电路芯片封装测试的工艺流程专业∶班级∶姓名∶指导老师∶前言本次毕业设计的课题是集成电路芯片封装测试的工艺流程。

在集成电路芯片的制造过程中,由于温度、噪音、空气中的微粒、人为的操作失误及机器设备的误差,致使外表看上去很完美的芯片内部有可能出现开短路的情况,严重影响芯片的质量,因此,在集成电路芯片封装测试中,电性能测试就是为了检查芯片是否存在上述现象。

本次设计是将芯片放入机器里,根据事先存好的芯片测试程序,在特定的高温环境下对芯片进行相应的测试,看测试出来的数据是否符合芯片的标准。

在整个测试流程中,电性能测试是相当重要的,所有的芯片在推向市场以前必须经过电性能测试。

摘要本次设计包括第一章集成电路设计概述,主要陈述了集成电路(IC)的发展,当前国际集成电路技术发展趋势,我国微电子技术的发展现状;集成电路制造材料概述,其中包括半导体材料、绝缘体材料、金属材料、材料系统等等;集成电路制造工艺流程,外延生长,掩膜的制版工艺,光刻,刻蚀,掺杂,绝缘层的形成,金属层的形成;第二章是集成电路芯片封装,包括以下内容,集成电路芯片封装概述、集成电路芯片封装历程、封装定义及其功能、封装的分类、封装的发展趋势。

第三章是FCBGA的工艺流程,硅片回流(water reflow),粘膜,硅片切割,载体转换,焊剂铺垫,焊膏铺垫,芯片粘贴,回流,助焊剂清除。

第四章是FCBGA的测试工艺流程,半成品仓库(Raw Store),老化板装载/卸载(Board Load/Unload),老化测试(Burn In),电性能测试(Electrical Test),激光印码(Laser Mark),脱水烘烤(Desiccant Bake),焊球粘贴(Ballattach)包装(Pack),最终目测检验(Final Visual Insection)。

第五章是CMT 站点简介,包括以下内容:CMT全称,CMT前后站点简介,CMT站点的四种测试,CMT站点所用到的化学品,C MT站点所用到的几种系统,CMT站点的产品的两条主路径,CMT站点一般安全行为,CMT站点所需要用到的命令,什么叫STD?什么情况下需要运行STD?第六章是电性能测试的过程。

集成电路工程毕业论文题目

集成电路工程毕业论文题目一、论文说明本团队专注于原创毕业论文写作与辅导服务,擅长案例分析、编程仿真、图表绘制、理论分析等,论文写作300起,所有定制的文档均享受免费论文修改服务,具体价格信息同时也提供对应的论文答辩辅导。

二、论文参考题目集成电路工程硕士毕业论文集成电路企业税收筹划研究TFT-LCD周边集成驱动电路的设计QVGA AM-OLED像素电路及集成一体化周边驱动电路的研究与设计中国集成电路产业发展战略AM-OLED像素及集成一体化周边驱动电路的研究与设计混合集成电路测试硬件电路测试板的设计混合信号集成电路自动测试设备的研究与实现数字集成电路自动测试硬件技术研究多通道高精度集成电路直流参数测试模拟集成电路自动化设计方法的研究中国集成电路产业发展战略研究集成电路芯片级热分析方法研究脉象识别神经网络集成电路研究模拟集成电路设计方法学及模拟IP设计技术的研究中小规模集成电路的自动化集成方法研究及应用集成电路生产车间的安全风险控制硅磁敏三极管开关集成电路设计上海集成电路企业创新网络研究基于TSV的三维集成电路分割算法的研究集成电路测试仪总体软件与人机界面设计集成电路布图设计的知识产权保护我国半导体集成电路企业创新生态系统耦合机制研究大功率模拟集成电路直流参数测试研究与实现上海市集成电路行业协会的知识产权管理厚膜集成电路的计算机辅助检验我国集成电路产业发展的现状分析与对策研究集成电路布图设计法律保护研究试论我国集成电路布图设计的特殊保护数字集成电路测试仪通信接口的研究与设计集成电路行业物质流分析若干问题研究定制集成电路设计流程研究集成电路测试系统微小微电子参量校准技术研究基片集成非辐射介质波导(SINRD)与平面电路的混合集成研究中国集成电路对外贸易问题的思考集成电路测试系统后逻辑支持电路改进与模拟延迟线性能分析数字集成电路测试系统软件设计集成电路布图设计权法律保护研究数字专用集成电路检测技术的研究及信号发生器的设计功率集成电路中电机驱动电路和数控功率放大器的研究与设计上海集成电路产业发展政策研究射频与微波集成电路参数提取的积分方程方法及应用研究集成电路布图设计的法律保护集成电路测试生成算法与可测性设计的研究功率集成电路中的闩锁效应研究模拟集成电路布局方法研究数字集成电路测试仪软件设计集成电路自动测试方法及可测性设计研究集成电路设计的项目管理应用研究存储测试专用集成电路成测技术研究混合集成电路测试系统上位机软件设计中国集成电路布图设计专有权撤销制度研究中小规模集成电路测试方法的分析与仿真实现混合集成电路自动测试系统研究与设计功率集成电路中高压器件的设计深圳集成电路产业发展战略研究集成电路布图设计独创性的认定中日集成电路产业竞争力的比较研究模拟集成电路测试系统及网络设计集成电路自动测试设备接口板网表生成方法研究集成电路布图设计权及其保护研究集成电路布图设计的国际保护与我国的立法探析数字集成电路低功耗优化设计研究3D集成电路TSV自动布局研究福建省集成电路产业发展研究论集成电路布图设计权的保护与限制基于小波变换的故障电路特征值提取的研究集成电路布图设计复制侵权认定标准研究集成电路布图设计的知识产权保护从中外法律比较看我国集成电路知识产权的法律保护我国集成电路分销商新市场开发策略研究高速集成电路测试板仿真与设计一种大规模集成电路测试方法塑封集成电路可靠性评价技术研究集成电路测试仪的总线接口与驱动程序设计图形化编程在集成电路测试软件平台中的研究与应用音频功率集成电路及功率器件研究模拟集成电路优化方法研究集成电路设计行业项目管理研究我国集成电路产业技术创新能力评价研究集成电路布图设计侵权问题研究集成电路多故障测试生成算法及可测性设计的研究苏州工业园区集成电路产业战略研究上海张江高科技园区集成电路地方产业网络研究用于微热板式气压传感器的数字集成电路设计基于VIIS-EM平台的虚拟数字集成电路测试仪的研制TRIPS协定下我国集成电路布图设计权利保护的法律分析集成电路测试仪通信驱动与中间层软件设计面向环境、安全和健康(ESH)的集成电路产业园区规划布局研究上海地区集成电路设计产业的困境及出路探讨集成电路知识产权法律制度研究国际法视野下的集成电路布图设计知识产权保护面向集成电路封装的有限角度下X-Ray图像重建微热板气体传感器阵列的单片集成电路设计植入式神经信号处理专用集成电路设计研究数字集成电路测试生成算法研究一种厚膜混合集成DC/DC开关电源电路研制用于模拟集成电路测试的浮地恒流恒压源的研究论集成电路布图设计专有权的保护集成电路HPM损伤的计算机模拟上海集成电路创新集群形成的充分条件和必要条件研究低功耗CMOS集成电路设计方法的研究MEMS电容式传感器接口集成电路研究集成电路的老化预测与ESD防护研究基于单测点的模拟集成电路测试系统设计基于全球价值链理论的我国集成电路产业升级路径研究集成电路电磁干扰测量方法的研究射频集成电路中平面螺旋电感的研究基于SOI的高压开关集成电路设计中国集成电路布图设计权限制的法经济学分析数字集成电路故障模型研究及故障注入平台设计FTFN在模拟集成电路中的应用研究超深亚微米集成电路制造过程中光学邻近效应模拟的研究三维集成电路测试时间的优化方法研究大功率模拟集成电路直流参数测试单片开关电源管理集成电路设计低电压低功耗FTFN及其在模拟集成电路设计中的应用研究面向集成电路封装检测的X射线图像滤波与增强方法研究基于粒子群算法的数字集成电路测试生成研究集成电路制造中Contact Process造成SRAM失效分析与解决SH2000集成电路测试系统PCI驱动及上位机软件的研制基于知识的集成电路光刻工艺设计系统研究中国大陆集成电路产业的国际竞争力研究FDT对我国集成电路产业市场结构的影响研究集成电路设计企业技术能力综合评价研究倍流整流电路中集成磁件的应用研究射频集成电路电磁参数提取集成电路布图设计法律保护研究集成电路制造过程中光刻系统仿真的多边形处理算法研究中国集成电路产业国际竞争力研究混合集成电路测试板FPGA逻辑设计海尼克斯集成电路企业发展战略研究面向AMOLED应用的氧化锌基TFT集成电路研究集成电路布图设计的知识产权保护霍尔集成电路设计及其测试系统的研发碳纳米管在纳米集成电路互连线中的应用研究CMOS射频集成电路中无源器件频变参数提取的研究集成电路等价性验证系统设计及其实现集成电路布图设计的知识产权保护军用集成电路老炼筛选技术研究应用于射频集成电路的新型交变结构平面螺旋电感研究集成电路测试仪控制模块及驱动设计SOI高压器件及功率开关集成电路的研究基于DEA-Malmquist方法的我国集成电路产业全要素生产率研究CMOS模拟集成电路中放大器和比较器的SET分析上海市集成电路创新集群构成要素研究集成电路布图设计专有权撤销程序的探讨集成电路制造企业新衬底导入项目风险管理集成电路可测性设计的研究与实践MOS模拟集成电路交互式自动化Sizing符号化方法探索研究和软件实现集成电路测试仪控制电路与分选系统接口技术研究。

《数字系统测试与可测试性设计基础》结课论文

《数字系统测试与可测性设计基础》结课论文题目:基于测试向量重组的VLSI低功耗测试算法基于测试向量重组的VLSI低功耗测试算法摘要:随着集成电路集成度和时钟频率的大幅度提高,测试功耗和测试时间急剧增加,这便成为集成电路测试中亟待解决的问题。

本文在课本所学知识的基础上,对当前流行的几种集成电路测试算法进行了简要介绍,并着重探讨了基于测试向量重组的低功耗测试算法。

关键字:低功耗测试;汉明间距;重组算法Abstract:With the rapid development of integrated circuits and increased clock frequency, the power consume and test time become an urgent problem to solve. Based on the knowledge that learned in class, this article introduces a few algorithms briefly, and talks about the low-power test algorithm based on test vectors reordering in detail.Key words:low test power;Hamming Distance;reordering algorithm1.引言近些年来,随着电路集成度和制造工艺的进步,与之相关的集成电路测试复杂度和测试功耗也越来越高。

集成电路的测试功耗不仅会使系统可靠性降低,成品率下降,还会减少电路寿命。

与此同时,集成电路的测试功耗会直接反映在其热损耗上,而且需要昂贵的冷却技术和负载与之匹配,从而极大地增加了电路的成本。

所以,在集成电路可测试性设计中,考虑如何降低测试功耗是当前新的研究热点和研究领域。

集成电路测试,就是生成一组被称为测试向量的二进制向量,将其输入到电路系统中,观察由此产生的输出响应,并与预期的正确结果进行比较,一致就表示系统正常,不一致则表示系统有故障。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

集成电路测试与可靠性设计结课论文基于FPGA的图像处理开发板设计姓名:***班级:B09212学号:***********模拟集成电路设计与应用摘要近年来,随着集成电路工艺技术的进步,整个电子系统可以集成在一个芯片上。

这些变化改变了模拟电路在电子系统中的作用,并且影响着模拟集成电路的发展。

随着信息技术及其产业的迅速发展,当今社会进入到了一个崭新的信息化时代。

微电子技术是信息技术的核心技术,模拟集成电路又是微电子技术的核心技术之一,因而模拟集成电路成为信息时代的重要技术领域。

已广泛应用于信号放大、频率变换、模拟运算、计算机接口、自动控制、卫星通信等领域。

关键词:模拟集成电路;微电子技术;信号放大;频率变换引言集成电路是一种微型电子器件或部件。

采用一定的工艺,把一个电路中所需的晶体管、二极管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构。

集成电路具有体积小,重量轻,引出线和焊接点少,寿命长,可靠性高,性能好等优点,同时成本低,便于大规模生产。

它不仅在工、民用电子设备如收录机、电视机、计算机等方面得到广泛的应用,同时在军事、通讯、遥控等方面也得到广泛的应用。

集成电路按其功能、结构的不同,可以分为模拟集成电路、数字集成电路和数/模混合集成电路三大类。

模拟集成电路又称线性电路,用来产生、放大和处理各种模拟信号(指幅度随时间边疆变化的信号。

例如半导体收音机的音频信号、录放机的磁带信号等),其输入信号和输出信号成比例关系。

下面就我所学的和了解到的知识简单的介绍一下模拟集成电路555定时器的设计与应用。

内容一、模拟集成电路555定时器555 定时器是一种模拟和数字功能相结合的中规模集成器件。

一般用双极性工艺制作的称为 555,用 CMOS 工艺制作的称为 7555,是美国Signetics公司1972年研制的用于取代机械式定时器的中规模集成电路,因输入端设计有三个5k Ω的电阻而得名。

此电路后来竟风靡世界。

555 定时器成本低,性能可靠,只需要外接几个电阻、电容,就可以实现多谐振荡器、单稳态触发器及施密特触发器等脉冲产生与变换电路。

它也常作为定时器广泛应用于仪器仪表、家用电器、电子测量及自动控制等方面。

555时基电路是一种将模拟功能与逻辑功能巧妙地结合在同一硅片上的组合集成电路。

二、集成电路555定时电路的组成555集成定时器由五个部分组成:(1)由三个阻值为5kΩ的电阻组成的分压器;(2)两个电压比较器C1和C2:v+>v-,vo=1;v+<v-,vo=0。

(3)基本RS触发器;(4)放电三极管T及缓冲器G图1 555 定时器的内部单元组成框图和外引脚排列图它的各个引脚功能如下:1脚:GND(或Vss)外接电源负端VSS或接地,一般情况下接地。

8脚:VCC(或VDD)外接电源VCC ,双极型时基电路VCC 的范围是4.5~16V ,CMOS 型时基电路VCC 的范围为3~18V 。

一般用5V 。

3脚:OUT (或Vo )输出端。

2脚:TR 低触发端。

6脚:TH 高触发端。

4脚:R 是直接清零端。

当R 端接低电平,则时基电路不工作,此时不论TR 、TH 处于何电平,时基电路输出为“0”,该端不用时应接高电平。

5脚:CO(或VC)为控制电压端。

若此端外接电压,则可改变内部两个比较器的基准电压,当该端不用时,应将该端串入一只0.01μF 电容接地,以防引入干扰。

7脚:D 放电端。

该端与放电管集电极相连,用做定时器时电容的放电。

电阻分压器由三个5k Ω的等值电阻串联而成。

电阻分压器为比较器C1、C2提供参考电压,比较器C1的参考电压为2/3Vcc ,加在同相输入端,比较器C2的参考电压为1/3Vcc ,加在反相输入端。

比较器由两个结构相同的集成运放C1、C2组成。

高电平触发信号加在C1的反相输入端,与同相输入端的参考电压比较后,其结果作为基本RS 触发器R 端的输入信号;低电平触发信号加在C2的同相输入端,与反相输入端的参考电压比较后,其结果作为基本RS 触发器S 端的输入信号。

基本RS 触发器的输出状态受比较器C1、C2的输出端控制。

三、集成电路555定时电路的工作原理由555 定时器的内部电路图可知,它的功能主要由两个比较器决定当5脚悬空时,比较器C1和C2的比较电压分别为cc V 32和cc V 31(1)当vI1>cc V 32,vI2>cc V 31时,比较器 C1输出低电平,C2输出高电平,基本RS 触发器被置0,放电三极管T 导通,输出端vO 为低电平。

(2)当vI1<cc V 32,vI2<cc V 31时,比较器 C1输出高电平,C2输出低电平,基本RS 触发器被置1,放电三极管T 截止,输出端vO 为高电平。

(3)当vI1<cc V 32,vI2>cc V 31时,比较器 C1输出高电平,C2也输出高电平,即基本RS 触发器R=1,S=1,触发器状态不变,电路亦保持原状态不变。

由于阈值输入端(vI1) 为高电平(>cc V 32)时,定时器输出低电平,因此也将该端称为高触发端(TH )。

因为触发输入端(vI2)为低电平(<cc V 31)时,定时器输出高电平,因此也将该端称为低触发端(TL )。

如果在电压控制端(5脚)施加一个外加电压(其值在0~VCC 之间),比较器的参考电压将发生变化,电路相应的阈值、触发电平也将随之变化,并进而影响电路的工作状态。

另外,RD 为复位输入端,当RD 为低电平时,不管其他输入端的状态如何,输出vo 为低电平,即RD 的控制级别最高。

正常工作时,一般应将其接高电平。

其功能如下表1所示:四、555时基电路的设计与应用由555时基电路构成常见的最基本的典型应用电路有:单稳态触发电路、双稳态触发电路、无稳态电路,而用这3种方式中的1种或多种组合起来可以组成各种实用的电子电路,如定时器、分频器、脉冲信号发生器、元件参数和电路检测电路、玩具游戏机电路、音响告警电路、电源交换电路、频率变换电路、自动控制电路等。

下面就简单的介绍三种由555时基电路构成的应用。

1、单稳态电路单稳态触发器只有一个稳态状态。

在未加触发信号之前,触发器处于稳定状态,经触发后,触发器由稳定状态翻转为暂稳状态,暂稳状态保持一段时间后,又会自动翻转回原来的稳定状态。

单稳态触发器一般用于延时和脉冲整形电路。

单稳态触发器电路的构成形式很多。

图2(a)所示为用555定时器构成的单稳态触发器,R、C为外接元件,触发脉冲u1由2端输入。

5端不用时一般通过0.01uF电容接地,以防干扰。

下面对照图2(b)进行分析。

a b图2 单稳态触发器(1) 稳态接通电源后,经R给电容C充电,当uc上升到大于时,基本RS触发器复位,输出u0=0。

同时,晶体管T导通,使电容C放电。

此后uc<,若不加触发信号,即u1>,则u保持0状态。

电路将一直处于这一稳定状态。

(2) 暂稳态在t=t1瞬间,2端输入一个负脉冲,即u1<,基本RS触发器置1,输出为高电平,并使晶体管T截止,电路进入暂稳态。

此后,电源又经R向C充电,充电时间常数=RC,电容的电压按指数规律上升。

在t=t2时刻,触发负脉冲消失(u1>),若uc<,则=1,=1,基本RS触发器保持原状态,u仍为高电平。

在t=t3时刻,当uc上升略高于时,=0,=1,基本RS触发器复位,输出u=0,回到初始稳态。

同时,晶体管T导通,电容C通过T迅速放电直至uc为0。

这时=1,=1,电路为下次翻转做好了准备。

输出脉冲宽度tp为暂稳态的持续时间,即电容C的电压从0充至所需的时间。

由=(1-)得由上式可知:①改变R、C的值,可改变输出脉冲宽度,从而可以用于定时控制。

②在R、C的值一定时,输出脉冲的幅度和宽度是一定的,利用这一特性可对边沿不陡、幅度不齐的波形进行整形。

2、多谐振荡器——产生矩形脉冲波的自激振荡器在数字电路中,常常需要一种不需外加触发脉冲就能够产生具有一定频率和幅度的矩形波的电路。

由于矩形波中除基波外,还含有丰富的高次谐波成分,因此我们称这种电路为多谐振荡器。

它常常用作脉冲信号源。

多谐振荡器没有稳态,只具有两个暂稳态,在自身因素的作用下,电路就在两个暂稳态之间来回转换。

它的电路组成及其工作原理:如图3所示 为555定时器构成的多谐振荡器,接通VCC 后,VCC 经R1和R2对C 充电。

当uc 上升到2VCC/3时,uo=0,T 导通,C 通过R2和T 放电,uc 下降。

当uc 下降到VCC/3时,uo 又由0变为1,T 截止,VCC 又经R1和R2对C 充电。

如此重复上述过程,在输出端uo 产生了连续的矩形脉冲。

振荡频率的估算和占空比可调电路电容C 充电时间:C R R t w )(7.0211+= 电容C 放电时间:C R t w 227.0=电路谐撼振频率f 的估算:振荡周期为:C R R T )2(7.021+=振荡频率为:C R R R R T f )2(43.1)2(7.0112121+≈+== 占空比D :2121212112)2(7.0)(7.0R R R R R R C R R T t D w ++=++==3、模拟声响发生器图4是由两个多谐振荡器构成的模拟声响发生器。

左侧振荡器Ⅰ的振荡频率较低(整定元件为RA1、RB1、C1)比如2Hz ;右侧的振荡器Ⅱ的振荡频率较高(整定元件为RA2、RB2、C2)比如为1kHz 。

由于低频振荡器Ⅰ的输出端3接到高频振荡器Ⅱ的复位端4,故当振荡器Ⅰ的输出电压uo1为高电平时,振荡器Ⅱ就振荡;当uo1为低电平时,振荡器Ⅱ停止振荡,从而使扬声器便发出间歇声响。

总结这次论文的完成不仅是对所学过的基础理论和专业知识进行一次全面、系统地回顾和总结,而且也是对自己能力的一种提高。

在本次论文中,我遇到了很多的困难,通过查阅大量有关资料和自学,但更多的是得到王玉峰老师的帮助和指导才得以顺利解决。

并使我明白了原来自己的知识还比较欠缺,不够全面。

学习是一个长期积累的过程,我应在以后的工作、生活中都应该不断的学习,努力提高自己知识和综合素质。

由于自己水平有限,论文中难免有疏漏不足之处、还望老师指点、修正并提出宝贵意见,使本论文更加完善。

在此表示衷心的感谢。

参考文献:[1]陆秀令,韩清涛.模拟电子技术.北京:北京大学出版社,2008 [2]谢自美.电子线路设计•实验▪测试(第三版).武汉:华中科技大学出版社,2006[3]吴运昌.模拟集成电路原理与应用.广州:华南理工大学出版社,1995[4]姚福安.电子电路设计与实践.山东:山东科学技术出版社,2001[5]百度百科.555定时器: /view/1102178.htm.。