第四章_集成电路导线

数字集成电路-互连线

pF/cm

数字集成电路 Digital Integrated Circuit

互连线

互连线的电容效应

线间电容

连线的水平尺寸与垂直尺寸不按相同比例缩小,连线间距D 减小,线厚度H基本维持不变,导致线间寄生电容增大。

Level 2

Level 1

数字集成电路 Digital Integrated Circuit

Intel 45 nm Stack

[Moon08]

互连线

互连线模型

考虑各种寄生参数的模型

数字集成电路 Digital Integrated Circuit

电容模型

互连线

互连线特征

连线数目(对数幅度) Source: Intel

Local Interconnect SLocal = STechnology

Cwire C p p C fringe

W

H/ tdi

2 di

2 di

log2tdi / H

1

互连线

互连线的电容效应

互连线电容与W/H的关系

电介质为SiO2, r=3.9 电 容 (

)

• W/H 较大时,总

电容接近平行板 电容模型

• W/H 较小时 (W/H <1.5),边

缘电容占总电容 的主要部分

数字集成电路 Digital Integrated Circuit

互连线

互连线的电容效应

平行板电容模型(W >> tox)

C int

ox WL

tox

L

H tox

按比例缩小:

W

电力线 W、tox1/S

L 1/SL

SiO2 substrate

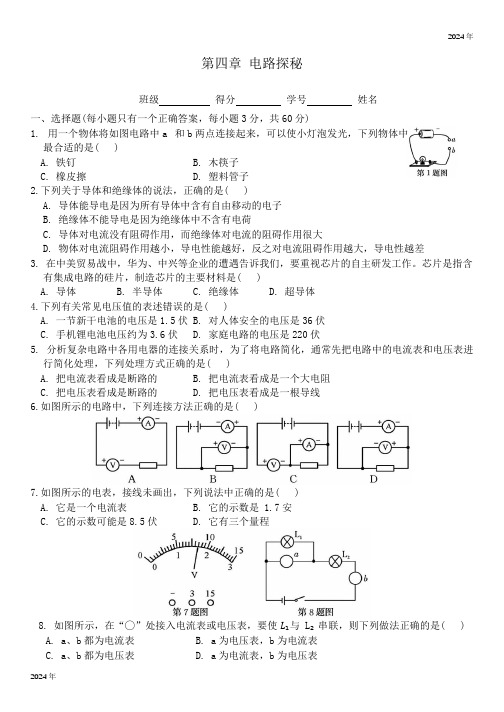

初中九年级(初三)物理 第四章认识电路

图4.1-2第四章 认识电路 第1节 电路 自主学习知识要点 1.电路的组成(1)最简单的电路由四部分组成。

分别是: 、 、 、 。

(2)从能的转化的角度看:电源是 能量的、用电器是 能量的、导线是是传输能量的、开关是 能量传输的。

2.电路的三种状态 (1)通路:接通的电路。

(2)开路:断开的电路。

开路又叫 路。

(3)短路:使导线不通过用电器直接跟 两极连接。

3.电路图(1)使用 画出的电路叫做电路图。

(2)画出下列元件的电路符号:电灯 、干电池 、开关 、电铃 、电动机 。

(3)画电路图时的要求:使用统一规定的 ;连线要横平竖直;拐角处不能画元件。

(4)在右边画出图4.1-1中所示实物电路的电路图。

图4.1-1 特别提醒1.生活中所说的开灯是指闭合开关,电路处于通路状态;关灯是指断开开关,电路处于开路状态。

2.开路有两种情况:一是正常开路,控制电路的开关断开。

二是电路故障造成。

此时虽然开关闭合,但由于电路中其它元件接触不良或损坏,造成电路中没有电流。

所以判断电路状态时要从用电器、开关及电流三方面来考虑。

3.短路有两种情况:一是电源短路。

指整个电路短路,无法工作。

此时电路中的电流很大,会烧坏电源和导线,重则会引发火灾,所以电源短路是决不允许的。

二是局部短路。

电路中部分元件短路,该元件不能工作,其它电路元件还可以工作。

互动课堂例1如图4.1—2所示的电路图中,正确的是( )【思路点拨】一个正确的电路应该满足以下要求:1.完整。

即四个部分都有。

2.无短路现象。

3.开关能起控制作用。

根据这些要求逐一对比分析即可作出判断。

【规律总结】电路常见的错误有:①电路不完整;②部分用电器未接入电路;③开关不能正常控制电路;④电路中出现电源被短路或局部短路。

变式训练1如图图4.1-3所示电路图中正确的是( )变式训练2如图4.1-4所示的电路中,要使小灯泡正常发光,a 、b 两处可连入的元件是( )A. a 、b 两处都接开关B. a 、b 两处都接导线C. a 处接电源,b 处接开关D. a 处接电源,b 处接导线例2 在右边的虚线框中画出图图4.1-5中所示实物电路的电路图。

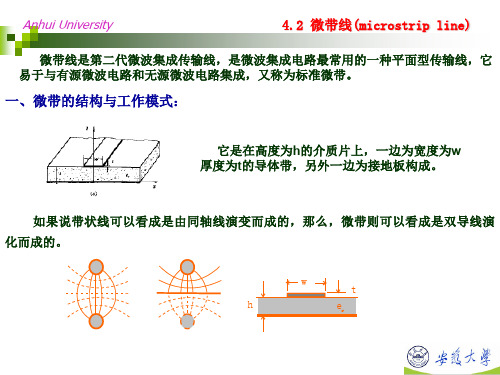

第9次 第四章 微波集成传输线 微带线 耦合传输线

Anhui University

2.奇模激励 (odd-mode excitation):

由大小相等、方向相反的电流对耦合线两带状导体产生的激励,奇模激励 时中间对称面为电壁。

奇模激励的场结构

单根带状导体对地的分布电容为奇模电容

等效电容网络

Co C11 2C12 C22 2C12

Anhui University

求解Z 0a , e

采用保角变换法可精确求解零厚度导体带空气微带线的特性阻抗:

Z 0a 60

k为模数,K‘、K分别为第一类全椭圆积分和第一类余全椭圆积分,它们均是超越函数, 不便于应用,才有数值方法作曲线拟合可得如下近似公式:

Anhui University

零厚度导体带特性阻抗和有效介电常数 P115(4.2-7)

60 2 其中:B Z0 r

应用以上设计公式可得到特性阻抗、有效介电常数与宽高比之间的关系曲线; 也可得到微带线特性阻抗数据表。

Anhui University

三、微带线衰减常数

导体损耗 c :截面较小,导体损耗大

介质损耗 ----热损耗 :介质分子交替极化和晶格来回碰撞 d

辐射损耗:由半开放性所引起,截面小则不均匀点较大,故微 带线常放在金属屏蔽盒中—可避免辐射损耗 无辐射损耗时

微带线最大特点就是易于系统化和集成化,可以成批量生产:

微带线工艺过程如下:

基片

打孔

蒸发

光刻

腐蚀

电镀

由于实际微带线具有介质分界面,因此不可能存在纯TEM波,致使微带分析更加困 难和复杂,本节采用准静态法分析微带的准TEM波特性及其一些实用简化结果。

Anhui University

二、微带线中准TEM波特性

数字电路第4章(6竞争与冒险现象)_2综述

A

A A'

A A' L

L

★ 分析:2—4译

码器中的竞争冒险现象

★ 当AB从10->01

时,动态过程 中出现00和11 状态,在Y3和 Y0输出端可能 产生冒险。

*2、检查竞争与冒险现象的方法(1)

一、代数法: (1) 检查是否存在某个变量A,它同时以原变量和 反变量的形式出现在函数表达式中。

★编码器、译码器、数据选择器、数据分配 器、数值比较器和加法器是常用的MSI组合逻 辑部件,学习时重点掌握其逻辑功能及应用。

★数据选择器的作用是根据地址码的要求,从 多路输入信号中选择其中一路输出。 ★数据分配器的作用是根据地址码的要求,将 一路数据分配到指定输出通道上去。

★编码器的作用是将具有特定含义的信息编成 相应二进制代码输出;常用的有二进制编码

关的电路。它在逻辑功能上的特点是:没有存储

和记忆作用;在电路结构上的特点是:由各种门 电路组成,不含记忆单元,只存在从输入到输出

的通路,没有反馈回路。

组合逻辑电路的基本分析方法是:根据给定电 路逐级写出输出函数式,并进行必要的化简和 变换,然后列出真值表,确定电路的逻辑功能。 组合逻辑电路的基本设计方法是:根据给定设 计任务进行逻辑抽象,列出真值表,然后写出输 出函数式并进行适当化简和变换,求出最简表达 式,从而画出最简(或称最佳)逻辑电路。

再加选通脉冲选取输出结果, 即可消除现象。

该方法简单易行,但对选通信号的作用时间和 脉冲宽度有严格的要求。

3、消除竞争与冒险现象的方法

(3) 修改逻辑设计 采用增加冗余项的方法。 在表达式中“加”上多余的“与项”或者“乘” 上多余的“或项”,使原函数不可能在某种条件 下再出现A+A‘和AA’的形式。

(整理)集成电路原理学习指南-第二版

沟道等效电阻

(1)与W/L反比,

(2)与电压有关,

(3)VDD大的时候较小(饱和工作区)

(4)VDD接近Vt的时候急剧增大

(5)一般使用工作区平均电阻

掌握

3.18

电阻的近似

平均电阻,并估算其误差(保守估计还是过估计)

掌握

3.19

结构电容

栅电容,覆盖电容

掌握

3.20

沟道电容

在不同工作区域的变化和原因,在阈值附近最小

f=Cext/Cint=Cext/γCg,尺寸决定电容,所以也是扇出尺寸,为工艺决定的系数,代表自电容与栅电容的关系

掌握

5.13

反相器链的最优尺寸设计

每一级为前后级的几何平均

扇出系数公式(5.35),公式(5.36)

掌握

5.14

最佳等效扇出

图5.21(pp 152),一般取4

掌握

5.15

上升下降时间对延时的影响

了解

3.26

电容估算

(1)栅电容,扩散电容大致相当(定义单位NMOS和PMOS的栅电容为C)

(2)它们随沟道宽度等比增加(kC)

(3)最小晶体管C值可初略估计为1fF/um宽度(65nm工艺,宽0.1um晶体管的C值约为0.1fF)

[Weste,4.3.2]

掌握

第四章导线

序号

概念

知识点和关键词

掌握程度

掌握

3.13

MOS IV特性

画出IV图,标出工作区,图3.24(pp 74)

掌握并会定性画图

3.14

手工分析的局限

在电阻区和过度区之间的区域偏差较大

了解

3.15

设计测试点验证IV

知道晶体管几个端口的电压,固定哪个,量哪个电流,可以提取以上列出的某个参数。

数字集成电路的特点与分类

CMOS 传输门

39

A 和 A 控制传输门的通断: A=+UDD A=0V时,传输门接通 A=0V A=+UDD时,传输门断开

左下图 uI 由0V变为UDD时,CL充电 右下图 uI 由UDD变为0V时,CL放电

40

41

UNH=UOH(min)- UIH(min)

=2.4-2.0V=0.4V

UOH

UIH

P106

躁声容限 门电路之间相互连接时,前一级24 门的输出就是后一级门的输入,在前一级输 出为最坏的情况下(输出低电位为UOL(max)), 后一级门的输入电压允许的变化幅度叫做噪 声容限。

UNL=UIL(max)- UOL (max)

6

同一个电路,按两种不同的约定去分析, 会得出不同的结论。

在今后讨论电路时,必须明确采用哪种约定。 一般采用正逻辑约定。

uo

高电位 低电位

正 逻 辑 约 定

0

1 1

0

负 逻 辑 约 定

7

4.2 晶体管-晶体管逻辑电路(TTL电路)

4.2.1 最简单的与门、非门和与非门电路 1. 二极管与门

10

由真值表可知,上面电路是一个非门

电路的输入与输出电位

输入A 0.2V 5V

输出F 5V 0.2V

电路的真值表

输入A 0 1

输出F 1 0

门

3 晶

体

管

与

非

11

+

12

4.2.1 TTL与非门电路

输入

输A 入

与 0.2V

输 0.2V

出 电

5V

位 5V

B 0.2V 5V 0.2V 5V

输出 F 5V 5V 5V

集成电路的基本原理和工作原理

集成电路的基本原理和工作原理集成电路是指通过将多个电子元件(如晶体管、电容器、电阻器等)和互连结构(如金属导线、逻辑门等)集成到单个芯片上,形成一个完整的电路系统。

它是现代电子技术的重要组成部分,广泛应用于计算机、通信、嵌入式系统和各种电子设备中。

本文将介绍集成电路的基本原理和工作原理。

一、集成电路的基本原理集成电路的基本原理是将多个电子元件集成到单个芯片上,并通过金属导线将这些元件互连起来,形成一个完整的电路系统。

通过集成电路的制造工艺,可以将电子元件和互连结构制造到芯片的表面上,从而实现芯片的压缩和轻量化。

常见的集成电路包括数字集成电路(Digital Integrated Circuit,简称DIC)、模拟集成电路(Analog Integrated Circuit,简称AIC)和混合集成电路(Mixed Integrated Circuit,简称MIC)等。

集成电路的基本原理包括以下几个关键要素:1. 材料选择:集成电路芯片的制造材料通常选择硅材料,因为硅材料具有良好的电子特性和热特性,并且易于形成晶体结构。

2. 晶圆制备:集成电路芯片的制造过程通常从硅晶圆开始。

首先,将硅材料熔化,然后通过拉伸和旋转等方法制备成硅晶圆。

3. 掩膜制备:将硅晶圆表面涂覆上光感光阻,并通过光刻机在光感光阻表面形成图案。

然后使用化学溶液将未曝光的部分去除,得到掩膜图案。

4. 传输掩膜:将掩膜图案转移到硅晶圆上,通过掩膜上沉积或蚀刻等方法,在硅晶圆表面形成金属或电子元件。

5. 互连结构制备:通过金属导线、硅氧化物和金属隔离层等材料,形成元件之间的互连结构,实现元件之间的电连接。

6. 封装测试:将芯片放置在封装材料中,通过引脚等结构与外部电路连接,然后进行测试和封装。

集成电路的基本原理通过以上几个关键步骤实现电子元件和互连结构的制备和组装,最终形成一个完整的电路系统。

二、集成电路的工作原理集成电路的工作原理是指通过控制电流和电压在电路系统中的分布和变化,从而实现电子元件的工作和电路系统的功能。

chap4-6

第四章数字集成电路的基本单元电路-动态CMOS电路动态逻辑电路的特点静态电路:靠管子稳定的导通、截止来保持输出状态动态电路:靠电容来保存信息V DDV V V outΦDD AMMP2P1A BC LB Y =A .B M MN2V out动态电路的优点AN1B:相对NMOS 电路:动态电路可降低功耗,无比电路电路:用动态电路简化电路提高速度相对CMOS 电路:用动态电路简化电路,提高速度—预充求值动态CMOS 电路的构成Φ=0,预充;Φ=1,求值V DDV ΦV outA C LoutA M1B存在的问题:Φ=0,A =B =1,V V 解决了预充过程OH 小于DD下拉支路导通问题outV outΦΦ富NMOS 动态电路Φ=0,预充;Φ=1,求值富PMOS 动态电路Φ=1,预充;Φ=0,求值下降时间影响速度上升时间影响速度YCBNΦY AB C=+Y AB C=+富NMOS 电路实现富PMOS 电路实现—预充求值电路中的电荷分享问题M1V V out (0) =V (0) =0V DD ()1()M1C B1Φf L DD L V V C V C C V C )(1+=出现电荷分享的条件:时LDDL DD L f C C C C V /111+=+=Φ=0时,A =0;Φ=1时,A =1;B 始终为0。

电荷分享过程中的节点电平变化M1V outΦ极端情况:C L =C 1, 则V f =V DD /2一般情况:般情况:C L >C 11C V V V V =−−()outDD DD TN LCMOS 管电容的耦合作用对电荷分享的影响V DDV outC C GDC V A AALC C GSV 1AC LC C GS GD V 1V out 11—预充求值电路的级连举例A=B=1,C=0M P1V outΦCV1M N1V2不能用富富NMOS注意:NMOS与富NMOS(或富PMOS与富PMOS)电路直接级连。

清华大学《数字集成电路设计》周润德 第4章 互连线

V = V inc (1 + ρ )

I = I inc (1 − ρ )

2004-9-22

清华大学微电子所《 数字大规模集成电路》 周润德

第 4 章 第 27 页

源电阻 > 特征阻抗 源电阻 < 特征阻抗

无损传输线的瞬态响应

源电阻 = 特征阻抗

2004-9-22

源电阻 < 特征阻抗 有限的上升斜率

清华大学微电子所《 数字大规模集成电路》 周润德

第 4 章 第 23 页

考虑连线RC延时的准则

• 当连线的 RC 延时与驱动门的延时相比较大,即:

(tpRC >> tpgate )时需要考虑连线的 RC 延时。

需要考虑RC延时的连线临界长度为:

Lcrit >> √ tpgate/0.38 rc

• 当连线输入端信号的上升或下降时间小于连线的上升或下

一般制造商会提供每层的面电容和周边电容。 实际设计时,可以查表或查图。

考虑性能时,电容的计算:

1。要用制造后的实际尺寸, 2。考虑延迟或动态功耗时, 一般用 最坏情况

(最大宽度W ,最薄介质) 3。考虑竞争情况时用最小宽度W 及最厚介质。

2004-9-22

清华大学微电子所《 数字大规模集成电路》 周润德

1.75

导线层

Poly

Al1

Al2

Al3

Al4

Al5

电容

40

95

85

85

85

115

2004-9-22

清华大学微电子所《 数字大规模集成电路》 周润德

第 4 章 第 11 页

导线电容 (0.25 µm CMOS)

集成电路的工作原理

集成电路的工作原理集成电路是微电子技术的重要应用领域之一,它的工作原理主要依靠半导体材料的特性和微电子器件的结构。

本文将详细介绍集成电路的工作原理。

集成电路是一种将多个电子器件集成在单个芯片上的电路。

它的基本构成包括晶体管、电阻和电容等元器件,通过这些元器件的组合与互连,实现各种电路功能。

集成电路的工作原理可以分为几个方面来讨论。

首先,集成电路的工作原理与半导体材料的特性密不可分。

半导体材料是集成电路的基础材料,其电子特性有别于金属和绝缘体。

半导体材料的原子结构中含有杂质,通过这些杂质的掺入可以使半导体材料形成P型和N型两种类型。

当P型和N型半导体连接构成PN结时,形成了二极管,这是集成电路中最基本的器件之一。

其次,集成电路的工作原理与晶体管的工作原理密切相关。

晶体管是一种控制电流流动的电子器件,它由发射极、基极和集电极组成,通过控制基极电流来控制集电极电流的大小。

在集成电路中,晶体管起到放大和开关的作用,通过多个晶体管的互连组合,可以构成不同类型的逻辑电路。

此外,集成电路的工作原理还与电容和电阻等器件的特性有关。

电容器是一种可以存储电荷的器件,而电阻器是一种限制电流流动的器件。

集成电路通过使用电容器和电阻器来实现电路的滤波、去干扰和保护等功能。

最后,集成电路的工作原理还依赖于金属导线和氧化物层等互连技术。

在集成电路中,各个元器件之间需要使用金属导线来连接,而氧化物层则起到了隔离和保护的作用。

通过不同层次的金属导线和氧化物层的设计,可以实现复杂电路的互连和布线。

综上所述,集成电路的工作原理涉及了半导体材料的特性、晶体管的工作原理、电容和电阻的特性以及互连技术等多个方面。

它将多个电子器件集成在单个芯片上,实现了电路功能的高度集成和微型化。

集成电路的工作原理不仅是微电子学的基础知识,也是当代电子技术发展的重要依托。

在集成电路的工作原理中,还有一些重要的概念和技术需要考虑。

首先,集成电路的工作原理与逻辑门有关。

数字集成电路设计笔记归纳

数字集成电路设计笔记归纳第三章、器件⼀、超深亚微⽶⼯艺条件下MOS 管主要⼆阶效应:1、速度饱和效应:主要出现在短沟道NMOS 管,PMOS 速度饱和效应不显著。

主要原因是TH GS V V -太⼤。

在沟道电场强度不⾼时载流⼦速度正⽐于电场强度(µξν=),即载流⼦迁移率是常数。

但在电场强度很⾼时载流⼦的速度将由于散射效应⽽趋于饱和,不再随电场强度的增加⽽线性增加。

此时近似表达式为:µξυ=(c ξξ<),c s a t µξυυ==(c ξξ≥),出现饱和速度时的漏源电压DSAT V 是⼀个常数。

线性区的电流公式不变,但⼀旦达到DSAT V ,电流即可饱和,此时DS I与GS V 成线性关系(不再是低压时的平⽅关系)。

2、Latch-up 效应:由于单阱⼯艺的NPNP 结构,可能会出现VDD 到VSS 的短路⼤电流。

正反馈机制:PNP 微正向导通,射集电流反馈⼊NPN 的基极,电流放⼤后⼜反馈到PNP 的基极,再次放⼤加剧导通。

克服的⽅法:1、减少阱/衬底的寄⽣电阻,从⽽减少馈⼊基极的电流,于是削弱了正反馈。

2、保护环。

3、短沟道效应:在沟道较长时,沟道耗尽区主要来⾃MOS 场效应,⽽当沟道较短时,漏衬结(反偏)、源衬结的耗尽区将不可忽略,即栅下的⼀部分区域已被耗尽,只需要⼀个较⼩的阈值电压就⾜以引起强反型。

所以短沟时VT 随L 的减⼩⽽减⼩。

此外,提⾼漏源电压可以得到类似的效应,短沟时VT随VDS增加⽽减⼩,因为这增加了反偏漏衬结耗尽区的宽度。

这⼀效应被称为漏端感应源端势垒降低。

4、漏端感应源端势垒降低(DIBL):VDS增加会使源端势垒下降,沟道长度缩短会使源端势垒下降。

VDS很⼤时反偏漏衬结击穿,漏源穿通,将不受栅压控制。

5、亚阈值效应(弱反型导通):当电压低于阈值电压时MOS管已部分导通。

不存在导电沟道时源(n+)体(p)漏(n+)三端实际上形成了⼀个寄⽣的双极性晶体管。

集成电路的工作原理

集成电路的工作原理集成电路(Integrated Circuit,简称IC)是由多个电子元件(如晶体管、电阻、电容等)和互连网络组成的微小芯片,通过将这些元件和互连网络集成在一个单一的硅基片上,实现了电子电路的功能。

集成电路具有体积小、功耗低、可靠性高的特点,广泛应用于电子设备中。

集成电路的原理是基于半导体材料的特性。

半导体材料的电导率介于导体和绝缘体之间,通过控制半导体材料的电荷状态可以控制电流的流动。

集成电路中的晶体管是其中最重要的元件之一。

晶体管由三层半导体材料P型和N型半导体构成。

P型半导体带正电的离子,N型半导体带负电的离子,它们的接口处形成PN结。

PN结的特性是在正向偏置时,电流容易通过;在反向偏置时,电流难以通过。

集成电路中,可以通过控制PN结的偏置、施加电压或电流的方式,利用晶体管的三种工作状态来实现电路的功能操作。

这三种工作状态分别是截止状态、放大状态和饱和状态。

截止状态下,PN结反向偏置,电流无法通过晶体管。

放大状态下,PN结正向偏置,电流可以通过晶体管。

饱和状态下,PN结正向偏置,电流大量通过晶体管。

集成电路中的互连网络用于连接晶体管之间以及其他电子元件之间,实现电路的功能运算或信号传输。

互连网络通常由导线、电阻和电容等元件构成。

在集成电路的制造过程中,先在硅片上制作晶体管,再利用光刻技术将电路图案形成在硅片表面。

最后,通过多层金属层的刻蚀和镀铜等工艺来形成互连网络。

通过集成电路的工作原理,我们可以实现各种各样的电子电路,包括计算机、手机、电视机等。

集成电路的技术不断发展,使得电子设备变得更加高效和便携。

总之,集成电路通过将多个电子元件和互连网络集成在一个微小的芯片中,利用晶体管的工作原理实现电路功能。

它是现代电子设备中不可或缺的核心技术之一。

数字集成电路设计第四章习题

1. 如下图所示时钟数, 根据下表中提供的电容电阻数据, 计算从节点A到节点B的Elmore 延时。

图计算延时的RC树

表Values of the components in the RC tree

Resistor Value( ) Capacitor Value(fF)

R1 0.25 C1 250

R2 0.25 C2 750

R3 0.50 C3 250

R4 100 C4 250

R5 0.25 C5 1000

R6 1.00 C6 250

R7 0.75 C7 500

R8 1000 C8 250

3等分并插入2个传播延时为100ps的反相器,计算在这种情况下各层上整个导线的传播延时。

3.设计一个时钟分布网络,在各个时钟之间的最小偏差是很关键的问题,从一个时钟网络中抽象出如下图所示的RC网络,最初CLK3比CLK1和CLK2的路径更短,为了补偿这一不平衡,在CLK3的路径中插入一个传输门。

1)写出节点CLK3、CLK1和CLK2的时间常数,假设传输门用R3模拟;

2)如果R1=R2=R4=R5=R,C1=C2=C3=C4=C5=C,R3为多大时可以平衡;

3)当R=750Ω,C=200fF,传输门有多大的W/L比可以消除偏差;。

电路知识点总结pdf

电路知识点总结pdf第一章电路基础知识1.1 电路的定义电路是指由电源、导线、电器元件(例如电阻、电容、电感等)等组成的通电路径。

在电路中,电流经过电器元件后可以被改变,不同的电路结构和元件组合可以实现不同的电学功能。

1.2 电路的基本元件电路中的基本元件包括电源、导线、电阻、电容和电感等。

电源用于提供电流,导线用于连接各个元件,电阻用于限制电流,电容用于存储电荷,电感用于储存电能。

1.3 电路的基本定律欧姆定律、基尔霍夫定律和法拉第定律是电路中的三大基本定律。

欧姆定律描述了电压、电流和电阻之间的关系,基尔霍夫定律描述了电路中的电流和电压的分布规律,法拉第定律描述了电感和电流之间的关系。

1.4 电路的分类根据电路中的元件和连接方式,电路可以分为直流电路和交流电路,串联电路和并联电路等不同类型。

第二章电阻电路2.1 电阻的基本性质电阻是电路中用于限制电流的元件,具有一定的电阻值。

电阻的电阻值与电阻本身的材料、长度和截面积等有关。

2.2 串联电阻和并联电阻串联电阻指多个电阻按照一定方向依次连接在一起,相同电流依次通过各个电阻,串联电阻的总电阻等于各个电阻的电阻之和。

并联电阻指多个电阻同时连接在一点上,电流依次分流通过各个电阻,并联电阻的总电阻等于各个电阻电阻值的倒数之和的倒数。

2.3 电阻的功率和能量利用电阻的电压和电流可以计算出电阻消耗的功率,电阻会将电能转换成热能,电阻的功率和电能的关系可以用来计算电阻的热效应。

2.4 电桥电桥是一种利用电阻比值测量未知电阻值的方法,常见的电桥有维恩桥和韦斯通桥等。

第三章电容电路3.1 电容的基本性质电容是电路中用于存储电荷和电能的元件,具有一定的电容值。

电容的电容值与电容本身的材料、形状和尺寸等有关。

3.2 并联电容和串联电容并联电容指多个电容同时连接在一点上,电荷依次分流通过各个电容,而串联电容指多个电容按照一定方向依次连接在一起,相同电压依次加在各个电容上。

浙教版科学八年级上册 第4章 电路探秘(4.2-4.5) 单元测试卷(含答案)

第四章电路探秘班级得分学号姓名一、选择题(每小题只有一个正确答案,每小题3分,共60分)1. 用一个物体将如图电路中a 和b两点连接起来,可以使小灯泡发光,下列物体中最合适的是( )A. 铁钉B. 木筷子C. 橡皮擦D. 塑料管子2.下列关于导体和绝缘体的说法,正确的是( )A. 导体能导电是因为所有导体中含有自由移动的电子B. 绝缘体不能导电是因为绝缘体中不含有电荷C. 导体对电流没有阻碍作用,而绝缘体对电流的阻碍作用很大D. 物体对电流阻碍作用越小,导电性能越好,反之对电流阻碍作用越大,导电性越差3. 在中美贸易战中,华为、中兴等企业的遭遇告诉我们,要重视芯片的自主研发工作。

芯片是指含有集成电路的硅片,制造芯片的主要材料是( )A. 导体B. 半导体C. 绝缘体D. 超导体4.下列有关常见电压值的表述错误的是( )A. 一节新干电池的电压是1.5伏B. 对人体安全的电压是36伏C. 手机锂电池电压约为3.6伏D. 家庭电路的电压是220伏5. 分析复杂电路中各用电器的连接关系时,为了将电路简化,通常先把电路中的电流表和电压表进行简化处理,下列处理方式正确的是( )A. 把电流表看成是断路的B. 把电流表看成是一个大电阻C. 把电压表看成是断路的D. 把电压表看成是一根导线6.如图所示的电路中,下列连接方法正确的是( )7.如图所示的电表,接线未画出,下列说法中正确的是( )A. 它是一个电流表B. 它的示数是 1.7安C. 它的示数可能是8.5伏D. 它有三个量程8. 如图所示,在“◯”处接入电流表或电压表,要使L₁与 L₂串联,则下列做法正确的是( )A. a、b都为电流表B. a为电压表,b为电流表C. a、b都为电压表D. a为电流表,b为电压表9. 某技术监督部门对市场上的电线产品进行抽查,发现有一个品牌的铜芯电线不符合规格:电线直径明显比说明书上标有的直径要小。

这种电线不符合规格的主要原因是( )A. 电线的温度引起电阻偏大B. 电线的材料引起电阻偏大C. 电线的长度引起电阻偏大D. 电线的横截面积引起电阻偏大10. 在如图所示的电路中,用滑动变阻器调节灯的亮度,若要求滑片 P 向右端滑动时灯逐渐变亮,则下列接法正确的是( )A. M接A,N接DB. M接C,N接DC. M接C,N接BD. M接A,N接B11. 如图所示的电路,开关S闭合后,两灯均发光,下列说法中正确的是( )A. 两灯并联B. 电压表测的是灯 L₁两端的电压C. 电压表测的是灯 L₂两端的电压D. 开关断开时,电流表无示数但电压表有示数12. 在如图所示的电路中,闭合开关S后,灯L不发光。

数字集成电路——电路、系统与设计

数字集成电路——电路、系统与设计目录第一部分基本单元第1章引论1.1 历史回顾1.2 数字集成电路设计中的问题1.3 数字设计的质量评价1.4 小结1.5 进一步探讨第2章制造工艺2.1 引言2.2 CMOS集成电路的制造2.3 设计规则——设计者和工艺工程师之间的桥梁2.4 集成电路封装2.5 综述:工艺技术的发展趋势2.6 小结2.7 进一步探讨设计方法插入说明A——IC版图第3章器件3.1 引言3.2 二极管3.3 MOS(FET)晶体管3.4 关于工艺偏差3.5 综述:工艺尺寸缩小3.6 小结3.7 进一步探讨设计方法插入说明B——电路模拟第4章导线4.1 引言4.2 简介4.3 互连参数——电容、电阻和电感4.4 导线模型4.5 导线的SPICE模型4.6 小结4.7 进一步探讨第二部分电路设计第5章CMOS反相器5.1 引言5.2 静态CMOS反相器——直观综述5.3 CMOS反相器稳定性的评估——静态特性5.4 CMOS反相器的性能——动态特性5.5 功耗、能量和能量延时5.6 综述:工艺尺寸缩小及其对反相器衡量指标的影响5.7 小结本文由整理提供5.8 进一步探讨第6章CMOS组合逻辑门的设计6.1 引言6.2 静态CMOS设计6.3 动态CMOS设计6.4 设计综述6.5 小结6.6 进一步探讨设计方法插入说明C——如何模拟复杂的逻辑电路设计方法插入说明D——复合门的版图技术第7章时序逻辑电路设计7.1 引言7.2 静态锁存器和寄存器7.3 动态锁存器和寄存器7.4 其他寄存器类型7.5 流水线:优化时序电路的一种方法7.6 非双稳时序电路7.7 综述:时钟策略的选择7.8 小结7.9 进一步探讨第三部分系统设计第8章数字IC的实现策略8.1 引言8.2 从定制到半定制以及结构化阵列的设计方法8.3 定制电路设计8.4 以单元为基础的设计方法8.5 以阵列为基础的实现方法8.6 综述:未来的实现平台8.7 小结8.8 进一步探讨设计方法插入说明E——逻辑单元和时序单元的特性描述设计方法插入说明F——设计综合第9章互连问题9.1 引言9.2 电容寄生效应9.3 电阻寄生效应9.4 电感寄生效应9.5 高级互连技术9.6 综述:片上网络9.7 小结9.8 进一步探讨第10章数字电路中的时序问题10.1 引言10.2 数字系统的时序分类本文由整理提供10.3 同步设计——一个深入的考察10.4 自定时电路设计10.5 同步器和判断器10.6 采用锁相环进行时钟综合和同步10.7 综述:未来方向和展望10.8 小结10.9 进一步探讨设计方法插入说明G——设计验证第11章设计运算功能块11.1 引言11.2 数字处理器结构中的数据通路11.3 加法器11.4 乘法器11.5 移位器11.6 其他运算器11.7 数据通路结构中对功耗和速度的综合考虑11.8 综述:设计中的综合考虑11.9 小结11.10进一步探讨第12章存储器和阵列结构设计12.1 引言12.2 存储器内核12.3 存储器外围电路12.4 存储器的可靠性及成品率12.5 存储器中的功耗12.6 存储器设计的实例研究12.7 综述:半导体存储器的发展趋势与进展12.8 小结12.9 进一步探讨设计方法插入说明H——制造电路的验证和测试本文由整理提供。

集成电路课件ppt

总结词

集成电路的发展历程经历了从小规模集成电路到大规模集成电路再到超大规模集成电路的演变。随着技术的不断发展,集成电路的集成度越来越高,功能越来越强大。

要点一

要点二

详细描述

集成电路的发展历程是一个不断创新和演进的过程。最早的集成电路是小规模集成电路,只能实现简单的电路功能。随着技术的不断发展,集成电路的集成度越来越高,功能越来越强大。从20世纪60年代开始,大规模集成电路的出现使得电子设备变得更加小型化、轻便化。进入20世纪80年代后,超大规模集成电路的发展进一步推动了电子设备的微型化和智能化。如今,随着半导体制造工艺的不断进步,集成电路的集成度越来越高,性能越来越强大,为各种电子设备的发展提供了强大的支持。

全球集成电路产业竞争格局日益激烈,企业兼并重组加速,产业集中度不断提高。

中国集成电路产业面临技术瓶颈、人才短缺、产业链不完善等挑战,需要加强自主研发和创新能力。

中国政府出台了一系列政策措施,支持集成电路产业发展,推动产业升级和转型。

中国集成电路产业发展迅速,市场规模不断扩大,技术水平不断提高。

01

导出与交付

根据集成电路的规格和性能要求,选择合适的封装形式,如DIP、SOP、QFP等。

封装形式

测试设备

测试程序

测试报告

使用专业测试设备对集成电路进行功能测试、性能测试和可靠性验证。

编写测试程序,模拟集成电路的实际工作场景,进行全面测试。

根据测试结果生成测试报告,记录集成电路的性能指标和可靠性数据。

加强集成电路教育资源建设,包括教材建设、师资队伍建设、实验设备建设等,以提高教育质量。

建立集成电路教育平台,实现优质教育资源的共享和交流,促进教育公平和协同发展。

加强校企合作,推动产学研用深度融合,为学生提供实践机会和就业渠道,提高人才培养的针对性和实用性。

集成电路版图设计基础第4章:标准单元技术

school of phye

basics of ic layout design

16

网格式布线系统要求的库设计规则 对齐输入输出:

• 输入A和输出Z不能随意放置。它们必须像所有的连线一样位于同 样的网格上。 • 保证标准单元的所有输入输出不仅在x网格上,还要在y网格上。 要保证自动布线软件在水平方向和垂直方向都能找到它们。 • 保证所有的库单元以及库单元内部的器件符合网格规则。

school of phye

basics of ic layout design

7

标准网格

- 网格式布线器

grid-based router

• techfile - PHYSICAL RULES • 最小间距minSpacing:各几何图形外边界之间的距离。

school of phye

basics of ic layout design

school of phye basics of ic layout design 11

标准网格

- 网格式布线器

grid-based router

• coarse grid example:

1 microns 2 microns

1 microns

1 microns

Minimum wire is 1 micron, minimum spacing is 1 micron, therefore, our two wires use 3 microns, and we have established center-to-center grid spacing of 2 microns for this process.

• 数字库:高度固定,宽度可变。(fixed height, variable width.) 大多数库都是这样的。 对于数字版图,特别是标准单元版图,是唯一可行的方式。 在模拟版图设计中也非常有用,甚至是全定制的AIC。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

w l C sub C1 2

Cp N w

2

传输线电感

单端口电感的另一种方法是使用长度l<l/4波长的 短电传输线(微带或共面波导)或使用长度在l/4< l<l/2 范围内的开路传输线。

两种传输线类型的电感值计算 如下:

L

2 Z 0

tanh l

'

2 Z 0

MOS结构电容

a a + + + + + + + + + 1.0 Co 沟道 Cdep 沟道 耗尽层 p型衬底 Vss Vss (a) (b) Vgs d tox Cgb Co 0.2 积累区 耗尽区 反型区

MOS电容 (a)物理结构 (b)电容与Vgs的函数关系

MOS结构电容

Cox Cox Í µ µ Æ

CSi C ox ß µ ¸ Æ CSi C ox

0

VT

Vgs

MOS动态栅极电容与栅极电压的函数关系

电感

在集成电路开始出现很长一段时间内, 人们一直认为电感不能集成到芯片上 现在情况不同,集成电路的速度越来越 快,芯片上金属结构的电感效应越来越 明显,芯片电感的实现成为可能 半绝缘GaAs衬底、高阻Si衬底、挖去衬 底的空气桥形金属结构使电感获得有用 的品质因素

电感

集总电感可以有下列两种形式:

单匝线圈

多匝螺旋型线圈

多匝直角型线圈

硅衬底上电感的射频双端口等效电路:

Cp Rs Cox/2 R1 C1 Ls Cox/2 R1 C1

l Rs w 1 e t /

2 R1 w l G sub

2

0

ox

电阻

集成电路中的电阻分为 :

无源电阻

通常是合金材料或采用掺杂半导体制作的电阻

有源电阻 将晶体管进行适当的连接和偏置,利用晶体管的

不同的工作区所表现出来的不同的电阻特性来做电阻。

无源电阻

合金薄膜电阻 采用一些合金材料沉积在二氧化硅或其它介电材

料表面,通过光刻形成电阻条。常用的合金材料有: (1)钽(Ta); 多晶硅薄膜电阻 掺杂多晶硅薄膜也是一个很好的电阻材料,广泛 应用于硅基集成电路的制造。 (2)镍铬(Ni-Cr);

分布元件

集成电路设计中的分布元件主要包括微 带(Micro-strip)型和共面波导(CPW: Co-Plane Wave Guide)型的传输线。 集成电路中的传输线主要有两个功能: 传输信号和构成电路元件。

微带线

微带线(Micro-strip) 在一片介质薄板两面形成的两条平行带状导线。

互连线设计中应注意的事项

对于各种互连线设计,应该注意以下方面:

为减少信号或电源引起的损耗及减少芯片面积,

连线尽量短。

为提高集成度,在传输电流非常微弱时(如

MOS栅极),大多数互连线应以制造工艺提供的 最小宽度来布线。

互连线设计中应注意的事项

在连接线传输大电流时,应估计其电流容量并保留足 够裕量。 制造工艺提供的多层金属能有效地提高集成度。

电感

集成电路的电感影响包括振荡和过冲效应、由于阻抗失配引 起的信号反射、在导线间的电感耦合以及电压降引起的开关 噪声。

通过电感的电流变化产生如下的电压降:

例4.4

半导体导线的电感

导线模型

集总模型(Lumped Model)

把分布的电容集总为单个电容,导线仍表示为一个等势区,因而导线本身并不 引入任何延时,对于性能的唯一影响是由电容对于驱动门的负载效应引起。

2

MIM电容

电容模型等效电路:

固有的自频率:

f0

1 2 LC

金属叉指结构电容

MOS结构电容

平板电容和PN结电容都不相同,MOS核心部分,即 金属-氧化物-半导体层结构的电容具有独特的性质。

它的电容-电压特性取决于半导体表面的状态。

随着栅极电压的变化,表面可处于: 积累区 耗尽区 反型区

各类晶体管

寄生参数(电容、电阻、电感)对 集成电路的特性影响

都会使传播延时增加,相应性能下降。 都会影响能耗和功率的分布。 都会引起额外的噪声来源,影响集成电 路的可靠性。

举例

互连参数-电容

总电容:

边缘场电容

电阻

矩形导体的电阻可以定义为:

对给定工艺H是一个常数,电阻可以定义为:

集总RC模型

例4.6

树结构网络的RC延时

梯形链网络的Elmore延时:

结 论:

分布rc线

例4.8

铝线的RC延时

经验规则

例4.9

RC与集总C

传输线

波的传播方程:

传输线

在集成电路中传输线的电阻不能忽略,因此应当考虑一个较为复杂的模 型,称为有损传输线。

无损传输线

波是如何进行无损传输线传播?

第四章

导线

§4.1 §4.2 §4.3 §4.4

确定并定量化互连参数 介绍互连线的电路模型 导线的SPICE细节模型 工艺尺寸缩小及它对互连的影响

引言

集成电路可以认为是由元器件组成的。元器 件可以分为两大类:

△无源器件 △有源器件

■ 无源元件包括电阻、电容、电感、互连线、

传输线等。

■ 有源元件包括二极管、三极管、CMOS管等

有源电阻

I D + V S I IDS I O G S + V D (b) VGS V VTP

G

O

I IDS

VTN V (a)

VGS

MOS有源电阻及其I-V曲线

2t ox L V V 直流电阻: Ron︱VGS=V = I n ox W (V VTN ) 2

交流电阻:

rds

VDS I DS

高的集成度和更小的芯片尺寸。

比金属孔有更低的接地电感。

低的阻抗和速度色散。

共面波导

CPW的缺点是:

★衰减相对高一些。

★由于厚的介质层,导热能力差,不利于

大功率放大器的实现。

§7.2 二极管及其SPICE模型

端电压V与结电压VD的关系是:

VD V I D RS

其中

VD nVt I D IS e 1

电阻射频等效电路

芯片上的薄层电阻的射频双端口等效电路:

衬底电位与分布电容:

s n n+

n型外延层

a p

b

a R

b

a R

b

Cb 2

n s (b)

n

Cb 2

p (a)

Csub s (c)

有源电阻

有源电阻是指采用晶体管进行适当的连 接并使其工作在一定的状态,利用它的 直流导通电阻和交流电阻作为电路中的 电阻元件使用。 双极型晶体管和MOS晶体管可以担当有 源电阻。

Cj0 m

PN结内建势垒

V0

VJ

V

1

器件的电子噪声

所谓电子噪声是指电子线路中某些元器 件产生随机起伏的电信号。这些信号一 般是与电子(或其它载流子)的电扰动 相联系的。 一般包括:热噪声(白噪声)和半导体 噪声。半导体噪声包括散弹噪声、分配 噪声、闪烁噪声(1/f噪声)和场效应管 噪声。

例4.5 导线的集总电容模型

在图4.11的电路中,假设电源内阻为10KΩ的一个驱动器, 用来驱动一条10cm、1μm宽的AL1导线。在例4.1中,这条 导线总的集总电容等于11pF.

当外加一个阶跃输入(Vin 从0至 V)时,这一电路的过渡响应已知为一个指数函 数并可用下式表示:

解决方法:降低驱动器的电源内阻。

际电路设计中需借助SPICE等模拟工具来大致确定击穿电压值。

二极管模型参数对照表

参数名 饱和电流 发射系数 公式中符号 SPICE中符号 IS N 单 位 A SPICE中默认值 1.0E-14 1

IS n

串联体电阻

渡越时间 零偏势垒电容 梯度因子

RS

τ

T

RS

TT CJ0 M

Ω

Sec F -

0

0 0 0.5

电容

在集成电路中,有多种电容结构:

金属-绝缘体-金属(MIM)结构

多晶硅/金属-绝缘体-多晶硅结构 金属叉指结构

利用二极管和三极管的结电容 MOS电容

MIM电容

制作在砷化镓半绝缘衬底上的MIM电容结构:

C

r o lw

d

考虑温度系数时,电容的计算式为:

C Cox A 1 TC1t emp t nom TC 2t emp t nom

+V RS + VD ID Cj Cd

高频下:

V C j C j0 1 D 势垒电容Cj: V 0

m

_

二极管等效电路模型

dI D τT I D dQ C τT 扩散电容Cd: d dVD dVD n Vt

二极管参数

二极管在反向偏压很大时会发生击穿。专门设计在击穿状态下工作的 二极管称为齐纳二极管。但二极管的电流电压方程没有预示这种击穿,实

有损传输线

经验设计规则

当输入信号的上升或下降(tr , tf)时间小于传输线的飞行时间 (tflight)时应考虑传输线效应;

对于最长为1cm的芯片上导线,只需在tr<150ps时关注传输线效应。

传输线效应只有当导线的总电阻比较小时需考虑。如果不是, 可开用分布RC模型。

以上两个约束条件合成的导线长度的界定: 当总电阻比特征阻抗小很多时,传输线可以考虑为无损。