信号源的设计与制作

DDS信号源的设计与实现(电子科大)

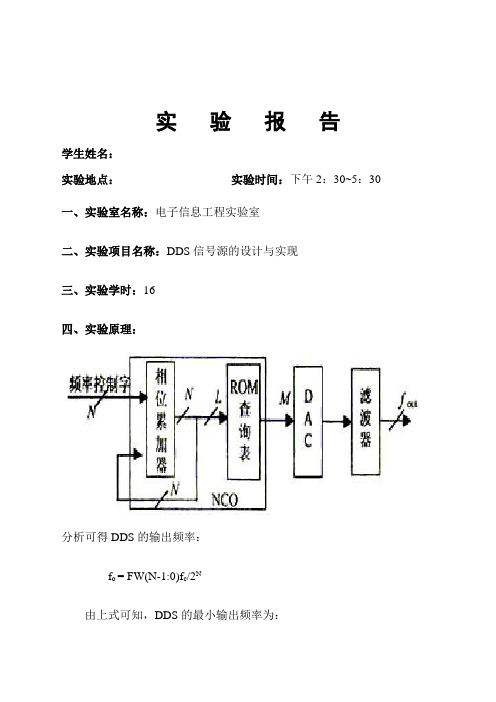

实验报告学生姓名:实验地点:实验时间:下午2:30~5:30一、实验室名称:电子信息工程实验室二、实验项目名称:DDS信号源的设计与实现三、实验学时:16四、实验原理:分析可得DDS的输出频率:f o = FW(N-1:0)f c/2N由上式可知,DDS的最小输出频率为:f omin = f c/2NDDS的频率分辨率为:f o = f c/2NDDS频率输入字的计算:FW(N-1:0) = 2N f0/f c五、实验目的:通过本实验项目,可使学生利用VHDL硬件描述语言对比较复杂的、综合性的实际电路系统进行设计、描述,利用EDA开发工具完成系统的综合、仿真,并用硬件平台完成系统的硬件实现, 着重培养学生的实际动手设计能力。

六、实验内容:1.EDA技术及VHDL2.EDA开发软件及实验箱的使用3.DDS信号源的设计与实现七、实验器材(设备、元器件):电脑,实验箱(带有EPF10K10 LC84-4芯片)八、实验步骤:① 创建新目录“D:\XX”,运行MAXPLUS II软件;② 打开Altera MAX+plus软件后,首先选择“File”中的“New”, 建立一个新的VHDL文件;③ 编辑VHDL源程序选择“Text Editor file”,再输入程序: library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity dds_nes isport (clk,swithc : in std_logic;freqin : in std_logic_vector(11 downto 0); --频率控制字宽:12位phasein : in std_logic_vector(5 downto 0); --相位字宽ampin : in std_logic_vector(7 downto 0); --加法器宽度ddsout : out integer range 0 to 255 );end dds_nes;architecture rtl of dds_nes issignal acc:std_logic_vector(11 downto 0);signal phaseadd: std_logic_vector(5 downto 0);signal romaddr: std_logic_vector(5 downto 0);signal freqw:std_logic_vector(11 downto 0);signal phasew:std_logic_vector(5 downto 0);signal romaddr_i:integer range 0 to 63;signal amp_t:std_logic_vector(15 downto 0);signal ddsout_t:integer range 0 to 255;beginprocess(clk)beginif clk'event and clk='1' thenif swithc='1' thenfreqw<=freqin;elsefreqw<=freqin+freqin;end if;phasew<=phasein;acc<=acc+freqw;end if;end process;phaseadd<=acc(11 downto 6)+phasew;romaddr<=phaseadd(5 downto 0);romaddr_i<=conv_integer(romaddr); --查找表字宽取整amp_t<=ampin*conv_std_logic_vector(ddsout_t,8);--8*8ddsout_t转为8位ddsout<=conv_integer(amp_t(15 downto 8)); --取高8位后转整process(romaddr_i)begincase romaddr_i iswhen 00 => ddsout_t<=255;when 01 => ddsout_t<=254;when 02 => ddsout_t<=252;when 03 => ddsout_t<=249;when 04 => ddsout_t<=245;when 05 => ddsout_t<=239;when 06 => ddsout_t<=233;when 07 => ddsout_t<=225;when 08 => ddsout_t<=217;when 09 => ddsout_t<=207;when 10 => ddsout_t<=197;when 11 => ddsout_t<=186;when 12 => ddsout_t<=174;when 13 => ddsout_t<=162;when 14 => ddsout_t<=150;when 15 => ddsout_t<=137;when 16 => ddsout_t<=124;when 17 => ddsout_t<=112;when 18 => ddsout_t<=99;when 19 => ddsout_t<=87;when 20 => ddsout_t<=75;when 22 => ddsout_t<=53; when 23 => ddsout_t<=43; when 24 => ddsout_t<=34; when 25 => ddsout_t<=26; when 26 => ddsout_t<=19; when 27 => ddsout_t<=13; when 28 => ddsout_t<=8; when 29 => ddsout_t<=4; when 30 => ddsout_t<=1; when 31 => ddsout_t<=0; when 32 => ddsout_t<=0; when 33 => ddsout_t<=1; when 34 => ddsout_t<=4; when 35 => ddsout_t<=8; when 36 => ddsout_t<=13; when 37 => ddsout_t<=19; when 38 => ddsout_t<=26; when 39 => ddsout_t<=34; when 40 => ddsout_t<=43; when 41 => ddsout_t<=53; when 42 => ddsout_t<=64; when 43 => ddsout_t<=75;when 45 => ddsout_t<=99;when 46 => ddsout_t<=112;when 47 => ddsout_t<=124;when 48 => ddsout_t<=137;when 49 => ddsout_t<=150;when 50 => ddsout_t<=162;when 51 => ddsout_t<=174;when 52 => ddsout_t<=186;when 53 => ddsout_t<=197;when 54 => ddsout_t<=207;when 55 => ddsout_t<=217;when 56 => ddsout_t<=225;when 57 => ddsout_t<=233;when 58 => ddsout_t<=239;when 59 => ddsout_t<=245;when 60 => ddsout_t<=249;when 61 => ddsout_t<=252;when 62 => ddsout_t<=254;when 63 => ddsout_t<=255;when others=>null;end case;end process;end rtl;④ 将源程序存为VHDL文件格式,并将VHDL文件设置为当前工程;⑤ 编译VHDL源文件,点击“MAX+plus II→Compiler→Start”进行编译,如果警告和错误不为0,要改正错误直至全部正确;⑥ 对照芯片,用导线依次对应连接好实验箱芯片的每一个接口;⑦ 确定无误后,打开试验箱与示波器电源,并运行程序,下载程序。

基于DDS技术的信号源设计与实现_彭文标

表 3 AD9852 的控制寄存器

- 272 - 360元 / 年 邮局订阅号: 82-946

图 4 BPSK 子程序流程图 图 4 为 BPSK 输出是的子程序流程图, 首先根据需要设置 AD9852 的控制寄存器, 然后 设 置 载 波 信 号 的 频 率 控 制 字 、两 个 相位调节字, 将待调制数据送入 AD9852 的 29 脚, 最后, 待更新 时钟作用后, 电路就输出 BPSK 信号。

基金项目:谐波信号处理与谐波电能精确计量研究 湖 北 省 自 然 科 学 基 金 (2006ABA202)

中(并 行 地 址 为 1FH) 的 三 位 工 作 模 式 设 置 位 进 行 选 择 , 设 置 方 式如表 1 所列。

《P LC 技术应用 200 例》

邮局订阅号: 82-946 360 元 / 年 - 271 -

题。AD9852 采用 3.3V 供电, 和单片机之间应设置一电平转换电

路 ; 参 考 时 钟 可 以 单 端 输 入 , 也 可 以 差 分 输 入 , 当 DIFF/SINGLE

SELECT(pin64)为 高 电 平 时 , 应 该 采 用 差 分 输 入 , 当 DIFF/SIN-

技 GLE SELECT 为低 电平时, 应该采用单端输入; AD9852 采用高

N 时, 输出的信号频率为 fout=FTW*fsc/2N。

系 统 时 钟 下 输 出 频 率 的 精 度 可 达 0.07Hz; 可 进 行 sin(x)/x 校 正 ;

理论上, DDS 的最高 输 出 频 率 可 达 参 考 源 频 率 的 一 半 。 当 具有良好的动态性能, 在 100MHz 输出时, DAC 输出的抑制寄生

5 结束语

高频信号源的设计与制作原理

题目:高频信号源的设计与制作原理所属系电子工程系专业电子信息工程学号01409227姓名丁亚指导教师丁文秋起讫日期2011.6.25—2011.7.15设计地点东南大学成贤学院高频信号源的原理与制作摘要关键词:高频频率源信号合成课程背景:随着社会的发展,通讯工具在我们的生活中的作用越来越重要。

通信工程专业的发展势头也一定会更好,为了自己将来更好的适应社会的发展,增强自己对知识的理解和对理论知识的把握。

无线电设备中广泛使用各类频率源,通常一个无线电通信系统或网络需要大范围能任意切换的频率点,需要采用频率合成技术来实现。

频率合成技术是现代通信对频率源的稳定度、准确度、频谱纯度及频带利用率提出愈来愈高要求的产物。

它能够利用一个高稳标准频率源合成出大量具有同样频率标准高性能的离散频率。

单片机在数字时钟中的应用已是非常普遍的,由单片机作为数字钟的核心控制器,可以通过它的时钟信号实现计时功能,将其时间数据经单片机输出,利用显示器显示出来。

本次设计是利用高频合成技术和单片机的计时功能,本文详细阐述了高频信号源的设计过程,涵盖了从需求分析,系统设计,编程,原理图,PCB图以及最后的试验板焊制等基本过程。

Principle and Production of High-frequency Signal GeneratorAbstractIn the field of communications, PLL synthesizers playing an increasingly important role. Synthesis is a system, initially the frequency of a series of reference for the entire frequency several times, the reference frequency is usually fixed. This synthesizer called integer N Synthesis. Synthesis technology is constantly advancing, there are a lot of new frequency synthesizer circuit, and in the communications circuits are widely used.This design is utilizing the SCM to work, among which the SCM AT89C51 is the core element. Meanwhile, LED digitron monitor dynamically to be designed ,invented, watched , texted.Radio equipment widely used in various frequency source, usually a radio communications system, or network requires a large range of arbitrary switching frequency point, require the use of frequency synthesis technology. Frequency synthesis technology is a modern communications on the frequency stability, accuracy, spectrum utilization for purity and moved more and more demanding products. It can take advantage of a high standard frequency synthesis out of a large number of sources with the same frequency standard high-performance discrete frequency.SCM in the application of digital clock is already very widespread, the MCU core as a digital clock, you can pass it to the controller of the clock signal timing features, its time data output by the microcontroller, the use of the monitor is displayed.This design is the use of high frequency synthesis technology and single chip timing functions, this article details the design of high-frequency signal source, ranging from requirements analysis, system design, programming, PCB diagram schematic diagram, as well as the final test of the basic plate welding system.Keywords: frequency synthesis technology for high-frequency signal source SCMKeywords: phase locked loop (PLL);PROTEL;PCB CARD;Synthesis目录高频信号源的原理与制作 (I)Principle and Production of High-frequency Signal Generator (I)Abstract (I)第一章课程背景 (1)1.1 高频信号源 (1)1.2锁相环 (2)1.3单片机 (2)1.4频率合成器 (5)第二章课程目的 (9)2.1树立正确的设计理念 (9)2.2学会项目的设计流程 (9)2.3养成良好的研究习惯 (9)2.3巩固与知新 (9)第三章课程任务 (10)3.1 基本元器件认识 (10)3.2 高频信号源的制作 (10)第四章课程介绍 (11)4.1PLL频率合成 (11)4.1.1 LC正弦振荡器电路 (12)4.1.2环路滤波器 (13)4.1.3锁相频率合成器 (15)4.2频率设置及显示电路 (16)4.3输出电路 (17)4.4电源部分 (19)第五章调试总结 (19)5.1调试电路 (19)5.1.1压控振荡器电路的调试 (19)5.1. 2分频方波信号的观察 (20)5.1. 3场效应管静态工作电压调试 (20)5.1. 4输出波形及显示电路调试 (20)5.2实验总结 (21)5.2. 1设计步骤 (21)5.2. 2布局原则 (21)5.2. 3焊接问题 (22)5.2. 4调试问题 (22)第六章 PROTEL 99SE 介绍 (22)6.1 PROTEL99SE的运行环境....................................................................... 错误!未定义书签。

信号源设计

信号源设计院系:班级:学号:姓名:指导老师:信号源设计1.信号源要求1)、在给定的+5V直流电源电压条件下,使用555芯片和运算放大器设计并制作一个多波形(方波、三角波和正弦波)发生器2)、信号频率f:0.85kHz~1.14kHz (实现频率可调)3)、信号周期T:874us~1.155ms4)、输出电压峰峰值:方波:2V≤Vp-p≤5V三角波:220mv≤Vp-p≤340mv正弦波:4mv≤Vp-p≤14mv2电路原理及主要元器件介绍2.1电路原理本次设计采用555定时器组成多谐振荡器,在接通电源后自行产生矩形波,通过积分电路将矩形波转变为三角波,再经积分网络转变为正弦波。

具体示意图如图1所示。

积分电路积分电路图1波形转换示意图2.2 555芯片介绍555定时器是一种集模拟、数字于一体的中规模集成电路,可以将输入的模拟信号变化为一定的数字信号输出,因而广泛应用于生产实践的各个领域。

它不仅用于信号的产生和变换,还常用于控制和检测电路中。

555定时器的内部电路由分压器、电压比较器C1和C2、由两个与非门G1和G 2组成的基本RS触发器(低电平触发)、放电三极管T以及输出反相缓冲器G3组成,其内部结构图如图2所示。

多谐振荡器方波三角波正弦波图2 555定时器内部结构图引脚功能:Vi1(TH):高电平触发端,简称高触发端,又称阈值端,标志为TH。

Vi2(TR):低电平触发端,简称低触发端,标志为TR。

V CO :控制电压端。

VO:输出端。

Dis:放电端。

Rd:复位端。

555定时器内含一个由三个阻值相同的电阻R组成的分压网络,产生31V CC和32V CC两个基准电压;两个电压比较器C1、C2;一个由与非门G1、G2组成的基本RS触发器(低电平触发);放电三极管T和输出反相缓冲器G3。

Rd是复位端,低电平有效。

复位后, 基本RS触发器的Q端为1(高电平),经反相缓冲器后,输出为0(低电平)。

分析555定时器的内部电路图可知:在555定时器的VCC端和地之间加上电压,并让VCO 悬空,则比较器C1的同相输入端接参考电压32V CC,比较器C2反相输入端接参考电压31V CC,为了学习方便,我们规定:当TH端的电压>32V CC时,写为V TH=1,当TH端的电压<32V CC时,写为V TH=0。

信号源的设计和制作

一、 总体方案

设计制作一个能产生正弦波和脉冲波信号源。要求信号频率 在20Hz~20kHz范围内能程控步进调整,脉冲波的占空比在 2%~98%之间能程控步进可调,且性能良好,满足指标。

1. 方案比较

(1)正弦波产生

方案一:采用单片函数发生器(8038),8038可同时产生 正弦波、脉冲波,方法简单,,但步长难以满足要求,且频 率稳定度不高。

模拟开关CD4051

滤波器

波形输出 输出驱动NE5532

三、调试过程

1.使用的仪器与仪表

PC机,386DX40,5M内存 数字频率计,8610A型 MICE—51仿真器 XD低频信号源 20MHz双踪示波器 真空管毫伏表,DYC—5 BSIA失真度测量仪 890型数字万用表 JWY—30F稳压电源

2.实施方案

根据以上分析,选用如下方案。

(1)正弦波产生 800Hz以下的正弦波产生采用软件相位累加DDS方案来实

现。800Hz~50kHz的正弦波采用动态生成程序的方法来实现。

(2)方波的产生

方波由同频率的正弦波产生,采用计数定时方案来实现占 空比的步进调整。为提高占空比的精度,采用预分频和择优技 术。

另一个是使用可编程逻辑器件,如GAL,这样在发现错误时只要 重新改变编程,不需要做大的改动。

系统实现错误主要是器件接线错误或工作点设置错误。查找实现 错误时可以根据模拟的结果进行对照调试,或由电路的因果关系确定 故障的位置。

四、结束语

频率合成部分是信号源的关键。可以采用动态编程 和吞时钟脉冲技术,提高了软件的处理效率,使正弦波 频率的高端扩展到50kHz,步进1Hz。从实际制作的结果 来看,各方面的指标可达到指标要求,可有不同程度的 提高,也可证明该方案的正确性和可行性。

高速脉冲信号源的设计与实现

1

在高速运放调理 电路设 计 中, 主要考虑 高速运放

的选择 、 号幅值的凋理和驱 动电路的设计。 信

2 1 1 高 速 运 放 的选 择 ..

从 FG P A输出的原始信号经过差动放大 电路进行

( i一 )+ U. ’ ) ( 2)

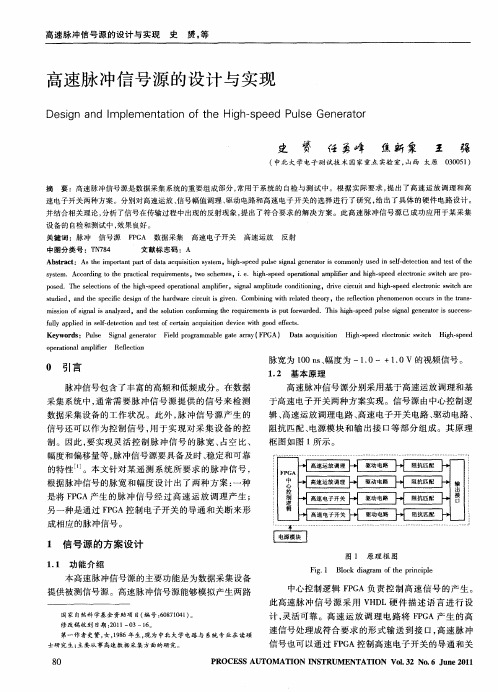

框 图 如 图 l所 示 。

FPGA

中 心 控 制 逻 辑

输 出 接

口

1 信号源 的方案设计

图 1 原 理 框 图

1 1 功 能介 绍 .

F g 1 Blc ig a o h r cpe i. o k d a r m ft e p i il n

本高速脉冲信号源的主要功能是为数据采集设备

( 中北大 学电子测试技 术 国家重点 实验 室, 山西 太原 0 0 5 ) 3 0 1

摘

要 :高速 脉冲信号 源是数 据采集 系统 的重要组 成部分 , 常用于 系统 的 自检与 测 试 中。根 据实 际要 求 , 出了 高速 运放 调理 和 高 提

速 电子开关两 种方案 。分别对 高速运放 、 信号 幅值调 理 、 驱动 电路和 高速 电子 开 关的 选择 进行 了研究 , 出 了具体 的 硬件 电路 设计 。 给

中图分类 号 :T 7 4 N 8

文献 标志码 :A

Ab ta t: Aste i otn ato aaa qust ns se ,hg s e u s in lg n rtri c mmo l s d i efdee t na dts fte sr c h mp ra tp r fd t c iio ytm i ih-pe dp lesg a e e ao s o nyu e n sl- tci n e to o h s se y tm. Ac odigt h rcia e uie ns wo sh me c r n ote p a t lrq r me t,t c e s,i e ih s e d o eain la l e ndhg —p e lcrncs th ae po c . .h g —p e p rt a mpi ra ih s e d ee to i wic r r— o i f p s d T e slcin fteh g s e d o eain la lf r in mp i d o dt nn o e . h ee t so h ih—p e p rt a mp ie ,sg a a lt ec n io ig,die cr uta d hg —p e lcrnc s th ae o o i l u i rv ic i n ih s e dee to i wic r su id。a d te s e i cd sg ftehad r ic i sgv n t de n h p cf e ino r waecru ti ie .Co iigwihr ltd te r i h mbnn t eae h oy,terfe to h n me o c u si h rn — h e cin p e o n no c r nteta s l miso fsg a sa ay e sino in li n lzd,a d tes lt n c no mi gte rq ie nsi u owad d.T i ih s e d p lesg a e e ao sS c e s n h oui of r n h e ur me t sp tfr r e h shg —p e us in lg n rtri u c s— o f l p le n s l-ee to n e to e an a q iiin d vc t o d e e t. ul a p id i efd tcina d ts fc r i c usto e iewi g o f cs y t h

实用信号源的设计和制作(严俊宇)

电子系统设计报告设计课题:实用信号源的设计和制作学院:机械与电子工程学院专业:自动化姓名:***学号:*********实用信号源的设计和制作一、设计任务及主要技术指标设计任务:在给定±15V电源电压条件下,设计并制作一个正弦波和脉冲波信号源。

设计要求:1.基本要求(1)正弦波信号源①信号频率:20Hz~20kHz步进调整,步长为5Hz,②频率稳定度:优于10-4③非线性失真系数≤3%(2)脉冲波信号源①信号频率:20Hz~20kHz步进调整,步长为5Hz②上升时间和下降时间:≤1μs③平顶斜降:≤5%④脉冲占空比:2%~98%,步进可调,步长为2%(3)上述两个信号源公共要求①频率可预置。

②在负载为600Ω时,输出幅度为3V。

③完成5位频率的数字显示。

2.发挥部分(1)正弦波和脉冲波频率步长改为1Hz。

(2)正弦波和脉冲波幅度可步进调整,调整范围为100mV~3V,步长为100mV。

(3)正弦波和脉冲波频率可自动步进,步长为1Hz。

(4)降低正弦波非线性失真系数。

二、本设计总体方案由于本设计要求不能采用专用信号发生芯片和可编程器件,并且要求达到的频率范围为20Hz~20KHz,为低频信号发生器,因此拟采用方法一,即由分立器件构建频率产生单元,产生振荡后再实现正弦波和脉冲波,这种方法有以下两种信号输出方案。

方案一:如图2.1所示。

图2.1 信号输出方案一方案二:如图2.2所示。

图2.2 信号输出方案二考虑电路结构和实现方便,拟采用方案二。

系统总体框图如图2.3所示。

所设计的信号发生器由振荡电路、稳幅电路、正弦波调幅电路、电压比较电路、脉冲波调幅电路组成。

频率产生单元由振荡电路和电压放大电路构成,能够产生频率可调的正弦波信号,正弦波信号的幅度调整后经电压比较器和脉冲调幅电路输出要求的脉冲波。

图2.3系统总体框图三、正弦波信号生成方案信号发生器的工作频率范围、频率稳定度、频率设置精度、相位噪声、信号频谱纯度是信号发生器性能的重要指标,都与频率产生单元有关,在本设计中频率产生单元首先生成正弦波信号,正弦波信号的频率大小直接影响后面脉冲波信号的步进,因此正弦波信号的产生方法十分重要。

基于MARX电路的高斯脉冲信号源的设计与实现

基于MARX电路的高斯脉冲信号源的设计与实现文章对高斯脉冲信号在电磁兼容测试方面的应用进行了概述,讲述了雪崩三极管以及MARX电路的基本理论,采用雪崩三极管组成MARX电路来生成高斯脉冲信号的原理,分析MARX电路结构对脉冲的影响,对波形各项指标进行了分析和规律总结。

设计了基于MARX电路和雪崩三极管的高斯脉冲信号发生器,脉冲幅值800V(50欧负载),半高宽2ns,重复频率从1kHz至20kHz可调,工作状态稳定已持续工作数十小时,对脉冲源的改进提出了设想。

标签:雪崩三极管;MARX电路;脉冲源;电磁兼容引言随着科学技术的发展,电子系统和设备的数量与日俱增,性能也在不断提高,并正向高频率、宽频带、高集成度、高可靠性、高精度和高灵敏度方向发展。

与此同时,电磁干扰的问题势必越来越严重,现已成为电子系统和设备正常工作的突出障碍。

在实际工作环境中,随着设备的增多,多个设备共同工作在同一环境下,设备之间会产生扰动,特别是在大型的设备与机器上,同时工作的元器件多达几百甚至上千个,电磁环境非常复杂,导致设备的故障率大幅提高,如何对设备的电磁兼容环境进行测试成为一个热点问题。

高斯脉冲信号具有功率大,频谱广的特点,能够覆盖设备的各个敏感点,有利于模拟真实的电磁环境。

高斯脉冲信号生成电路在军工、科研、雷达探测、超宽带传输等多个领域具有重大的作用,是当前研究热点。

1 雪崩三极管的二次击穿雪崩三极管是一类专门用于工作在雪崩区的三极管,具有较高的Vceo与Vcbo,在脉冲状态下最大工作电流可以达到几十安。

这类雪崩三极管通常可以工作在负阻区,并具有二次击穿的特性,非常符合脉冲生成电路的制作要求。

负阻效应是指当三极管工作在雪崩区时,Vce随Ic的增大而减小的效应。

二次击穿指当三极管工作在雪崩区时,它的工作点并不稳定,当电流继续增大时会发生二次击穿,此时的电流非常大。

如图1所示:当雪崩三极管处于第一次雪崩时,工作在c点,而随着电流增大,导致工作点的上移至b点,而b点的工作状态并不稳定,雪崩三极管发生2次击穿,此时工作点继续上移至a点。

发射台信号源系统的设计与改造

质 量, 对于合肥大蜀山发射台这样综合 际要求来具体分析。 性台站来说 , 由于信号源系统复杂庞 大 常用的机架、 机柜类型有三种,组合式标准安装, 可以进行扩展 , 另外 使用机柜时, 必须要考虑 电缆的数

因此其重要性也更为突出。自2 0 年以 双柱开放式机架、 04 四柱开放式机架和专 机柜还 自 带竖直长配电盒为设备供 电。 来, 大蜀 山发射台陆续对信号源系统进 用机柜。双柱开放式机架成本较低 , 负

可靠性、 科学性、 方便性和规范化 , 使其 的安装, 有多种尺寸选择 ; 专用机柜则主 远达不到实际需要的面积 , 为此我们对 安全性 大幅提升, 同时彻底解决了过去 要用于高密度伺服器 、 网路设备、 电信和 电缆入 口孔进行 了重新 设计, 并从机房

系统操作及维护繁琐的弊端。

广电设备, 着重于冷却、 配电、 缆线管理 地沟走线边缘打出一走线槽直通机柜底

要求。经过充分的调研后, 我们结 合发 装侧门, 两边的机柜各有一个 侧门, 与 直接切换对负载供电, 功能 的实现通 其

射台自己的实际情 况, 重对 机柜 选型、 通用机柜不同的是 , 着 所有机柜我们都没 过外接交流接触器实现, 切换原理 如图 配电、 防雷、 抗干扰、 布线及标识方法等 有订做前门, 而是要求厂家提供 更多数 1 所示, 接触器线包J P 输出供 电, 由u s 同

间的距离要尽量大些, 因为感应噪声u n

常开接点吸合, 常闭接点断开, P 输出 US

最 后, 对一些易受雷电影响的设备 和 导线 间隔成 反 比 , 间隔越小 噪声越

直接供负载使用, 实现u s P 的在线供 电 及数据 口进行处理 , 如对与发射机连接 大, 以交流做 电源的器件, 对 它们的输入、 功能; P 出现故障, 而U s 无输出时, 线包J 的R 一3 及R 一8 接口采用专门的光电 输出线应分开 走线; S2 2 S4 5 对低 电平信号线和

一种L波段跳频信号源的设计与实现

又

Ⅳ:I( OM+1+ )A

则有

1 跳 频信号源 工作原理

本跳频 源实 现框 图如 图 1 所示 . 考信号 由 参

收 稿 日 期 : 0 60 . 6 修 订 日期 : 0 6 0 - 8 2 0 — 92 ; 2 0 -9 2

f [R( o [/ 厂 R+1 [ ( +1十 )1 ]0 ) ]

图 1 跳 频源 实现 框 图

相 位 噪声 恶化 控 制在 2 B以 内. 2d 同时 , 用 频率 采

预置 技术 来提 高 系统 的跳 频速 度 , 足 系统 设计 满

可 编程 分频 比 Ⅳ的值 南 E R M 给 m. O输 PO VC 出频 率 与参 考 源的输 出频 率 和环路 分 频 比Ⅳ 之 问的关 系 为 丘

频率合 成 主要 有直 接 式 、锁 相式 和直 接 数字

10MH 0 z的晶体 振 荡器提 供 , 经参考 分 频器 +1

式3 种方 法 . 直接 式频 率合 成 , 对 当频率 源输 出跳

频点 数较 多时 , 合成 器 的体积较 大 , 在对体 积 要求

分 频后 , 到频率 为. 的鉴 相信 号. 得 鉴相信 号与

V O采 用 集成 宽 带压 控振 荡器 H 43 它采 C E 0B, 用 硅双 极 晶体 管振 荡 , 有 低相 位 噪声 和 良好 的 具

器 和 A计数 器 的值 . 要求 : 且 A

频 比 Ⅳ 9. 0

+1 ≠0 由 , .

此可知, 若要 获 得连 续 的跳 频信 道 , 则要 求环 路分

即相 位锁 定. 中 , 率预 置 电 为粗 调 电压 , 其 频 它 使 得 跳频 时 VC O能够快 速 存跳 频点 附 近振 荡 , 从

信号源的设计和制作

信号源的设计和制作内容摘要:本文介绍了信号发生器的基本原理以及工作流程,在电子信息技术领域,经常要用到一些信号作为测量基准信号或输入信号,也就是所谓的信号源。

信号源的好坏在很大程度上决定了系统的性能,因而常称之为电子系统的“心脏”。

随着电子技术的发展,对信号源的要求越来越高,要求其输出频率高达微波频段甚至更高,及频率分辨率达到m级Hz甚至更小,相应频点数更多,频率转换时间达到ns级,频谱纯度高,同时对频率的功耗、体积、重量等也有更高的要求。

要实现高性能的信号源,必须在技术手段上有新的突破。

针对以上对信号源高性能的要求,研究和制作一款频率和分辨率更高、转换时间更少、频谱纯度更高的信号发生器成为了人们广泛关注的焦点。

而基于DDS技术的产品,可以很好的达到上述各项性能的要求,为当今科技更好更快发展提供了有效的设备基础,正是在这样的背景下,高精度的信号发生器应运而生。

关键词:信号发生器频率歩进占空比1信号源的设计和制作前言本系统基于DDS工作原理并对累加器与地址存储器等加以优化,利用FPGA编程实现DDS 硬件功能,实现了题目要求产生频率可调正弦波、占空比可调脉冲的设计目的。

以单片机(AT89S51)为核心,实现对波形、频率、脉冲占空比、幅度调整等的选择与连续控制。

同时,将设定的参数和相关信息通过LCD12864显示。

所设计的信号发生器由振荡电路、稳幅电路、正弦波调幅电路、电压比较电路、脉冲波调幅电路组成。

采用RC振荡方式产生振荡信号,通过二极管IN4148和运放TL082实现振荡信号稳幅,调幅之后输出正弦波信号,再经电压比较器和调幅电路实现脉冲波的占空比和幅度的变化。

采用了多级电阻和多级双联电位器实现频率的分段和步进。

信号发生器技术发展至今,引导技术潮流的仍是外国的几大仪器公司,如日本横河、Agilent、Tektronix等.美国的FLUKE公司的FLUKE-25型函数发生器是现有的测试仪器中最具多样性功能的几种仪器之一,它和频率计数器组合在一起,在任何条件下都可以给出很高的波形质量,能给出低失真的正弦波和三角波,还能给出过冲很小的方波,其最高频率可以达到5MHZ,最大输出幅度也达到10Vpp。

高频脉冲雷达信号源的设计与实现

源 系 统 产 生 的 高 频 信 号 频 率 稳 定 度 高 , 频 转 换 时 间 短 , 位 调 制 精 确 , 适 合 于多 种 编 码 方 式 , 全 满 足 高 频 脉 扫 相 且 完 冲雷达对信号 源的性能指标 和技术要求 .

Zhu Zhe gpi g , i gl , n n LiN n i Che un, nK Lan Ji pi g a n

(Co lg fElc r n c n n o ma i n En i e rn So t - n r lU n v r i o to a i e , u a 3 0 4, i a l e o e t o is a d I f r to g n e i g, u h Ce t a i e st f rNa i n l i s W h n 4 0 7 Ch n ) e y t Ab t a t Ac o d n o t e t c n c ld ma d o ie t dg t ls n h sz r ( sr c c r i g t h e h ia e n f d r c i ia y t e ie DDS) i h s p p r we d sg e n ,n t i a e e i n d a d

ห้องสมุดไป่ตู้

r a ie o r sg a o r e o i h f e u n y p le r d r b s d o h o e c i e l d f u i n l u c s f r h g —r q e c u s a a a e n t e c r h p AD9 5 ,wh c s c n r l d b z s 99 ih i o t o l y e C8 5 c o o o 1 mir c mp t r u e .Th 0 1 M CU sa o t d t r c s h n u o t o r n h n p o r m eC8 5 i d p e o p o e s t e i p tc n r l wo d a d t e r g a AD9 5 o 9 9t

信号源的设计与制作Multisim实验报告

该电路Rf回路串联两个并联的二极管,如上图所示串联了两个并联的1BH62,这样利用电流增大时二极管动态电阻减小、电流减小时动态电阻增大的特点,加入非线性环节,从而使输出电压稳定。

用Multisim10.0对电路进行仿真得到下图

仿真波形

仿真得出的数据与理论计算一样,电路正确。

从电压传输特性上可以看出,当-UT<uI<+UT时,UO可能是-UT,也可能是+UT。如果uI是从小于-UT,的值逐渐增大到-UT<uI<+UT,那么UO应为+UT;如果uI从大于+UT的值逐渐减小到-UT<uI<+UT,那么应为-UT。曲线具有方向性,如图b)所示。

实际上,由于集成运放的开环差模增益不是无穷大,只有当它的差模输人电压足够大时,输出电压UO才为±UZ。UO在从+UT变为-UT或从-UT变为+UT的过程中,随着uI的变化,将经过线性区,并需要一定的时间。滞回比较器中引人了正反馈,加快了UO的转换速度。例如,当UO=+UZ、uP=+UT时,只要uI略大于+UT足以引起UO的下降,即会产生如下的正反馈过程:UO的下降导致uP下降,而UP的下降又使得UO进一步下降,反馈的结果使UO迅速变为-UT,从而获得较为理想的电压传输特性。

本电路中该电路的作用是将正弦信号转变成方波信号,其传输特性曲线如下图所示:

正弦波传输特性

2.4方波转换成三角波电路的工作原理:

当输入信号为方波时,其输出信号为三角波,电路波形图如下:

2.5总电路图

三 单元电路设计原理与仿真

3.1 正弦波发生电路的设计

本电路中采用RC桥式正弦波振荡电路(文氏桥正弦波振荡电路)产生正弦波,其电路图如下所示

直接数字频率合成低频信号源的设计与实现

难 以集 成 化 且 成 本 高 。间 接 合 成 法 的 核 心是 锁 相 环 技

修 改 稿 收 到 日期 :0 0—0 21 6—2 9。

第一作 者邹 尔宁 , ,9 6年 生 ,9 8年毕 业 于北京航 空 学 院分 院 自 女 15 17

术 , 了合 成 所 需 要 的频 率 , 要 采用 多种 形 式 的锁 相 为 需

Abta t Drc dgt rq ec y tei D S)fa rsa v nae f ih rslt n,p aecniuu p nf q ec w t igad sr c: i t iilf u n ysnhss( DF e a e et e d a t so g eoui u g h o h s o t o su o r un ys i hn n n e c

+ [

丑一 ,

图 1 DDF S原 理 图

Fi 1 Prncp e o g. i il fDDFS

高于其他频段 的频率 覆 盖系数 , 一般 的 R C振 荡器 或 L c振荡器都无法达到… 。随着计算机技术 的发 展 , 数

字技 术 已广 泛 应 用 于 各 类 电 子 测 量 仪 表 , 接 数 字 频 直

正 弦样本 , 需要 一 个容 量 为 2的 计 数器 , 还 以此 得 到 2

一种精密信号源的设计与实现

第 l卷 9

第5 期

山 东 科 学

S N 0NG S I NC HA D C E E

V 1 1 No 5 0.9 . 0c . 0 6 t2 0

பைடு நூலகம்

20 06年 l 月 0

文章编号 :024 2 (())50 8.3 10.(6 2 6 o . 50 r x 0

2 2 1 脉 冲信 号产 生原 理 ..

图 2 单 片机 系统的基本框图

要产生精确的脉冲信号 , 必须正确设定 c U内的定时器, P 在定时中断中将信号 出 口翻转 , 进入定时 中

断的间隔时间为信号周期的二分之一 , 对于单片机 A 8C 2 T9 5 来说 , l 位定时器定时时间为 : = 656 用 6 t (53 一

有了 4 2m ~ 0 A的电流输出后 , 只要外接一个 20 的高精度电阻 , 51 2 便得到了 1 5 ~ V的电压信号。这也是

为 了使 电路 变得 简 洁 , 体 电路 如 图 1 具 所示 。

另外 , 实际中还需要 0 v电压 , 若采用 图 1 的接法 , 就需要有 0 A的电流输 出。因为实际 中使用 的旋转 m 开关具有两路独立 的档位 , 所以在旋转 开关 8 脚对应另外一路的位 置 1 上, 脚 设置 了一个接地 , 电压 为 使

接 口简单 、 整体体积小 巧等特点。在实际应用 中 , 可以极大地缩短研发周 期 、 降低成本 。

关键词 : 精密信号源 ; 基准信号 ;T 9 5 ;E 15 A 8C 2R F9

中图分类号 :P6 . 38 2 T 文献标识码 : B

1 引言

在浮标的各种电子设备的研制 、 试验过程当中有一个基本方法 : 模拟试验法 , 即通过模拟传感器 的各个 参数对仪器进行检测 。精密信号源就是基于这种方法的需求而设计 的, 的基本功能是模拟 浮标系统各个 它

调幅波信号源的设计与制作

摘要波形发生器是一种常用的信号源,广泛地运用在电子电路、自动控制系统、和教学实验等领域。

文中以AT89C51单片机为核心设计了一个低频函数信号发生器。

信号发生器采用数字波形合成技术,通过硬件电路和软件程序相结合,可输出自定义波形,如正弦波、方波、三角波、梯形波及其他任意波形,波形的频率和幅度在一定范围内可任意改变。

波形和频率的改变通过软件控制,幅度的改变通过硬件实现。

介绍了波形的生成原理、硬件电路和软件部分的设计原理。

关键词:低频信号发生器; 单片机;D/A转换AbstractWaveform generator is a common signal source, widely used in electronic circuits, automatic control system, and teaching experiment etc.. Based on the 89C51 microcontroller as the core design of a low frequency signal generator. The signal generator with digital waveform synthesis technology,combined with the hardware circuit and software program, custom output waveforms, such as sine wave, triangle wave, trapezoidal, Fang Bo and otherarbitrary waveform, frequency and amplitude of the waveform can be changed in a certain range. The waveform and frequency change through software control,the magnitude of change by hardware. The design principle of the generation principle, hardware circuit and software part of the waveform.Keywords:Low frequency signal generator;Single chip microcomputer;D/A conversion目录1 绪论 (1)1.1研究背景和意义 (1)1.2国内外研究现状 (1)1.3主要内容和结构安排 (2)方案设计 (3)2.1方案设计思想 (3)2.1.1波形产生方案 (3)2.1.2 改变幅度方案 (3)2.2工作原理 (3)3 硬件电路设计 (5)3.189C51单片机简介 (5)3.2单片机最小系统电路 (7)3.3DA转换电路设计 (8)3.4运算放大电路和低通滤波电路 (10)3.5系统总电路图 (11)4 系统软件设计 (13)5系统仿真 (16)5.1仿真软件 (16)5.2系统仿真步骤与结果 (16)5.3出现的问题和解决办法 (18)6 结论与展望 (19)参考文献 (20)致谢............................................................................................................... 错误!未定义书签。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、直接数字合成(DDS)

直接数字合成(Direct Digital Synthesis、DDS)是一种新的频率合成技术和信号产 生的方法。直接数字频率合成器(DDS)具有超高速的频率转换时间,极高的频率分辨率和较 低的相位噪声,在频率改变与调频时,DDS 能够保持相位的连续,因此很容易实现频率、相 位和幅度调制。 此外, DDS 技术大部分是基于数字电路技术的, 具有可编程控制的突出优点。 因此这种信号产生技术得到了越来越广泛的应用, 很多厂家已经生产出了 DDS 专用芯片, 这 种器件成为当今电子系统及设备中频率源的首选器件。例如 ANALOG DEVICES 公司的 AD9850 就是一个可以工作在 125MHz 时钟频率的,具有 10bit DAC 的 DDS 芯片。AD9854 是一个可以 工作在 300MHz 时钟频率,具有 I/Q 两路 12bit DAC 的 DDS 芯片。当今通信系统迅速发展,软 件无线电成为很热门的话题,DDS 在这些系统中都成为很重要的一门技术。有兴趣的同学可 以参考上面提到的两款芯片资料,了解当今 DDS 系统。 1、 DDS 的基本原理 DDS 的原理框图如图 1 所示。 图中相位累加器可在每一个时钟周期来临时将频率控制字 (TUNING WORD)所决定的相位增量 M 累加一次,如果记数大于 2 ,则自动溢出,而只保 留后面的 N 位数字于累加器中。 正弦查询表 ROM 用于实现从相位累加器输出的相位值到正弦 幅度值的转换, 然后送到 DAC 中将正弦幅度值的数字量转变为模拟量, 最后通过滤波器输出 一个很纯净的正弦波信号。

f 0 min ~ f 0 max ,则 f c 应大于 f 0 max 的2倍,这是由Nyquist定 f 0 max 的

理决定的。为了使输出波形更好,同时减低低通滤波器的参数要求,一般 f c 至少取

4倍以上。DDS系统中的数模转换器DAC的转换时间应小于1/ f c ,数模转换比特数 n 越大, 则波形失真及量化误差越小。但受价格等因素的限制,只能取一个适当的值。

1 为采样率。由式(3.8)和式(3.10)得出: ts

(3.11)

X ZOH

f − jπ f / s ∞ ( f ) = sin c ( ) e ∑ X ( f − kS ) S k = −∞

由式(3.11)可看出零阶保持采样使频谱衰减且引起 sinc 函数失真。 4.3 量化的影响: 数字化模拟信号不仅表现在时间上采样信号, 还要把幅度量化为有限个比特的数值。 由 于 DDS 系统对应的是均匀量化, 这里我们主要关心均匀量化。 均匀量化是把信号的幅度范围 内均匀分成 2 等份,构成 m 比特均匀量化,在两个相邻量化幅度之间的信号幅度值,通过 取整或截尾处理,取量化电平。一般的讲,定量分析量化的影响是很困难的。对于 DDS 系统 做分析,如果 DAC 数模转换比特数为 n ,正弦查询表 ROM 的地址数最小为 m ,相位累加器

k = −∞ k = −∞

(3.8)

XI ( f ) 在频率上具有周期性,其周期为采样率 S 。对于单频正弦信号,如图 3.3:

X(f)

XI(f)

-fO 0 fO

f

-s

-fO 0 fO

s

f

图 3.3A

图 3.3B

4.2 零阶保持采样: 实际中,模拟信号采用零阶保持(zero-order-hold ZOH)装置进行采样,这种采样就 是在得到下一个采样前保持前一个采样, 也叫平顶采样。 这种采样等价于理想采样后通过了 一个系统,该系统的冲激响应为:

f 0 min 是DDS

系统的频率分辨率或输出最小频率。 当要求的最小输出频率大于要求的频率分辨率时,f 0 min

45

应取要求的频率分辨率。由式(3.3)可计算出相位累加器的位数 N :

相位累加器的位数 N :

⎛ fc ⎞ N ≥ ln2 ⎜ ⎜f ⎟ ⎟ ⎝ 0min ⎠

(3.4)

一般情况, N 选大一些对于数字电路是比较容易的。所以 DDS 系统可以很容易地实现 高频率分辨率、大频率变化比(最大输出频率与最小输出频率的比)的信号。另一方面,如 果 N 比较大,一个周期内时间轴被分为 2 个点,DDS 系统的正弦查询表 ROM 中是否必须 存储 2 个点的数据呢,答案是否定的。这是因为 DDS 系统的数模转换比特数 n 是有限的, 一般不太大,特别对于高速 DAC,高比特数 DAC 也没有很大必要。这样,正弦查询表 ROM 中 如果存储非常多的点,则很多相临的点存储的是同样的幅度值。

48

二、用 DDS 的方法设计信号发生器

1、 信号发生器框图

8051 最小系统

DDS系统 可变占空比方波 单脉冲波形产生

波形 输出

输出

输入

图3.4 信号发生器框图

2、 参数计算 依题目要求: 信号频率为 1Hz~20KHz步进调整, 步长为1Hz 。 可以取频率控制字M=1 时,输出信号为 1Hz ,这样输出信号频率可表示为:MHz 。则有:Mmin=1 , Mmax=20K 。 为保证输出波形质量,当Mmax=20K 时,选 DAC 输出点数为 50 ,则可算出相位累加器 位数 N=20 。时钟频率 f c =2 =1.048576 MHz 。

m

2 N −m × f c 时,输出信号等效于采样频率降低,这是因为有多于一个 的位数为 N ,当 f 0 < 2N

时钟才有幅度变化。 4.4 LPF 的设计依据讨论。 在前三个小节中(4.1、4.2、4.3)分别讨论了理想采样、零阶保持和量化在模书数转 化中对信号的影响,对应到 DDS 系统中,要恢复原始的模拟单频信号也应考虑这些因素。设 计 DDS 系统的 LPF 时,由于 DDS 系统的时钟对应于采样率,一般是固定不变的,由 4.1 节的 讨论,似乎 LPF 的设计很简单,设 DDS 的输出频率范围为 则 LPF 的通带为 0 ~

2π 2 ≤ n m 2 2

(3.5)

对于 m 和 n 都为正整数,可得出:

m=n+2

(3.6)

从 DDS 系统中相位累加器的位数 N 取高 m 位送到正弦查询表 ROM 作为地址线即可满

46

足要求。之所以将低位舍弃,是因为舍弃的低位变化对应于输出幅度在 ± 输出同一个量化电平。 4、 DDS 系统的低通滤波器 LPF 设计依据

n = −∞

∑

∞

δ ( t − nt s ) =

n = −∞

∑

∞

x [ n ]δ ( t − nt s )

(3.7)

式中 x [n] 代表采样值 x ( nt s ) 的序列。 x I

∞

(t ) 的频谱 XI ( f ) 由下面的卷积表示:

∞

X I ( f ) = X ( f ) ∗ I ( f ) = X ( f ) ∗ S ∑ δ ( f − kS ) = S ∑ X ( f − kS )

20

选用分辨率为 n=8 的 DAC ,则用于角度-幅度变换的 EPROM 地址为 m=10位。考虑到 此系统中有正弦波和占空比2%~98%的方波共50种,因此 EPROM 应再增加 6 位控制波形 的地址,共需 16位 地址。 3、 注意问题 (1) 元件时序 DDS 时钟频率若选 f c =1.048576 MHz,则 Tc =953.7ns 。 选择寄存器、加法器元件,使得相位累加总时间小于 Tc ; 选择用于角度-幅度转换的 EPROM 速度大于 Tc ; 选择 DAC 的转换速度大于 Tc 。 (2) 滤波器 DAC 输出的是阶梯正弦波,存在奇次谐波。滤波器的作用就是滤去谐波,提高输出正弦 波的质量。对于不同的输出频率,DAC 输出的等效采样频率也不同,故低通滤波器的截止频 率设计应根据输出频率作相应调整,可进行分段处理。 滤波器设计参考实验一中的实验指导。 (3)电路实现不能使用DDS专用芯片,可以使用分离元件或使用通用FPGA实现。当使用FPGA 实现时又分两种情况,一个是正弦表在FPGA芯片内部,优点是集成度高,缺点是FPGA的门数 多,造价高;另一种是正弦表在FPGA芯片外部,优点是便宜,缺点是电路复杂。

1 LSB 范围内, 2

4.1 单频正弦信号的理想采样: 理想采样把一个采样信号描述为冲激的加权和, 这些加权和等于模拟信号在冲激位置的 值。 一个理想采样信号 xI (t) 可以认为是一个模拟信号 x 数学描述如下:

(t)

和一个周期冲激串 i(t) 的乘积。

x I (t ) = x (t )i (t ) x ,时钟频率为 f c ,

f 0 max ,阻带为 f c − f 0 max ~ ∞ ,即可还原单频信号。但事实上,如果

需要精确的幅度控制,4.2 节讨论的 sinc 函数失真则不能忽略,如果对输出信号的谐波失 真有很高要求,对输出频率较低时,4.3 节讨论的量化的影响不能忽略。

实用信号源的设计和制作

实验指导

信号源的核心就是产生一个频率稳定的周期性信号。 设计一个实用信号源, 可以采用多 种振荡电路来产生周期性信号。例如:用频率合成方法产生振荡信号;利用专用集成函数发 生器(如:ICL8038)产生方波、三角波、正弦波信号;利用直接数字合成(DDS)的方法产 生振荡信号;利用单片机产生信号波形;利用数字比例乘法器(如:CD4527)产生振荡信号。 该实验指导将对直接数字合成(DDS)的方法加以介绍,其它设计方法请参阅参考书。

f 0 min =

fc 2N

(3.3)

输出信号的最大频率为:

f 0 max =

M max × f c 2N

(3.4)

DAC 每信号周期输出的最少点数为:

k=

2N M max

(3.5)

当 N 比较大时, 对于很大范围内的 M 值, DDS系统都可以在一个周期内输出足够的点, 保证输出波形失真很小。 3、 DDS 的各组成部分的具体参数及其相互关系 作为频率信号源,DDS 系统的输出频率范围、频率分辨率、频率稳定度、波形的谐波失 真等是我们主要关心的指标。由于电路复杂性、价格及现有技术条件的限制,我们不可能无 限地提高这些指标,那么这些限制关系是怎样的呢?下面我们做一些简要的分析。 相位累加器的位数 N 、数模转换比特数 n 、时钟频率 f c 及其稳定度、LPF 的特性等 是决定 DDS 系统指标的重要参数。 事实上,我们可以认为DDS系统是模拟信号转化成数字信号的逆过程,即是将单频正弦 模拟信号采样、量化的逆过程。单频正弦模拟信号的频率对应于DDS系统的输出信号频率, 采样频率对应于DDS系统的时钟频率 f c ,量化比特数对应于DDS系统的数模转换比特数 n 。 如果要求DDS的输出频率范围为