FPGA的CIC滤波器的设计要点

数字中频的基本原理和fpga的实现

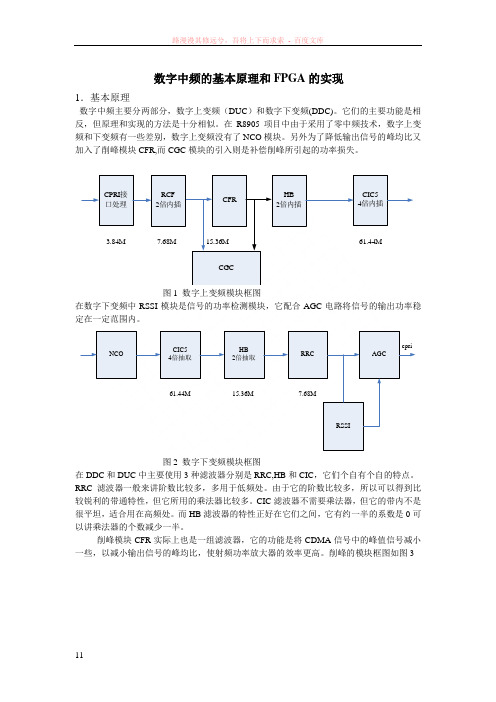

数字中频的基本原理和FPGA的实现1.基本原理数字中频主要分两部分,数字上变频(DUC)和数字下变频(DDC)。

它们的主要功能是相反,但原理和实现的方法是十分相似。

在R8905项目中由于采用了零中频技术,数字上变频和下变频有一些差别,数字上变频没有了NCO模块。

另外为了降低输出信号的峰均比又加入了削峰模块CFR,而CGC模块的引入则是补偿削峰所引起的功率损失。

CPRI接口处理RCF2倍内插HB2倍内插CFRCGCCIC54倍内插3.84M7.68M15.36M61.44M图1 数字上变频模块框图在数字下变频中RSSI模块是信号的功率检测模块,它配合AGC电路将信号的输出功率稳定在一定范围内。

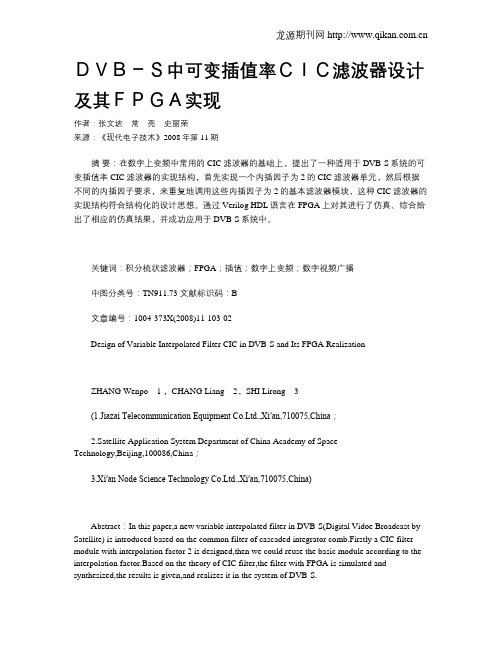

NCOCIC54倍抽取HB2倍抽取RRC AGCRSSI61.44M15.36M7.68Mcpri 图2 数字下变频模块框图在DDC和DUC中主要使用3种滤波器分别是RRC,HB和CIC,它们个自有个自的特点。

RRC滤波器一般来讲阶数比较多,多用于低频处。

由于它的阶数比较多,所以可以得到比较锐利的带通特性,但它所用的乘法器比较多。

CIC滤波器不需要乘法器,但它的带内不是很平坦,适合用在高频处。

而HB滤波器的特性正好在它们之间,它有约一半的系数是0可以讲乘法器的个数减少一半。

削峰模块CFR实际上也是一组滤波器,它的功能是将CDMA信号中的峰值信号减小一些,以减小输出信号的峰均比,使射频功率放大器的效率更高。

削峰的模块框图如图3图3 单级削峰示意图削峰的原理是这样的一个复信号(I,Q)如果它的模大于某个门限,就将其减去这个门限得到一个复信号(dI,dQ),否则(dI,dQ)=(0,0)。

将(dI,dQ)送到fir滤波器中,fir滤波器是一个低通滤波器将峰值限定在一定的带宽内,防止影响临道。

将原信号(I,Q)减去滤波后的信号(fir_i,fir_q)就得到了削峰的值。

如果有必要这这样的削峰可以连续做几次,在R8905设计中削峰用了两次。

基才FPGA的DDC中CIC滤波器的设计

单 级 CIC 滤 波 器 的 频 率 响 应 为 :

H (e )=DM ·Sn(

)·s旷t( )

(2)

式 中 ,Sa(x)=sl 为 抽 样 函 数 ,且 Sa(0)=1,所 以 CIC

滤波 器 在 to=0处 的 幅 值 为 D,即 H(e。)=D 。

0-2 ̄/D的 区 间为 CIC滤 波器 的主瓣 ,而 其 他 区 19成为 旁

XIAO Rui—chuan,LIU Yan—ping,PENG Cheng—gong

(School ofInformation Engineering,Hebei University o f Technology,Tianjin 300401,China)

A bstract:This article describes the design of CIC f ilter based on the signal processing theory.This article f irst ana l yses the theor y and the parameters of the filter.Then design the CIC f ilter meet the system requirements with M atlab.In the end,we carries out the design of the CIC filter with FPGA . Key words:DDC;CIC filter;ISOP filter;FPGA

(4)

单 极 CIC滤 波 器 的旁 瓣 电 平 是 比较 大 的 ,只 比 主 瓣 低

13.46 dB,只 也 就 是 意 味 着 阻 带 衰 减 很 差 ,一 般 难 以 满 足 实 用

Xilinx器件CIC滤波器设计实现

DS613 March 24, 2008

1

Product Specification

CIC Compiler v1.1

Frequency Response Characteristics

The frequency response of a CIC filter is obtained by evaluating Equation 1 at:

implementations • Optional mapping to DSP48/E/A primitives • Synchronous clear input • Clock enable input

General Description

The Xilinx LogicCORETM IP CIC Compiler core v1.1 provides the ability to design and implement Cascaded Integrator-Comb (CIC) filters for a variety of Xilinx FPGA devices. CIC filters, also known as Hogenauer filters, are multi-rate filters often used for implementing large sample rate changes in digital systems. They are typically employed in applications that have a large excess sample rate. That is, the system sample rate is much larger than the bandwidth occupied by the processed signal as in digital down converters (DDCs) and digital up converters (DUCs). Implementations of CIC filters have structures that use only adders, subtractors, and delay elements. These structures make CIC filters appealing for their hardware-efficient implementations of multi-rate filtering.

cic滤波器的fpga实现

cic滤波器的FPGA实现发布时间:2016-01-26 15:07:21技术类别:CPLD/FPGA一、关于多采样率数字滤波器很明显从字面意思上可以理解,多采样率嘛,就是有多个采样率呗。

前面所说的FIR,IIR滤波器都是只有一个采样频率,是固定不变的采样率,然而有些情况下需要不同采样频率下的信号,具体例子我也不解释了,我们大学课本上多速率数字信号处理这一章也都举了不少的例子。

按照传统的速率转换理论,我们要实现采样速率的转换,可以这样做,假如有一个有用的正弦波模拟信号,AD采样速率是f1,现在我需要用到的是采样频率是f2的信号,传统做法是将这个经过f1采样后的信号进行DA转换,再将转换后的模拟信号进行以f2采样频率的抽样,得到采样率为f2的数字信号,至此完成采样频率的转换但是这样的做法不仅麻烦,而且处理不好的话会使信号受到损伤,所以这种思想就被淘汰了,现在我们用到的采样率转换的方法就是抽取与内插的思想。

二、抽取先来总体来解释一下抽取的含义:前面不是说,一个有用的正弦波模拟信号经采样频率为f1的抽样信号抽样后得到了数字信号,很明显这个数字信号序列是在f1频率下得到的,现在,假如我隔几个点抽取一个信号,比如就是5吧,我隔5个点抽取一个信号,是不是就是相当于我采用了1/5倍f1的采样频率对模拟信号进行采样了?所以,抽取的过程就是降低抽样率的过程,但是我们知道,这是在时域的抽样,时域的抽样等于信号在频域波形的周期延拓,周期就是采样频率,所以,为了避免在频域发生频谱混叠,抽样定理也是我们要考虑的因素下面来具体来介绍如上图所示,假如上面就是某一有用信号经采样频率f1抽样得到的频谱,假设这时候的采样频率为8Khz ,可以通过数格子得到,从0到F1处有8个空格,每个空格代表1Khz,有些朋友可能会问,这不是在数字频域吗,单位不是π吗,哪来的hz?是的,这里是数字频域,采样频率F1处对应的是2π,这里只是为了好解释,我们用模拟频率来对应数字频率。

cic滤波器原理详解

级联积分梳状(Cascade Integrator Comb,CIC)[1]滤波器结构简单、标准化,是高速抽取器中十分简单有效的抗混叠滤波单元,已被广泛使用于多抽样率信号处理系统中。

其组成只有积分器、加法器、寄存器,没有乘法器,使得CIC滤波器非常适合在具有较强实时性和并行处理能力的FPGA 上实现。

但是其阻带衰减和通带波纹的相互抑制限制了其滤波性能。

锐化级联积分梳状滤波器[2]、CIC 滤波器的部分锐化[3]、在CIC 滤波器级联分解的基础上级联一级余弦滤波器[4]、二级补偿CIC 滤波器( TSC -CIC)[5]、内插二阶多项式级联积分梳状滤波器(ISOP-CIC)[6]都是用来进行CIC滤波器改进的技术。

但上述CIC 滤波器的改进或只是降低了通带衰减,或只是提高了阻带衰减,或同时降低通带衰减、提高阻带衰减,但是占用硬件逻辑资源较多。

FPGA的CIC滤波器的设计

FPGA的CIC滤波器的设计1.原理概述CIC滤波器由差分器、积分器和组合器三部分组成,可有效实现信号的重采样和滤波功能。

其基本原理是将输入信号通过差分器进行差分运算,然后经过积分器进行累积运算,最后通过组合器实现滤波和重采样。

CIC滤波器的特点是具有高的通带增益和截止频率,且不需要乘法器和存储器,适合在FPGA中实现。

2.设计步骤(1)确定CIC滤波器的设计参数,包括增益因子、积分阶数、截止频率等。

(2)根据设计参数计算滤波器的结构参数,包括输入和输出数据宽度、积分器的阶数和阶间差值等。

(3)根据计算结果,设计CIC滤波器的硬件结构,包括差分器、积分器和组合器的实现方法。

(4) 使用HDL语言(如Verilog或VHDL)编写FPGA的CIC滤波器的代码,同时进行功能仿真和波形仿真。

(5)在FPGA开发板上进行综合、布局布线和验证,实现CIC滤波器的硬件设计。

3.设计关键技术(1)差分器设计:差分器实现差分运算,可以简单采用异或门或加减器实现。

需要注意输入信号的幅度范围和差分器的输出范围。

(2)积分器设计:积分器实现累积运算,需要考虑积分阶数、数据宽度和溢出等问题。

可以采用寄存器与加法器的串行或并行结构实现。

(3)组合器设计:组合器实现滤波和重采样功能,需要根据设计参数确定组合器的截止频率和增益系数。

可以采用多级组合器结构实现。

(4)输入输出接口设计:FPGA的CIC滤波器需要与外部系统进行数据交换,因此需要设计合适的输入输出接口,包括数据接口、时钟接口和控制接口等。

4.实现优化技术(1)折叠积分器:为了减少资源占用和延迟,可以采用折叠积分器结构,将多级积分器合并为一个积分器实现。

(2)级联结构:为了增加滤波器的阶数和降低截止频率,可以采用级联结构,将多个CIC滤波器级联实现。

(3)变系数设计:为了实现可调节的滤波参数,可以设计可变系数的CIC滤波器,在运行时动态调整增益因子和积分阶数。

综上所述,FPGA的CIC滤波器设计是一项复杂的数字信号处理任务,需要深入理解CIC滤波器的原理和设计方法,结合FPGA的硬件实现技术进行设计和优化。

(完整版)CIC滤波器的原理与设计

CIC 的冲击响应{1,010,()n D h n ≤≤-=其他,D 为CIC 滤波器的阶数(即抽取因子),Z 变换后11()1Dz H z z ---=-,当积分梳状滤波器的阶数不等于抽取器的抽取倍数时,令N=DM(N 为滤波器的 阶数,D 为抽取倍数)则积分梳状滤波器的传递函数为:)1(11)(1DM z zz H ----=M 是梳状滤波器中的延时因子,故称M 为差分延时因子;其频率总响应为12()()()jw jw jwH e H e H e ==sin(/2)sin(/2)wDM w =1()()22wDM wDM Sa Sa -⋅⋅x x x Sa /)sin()(=为抽样函数,且1)0(=Sa ,所以CIC 滤波器在0=ω处的幅度值为N ,即:DM e H j =)(0; 一般数字滤波器的指标:()20lg()()20lg ()a pa p a s a s H j H j H j H j ααΩ=ΩΩ=Ω通带最大衰减阻带最小衰减即:CIC 幅频特性响应曲线图由其频率响应函数可以看出其主瓣电平最大为D ,旁瓣电平为21.51()sin(3/2)/sin(3/2)sin(3/2)j DMH e DM DM ωπωπππ=⋅==,旁瓣与主瓣的差值 (用dB 数表示)为: dB A DM s 46.1323lg 20lg201===πα 可计算出旁瓣与主瓣的差值约为13.46,意味着阻带衰减很差,单级级联时旁瓣电平很大,为降低旁瓣电平,增加阻带衰减采用级联的方式,N 级频率响应为:)2()2()()2/sin()2/sin()(ωωωωωQ Q Q Qj Q Sa DM Sa DM DM e H -⋅⋅=⎥⎦⎤⎢⎣⎡=, 可得到N 级CIC 的旁瓣抑制 dB Q Q A DM Q Qs )46.13(23lg 20)lg(201⨯=⋅==πα 分析一下发现在Q 级联时多出了Q DM 这个处理增益,因此分析一下尽量减少带内容差(通带衰减),即,在通带内,幅度应尽量平缓;下面就它的幅平响应曲线来分析:00()20lg ()()20lg()ps j a p jw a j a s jw a H e H eH e H e αα==1、设在红线w1处抽取的信号带宽很窄,为无混叠信号的带宽,能很好的对窄带信号进行滤波,去除掉高频信号噪声;且在绿线w2=2pi/DM-w1处衰减值足够大,则在其信号带宽内,红线到绿线,信号给CIC 滤波器带来的混叠就可以忽略,计算此时阻带衰减:)2/sin()2/sin(lg 20()(lg 2022012w DM w DM e H e H A jw j ==·引入带宽比例因子b=B/(fs/DM ), B 为抽取信号的带宽,D 为抽取因子,M 为延时因子;fs 为输入端采样率,则w1=b*2pi/DM ;带入可化简得:b A lg 201-≈; (假设b=0.01;即fs=100MHz ,D=20,信号带宽为50khz,此时衰减为40dB);可见单级的CIC 滤波器的无混叠信号带宽内的阻带衰减能达到40dB;;并不怎么大,适用于较粗略的滤波,适合放在第一级抽取;如果采用级联的方式可以加大无混叠信号带宽;但是满足的通带不够窄;2、在红线w1处幅度不能下降太多,通带内幅值容差不能太大,否则会引起高频失真;设该带内容差为s δ,则,)()(lg 2010jw j s e H e H =δ将w1带入可简化得)sin(lg 20b bs ππδ≈,当N 级时,其带内容差也会增大;由上面分析可知,阻带衰减和带内容差,只与带宽比例因子b 有关,Df Bb s /=,分析可知,在信号带宽一定的前提下,应尽可能采用小的抽取因子,或增大输入采样率;故一般把它放在抽取系统的第一级,所以在配置CIC 时,信号带宽,采样率,抽取因子,综合考虑,下面是阻带衰减和通带衰减的一个表:表1:大抽取因子下的通带衰减由CIC频幅响应图可以发现,幅频特性的零点位于1/M处(M取值为整数),这说明差分因子M决定了零点的位置;抽取因子D狭定了抽取后信号的采样频率,它同差分延时因子M一起还决定了主瓣和旁瓣的宽度;级数Q可以用来控制阻带衰减,Q越大阻带衰减越大,通带内的混叠就越小,但Q越大,通带内主瓣衰减也越大,所以Q不可太大,不宜超过5级。

高速CIC插值滤波器的位宽与优化

1432012年第09期,第45卷 通 信 技 术 Vol.45,No.09,2012总第249期 Communications Technology No.249,Totally高速CIC 插值滤波器的位宽分析与优化﹡聂 阳, 戈 华, 赵鹏宇(集宁师范学院 物理系,内蒙古 集宁 012000 )【摘 要】分析了级联积分-梳状(CIC,Cascaded Integrator Comb)插值滤波器的位宽增长原因,重点研究了CIC 插值滤波器非等值位宽的数据通路设计。

在此基础上利用Matlab 和Xilinx System Generator 开发工具搭建了电路的系统模型,最后通过现场可编程门阵列(FPGA,Field Programmable Gate Array)完成电路的寄存器传输级(RTL,Register Transfer Level)验证,仿真结果表明电路设计具有很高的有效性和可行性。

【关键词】CIC 插值滤波器;位宽;FPGA 【中图分类号】TN911.7 【文献标识码】A 【文章编号】1002-0802(2012)09-0143-03Analysis and Optimization of High-Speed CIC Interpolation Filter WidthNIE Yang, GE Hua, ZHAO Peng-yu(Dept of Physics, Jining Teachers College, Jining Inner Mongolia 012000, China )【Abstract】This paper analyzes the increase of CIC (Cascaded Integrator Comb) interpolation filter width, and focuses on the data path design of non equivalent width. Based on this and with Matlab and Xilinx System Generator development tools, the system model of the circuit is built up, and finally through FPGA (Field Programmable Gate Array) RTL (Register Transfer Level), the verification of the circuit is completed. And simulation indicates the effectiveness and feasibility of circuit design.【Key words】CIC interpolation filter; width; FPGA0 引言随着现代无线通信中数据传输率的增加,在一个信号处理系统中常常需要不同的采样率处理信号以及不同采样率的信号之间相互转换。

DVB-S中可变插值率CIC滤波器设计及其FPGA实现

DVB-S中可变插值率CIC滤波器设计及其FPGA实现作者:张文坡常亮史丽荣来源:《现代电子技术》2008年第11期摘要:在数字上变频中常用的CIC滤波器的基础上,提出了一种适用于DVB-S系统的可变插值率CIC滤波器的实现结构,首先实现一个内插因子为2的CIC滤波器单元,然后根据不同的内插因子要求,来重复地调用这些内插因子为2的基本滤波器模块,这种CIC滤波器的实现结构符合结构化的设计思想。

通过Verilog HDL语言在FPGA上对其进行了仿真、综合给出了相应的仿真结果,并成功应用于DVB-S系统中。

关键词:积分梳状滤波器;FPGA;插值;数字上变频;数字视频广播中图分类号:TN911.73 文献标识码:B文章编号:1004-373X(2008)11-103-Design of Variable Interpolated Filter CIC in DVB-S and Its FPGA RealizationZHANG We,,(1.Jiazai Telecommunication Equipment Co.Ltd.,Xi′an,710075,China;2.Satellite Application System Department of China Academy of SpaceTechnology,Beijing,100086,China;3.Xi′an Node Science Technology Co.Ltd.,Xi′an,710075,China)Abstract:In this paper,a new variable interpolated filter in DVB-S(Digital Vidoe Broadcast by Satellite) is introduced based on the common filter of cascaded integrator comb.Firstly a CIC filter module with interpolation factor 2 is designed,then we could reuse the basic module according to the interpolation factor.Based on the theory of CIC filter,the filter with FPGA is simulated and synthesized,the results is given,and realizes it in the system of DVB-S.Keywords:CIC;FPGA;interpolation;digital up converter;DVBCIC(Cascaded Integrator Comb)滤波器是现代数字上变频的核心技术,具有简单而高效的结构。

Hogenauer CIC滤波器算法研究及FPGA设计实现

果 4 ( l o ∞ 5 ( O 1 一 Oo ) 一 一 11)

㈨

㈨

∞

+

则 在 计 算 6 4 (l 0 (L O (0 0 一 2山 现 + 一 O 1 )+ O O )一 11 )=

从 上 述 计 算 过 程 , 以 看 出 : 的 运 算 都 是 基 丁 2 可 所有 进 Ⅲ 行 运 算 的 , 果 最 终 的 结 果 在 有 效 范 围 内 , 对 于 中间 过 程 所 如 则

黻 l 号

为

为 了 快 速 准 确 地 设 计 C C滤 波 器 , 常 首二 进 制 补 码 形 式 , 上述 各 数 可 以 表示 为 : ) 故

6 ( l o 一 O1)

仿 真 , 后 利 用 Vei gHD 然 ro L进 行 硬 件 描 述 。在算 法仿 真 中 , l Malb中所 提 供 的 数 据 类 型 与 实 际 数 字 系 统 所 采 用 的 数 制 t a

定 的 参 考 价值 。

关键 词 : C; ta Ve i g; 进 制 补码 ; 据 抽 取 CI Ma lb; rl 二 o 数

中图 分 类 号 : N7 7T 1 2 T 1 . ; N9 17 3

文献标识码 : A

高分解 速率滤波 器的一种非 常有 效的结构 就是 由

H g n u r引 入 的 “ 联 积 分 器 梳 状 ” c sa e itg ao o ea e 级 f cd nertr a

。

,

如下 形 式 :

一

2 1 单 级 C C 滤 波 器 . I

∑ x“ 2

X 一

一

( ) x o

() 1

c 滤 器 两个 本的 节 I 波 是由 基 环 组成, 图1 示, 别 c 如 所 分

CIC滤波器设计

课程设计(论文)说明书题目:CIC滤波器设计院(系):信息与通信学院专业:学生姓名:学号:年月日摘要在数字下变频(DDC)中,CIC ( 级联积分梳状)滤波器起着重要的作用。

它主要用于采样速率的抽取,同时具有低通滤波的作用。

CIC 滤波器的主要特点是,仅利用加法器、减法器和寄存器( 无需乘法器) ,因此占用资源少、实现简单且速度高。

关键词:数字下变频; CIC 抽取滤波器AbstactThe filter of cascaded integr at or comb is becoming more important in the application of digital down converter (DDC) . Firstly , it is used to decimate the sample frequency.Secondly, it can be used as a low pass filter. The CIC filter is a flexible, multiplier-free filter which includes adders,subtracters and registers , so it uses less resorces and can play well in higher frequency . Based on the theory of CIC filter,Key words: DDC; the decim at ion filt er of CIC前言在软件无线电中, 数字下变频器接收经过高速采样的中频数字信号, 将所需的频带下变到基带。

它一般位于信号处理链的前端, 靠近A/ D。

它主要由数字振荡器、数字乘法器、数字滤波器三部分组成。

DDC 中数字滤波器的主要作用是抽取、低通滤波, 一般由FIR 滤波器实现。

但FIR 滤波器需要大量的乘法器, 且一般DDC 中的采样速率很高, 因此FIR滤波器需要工作在很高的频率, 使用资源多、功耗大。

基于FPGA的DDC设计及仿真

基于FPGA的DDC设计及仿真王力;薛红喜【摘要】在软件无线电数字接收机中,从AD前端采集过来的数字信号频率高达72 MHz,如此高的频率使得后端DSP不能直接完成相关的数字信号处理任务。

因此合理的设计基于FPGA的DDC,以降低数字信号频率,方便后端DSP实时完成相关的数字信号处理任务就显得尤为重要。

在很多数字信号处理系统中,数字信号频率是非常高的,而后端数字信号处理器件几乎不能满足系统的实时性要求,此时通过合理的设计DDC就可以解决上述问题。

%In the software radio receiver,the frequency of digital signal which comes from AD front-end is up to 72 MHz.Such a high frequency makes the DSP cannot directly complete digital signal processing tasks.So how to rational design DDC which based FPGA is very important,it can reduce the digital signal frequency,and make the digital signal processing tasks convenient.In many digital signals processing system,the frequency of the Digital signal is very high.The back-end digital signal processors can hardly meet the real-time requirements;the problems above can be resolved through rational design of DDC.【期刊名称】《电子设计工程》【年(卷),期】2012(020)010【总页数】4页(P158-161)【关键词】FPGA;DDC;数字信号处理;软件无线电【作者】王力;薛红喜【作者单位】电子科技大学电子工程学院,四川成都610054;电子科技大学电子工程学院,四川成都610054【正文语种】中文【中图分类】TN492近年来,软件无线电已经成为通信领域一个新的发展方向,数字下变频技术(Digital Down Converter-DDC)是软件无线电的核心技术之一,也是计算量最大的部分[1]。

CIC

CIC设计说明

1.1 MATLAB设计说明

这个CIC滤波器的频率特性,如果上图,上图和梳子比较相似。

所以称为梳状滤波器。

这个是CIC抽取滤波器,如图可以看到,每2个点抽取一个点,达到抽取效果。

这个是CIC内插滤波器,如图可以看到,每2个点插入一个点,达到抽取效果。

1.2 FPGA设计说明

一般在实际应用中,我们多半设计抽取滤波器用的更多,一般抽取滤波器如下所示:

在这里,我们将其中一些参数具体化,设计一个具体参数的CIC滤波器。

我们将这个系统模块话,然后在实际应用的时候,我们只要改变其中的参数就可以了。

系统分为如下三个模块。

模块一的设计:

delay_one(

i_clk,//输入时钟

i_rst,//输入复位信号

i_data,//输入信号

o_data//输出信号

);

模块二的设计:

down(

i_clk,//输入时钟

i_rst,//输入复位信号

i_M, //抽取值

i_data,//输入信号

o_data//输出信号

);

模块三的设计:

delay_M(

i_clk,//输入时钟

i_rst,//输入复位信号

i_data,//输入信号

o_data//输出信号

);

那么其在顶层,我们只要调用这些模块就行了。

其中CIC积分器输出结果如下所示:

系统滤波输出结果如下所示:

可以看到,滤波后的效果。

当改变CIC级数的时候,就能得到不同效果的CIC滤波器。

多级抽取CIC滤波器的VerilogHDL设计

CIC滤波器

? CIC滤波器:

CIC(Cascaded Integral Comb) 抽取滤波器,最初由 Hogenauer提出,因为它结构简单,而且实现时无需乘法器和 系数的存储,是一种简单有效的抽样率转换方法。

? CIC抽取滤波器:

- 原理

CIC抽取滤波器通常是由一个积分梳状滤波器和一个抽取滤 波器级联组合而成,其中,级联的积分梳状滤波器又分为积 分部分和梳状部分。

Y_OUT

13

时序仿真结果图

CLK_GE的时序仿真结果图

RST_GE的时序仿真结果图

14

输入时钟信号

FPGA模块图

clk生成器

输入初始化信号

Reset生成器

输入数据

输出数据

3级CIC抽取滤波器的模块图

15

FPGA设计环境

电脑

下载

FPGA

输出信号

逻辑分析仪

FPGA设计流程图

实际FPGA测试环境

16

N

? ???

CIC抽取滤波器示意图

6

单级/多级CIC滤波器的原理

? 单级CIC抽取滤波器的原理 ? 多级CIC抽取滤波器的原理

单级CIC抽取滤波器示意图

多级CIC抽取滤波器示意图

7

单级CIC抽取滤波器的 Verilog HDL 设计

module cic_single(clk,clk1,reset,x_in,y_out); input clk,clk1,reset;

证明本设计方案的正确性、可行性。

- 处理器: EXCALIBUR ARM - FPGA集成块组件: EPXA4F672C3 - 逻辑单元: 180/16,640 - I/O端口: 21/463

基于FPGA的CIC滤波器设计

摘要在数字下变频(DDC)中,CIC(级联积分梳状)滤波器骑着重要的作用。

它主要用于采样速率的抽取,同时具有低通滤波的作用。

CIC滤波器的主要特点是, 仅利用加法器、减法器和寄存器(无需乘法器) ,因此占用资源少、实现简单且速度高。

本文在分析CIC 滤波器原理的基础上, 用Altera公司的系统级(或算法级)设计工具DSP builder 对CIC滤波器进行了建模、Simulink仿真,并通过Modelsim软件进行RTL级仿真,对CIC滤波器的功能进行了验证。

关键词:CIC滤波器;FPGA;DSP builder ;Modelsim目录引言 (2)1 CIC 抽取器和内插器介绍 (3)2 CIC滤波器理论 (3)2.1 单级CIC滤波器 (3)2.2 多级CIC滤波器 (4)3 Simulink简介 (5)3.1 什么是Simulink (5)3.2 功能 (5)4 DSP builder简介 (6)5 Simulink仿真验证 (8)5.1系统框图 (8)5.2 参数配置 (8)5.3 各模块设置 (9)5.4 仿真结果: (10)6 Dsp builder 模型设计 (11)6.1 系统框图 (11)6.2 DSP builder仿真结果 (15)7 ModelSim仿真(Modelsim 版本为6.3j) (17)7.1 操作步骤 (17)7.2 总结 (20)谢辞 (20)参考文献 (21)引言高分解速率滤波器的一种非常有效的结构就是由Hogenauer引入的“级联积分器梳状”(cascade integrator comb,CIC)滤波器。

CIC滤波器被证明是在告诉抽取或插值系统中非常有效的单元,一种应用就是无线通信,其中以射频或者中频为采样速率的信号需要降低到基带为主。

另一个领域就是数据转换。

为了快速准确地设计CIC滤波器,通常首先是进行算法仿真,然后利用Verilog HDL进行硬件描述。

FPGA的CIC滤波器的设计

FPGA的CIC滤波器的设计CIC滤波器是一种高效的滤波结构,主要用于在数字信号处理中降低采样率。

它的结构包括一个或多个级联的积分器和组合器。

积分器用于对输入信号进行累加,组合器用于将积分结果进行减法运算并输出。

设计FPGA上的CIC滤波器需要以下步骤:1.确定滤波器的规格:首先,你需要确定滤波器的采样率和通带、阻带的频率要求。

这将决定你需要设计多少级的CIC滤波器以及每级的系数。

2.确定滤波器的结构:根据滤波器的规格,你可以确定CIC滤波器的级数和输出信号的截止频率。

CIC滤波器的级数决定了降采样的比率,输出信号的截止频率将决定滤波器的性能。

3.设计CIC滤波器的系数:CIC滤波器的系数由积分器和组合器的阶数决定。

你可以使用公式来计算系数,也可以通过在FPGA上进行仿真来获得最佳的系数。

4. 实现CIC滤波器:一旦你确定了CIC滤波器的系数,你可以开始在FPGA上实现该滤波器。

你可以选择使用HDL (Hardware Description Language) 编写滤波器的代码,也可以使用可视化编程工具来设计滤波器。

5.测试和优化滤波器性能:一旦滤波器被实现,你可以使用测试向量对其进行性能测试。

你可以通过观察输出信号的频谱特性来评估滤波器的效果,并根据需要进行优化。

设计FPGA上的CIC滤波器需要一些基本的信号处理和FPGA编程知识。

你需要熟悉CIC滤波器的原理和性能特点,以及FPGA的编程语言和开发工具。

此外,你还需要掌握一些数字信号处理的基本概念,如离散时间系统、采样定理等。

总结起来,设计FPGA上的CIC滤波器需要先确定滤波器的规格和结构,然后设计滤波器的系数,最后在FPGA上实现并测试滤波器。

这个过程需要一些基本的信号处理和FPGA编程知识,但随着你的实践和学习,你将能够设计出高性能的CIC滤波器。

FPGA的CIC滤波器的设计

FPGA的CIC滤波器的设计CIC滤波器的设计主要涉及滤波器的参数确定、级联结构的设计、数据格式的选择和实现细节。

首先,CIC滤波器的参数包括滤波器阶数、滤波器响应和抽取/插值比例。

滤波器阶数决定了滤波器的截止频率和滤波器的响应速度。

滤波器响应可以是低通、高通或带通响应,根据实际需求选择。

抽取/插值比例决定了滤波器的抽取/插值功能,可以根据需要选择。

其次,CIC滤波器采用级联结构,每个级联包括一个积分器和一个信号延迟器。

级联结构的数量决定了滤波器的阶数,阶数越高滤波器的性能越好。

级联结构还可以根据需求进行扩展或压缩。

然后,对于FPGA的CIC滤波器设计,数据格式的选择非常重要。

常见的数据格式有定点(Fixed-Point)和浮点(Floating-Point)两种。

定点数据格式可以节省硬件资源,但需要进行定点数的运算和溢出处理。

浮点数据格式计算精度高,但需要更多的硬件资源。

根据实际需求选择合适的数据格式。

最后,实现细节包括CIC滤波器的硬件资源分配、时钟分配和时序约束等。

硬件资源分配需要根据滤波器的参数确定所需要的积分器、延迟器和加法器等硬件资源。

时钟分配需要合理分配时钟信号,以满足滤波器的运算速度和性能需求。

时序约束能够帮助设计人员解决时序问题,确保滤波器的正确性和稳定性。

总的来说,FPGA的CIC滤波器设计涉及滤波器参数选择、级联结构设计、数据格式选择和实现细节。

通过合理的设计和优化,可以实现快速、高效的滤波功能,满足各种信号处理需求。

基于FPGA的全数字锁相环的设计与实现

基于FPGA的全数字锁相环的设计与实现一、本文概述本论文聚焦于基于现场可编程门阵列(FieldProgrammable Gate Array, FPGA)技术设计与实现全数字锁相环(AllDigital PhaseLocked Loop, ADPLL)的研究工作。

全数字锁相环作为一种关键的信号处理模块,广泛应用于通信系统、雷达系统、高速数据采集、频率合成等领域,其性能直接影响到整个系统的稳定性和精度。

随着FPGA技术的发展,ADPLL在灵活性、集成度、可编程性及实时调整等方面展现出显著优势,成为现代电子系统中实现高精度频率合成与同步控制的理想选择。

本文旨在深入探讨基于FPGA平台构建全数字锁相环的理论基础、设计方案及关键技术,并通过实际工程实践验证其性能。

研究内容主要涵盖以下几个方面:理论背景与技术综述:对全数字锁相环的基本原理、组成结构以及工作模式进行全面阐述,对比分析其与传统模拟锁相环和混合信号锁相环的优缺点。

在此基础上,详细介绍FPGA技术的特点及其在ADPLL设计中的应用价值,为后续设计工作奠定理论基础。

系统架构与模块设计:详细阐述所设计的基于FPGA的全数字锁相环的整体架构,包括鉴相器(Phase Detector)、数字环路滤波器(Digital Loop Filter)、数控振荡器(Digitally Controlled Oscillator, DCO)等核心组件的设计思路与实现细节。

针对FPGA资源特性,优化各模块算法及硬件实现,确保其在有限逻辑资源下达到高性能指标。

关键算法与技术实现:探讨用于提升ADPLL性能的关键技术,如低噪声鉴相算法、快速锁定策略、频率牵引与抖动抑制技术等,并展示如何将其有效融入FPGA实现中。

同时,阐述如何利用FPGA的可编程特性实现实时参数调整与在线监控,增强系统的动态适应能力和故障诊断能力。

仿真验证与实验结果:通过高级硬件描述语言(HDL)对设计进行建模,并利用FPGA开发环境进行功能仿真与时序分析,验证设计的正确性和稳定性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的CIC数字滤波器的设计摘要:级联积分梳状(Cascade Integrator Comb,CIC)滤波器是数字系统中实现大采样率变化的多速率滤波器,已经证明是在高速抽取和插值系统中非常有效的单元,在数字下变频(DDC)和数字上变频(DUC)系统中有广泛的应用。

它不包含乘法器,只是由加法器,减法器和寄存器组成,而且需要的加法器的数目也减少了许多,因此CIC滤波器比FIR和IIR滤波器更节省资源,并且实现简单而高速。

本文主要讨论了CIC滤波器的基本原理和基于FPGA的仿真实现方法,具体是采用Verilog HDL语言编程,将滤波器分为积分器模块和梳状器模块2个部分,对每个模块进行具体的功能分析和设计实现,最后通过Modelsim 仿真对滤波器的性能进行分析,验证了设计的正确性。

关键词:CIC滤波器;抽取;FPGA;Verilog HDLthe Design of Cascade Integrator Comb Filter Based on FPGAAbstract:CIC (Cascade Integrator Comb, CIC) filter is a digital system to achieve large changes in multi-rate sampling rate filter, which has been proven to be a very effective unit in the high-speed extraction and interpolation system. It is widely used in the digital down conversion (DDC ) and digital up conversion (DUC) systems. It does not contain the multiplier, but just composes by adders, subtractors and registers, and the number of needing adders is reduced a lot. So it takes fewer resources than FIR filter and IIR filter. And the speed of CIC filter is very high and it is also very convenient to realize.This article discusses the basic principles of CIC filter and the simulation way based on FPGA. The modules were described with Verilog HDL. Firstly, the filter was divided into two parts which were integration module and the comb module. Then the function of each module were analyzed and designed. Finally the performance of the filter was analyzed under ModelSim and the correctness of the design was verified. Keywords:CIC filter; Decimation; FPGA; Verilog HDL1. 引言:数字滤波是数字信号分析中最重要的组成部分之一,数字滤波与模拟滤波相比,具有精度和稳定性高,系统函数容易改变,灵活性高,不存在阻抗匹配问题,便于大规模集成,可实现多维滤波等优点。

级联积分梳状(Cascade integrator comb,CIC)滤波器,是由Hogenauer引入的一种非常有效的高分解速率的数字滤波器结构,已经证明是在高速抽取和插值系统中非常有效的单元。

它具有较好的抗混叠和抗镜像性能;它不包含乘法器,只是由加法器,减法器和寄存器组成,而且需要的加法器的数目也减少了许多,因此CIC滤波器比FIR和IIR 滤波器更节省资源,并且实现简单而高速;无需存储滤波器的系数,结构规则易于拓展,无需外部控制,抽取倍数可变,对提高实时性和简化硬件有重要意义。

CIC滤波器的应用范围非常的广泛:由于其具有较好的抗混叠和抗镜像性能,可以实现任意采样率的转换,因此被用在软件无线电接收机中;用于正交多速率调制系统中,但又不仅仅是局限在调制器中,只要CIC滤波器之前或之后有FIR滤波器,对CIC滤波器的通带衰减进行补偿以后,都能够以很小的代价换取最大的硬件资源节省[1];在全数字接收机中的应用,CIC滤波器与HB滤波器共同实现了数字抽取滤波器,从输入的宽带高数据流的数字信号中提取所需的窄带信号,并在低通滤波器的作用下,下变频为数字基带信号[2];在-∆∑ADC中频信号处理模块中的应用,用CIC滤波器来匹配噪声抑制滤波器,并对采样后的数据再进行下采样,以降低噪声和后端硬件成本[3];在无线通信中的应用,如:蜂窝式无限电通信;CIC滤波器由于其结构的独有特性,已经成为了许多新型高性能器件的核心部件。

因此研究它具有很重要的实用意义。

本文是要设计一个基于现场可编程门阵列(FPGA),用Verilog HDL语言编程实现的级联积分梳状(Cascade integrator comb,CIC)数字滤波器。

主要内容包括:架构设计、接口逻辑设计、FSM设计、编码实现、功能仿真等。

2. 设计平台介绍:系统设计需要使用Verilog HDL(Hardware Descriptions Language)、ModelSim 6.0、FPGA(Field Programmable Gates Array)现场可编程门阵列。

2.1 Verilog HDL简介:Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。

被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。

数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

以文本形式来描述数字系统硬件的结构和行为的语言,用它表示逻辑电路图、逻辑表达式以及数字逻辑系统所完成的逻辑功能。

2.2 Modelsim简介:M odelsim仿真工具是Model公司开发的。

它支持Verilog VHDL以及他们的混合仿真,它可以将整个程序分步执行,使设计者直接看到他的程序下一步要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值,可以在Dataflow窗口查看某一单元或模块的输入输出的连续变化等。

ModelSim是业界最优秀的HDL语言仿真器。

它提供最友好的调试环境,是唯一的单内核支持VHDL和Verilog混合仿真的仿真器。

全面支持VHDL和Verilog语言的IEEE 标准,支持C/C++功能调用和调试。

2.3 FPGA简介:现场可编程门阵列FPGA(Field Programmable Gates Array)是近10年加入到用户可编程技术行列中的器件。

现场可编程阵列在器件的选择和内部的互联上提供了更大的自由度。

FPGA的结构类似于掩膜可编程门阵列(MPGA),由逻辑功能块排列成阵列组成,并由可编程的内部连线连接这些逻辑功能块来实现不同的设计[4]。

FPGA是由掩膜可编程门阵列和可编程逻辑器件两者特性结合演变而来的,所以FPGA既具有门阵列的高密度和通用性,又具有可编程逻辑器件的用户可编程特性。

对于ASIC设计,采用FPGA在实现小型化,集成化和高可靠性的同时,还减少了风险,降低了成本,缩短了周期。

2.3.1 FPGA基本原理:FPGA就结构上而言,主要由三个部分主成:可编程逻辑块CLB(Configurable Logic Blocks),可编程输入/输出模块IOB(Input/Output Block),可编程互连资源PIR(Programmable Interconnect Resource)等三种可编程电路。

图1所示为FPGA平面结构示意图[5]。

CLB是实现逻辑功能的基本单元,它们通常规则地排列成一个阵列,散步于整个芯片中;IOB主要完成芯片上的逻辑与外部引脚接口,它们通常排列在芯片的四周;PIR 包括各种长度的连线线段和一些可编程连接开关,它们将各个CLB之间或CLB与IOB 之间以及IOB之间连接起来,构成特定功能的电路。

其中,CLB主要由逻辑函数发生器,触发器,数据选择器等电路组成,逻辑函数发生器主要由查找表LUT(Look Up Table)构成;IOB主要由输入触发器,输入缓存器图1. FPGA的平面结构示意图Fig.1 The schematic diagram of FPGA和输出触发/锁存器,输出缓存器组成,每个IOB控制一个引脚,它们可配置为输入,输出或双向I/O功能;PIR由许多金属线段构成,这些金属线段带有可编程开关,通过自动布线实现各种电路的连接。

2.3.2 FPGA系统设计流程:FPGA系统设计流程包括硬件和软件设计流程。

首先确定系统功能,并对关键部分予以仿真。

在确定系统功能并划分功能块之后,根据不同的结构和算法,确定不同的资源消耗。

由上述过程可以确定系统设计需要消耗的门数,存储器的大小。

根据系统设计要求,对系统时序和时钟率进行考察和估计,可以确定所需器件的速度级别。

根据系统外部接口的要求,确定接口时序和芯片引脚资源消耗情况。

在上述过程完成以后,考虑系统功能和性能的可扩展性,确定器件型号。

型号确定之后,需要确定配置方式,因为不同型号的器件,其配置方式是有很大差异的。

硬件设计和软件设计可以同时进行。

系统设计在经过设计,改进,查错,再设计,再改进,再查错的螺旋型过程后,即可完成系统所有的设计,进入产品生产[6]。

如图2所示为FPGA系统设计流程:图2. FPGA 设计流程Fig.2 The design process of FPGA 3. CIC 滤波器的基本原理:3.1 多速率信号处理原理:所谓多速率信号处理是指改变信号的采样率,实质上是对采样后的离散序列重采样的过程,包括抽取和内插两种情况。

使采样率降低的采样率转换称为抽取;使采样率升高的采样率转换称为内插。

3.1.1 整数倍抽取:整数M 倍抽取是指原始抽样序列x(n)每隔(M-1)个取一个,形成一个新序列XM(n),XM(n)=x(Mn),正整数M 为抽取因子。