第四章 CMOS组合逻辑电路设计I

CMOS组合逻辑门的设计

THANKS

谢谢您的观看

与门

电路结构

CMOS与门由两个或多个反相器串联而成,所有输入都为高 电平时,输出才为高电平。

工作原理

当所有输入都为高电平时,每个反相器都工作在PMOS管导 通、NMOS管截止的状态,输出为低电平;当任意一个输入 为低电平时,相应的反相器工作在PMOS管截止、NMOS管 导通的状态,输出为高电平。

或门

CMOS非门由一个反相器构成,输入与输出相反。

工作原理

当输入为高电平(V<sub>DD)时,PMOS管导通,NMOS管截止,输出为低电平(V<sub>SS); 当输入为低电平(V<sub>SS)时,PMOS管截止,NMOS管导通,输出为高电平(V<sub>DD>) 。

03

CMOS组合逻辑门的性能优化

向着更小的尺度发展,提高集成度和运算速 度。

与其他逻辑门电路不断融合,形成更加复杂 和高效的逻辑功能模块。

发展高速度、高效率、低功耗的CMOS组合 逻辑门是主要趋势。

广泛应用在通信、计算机、消费电子等领域 ,需求驱动发展。

未来研究方向

研究适用于超低功耗应用的 CMOS逻辑门电路。

在更小的特征尺寸下,如何提 高CMOS逻辑门的性能和稳定 性是需要解决的重大问题。

CMOS组合逻辑门可以用于嵌入式系统中的数据处理和控 制操作,提高系统的可靠性和稳定性。

计算机硬件系统

计算机硬件系统是指由各种电子元件、部件和软件组成的计算机结构,包括中央 处理器、内存、输入/输出接口等。

CMOS组合逻辑门可以用于计算机硬件系统中的信号传输和处理,保障系统的稳 定性和高效性。

CMOS组合电路和CMOS基本逻辑电路

Req

Rp

A CL

Rn

B Rn A NAND2

Cint

A

B

晶体管尺寸的确定

当且只有当两个输入 A,B同时为低时输出为 高。最坏情况的下拉 翻转发生在只有一个 NMOS管导通时。

目的:确定NOR门的尺寸,使它的延时近似等于具有以下尺寸的反相器: NMOS = 0.5m/0.25 m;PMOS = 1.5m/0.25 m

(Vtn=-Vtp,μn=2 μp)

19

二、互补CMOS门的传播延时(以NAND2为例)

Rp A

Rn A Rn B NAND2

Rp B CL

内部节点电容:来 自于源漏区及M2和 M1的栅覆盖电容。

Cint

两输入NAND2门等效RC模型

20

开关延时模型

A A Rp A B Rp Rp B Rp A Rn A Cint INV CL Rn Rn CL NOR2

E

CP

CP

34

主从D触发器

1. 电路结构 主锁存器与从锁存器结

构相同 TG1和TG4的工作状态相同 TG2和TG3的工作状态相同

CP 1 D 主锁存器 C TG1 TG C C G1 1 C Q TG3 TG C C 1 G3 Q Q 从锁存器

时PMOS管关断并停止提供放电电流。因此NMOS管适用于PDN中。

7

(2) 推导一组规则来实现逻辑功能

NMOS的串/并联接

Transistors can be thought as a switch controlled by its gate signal NMOS switch closes when switch control input is high

CMOS逻辑电路设计

CMOS逻辑电路设计CMOS(Complementary Metal-Oxide-Semiconductor)逻辑电路是现代集成电路中广泛应用的一种电路结构。

它由N沟道MOS(NMOS)和P沟道MOS(PMOS)互补组成,具有低功耗、高噪声抑制和高速运算等优势。

在本文中,我们将探讨CMOS逻辑电路的设计原理和方法。

一、CMOS逻辑门的基本结构CMOS逻辑门是由一对互补的MOS管组成的。

其中,NMOS管是由N沟道与P+掺杂的互补金属氧化物半导体(CMOS)结构形成,而PMOS管是由P沟道与N+掺杂的CMOS结构形成。

CMOS逻辑电路通过控制这些NMOS管和PMOS管的某些管子通断来实现逻辑运算。

二、CMOS逻辑门的基本原理CMOS逻辑门的基本原理是利用MOS管在开关状态时流过的电流来实现信号的逻辑运算。

当NMOS管的门极接收到高电平信号(逻辑1)时,通常情况下,NMOS管导通,PMOS管截止。

相反,当NMOS 管的门极接收到低电平信号(逻辑0)时,NMOS管截止,PMOS管导通。

通过这种控制逻辑,CMOS逻辑门可以实现与门、或门、非门等基本逻辑运算。

三、CMOS逻辑电路的设计方法在进行CMOS逻辑电路设计时,需要遵循以下步骤:1. 确定逻辑功能:根据所需的逻辑运算,确定需要设计的CMOS逻辑门类型。

2. 绘制逻辑图:根据所需的逻辑功能,用逻辑符号绘制电路的逻辑图。

3. 分析逻辑功能:根据逻辑图,分析逻辑门输入和输出之间的关系,确定每个逻辑门的输入和输出真值表。

4. 选择器件尺寸:根据所需的逻辑门延迟、功耗和面积等要求,选择合适的管子尺寸。

5. 进行布线:根据所选用的管子尺寸,进行电路的布线设计。

6. 进行模拟仿真:使用电路设计软件,进行CMOS逻辑电路的仿真,验证其功能和性能。

7. 进行物理实现:根据设计结果,进行CMOS逻辑电路的物理实现,包括掩膜制作、晶圆制作和封装测试等过程。

四、CMOS逻辑电路的优势与应用CMOS逻辑电路具有以下优势:1. 低功耗:由于CMOS逻辑电路的特殊结构,只有在发生信号变换时才会有较大电流流过。

CMOS组合逻辑门的设计

CMOS组合逻辑门的设计CMOS(互补金属氧化物半导体)是一种集成电路技术,由P型和N型MOS(金属氧化物半导体)组成。

CMOS技术被广泛应用于数字逻辑门的设计中。

本文将详细介绍CMOS组合逻辑门的设计过程。

组合逻辑门是一种不带有存储元件的数字电路,根据输入的状态产生相应的输出状态。

CMOS组合逻辑门由MOS场效应晶体管和电阻组成。

在CMOS技术中,MOS晶体管可以工作在两种模式下:通过模式和截止模式。

通过模式下的晶体管导通,截止模式下的晶体管断开。

CMOS逻辑门的设计过程通常包括以下步骤:1.需求分析:首先确定需要设计的逻辑门的功能和特性。

了解输入输出关系和逻辑表达式。

2.逻辑表达式转换:将逻辑表达式转换为布尔代数表达式。

根据布尔代数原理,使用布尔代数运算符对逻辑表达式进行化简和转化。

3.逻辑电路设计:根据逻辑表达式,使用MOS晶体管和电阻等元件设计逻辑电路。

4.原理图绘制:根据逻辑电路设计,使用电路设计软件绘制电路原理图。

将所需的逻辑门、晶体管和电阻等组件进行布局。

5.模拟仿真:使用电路设计软件进行模拟仿真,验证逻辑门的设计是否正确。

通过输入信号,验证输出信号是否符合逻辑表达式。

6.物理布局设计:根据电路原理图和仿真结果,进行逻辑门的物理布局设计。

确保信号传输的最佳路径和减小电路延迟。

7.版图布线:根据物理布局设计,进行电路的版图布线。

将各个组件进行布线,保证信号传输的稳定性和最短路径。

8.工艺制造:根据版图布线,转化为切割、离子注入或敏感处理等工艺制造步骤。

生产出需要的CMOS逻辑门。

CMOS技术在逻辑门设计中具有许多优点,如低功耗、高集成度、高噪声抑制能力等。

CMOS逻辑门由于其优势得到了广泛应用,如在微处理器、数字信号处理器和存储器中。

总之,CMOS组合逻辑门的设计过程包括需求分析、逻辑表达式转换、逻辑电路设计、原理图绘制、模拟仿真、物理布局设计、版图布线和工艺制造等步骤。

CMOS技术在逻辑门设计中具有优越性能,得到了广泛应用。

cmos逻辑电路

cmos逻辑电路CMOS逻辑电路是数字电路中最重要的一种电路模型,也是在现代电子设备中普遍应用的电路模型之一。

其名称来源于电路中的两种互补金属氧化物半导体材料,即NMOS和PMOS。

CMOS逻辑电路具有如下优点:功耗低、速度快、噪声小、电路面积小、可靠性高等。

CMOS逻辑电路的组成主要分为以下几步:1.设计逻辑簇首先需要设计一个逻辑簇,即将要实现的电路功能模块。

逻辑簇可采用组合逻辑或时序逻辑设计,并进行模拟验证,保证其正确性和合理性。

此时,需要注意逻辑簇中的布局设计,以及电路中各元器件参数的选取和计算。

2.绘制原理图在确定了逻辑簇的设计之后,需要将其绘制成原理图。

在原理图中,将逻辑簇中各个部分表示为电路元器件,如门、触发器、计数器等,并连接它们。

可以使用常见的原理图软件,如Protel、Altium Designer等进行绘制。

3.模拟仿真在绘制好原理图之后,需要对其进行模拟仿真验证。

通过仿真软件对电路进行仿真实验,验证其能否正常工作和实现设计功能,同时检测电路是否存在问题,并进行优化调整。

4.设计布局在完成了逻辑簇的设计和仿真之后,需要进行布局设计。

布局设计包括电路的物理结构布局、板子尺寸、引脚安排等。

此时,需要考虑电路的散热问题,以及元器件之间的信号干扰等问题。

5.制作PCB板经过以上步骤以后,需要将原理图转换成PCB板图进行制作生产。

这一步需要采用常用的PCB板软件进行设计和加工制作,如PADS、ALLEGRO等。

在制作PCB板时,需要考虑工艺和制造难度,以及电路的性能和可靠性。

总之,CMOS逻辑电路的设计和制作需要耐心和细心,要考虑到各种因素,确保电路的稳定性和可靠性。

只有在多方面技能和知识的积累和应用下,才能成功完成CMOS逻辑电路的设计和制作。

cmos组合逻辑

cmos组合逻辑CMOS组合逻辑CMOS组合逻辑是一种基于互补金属氧化物半导体(CMOS)技术的数字逻辑电路。

它由一系列的CMOS门电路组成,用于实现各种逻辑功能,如与门、或门、非门等。

CMOS组合逻辑具有低功耗、高噪声抑制能力和高集成度等优点,因此在现代集成电路设计中得到广泛应用。

CMOS组合逻辑的基本单元是CMOS门电路,它由一个PMOS (P型金属氧化物半导体)和一个NMOS(N型金属氧化物半导体)晶体管组成。

PMOS的源极连接到正电源,NMOS的源极连接到地,两个晶体管的栅极相连,构成了CMOS门电路的输入端,而两个晶体管的漏极相连,构成了CMOS门电路的输出端。

CMOS组合逻辑的输入信号通过CMOS门电路的输入端进入,经过晶体管的驱动,最终输出到CMOS门电路的输出端。

不同的CMOS门电路通过晶体管的连接方式和工作状态的不同,实现了不同的逻辑功能。

与门是CMOS组合逻辑中最简单的一种逻辑门电路,它有两个输入端和一个输出端。

当且仅当两个输入信号同时为高电平时,输出信号才为高电平;否则输出信号为低电平。

与门的输入信号经过NMOS晶体管的驱动,当且仅当两个输入信号同时为高电平时,NMOS晶体管导通,输出端为低电平;否则NMOS晶体管截止,输出端为高电平。

同时,PMOS晶体管的工作状态与NMOS晶体管相反,实现了逻辑功能的与运算。

与门的逻辑功能可以通过串联多个与门电路来实现更复杂的逻辑功能,如与非门、与或非门等。

与非门是由一个与门和一个非门组成的,当且仅当输入信号为低电平时,输出信号为高电平;否则输出信号为低电平。

与非门的输入信号经过与门的驱动,当两个输入信号同时为高电平时,与门的输出为低电平,通过非门的反向作用,最终输出端为高电平。

或门是CMOS组合逻辑中另一种常见的逻辑门电路,它有两个输入端和一个输出端。

当两个输入信号中至少一个为高电平时,输出信号为高电平;否则输出信号为低电平。

或门的实现与与门类似,只是晶体管的连接方式有所不同,通过调整晶体管的工作状态,实现逻辑功能的或运算。

4组合逻辑电路的设计

GDOU-B-11-112广东海洋大学学生实验报告书(学生用表)实验名称组合和逻辑电路的设计课程名称电工学课程号学院(系)专业班级学生姓名学号实验地点实验日期一、实验目的掌握组合逻辑电路的设计与测试方法二、实验原理使用中、小规模集成电路来设计组合电路是最常见的逻辑电路。

设计组合电路的一般步骤如图12-1所示。

图12-1 组合逻辑电路设计流程图根据设计任务要求建立输入、输出变量,并列出真值表。

然后用逻辑代数或卡诺图化简法求出简化的逻辑表达式。

并按实际选用逻辑门类型修改逻辑表达式。

根据简化后的逻辑表达式,画出逻辑图,用器件构成逻辑电路。

最后,用实验来验证设计的正确性。

三、实验设备与器件序号名称型号与规格数量1 直流电源+5V 12 逻辑电平开关3 逻辑电平显示器 14 CC4011(74LS00)、74LS54(CC4085)各25 CC401274LS20) 3四、实验内容(一)、设计要求用“与非”门设计一个三人表决电路。

当三个输入端中有两个或三个为“1”时,输出端才为“1”,即指示灯亮。

(二)、实验要求1、根据控制要求写出真值表和逻辑表达式;2、画出用与非门(学生自选)实现其逻辑功能的逻辑电路图,并交实验指导教师审阅;3、经实验指导教师审阅后,按逻辑电路图接线并带上负载(指示灯),调试电路,应满足设计要求。

五、实验预习要求1、根据实验要求设计组合电路,并根据所给的标准器件画出逻辑图。

2、如何用最简单的方法验证“与或非”门的逻辑功能是否完好?答:与非门,有零出一,双一出零只要将其一端接高电平,另一端来1时出0,来0时出1即可。

或非门反之,将一端接低电平另一端来1出0,来0时出1,即非。

3、“与或非”门中,当某一组与端不用时,应作如何处理?答:对于本实验,可以悬空,也可以置“1”,但是如果是CMOS要接地。

六、实验报告1、根据设计要求,写出实验的设计过程,画出设计的电路图。

2、通过对所设计的电路进行实验测试,记录测试结果。

实验2-CMOS组合逻辑电路设计

数字集成电路-实验2:VTC仿真

反相器:r=3

nand2

Ln=Lp /um

Wn /um

Wp /um

Ln=Lp /um

Wn /um

Wp A=B= /um 0->1

0.8

1*L

0.8

1

2*L

1

1.5

3*L

1.5

2

4*L

2

2.5

5*L

2.5

Vth

A=1, B=0->1

B=1, A=0->1

2பைடு நூலகம்

nand2 输入数据模式与延时之间的关系

数字集成电路-实验2:延时仿真

Ln=Lp /um 0.8

1 1.5 2 2.5

tpHL(ps)

Wn A=B=0- A=1,

/um

>1

B=0->1

1*L

B=1, A=0->1

2*L

3*L

4*L

5*L

A=B=1>0

tpLH (ps)

A=1, B=1->0

B=1, A=0->1

3

组合逻辑传输链的最小延时和尺寸优化

3、根据负载电容和第2级第3级门的特性,设 计X和Y的值,让整个组合逻辑链的延时最小。

已知:第一级反相器尺寸为:

WP/LP=?/?; WN/LN=?/?;

r=3

Vin(V) 2.5

cgn (fF) cgp (fF) C1(fF)

第1级inv的输入电容C1:

C1 (1 r) 1 Cgn 4Cgn

tpLH (ps)

1

1

第2级单个nand2的输入电容C2:

第3级单个nor2的输入电容C3:

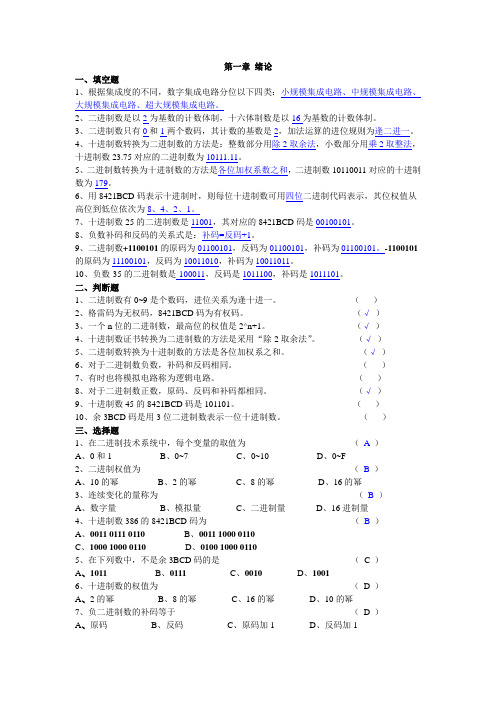

(完整版)数电1-10章自测题及答案(2)

第一章绪论一、填空题1、根据集成度的不同,数字集成电路分位以下四类:小规模集成电路、中规模集成电路、大规模集成电路、超大规模集成电路。

2、二进制数是以2为基数的计数体制,十六体制数是以16为基数的计数体制。

3、二进制数只有0和1两个数码,其计数的基数是2,加法运算的进位规则为逢二进一。

4、十进制数转换为二进制数的方法是:整数部分用除2取余法,小数部分用乘2取整法,十进制数23.75对应的二进制数为10111.11。

5、二进制数转换为十进制数的方法是各位加权系数之和,二进制数10110011对应的十进制数为179。

6、用8421BCD码表示十进制时,则每位十进制数可用四位二进制代码表示,其位权值从高位到低位依次为8、4、2、1。

7、十进制数25的二进制数是11001,其对应的8421BCD码是00100101。

8、负数补码和反码的关系式是:补码=反码+1。

9、二进制数+1100101的原码为01100101,反码为01100101,补码为01100101。

-1100101的原码为11100101,反码为10011010,补码为10011011。

10、负数-35的二进制数是-100011,反码是1011100,补码是1011101。

二、判断题1、二进制数有0~9是个数码,进位关系为逢十进一。

()2、格雷码为无权码,8421BCD码为有权码。

(√)3、一个n位的二进制数,最高位的权值是2^n+1。

(√)4、十进制数证书转换为二进制数的方法是采用“除2取余法”。

(√)5、二进制数转换为十进制数的方法是各位加权系之和。

(√)6、对于二进制数负数,补码和反码相同。

()7、有时也将模拟电路称为逻辑电路。

()8、对于二进制数正数,原码、反码和补码都相同。

(√)9、十进制数45的8421BCD码是101101。

()10、余3BCD码是用3位二进制数表示一位十进制数。

()三、选择题1、在二进制技术系统中,每个变量的取值为(A)A、0和1B、0~7C、0~10D、0~F2、二进制权值为(B )A、10的幂B、2的幂C、8的幂D、16的幂3、连续变化的量称为(B )A、数字量B、模拟量C、二进制量D、16进制量4、十进制数386的8421BCD码为(B)A、0011 0111 0110B、0011 1000 0110C、1000 1000 0110D、0100 1000 01105、在下列数中,不是余3BCD码的是(C )A、1011B、0111C、0010D、10016、十进制数的权值为(D )A、2的幂B、8的幂C、16的幂D、10的幂7、负二进制数的补码等于(D )A、原码B、反码C、原码加1D、反码加18、算术运算的基础是 ( A )A 、加法运算B 、减法运算C 、乘法运算D 、除法运算9、二进制数-1011的补码是 ( D )A 、00100B 、00101C 、10100D 、1010110、二进制数最高有效位(MSB )的含义是 ( A )A 、最大权值B 、最小权值C 、主要有效位D 、中间权值第二章 逻辑代数基础一、填空题1、逻辑代数中三种最基本的逻辑运算是与运算、或运算、非运算。

CMOS组合逻辑门的设计

高噪声容限

CMOS电路对噪声干扰具有较强的 容忍度,因此具有较高的信号完整 性。

高速运行

CMOS电路的开关速度很快,可以 实现较高的工作频率。

低成本

CMOS电路的制作成本较低,并且 可以采用大规模量产的方式,使得 价格更加实惠。

03

CMOS组合逻辑门的设计 要素

输入和输出端口的设计

输入和输出端口是组合逻辑门的接口,需要根据应用需求进行合理设计。

案例四

• 总结词:基于不同输入/输出类型的CMOS门电路设计需要考虑不同的输入/输出类型的特点和限制,以确保 电路的性能和稳定性。

• 详细描述:CMOS门电路可以采用不同的输入/输出类型实现,如TTL、CMOS、ECL等。每种类型都有其特 点和限制,因此需要根据具体需求选择合适的类型。例如,TTL类型具有较高的速度和较低的功耗,但需要 较高的电压;CMOS类型具有较低的功耗和较高的稳定性,但速度较慢;ECL类型具有较高的速度和较低的 功耗,但需要特殊的信号电平。在设计基于不同输入/输出类型的CMOS门电路时,需要考虑这些特点和限 制,以实现最佳的性能和稳定性。

分类

组合逻辑门包括基本逻辑门(AND、OR、NOT)、复杂逻辑门(多输入门、 多输出门)和其他特殊门(如异或门、半加器等)。

组合逻辑门的基本功能

01

02

03

实现逻辑运算

组合逻辑门可以用于实现 各种基本的逻辑运算,如 与、或、非等。

组合逻辑函数

组合逻辑门可以用于实现 组合逻辑函数,即多个输 入决定一个输出的函数。

,实现复杂的逻辑功能。

在实现逻辑功能时,需要考虑电 路的复杂度、时序和功耗等因素

,以优化设计。

性能优化与功耗控制

性能优化是CMOS组合逻辑门设计 的重要环节,包括时序、功耗、面 积等方面。

实验3.2 组合逻辑电路设计1

三、实验设备

数字电路实验箱( 74LS00、74LS86、74LS54、 74LS04数字集成芯片、脉冲源 )、数字万用表、示波器 、导线。

四、实验原理

左边一个半圆小缺口,管脚顺 序是从左下脚逆时针数起。输 入一般用A、B、C… …表示,输 出用Y、F表示

NC(管脚3和11)是空脚,

表示该引出线没有使用。

A B

=1

有“1”出“0” 全“0”出“1” 有“0”出“1” 全“1”出“0” 相同出“0” 不同出“1”

门的控制作用

门电路在使用中常将某一输入端作为控 制端,使该门始终处于“开启”或“关闭” 状态。在集成电路中,经常利用控制端来选 通整个芯片,称为选通端,或称使能端,记 作EN(Enable)。

数字电子技术实验

实验3.2 组合逻辑电路设计1

一、实验目的

1.学习数字电路的集成芯片的使用方法。

2.熟悉组合逻辑电路设计过程。 3.掌握ຫໍສະໝຸດ 门”的控制作用。二、实验任务

1.要求利用一片74LS00芯片(含有4个“与非”门 )设计实现一个“异或”功能的电路。

2.实现自备电站中发电机启停控制电路设计,电路 功能为:某工厂有三个车间和一个自备电站,站内有两台 发电机X和Y,Y的发电量是X的两倍,如果一个车间开工, 启动X就可满足要求;如果两个车间同时开工,启动Y就可 满足要求;若三个车间同时开工,则X和Y都应启动,试设 计一个用“异或”门(74LS86)控制X 、“与或非”门( 74LS54)及“非”门(74LS04)芯片控制Y的启停电路。

不可在接通电源的情况下插入或拔出芯片。

TTL集成块输出不允许并联(“线与”)使用,(集电 极开路门(OC门)和三态门电路除外)。否则会使电路 逻辑功能混乱,严重时串联形成大电流会导致器件损 坏。 加入输入波形时,可利用主箱最下面的脉冲源得到 输入波形。但要使该脉冲源工作,必须接入+5V电源打 开。如果脉冲源坏了,可用信号发生器“TTL/CMOS” 电平端口送出脉冲信号。注意仪器共地。

加法器、比较器

74LS85逻辑表达式

Y( A B ) A3 B3 ( A3 B3 ) A2 B2 ( A3 B3 ) ( A2 B2 ) A1 B1 ( A3 B3 ) ( A2 B2 ) ( A1 B1 ) A0 B0 (A3 B 3 ) (A 2 B 2 ) (A1 B1 ) A 0 B 0 ) I ( A B )

1位数值比较器

设A>B时L1=1;A<B时L2=1;A=B时L3=1。 得1位数值比较器的真值表。

A 0 0 1 1

B 0 1 0 1

L1 (A>B) 0 0 1 0

L2 (A<B) 0 1 0 0

L3 (A=B) 1 0 0 1

逻 辑 表 达 式

L1 AB L2 A B L3 A B AB A B AB

VCC B2 A2 S2 B3 A3 S3 C3 16 15 14 13 12 11 10 9 74LS283 1 2 3 4 5 6 7 8 S1 B1 A1 S0 B0 A0 C0-1 GND TTL 加法器 74LS283 引脚图

V DD B3 C3 S3 S2 S1 S0 C0-1 16 15 14 13 12 11 10 9 4008 1 2 3 4 5 6 7 8 A3 B2 A2 B1 A1 B0 A0 VSS CMOS 加法器 5、4.26、2.27

《数字电子技术基础》(第五版) 清华大学自动化系 阎石 王红

第四章 组合逻辑电路

4.3.5 数值比较器

一 1位数值比较器

二 4位数值比较器

三 数值比较器的位数扩展

本节小结

比较器:用来完成两个二进制数的大小比较的逻辑 电路称为数值比较器,简称比较器。

第四章 组合逻辑

L=A· C+BC 可见:A和B都为1时,电路存在干扰。

竞争:门的两个输入信号同时向相反方向变化, 而变化时间有差异的现象。 冒险:由竞争而可能使输出产生干扰脉冲的现象。

——有竞争不一定有冒险现象。

二、消去竞争冒险的方法

由上分析可见:当电路中存在由反相器产生的 互补信号(乘和加),且在互补信号的状态发生变 化时可能出现冒险现象。对此,可采取以下措施: 1、发现并消掉互补变量

幻灯片 54

B3 B2 B1 B0

从上逻辑表达式可看出,用异或门比用与门和或 门能使电路比较简单。在化简与变换中,使各式中相 同的项尽可能多,可减少门电路的数目。该电路可以 采用1片含四个CMOS异或门74HC86实现。

4· 组合逻辑电路中的竞争冒险 3

竞争冒险现象: ——由于从输入到输出的过程中,不同通路上门的 级数不同,或者门电路平均延时的差异,使信 号从输入经不同通路传输到输出级的时间不同。 由于这个原因,在信号变化瞬间,可能会使逻 辑电路产生错误输出。这种现象称为竞争冒险。

编码器的工作原理: (1) 普通编码器(4线-2线编码器) ——4个输入信号,2位二进制码输出的编码器

功能表:

输入 I0 1 0 0 0 I1 0 1 0 0 I2 0 0 1 0 I3 0 0 0 1 Y1 0 0 1 1

输出 Y0 0 1 0 1

Y1 = I0 I1 I 2 I3 + I0 I1 I 2 I3 Y0 = I 0 I1 I 2 I 3 + I 0 I1 I 2 I 3

冗余项

当A=B=1时,原来存在互补变量C+C ,加了冗余 项后,L=1,消除了干扰脉冲。

3、输出端并接电容器

Ro C

对图4.3.3电路输出 波形,负冲受抑

cmos组合逻辑

cmos组合逻辑摘要:1.CMOS组合逻辑简介2.CMOS组合逻辑的优势3.CMOS组合逻辑的应用4.设计CMOS组合逻辑的步骤5.举例:如何设计一个简单的CMOS组合逻辑电路6.未来发展趋势和挑战正文:CMOS组合逻辑是计算机系统中不可或缺的一部分,它用于实现各种逻辑功能。

CMOS组合逻辑以其低功耗、高噪声容限和低成本等优势在电子领域广泛应用。

本文将介绍CMOS组合逻辑的基本概念、设计方法和实例。

一、CMOS组合逻辑简介CMOS(互补金属氧化物半导体)是一种制造技术,用于制造集成电路。

在组合逻辑电路中,CMOS技术可以实现逻辑门、触发器等基本元件。

CMOS 组合逻辑电路主要包括逻辑门、触发器、寄存器、计数器等部件,这些部件通过互连实现各种逻辑功能。

二、CMOS组合逻辑的优势1.低功耗:CMOS电路在静态和动态功耗方面都表现出较低的功耗,有利于实现节能型电子设备。

2.高噪声容限:CMOS电路具有较高的噪声容限,能在恶劣环境下稳定工作。

3.低成本:CMOS工艺制造成本相对较低,有利于降低电子产品整体成本。

4.集成度高:CMOS技术可以实现高密度的集成电路,提高电子设备的性能。

三、CMOS组合逻辑的应用CMOS组合逻辑广泛应用于计算机、通信、嵌入式等领域。

如:1.计算机:CPU、北桥、南桥等芯片中的逻辑部分;2.通信:数字信号处理、基带处理、信道编解码等;3.嵌入式:微控制器、FPGA、ASIC等。

四、设计CMOS组合逻辑的步骤1.确定设计需求:明确逻辑功能和性能指标;2.设计原理图:画出逻辑电路的原理图,包括逻辑门、触发器等;3.化简逻辑:使用布尔代数或卡诺图化简逻辑表达式;4.布局布线:根据设计要求进行布局布线;5.仿真验证:对设计进行仿真验证,检查是否满足性能指标;6.制作掩膜:根据设计布局制作掩膜,进行集成电路制造。

五、举例:如何设计一个简单的CMOS组合逻辑电路假设我们需要设计一个实现异或(XOR)功能的CMOS组合逻辑电路。

数字电子电路与逻辑 刘可文主编 第四章 集成逻辑门电路 答案

习题44-1 电路如图题4.1所示,写出输出L 的表达式。

设电路中各元件参数满足使三极管处于饱和及截止的条件。

BL D D (a)CC(c)1233(d)图题4.14-1 解:(a )此电路由两级逻辑门构成,第一级是与门,输出为AB ;第二级是或门,输出为: L 1=AB +C(b )此电路是只有一个输入端的逻辑电路。

当输入端A 为低电平时,T 1发射结导通,V B1<2.1V ,D 、T 2截止,L 2输出高电平;当输入端A 为高电平时,T 1发射结不通,+V CC 足以使D 、T 2导通,L 2输出低电平。

由以上分析可见:A L =2(c )此电路有两个输入端,可以分几种情况讨论其工作过程:当输入A 、B 均为低电平时,T 1、T 2都截止,L 3以下部分的支路不通,输出高电平;当输入A 、B 一高一低时,T 1、T 2中有一个截止,L 3以下部分的支路仍不通,输出高电平;当输入A 、B 均为高电平时,T 1、T 2都饱和导通,L 3以下部分的支路导通,输出低电平。

根据以上分析可以列出真值表如表解2.1。

由真值表可得表达式:AB B A B A B A L =++=3(d )此电路有两个输入端,可以分几种情况讨论其工作过程:当输入A 、B 均为低电平时,T 1、T 2都截止,L 4以下部分的支路不通,输出高电平;当输入A 、B 一高一低时,T 1、T 2中有一个饱和导通,L 4以下部分的支路导通,输出低电平;当输入A 、B 均为高电平时,T 1、T 2都饱和导通,L 4以下部分的支路导通,输出低电平。

根据以上分析可以列出真值表如表解4.1。

由真值表可得表达式:B A B A L +=⋅=44-2 为什么说TTL 与非门的输入端在以下4种接法下都属于逻辑0:(1)输入端接地;(2)输入端接低于0.8V 的电源;(3)输入端接同类与非门的输出低电压0.3V ;(4)输入端通过200Ω的电阻接地。

第4单元 集成逻辑门电路和组合逻辑门电路

1、NMOS非门

+UDD R

d g

Ui

s

当Ui为低电平,截止,Uo为高电平 Uo 当Ui为高电平,导通,Uo为低电平

第四单元 集成逻辑门电路和组合逻辑门电路

2、CMOS门电路

CMOS门电路是由N沟道MOS管和P沟道MOS管互补而成。

CMOS非门逻辑关系:

VVDDDD

当Vi为低电平时,VN截止,VP导通。 VO≈VDD,输出为高电平。

功能: 二进制码

一组高低电平

以2/4译码器为例,熟悉译码器的设计过程和工作原理。

B 二进制码

A

2—4 线 译码器

E 使能端

Y0

Y1 一组高低电平 Y2

Y3

第四单元 集成逻辑门电路和组合逻辑门电路

3/ 8译码器

数 据 输出

U cc Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6

16 15 14 13 12 11 10 9

编码器是把 信号转换为二进制码 的组合逻辑电路。 功能: 一组高低电平 二进制码

以8421BCD编码器为例,熟悉编码器的设计过程和工作原理。

Y0

Y1

编

一组

Y2

码

高低电平

器

Y9

D C

二进制代码

B (8421BCD) A

第四单元 集成逻辑门电路和组合逻辑门电路

二、译码器

与编码器功能相反的逻辑电路就是译码器。 编码器是把 二进制码 转换 信号 为的组合逻辑电路。

组成:门电路,不存在记忆元件

数

例如:编码器、译码器、数据选择器等

字

电 路

当前的输入 功能:输出取决于

原来的状态

(第七讲)第4章 组合逻辑电路(2)

而四选一数据选择器输出信号的表达式

Y m0 D0 m1 D1 m2 D2 m3 D3

将A、B作为地址输入变量并比较L和Y可得

D0 C、D1 C、D2 0、D3 1

38

画出如图所示的逻辑电路图。

39

4.5.3 数据分配器

数据分配器能把一个输入端信号根据需要分配给 多路输出中的某一路输出。它的作用实际上相当于 一个多个输出的单刀多掷开关。其示意图如图所示 。

13

解:对图进行分析,可知:该 图将高位片的EO接 低位片的EI。当高位片输入端无有效信号输入时, EO=0,使低位片的EI=0,则低位片可以输入信号。 当高位片有有效信号输入时,EO=1,使低位片的 EI=1,禁止低位片工作。 设13有输入信号,因13输入端为高位片的5脚, 此时对应的高位片编码A2A1A0为010、EO=1、 CS=0,低位片的EI=EO=1,所以不工作,此时对应 的低位片输出A2A1A0为111、CS=1、EO=1。所以 A3A2A1A0=0010。

16

4.4.2二进制译码器

二进制译码器通常有n个输入端,2n个输出端,并 且每一个输出端对应一个n个输入端组成的最小项。 常见的MSI集成译码器有2线-4线、3线-8线和4线-16 线译码器。

17

由真值表(P88)可得输出逻辑函数表达式:

Y0 A2 A1 A0 Y4 A2 A1 A0

Y1 A2 A1 A0

(2)由于译码器74LS138的各输出端为最小项的 非,故将上式转化为以下形式:

F ( A, B, C ) m3 m6 m7 m3 m6 m7 Y3 Y6 Y7

22

(3)由上式可画出该函数的逻辑电路图如图所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第四章CMOS组合逻辑电路设计I -静态CMOS逻辑门电路第一节互补CMOS逻辑门的结构及性能第二节互补CMOS逻辑门的设计第三节类NMOS电路(有比电路)第四节传输门逻辑电路第五节差分CMOS逻辑电路(有比电路)第一节静态互补CMOS逻辑电路的结构及性能一、静态CMOS逻辑电路的结构二、静态CMOS逻辑电路的性能A B CV DDYFFF=(BA C,,)P MOSNMOS一、静态CMOS逻辑电路的结构PUNPDNPUN:pull up net上拉网络PMOSPDN:pull down net下拉网络NMOSPUN、PDN为双重网络设计时需保证,无论什么输入,仅有一个网络在稳定状态下导通。

静态CMOS 逻辑门特点1)带“非”的逻辑功能input: x1,x2, (x)output: 2)逻辑函数F(x1,x2,……,xn)决定于管子的连接关系。

NMOS :PMOS :串与并或串或并与),2,1(Xn X X F Y ⋅⋅⋅=3)每个输入信号同时接一个NMOS 管和一个PMOS 管的栅极, n 输入逻辑门有2n 个管子。

4)静态CMOS 逻辑门保持了CMOS 反相器无比电路的优点。

高噪声容限,VOH 、VOL 分别为VDD 和GNDABA + BA BA • BNMOS串与并或F1F2F1F2F =F1F2+F =F1F2A BCF =A B CABCF =A B C++A B A • BA BA B F001011101110AB例:CMOS与非门A •B = A + B[!(A • B) = !A + !B or!(A & B) = !A | !B]A +B = A • B[!(A + B) = !A • !B or !(A | B) = !A & !B]例:CMOS 或非门A + BAB A B F 00101010011ABA BExample:Y=A(B+C)+DY=A(B+C)+DY=A(B+C)+DAAAB B BCCCDDDV DD二、静态CMOS 逻辑电路的性能高噪声容限:V OH 、V OL 分别为VDD 和GND ,输出电平与器件尺寸无关,无比电路 无静态功耗:VDD 和GND (VSS )之间没有直流通路 在合适的设计时上升、下降时间几乎相同通常空穴迁移率<电子迁移率,需要根据μn/μp 将pMOS 的尺寸加宽 在复杂的组合逻辑门中,性能与输入信号的具体情况有关,即PUN 、PDN 中的电阻是输入信号的函数,分析难度加大,通常分析最坏情况,可以用等效反相器及开关模型去分析。

AR eqAR pAR n C LAC LB R nAR p BR pAR nC intBR pAR p AR n BR n C LC intNAND2INVNOR2开关模型例CMOS 与非门的分析ABY V DDA BYA B Y 000001111111=A .BM M M N1M N2P2P1直流电压传输特性使用等效反相器方法分析分两种情况:1. 两个输入信号同步2. 两个输入信号不同步注意:对不同输入状态,等效反相器参数不同。

C LB R n AR p BR pAR n C int1. 两个输入信号同步212121P P Peff N N N N NeffK K K K K K K K +=+∙=V DDV DDV V outV out K K K K K K PPPNNN eff eff =2=K K N inV inP P/ 2effT P DD eff T N V V V it V ββ+++=1)(()02/244ββ====NP N P Neff P eff K K K K K K eff 同步情况下逻辑阈值电平021)(2ββ+++=T P DD T N V V V it V2. 两个输入信号不同步B 固定在V DD ,Y 随A 的关系A 固定在V DD ,Y 随B 的关系等效反相器022ββ===N P NeffPeff eff K K K K 0021)(2ββ+++=T P DD T N V V V it V二输入与非门的直流电压传输特性A B A • BA B由于衬底偏置效应使M2的阈值大于M1的M2M1ABn 输入与非门2ββn NeffP eff K K eff ==n 个信号输入同步时n 个信号输入不完全同步时有(n -1)种情况peff p K nK =/Neff N K K n=n 输入与非门的直流电压传输特性DDn NHM DD NLM V v V V v V ⋅-=⋅=)1(100001)1(1)1(1βαβαβαβαn n n n n P N P N v v +-++-+==K 导电因子βo CMOS 比例因子12eff oxWK C Lμ=/K K β=归一电平TDDV V α=噪声容限小于V DD /2瞬态特性近似估算:t PHL t PLH()/LDDeff fall rise C mV βM 常数,一般为2-4()/eff fall rise βPUN 或PDN 的有效比例因子CL 门可见的负载电容:•门自加载的,由门中MOSFET 尺寸定•连接门的MOSFET 的尺寸和数量•门和它驱动的门之间的连线电容RC LRC电路的延迟若电路中只有R和C并在输入端加阶跃信号0.69RC•延迟和输入信号相关•Low -high 变化–两个输入同时变低•t pLH -0.69 R p /2 C L–只有一个输入变低•t pLH -0.69 R p C L•High -low 变化•两个输入同时变高•t pLH -0.69 2R n C LC LB R n AR p BR p AR n C intNAND 的延迟估计1t RCoutDD V V e -⎛⎫=- ⎪⎝⎭第二节互补CMOS逻辑门的设计一、电路和版图设计二、组合逻辑门的优化设计三、常见的组合逻辑电路一、电路和版图设计先设计PDN 串与并或利用子单元间的关系得到PUN 串或并与F=A(B+C)+D+baoutba outVDDGND tub ties版图设计NAND的版图版图设计NOR的版图baouta boutVDDGNDtub ties组合逻辑门的版图设计方法:1、画图(n 图和p 图)-2、找欧拉通路-3、求有相同标记的p 和n 欧拉通路-4、若找不到满足3的通路,则用单独的欧拉通路以达到3的要求。

(标记每个点上栅信号标号的次序)目标:将门以最少的端点数目实现连接1、画图把CMOS 电路图变换成符号图每个点对应与一条源漏连线每个边对应与一MOSFET ,可以用对应的栅信号命名nMOS 和pMOS 分别对应两个图,n 图和p 图反映了MOSFET 的连接若两条边是相接的,则可共享一个源漏连线并可合并对接3、求有相同标记的p和n欧拉通路2、找欧拉通路若p图和n图中都存在着包含所有边的一个序列,则该序列称为欧拉(Euler)通路,并且该序列的标记相同,,则这个门可以设计成不间断的扩散行。

Euler path: a path through all nodes in the graph suchthat each edge is visited once and only once. 一笔画jV DDXX iGNDABCC ABX = !(C • (A + B))BACijA B C例PDNPUNC ABX = !(C • (A + B))BACijjV DDXX iGNDABCPUNPDNA B Cj V DDXXiGNDABCA B C相同标记的欧拉通路有些电路找不到相同标记的欧拉通路x = !(a + bc + de)A B CXVDD GNDSingle-Line-of-Diffusion LayoutCA BX = !(C • (A + B)) BACijStick DiagramsC •(A + B)XCABABCXV DDGNDV DDGND Single-Line-of-Diffusion LayoutDiffusionsV DDXXGNDABCPUNPDNDC ABX = !((A+B)•(C+D))BA DC D A B C DBA DVDDGND CXCA BX = !((A+B)•(C+D))BADCDABCDxabcd V DDxxabcdV DDx(a b c d }cd x V DDGNDb c d }bx = ab+cd二、组合逻辑门的优化设计1.减小面积优化设计2. 提高噪声容限3. 提高速度CMOS与非门、或非门设计可能的设计方法1.减小面积所有管子取相同尺寸-没有考虑μp< μn,Rp=2Rn=2R,N输入NAND和N输入NOR的总面积在2nWL的量级,N输入NAND N输入NORtPLH=0.69RpCL=2x0.69RCL tPLH=0.69NRpCL=2x0.69NRpCL tPHL=0.69NRnCL=Nx0.69RCL tPLH=0.69RnCL=0.69RCL NAND的速度更快一些!2. 使NMOS管和PMOS管有相同的导电因子K N=K P, W P=2W N 考虑了μp< μn,W P=2W N,Rp=Rn=R,N输入NAND和N输入NOR的总面积在3NWL的量级,N输入NAND N输入NORtPLH=0.69RpCL=0.69RCL tPLH=0.69nRpCL=Nx0.69RCL tPHL=0.69NRnCL=Nx0.69RCL tPLH=0.69RnCL=0.69RCL 高、低电平传输延迟时间不对称CMOS与非门、或非门设计可能的设计方法3. 取串联管子增大n倍的设计n输入NAND ,NMOS串联n输入NOR PMOS串联WN=nW,WP=W WP=nW,WN=WA=(n2+n)WL A=(n2+n)WLtPLH=0.69RpCL=2x0.69RCL tPLH=0.69nRpCL=2x0.69RCL tPHL=0.69nRnCL=0.69RCL tPLH=0.69RnCL=0.69RCL 高、低电平传输延迟时间不对称,但速度改善了4. 全对称设计KNeff =KPeffn输入NAND ,NMOS串联n输入NOR PMOS串联WN=nW,WP=2W WP=n2W,WN=WA=(n2+2n)WL A=(2n2+n)WLtPLH=0.69RpCL=0.69RCL tPLH=0.69nRpCL=0.69RCL tPHL=0.69nRnCL=0.69RCL tPLH=0.69RnCL=0.69RCL 高、低电平传输延迟时间对称,速度改善,但与非门较或非门省面积尽可能使用与非门!!!DABCDABC 12224488OUT = D + A • (B + C)逻辑门的扇入和扇出扇入fan in-门的输入路径的数目扇出fan out-被该逻辑门的输出驱动的输入门的数目逻辑门的延迟时扇入和扇出的函数DC B A DC B A C LC 3C 2C 1可以近似采用分布电容模型t pHL = 0.69 R eqn (C 1+2C 2+3C 3+4C L )最坏情况下,延迟随扇入的增加,呈平方律地增加扇入的考虑fan in通常应该避免扇入大于4的逻辑门MOSFET 尺寸的影响DABCDABC 12224488OUT = D + A • (B + C)增大MOSFET 的W/L 增大充放电电流加大寄生电容提高速度的方法IIn NC LC 3C 2C 1In 1In 2In 3M1M2M3MNM1 > M2 > M3 > … > MN 离输出越近的MOSFET 尺寸越小!大扇入时,M1必须传送总电容(C1+C2+…+CL )放电电流,因此顺序安排M1-MN 的尺寸使之递减,有助于提高速度按大小排列晶体管以优化延迟DC B AC 3C 2C 144444567提高速度的方法II•合理安排输入信号的顺序–当所有的输入信号不是同时到达时关键信号-所有输入信号中最后稳定的信号关键路径-决定逻辑电路速度的路径,一般是关键信号所控制的路径使关键路径的晶体管靠近逻辑门的输出可以加快速度C 2C 1In 1In 2In 3M1M2M3CLC 2C 1In 3In 2In 1M1M2M3CLcritical pathcritical path 10→11110→1charged charged 提高速度的方法II使关键路径的晶体管靠近逻辑门的输出可以加快速度延迟取决于CL +C1+C2的放电延迟取决于CL 的放电提高速度的方法III •改变门的逻辑设计F = ABCDEFGH✓尽可能使用与非门,特别是在高速电路中✓通常应该避免扇入大于4的逻辑门✓合理安排尺寸,离输出越近的MOSFET尺寸越小✓合理安排顺序,使关键路径的晶体管靠近逻辑门的输出✓在高扇入和大输出间,增加逻辑级数或缓冲,使各级的effort (h)大致相同V DDAA C C BBDDYY=AB+CD三、常见的组合逻辑电路与-或-非门AOI。