芯片引脚定义翻译

c101芯片引脚定义

c101芯片引脚定义

C101芯片引脚定义:

C101芯片是一种具有多种功能的集成电路芯片。

它具有多个引脚,每个引脚都有其特定的功能和定义。

以下是C101芯片常见的引脚定义:

1. 电源引脚(VCC):用于提供芯片运行所需的正电源电压。

一般连接到电源正极。

2. 地引脚(GND):提供芯片的电流回路和参考零电位。

一般连接到电源负极或地线。

3. 数据输入引脚(DIN):用于接收输入信号的数字数据。

数据通过这个引脚输入芯片。

4. 数据输出引脚(DOUT):用于输出处理过的数据信号。

芯片处理完输入数据后,通过这个引脚输出结果。

5. 时钟引脚(CLK):控制芯片内部操作和数据传输的时序。

一般由外部提供时钟信号。

6. 复位引脚(RESET):用于将芯片复位到初始状态。

通过给这个引脚提供一个特定的电平来复位芯片。

7. 中断引脚(INT):用于通知外部设备或处理器发生了某个特定事件。

当特定条件满足时,引脚会发出中断信号。

8. 供电引脚(VDD):用于提供芯片的工作电压。

这些是C101芯片常见的引脚定义,不同芯片可能有不同的引脚功能和定义。

在使用C101芯片时,需要根据具体应用需求按照数据手册或技术规格说明书来正确设置和使用各个引脚。

这些引脚的正确连接和配置将决定芯片的功能和性能。

六脚电源芯片引脚功能

六脚电源芯片引脚功能

六脚电源芯片是一种常见的电源管理芯片,它主要用于提供电源管理功能以保护电路和电子设备。

六脚电源芯片的引脚功能如下:

1. VIN引脚:VIN引脚是电源输入引脚,用于接入电源输入。

该引脚通常连接到电源轨上,例如电池或外部电源。

2. GND引脚:GND引脚是地引脚,用于连接到电路的地节点。

通常,GND引脚与VIN引脚之间应具有低阻抗路径,以确保

电流的返回路径。

3. VOUT引脚:VOUT引脚是电源输出引脚,用于提供电路所需的稳定电压。

该引脚经过稳压电路处理,以确保输出电压稳定在预定范围内。

4. EN引脚:EN引脚是使能引脚,用于控制芯片的启用或禁用。

当EN引脚保持高电平时,芯片处于启用状态;当EN引

脚保持低电平时,芯片处于禁用状态。

5. PG引脚:PG引脚是电源好引脚,用于指示电源输出是否正常。

当输出电压在合理范围内时,PG引脚会产生一个高电平

信号,否则会产生一个低电平信号。

6. BIAS引脚:BIAS引脚是芯片的参考电压引脚,用于提供其他电路模块所需的参考电压。

通常情况下,BIAS引脚需要外

部连接一个适当的电压源。

六脚电源芯片的引脚功能在不同的芯片上可能会有所差异,具体功能取决于芯片的设计和厂商的设定。

但总体来说,这些引脚在电源管理中起着关键的作用,用于保证电路的稳定工作和电源的有效管理。

为了正确使用六脚电源芯片,用户需要仔细阅读芯片的数据手册,并根据实际需求正确连接每个引脚。

此外,还需要注意芯片的额定和限制条件,以确保芯片能够在规定的环境下安全稳定地工作。

博士40211芯片引脚定义

博士40211芯片引脚定义

博士40211芯片引脚定义是指博士40211芯片所使用的引脚的功能和定义。

引脚定义对于芯片的正确连接和使用非常重要。

博士40211芯片具有多个引脚,每个引脚都具有特定的功能。

以下是一些常见的博士40211芯片引脚定义:

1. 电源引脚:博士40211芯片需要提供电源来正常工作。

通常有VCC(电源正极)和GND(地)引脚。

2. 输入引脚:博士40211芯片用于接收外部信号的引脚。

输入引脚通常标记为INx,其中x表示引脚的编号。

3. 输出引脚:博士40211芯片用于输出信号的引脚。

输出引脚通常标记为OUTx,其中x表示引脚的编号。

4. 时钟引脚:博士40211芯片通常需要一个时钟信号来同步其内部操作。

时钟引脚通常标记为CLK。

5. 复位引脚:博士40211芯片可能具有一个复位引脚,用于重置芯片的内部状态。

复位引脚通常标记为RESET。

6. 地址引脚:博士40211芯片可能具有一些地址引脚,用于选择芯片的特定功能或配置。

地址引脚通常标记为ADDRx,其中x表示引脚的编号。

这些只是一些常见的博士40211芯片引脚定义示例,实际上,具体的引脚定义可能会因芯片的制造商和用途而有所不同。

因此,在使用博士40211芯片时,建议查阅相关的数据手册或技术规格以获取准确的引脚定义信息。

理解博士40211芯片引脚定义对于正确连接和配置博士40211芯片非常重要。

正确使用芯片的引脚定义可以确保芯片的正常工作,并满足特定的应用需求。

inter fpga芯片引脚定义

inter fpga芯片引脚定义Inter FPGA芯片引脚定义是指在FPGA系统中,不同的FPGA芯片之间进行通信时所使用的引脚定义。

在FPGA系统中,不同的FPGA芯片之间需要进行数据传输和控制信号传递,而这些信号需要通过Inter FPGA连接器进行传递。

因此,在设计FPGA系统时,需要对Inter FPGA芯片引脚进行定义和配置。

Inter FPGA芯片引脚通常包括以下几种类型:1. 数据引脚:用于数据传输。

在不同的FPGA芯片之间进行数据传输时,需要将数据从一个芯片的输出引脚发送到另一个芯片的输入引脚上。

2. 时钟引脚:用于同步不同FPGA芯片之间的操作。

时钟信号可以保证不同芯片之间的操作按照相同的时间基准进行。

3. 复位引脚:用于复位不同FPGA芯片中的电路。

当系统启动或者出现错误时,可以通过复位信号将所有电路恢复到初始状态。

4. 中断引脚:用于向其他FPGA芯片发送中断请求。

当某个模块完成了某项任务或者出现了错误等情况时,可以通过中断信号通知其他模块。

5. 控制信号引脚:用于控制不同FPGA芯片之间的操作。

例如,可以通过控制信号引脚控制数据传输的开始和结束时间。

在FPGA系统中,Inter FPGA芯片引脚的定义和配置需要遵循一定的规则和流程。

具体步骤如下:1. 确定需要进行通信的FPGA芯片,并确定它们之间需要传输哪些信号。

2. 根据需要传输的信号类型,选择合适的Inter FPGA连接器,并将连接器中的引脚与FPGA芯片中对应的引脚进行匹配。

3. 在设计FPGA系统时,根据Inter FPGA芯片引脚定义和配置,编写相应的Verilog或VHDL代码,以实现不同FPGA芯片之间的通信功能。

4. 在进行FPGA系统仿真或者实际测试时,需要对Inter FPGA芯片引脚进行验证和调试,以确保通信功能正常运行。

总之,在设计FPGA系统时,Inter FPGA芯片引脚定义和配置是非常重要的一步。

常用IC芯片管脚的定义中引文翻译

常用IC芯片管脚的定义中引文翻译1、VOL—V oltage Output Low 低电平输出电压;VIH(V oltage Input High)高电平输入电压。

2、CLKO(Clock Output) 时钟输出;Vss 数字地。

DP:USB端D+信号。

3、VDD—数字电源;Vssp:I/O驱动缓冲数字地。

DM:USB端D-信号。

4、CE:Chip enable input 片使能输出;OE:Output enable input 输出使能输入。

5、WP:Write protect 写入保护;FWR:Flash write enable input闪存写入使能信号。

6、V A: analog power 模拟电源输入;LVDS:Low voltage differential signal低电平微分信号。

7、FB:Output voltage feedback 输出电压返回输入;SW:Power switch input 电源开关输入。

8、SHON:Shutdown control input 关闭信号输入;COMP:comp voltage.9、TS:Temperature-sense input温度感应信号输入RC:Timer-program input定时程序信号输入10. SNS:Current-sense input 电流感应信号输入;CE:使能信号(enable signal).11 .WE:写入启动信号;RST: reset 复位信号;CLK:时钟控制信号;CKE:时钟控制信号。

12. Vcc:电源信号;CS:片选信号;SCLK:串行时钟输入;RF: 信号输出;FCOM:公共信号端。

13.XTALO:晶振信号输出;XTALI:晶振信号输入。

OPOLS:VCOM 信号输出。

14.TXD:ASCO 时钟、数据输出;RXD:ASCO 数据输入或输出。

15.SYNC:同步脉冲输入; RCT: 振荡器时间常数电路;DC: 占空比控制。

oled引脚翻译

Vss power pin

This is a ground pin.

这是接地引脚

Vlss power pin

This is an analog ground pin.It should be connected to Vss externally.

When 8080 interface mode is selected,this pin will be Write(WR#)input.Data write operation is initiated when this pin is pulled LOW and the chip is selected.When serial or IIC interface is selected,this pin must connected to Vss.

Vbat power pin

Reserved pin.It should be connected to Vdd.

预留引脚,接Vdd。

BGGND power pin

Resevered pin.It should be connected to ground.

预留引脚,接地。

这是数据/命令控制引脚。当它被置高时(即VDD),在D[7:0]输入的数据被当做是数据。当它被置低时,在D[7:0]的数据被传送到指令寄存器。在IIC模式下,这个引脚被当做SA0作为从机地址选择。当3线串联接口被选择时,这个借口必须置低(Vss)。要知道具体MCU接口信号,请参考时序特征图标:数据13-1到13-5。

这些是8位双向数据线连接到微处理器数据线。当串行接口模式被选择,D0会被用作串行时钟输入:SCLK;D1会被用作数据线:SDIN,D2被悬空。当IIC模式被选择时,D2,D1应该被一同使用作为SDAout,SDAin,D0被用作时钟输入,SCL。

芯片引脚定义翻译

芯片引脚定义翻译引脚名称引脚定义CSH高端电流检测正向输入CSL低端电流检测反向输入FB电压反馈输入端VDD电压回馈输入端SYNC同步电压频率选择/频率设置/同步信号TIME/ON5延时电容/开关控制端SKIP低噪音模式控制器/跳频冲输入RST基准电压输出端SEQ电压转换模式控制DH高端场管驱动方波信号输出端LX电感连接反馈输入/电感检测输入端BST自举端/高低端激放电路输入端DL低端场管驱动方波信号输出端VL线性基准电压V+供电SHDN总关闭模式/总控制信号RUN/ON3开关控制SUS挂起输入/待机电压OFS偏移控制分压器输入ILIM电流限制调节CCV电压积分电容CCI电流均衡补偿OAIN-运算放大器反相输入OAIN+运算放大器同相输入VROK电源好信号BSTM自举电容LXM主电感连接端CMP主电感电流正输入CMN主电感电流负输入CSN副电感电流正输入CSP副电感电流负输入ON3电压开关控制脚ADD地址线AFC自动频率控制AGC自动增益控制AVCC音频供电BACKLIGHT背光灯开启BAT_VOLT电压检测Boost-En升压启动BUZZER振铃CS FLASH字库片选CS ROM版本片选CSRAM暂存片选DATA数据线LCD_CS显示屏片选LCD-EN显示屏启动MIC-本机话筒负极MIC+本机话筒正极ON_OFF开机触发POWER ON开机启动Reset复位VBATT电池电压TIME频率设置TON导通时间选择S0挂起模式DLM低端管驱动EC嵌入式控制器THRMTRIP温度控制VRON开机电源电压控制信号VSB待机VCCP总线供电EMI电磁抗干扰电路MOSFET方波切割组件PWM脉宽调制定义说明同步信号用于逻辑控制电路。

51单片机外部引脚英文全称是什么

引言:51单片机是一种常用的嵌入式系统微控制器,常用于各种电子设备中。

在使用51单片机时,了解其外部引脚的英文全称是非常重要的。

本文将详细介绍51单片机外部引脚的英文全称,探讨其各个引脚的功能和用途。

概述:51单片机外部引脚的英文全称是根据它们在芯片上的物理位置和连接功能来命名的。

这些引脚包括电源引脚、输入输出引脚、复位引脚和其他特殊功能引脚。

了解这些英文全称可以帮助工程师更好地掌握51单片机的使用和应用。

正文:1. 电源引脚(Power Pins)1.1 VCCVCC引脚是指供电引脚,它连接到单片机的正电源。

VCC引脚提供的电压通常是5V,也可以是3.3V或其他电压。

1.2 GNDGND引脚是指接地引脚,它连接到单片机的负电源。

GND引脚用于建立电路的共地参考点。

2. 输入输出引脚(I/O Pins)2.1 P0.0 - P0.7P0引脚是51单片机上的一个8位可编程输入输出引脚组。

P0.0到P0.7分别对应于物理引脚P0.0到P0.7。

这些引脚可以配置为输入或输出,用于与其他设备进行数据交换。

2.2 P1.0 - P1.7P1引脚是51单片机上的另一个8位可编程输入输出引脚组。

P1.0到P1.7分别对应于物理引脚P1.0到P1.7。

这些引脚也可以配置为输入或输出,用于与其他设备进行数据交换。

2.3 P2.0 - P2.7P2引脚是51单片机上的第三个8位可编程输入输出引脚组。

P2.0到P2.7分别对应于物理引脚P2.0到P2.7。

这些引脚同样可以配置为输入或输出,用于数据交换。

2.4 P3.0 - P3.7P3引脚是51单片机上的第四个8位可编程输入输出引脚组。

P3.0到P3.7分别对应于物理引脚P3.0到P3.7。

这些引脚也可以配置为输入或输出。

3. 复位引脚(Reset Pin)3.1 RSTRST引脚是51单片机上的复位引脚。

当RST引脚被拉低时,单片机将被复位。

复位引脚通常通过一个复位电路提供一个确定的复位信号。

电子器件针脚 术语

GAIN:增益。

GCAP:电源IC。

GCAP-CLK:CPU输出到电源模块的时钟(用于摩托罗拉手机)。

GCLK:32.768kHz,输出到CPU的时钟信号。

GIF-SYN:双工中频。

GND:地址线。在手机机板上,大片的铜箔都是地。

PWM:脉冲宽度调制,被用来进行充电控制。常见于诺基亚手机的充电控制电路。

PWRLEV:功率控制参考电平。

PWR-SW:开机信号。

RAM:随机存储器。

RD:读。

R/W:读写。

RED:红色。

REF:参考。

RESET:复位。

RETC-BATT:实时时钟电源。

RF:射频。

MODEM:调制解调器。摩托罗拉手机使用,是逻辑射频接口电路。它提供AFC、AOC及GMSK调制解调等。

MS:移动台。

MSC:移动交换中心。

MSIN:移动台识别码。

MSRN:漫游。

MUTE:静音。

NAM:号码分配模块。

NC:空,不接。

NEG:负压。

NI-H:镍氢。

IFVCCO:中频VCO。用于接收机的第二混频器或发射机的I/Q调制器。与后面的VHFVCO作用一样,只要看到IFVCO或VHFVCO,就可以断定这种手机的接收机是超外差二次变频接收机,有两个中频。

IFLO:中频本振。

IF-IN中频输入。

IFTUNE:中频VCO控制信号。

IF-VCC中频电路供电,有些手机也用SW-VCC表示。

NI-G:镍镉。

NONETWORK:无网络。

OFSET:偏置。

OMC:操作维护中心。

芯片1408引脚定义

芯片1408引脚定义

芯片1408引脚定义是指芯片上的引脚所代表的功能和作用。

每个引脚都有其独特的任务和连接方式,以实现芯片的各项功能。

我们来看一下芯片1408引脚的定义及其作用。

1. 引脚1:VCC

该引脚是芯片的电源引脚,连接正电源以供芯片正常工作。

2. 引脚2:GND

该引脚是芯片的地引脚,连接负电源以供芯片正常工作。

3. 引脚3:RESET

该引脚是芯片的复位引脚,当该引脚接收到复位信号时,芯片会回到初始状态。

4. 引脚4:CLK

该引脚是芯片的时钟输入引脚,用于提供时钟信号给芯片的内部电路。

5. 引脚5:DATA_IN

该引脚是芯片的数据输入引脚,用于接收外部数据输入。

6. 引脚6:DATA_OUT

该引脚是芯片的数据输出引脚,用于输出芯片内部处理后的数据。

7. 引脚7:ADDR

该引脚是芯片的地址输入引脚,用于接收外部地址输入。

8. 引脚8:CS

该引脚是芯片的片选引脚,用于选择芯片进行操作。

通过上述引脚的定义,我们可以看出芯片1408具有电源供给、复位、时钟输入、数据输入输出、地址输入、片选等功能。

不同的引脚连接方式可以实现不同的操作和功能,从而满足不同的应用需求。

总结一下,芯片1408引脚的定义清晰明了,每个引脚都有其特定的作用和功能,通过合理连接和使用,可以实现芯片的各项功能。

在设计电路或应用中,我们需要根据具体需求来合理使用这些引脚,以达到预期的效果。

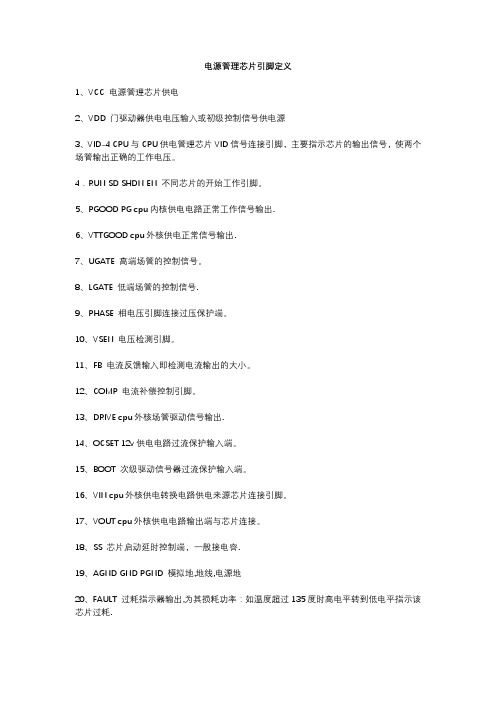

电源管理芯片引脚定义

电源管理芯片引脚定义(总1页) -本页仅作为预览文档封面,使用时请删除本页-电源管理芯片引脚定义1、VCC 电源管理芯片供电2、VDD 门驱动器供电电压输入或初级控制信号供电源3、VID-4 CPU与CPU供电管理芯片VID信号连接引脚,主要指示芯片的输出信号,使两个场管输出正确的工作电压。

4、RUN SD SHDN EN 不同芯片的开始工作引脚。

5、PGOOD PG cpu内核供电电路正常工作信号输出。

6、VTTGOOD cpu外核供电正常信号输出。

7、UGATE 高端场管的控制信号。

8、LGATE 低端场管的控制信号。

9、PHASE 相电压引脚连接过压保护端。

10、VSEN 电压检测引脚。

11、FB 电流反馈输入即检测电流输出的大小。

12、COMP 电流补偿控制引脚。

13、DRIVE cpu外核场管驱动信号输出。

14、OCSET 12v供电电路过流保护输入端。

15、BOOT 次级驱动信号器过流保护输入端。

16、VIN cpu外核供电转换电路供电来源芯片连接引脚。

17、VOUT cpu外核供电电路输出端与芯片连接。

18、SS 芯片启动延时控制端,一般接电容。

19、AGND GND PGND 模拟地地线电源地20、FAULT 过耗指示器输出,为其损耗功率:如温度超过135度时高电平转到低电平指示该芯片过耗。

21、SET 调整电流限制输入。

22、SKIP 静音控制,接地为低噪声。

23、TON 计时选择控制输入。

24、REF 基准电压输出。

25、OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连VCC丧失过压保护功能。

26、FBS 电压输出远端反馈感应输入。

27、STEER 逻辑控制第二反馈输入。

28、TIME/ON 5 双重用途时电容和开或关控制输入29、RESET 复位输出V1-0v跳变,低电平时复位。

30、SEQ 选择PWM电源电平轮换器的次序:SEQ接地时 5v输出在之前。

SEQ接REF上,5v各自独立。

常用IC芯片管脚的定义中引文翻译

使能信号。

VA: analog power 模拟电源输入; LVDS:Low voltage differential signal低电平微分信号。

电源开关输入。

定时程序信号输入signal).11 .WE:写入启动信号;RST: reset 复位信号;CLK 时钟控制信号;CKE 时钟控制信号。

12. Vcc:电源信号;CS 片选信号;SCLK:串行时钟输入;RF:信号输出;FCOM:公共信号端。

:晶振信号输出;XTALI:晶振信号输入。

OPOLS:VCO 信号输出。

:ASCO 时钟、数据输出;RXD:ASCO^据输入或输出。

: 同步脉冲输入 ; RCT: 振荡器时间常数电路 ;DC: 占空比控制。

:5V 基准电压;VFB:误差放大器倒相输入;COMP 误差放大器输出。

1、2、 3、 4、 5、 常用 IC 芯片管脚的定义中引文翻译VOL — Voltage Output Low 低电平输出电压; VIH (Voltage Input High )高 电平输入电压。

CLKO(Clock Out put)时钟输出;Vss 数字地。

DP:USB 端 D+言号。

VD —数字电源;Vssp:I/O 驱动缓冲数字地。

DM: USB 端 D-信号。

CE:Chip enable input 片使能输出; OE :Output enable input 输出使能输入。

WP:Write protect 写入保护; FWR Flash write enable input闪存写入6、 7、 FB :Output voltage feedback输出电压返回输入; SW:Power switch input8、 SHON:Shutdown control input 关闭信号输入 ;COMP:comp voltage. 9、 TS:Temperature-sense input温度感应信号输入 RC:Timer-program input10. SNS:Current-sense input电流感应信号输入;CE:使能信号(enable:软启动控制外接电容;Vc:功放电路电源(驱动电路电源);OUT 驱动输出。

芯片引脚定义

芯片引脚定义电源管理芯片引脚定义1、AGND GND PGND 模拟地地线电源地2、BOOT 次级驱动信号器过流保护输入端。

3、COMP 电流补偿控制引脚。

4、CT 定时电容。

5、DRIVE cpu外核场管驱动信号输出。

6、FAULT 过耗指示器输出,为其损耗功率:如温度超过135度时高电平转到低电平指示该芯片过耗。

7、FB 电流反馈输入即检测电流输出的大小。

8、FBS 电压输出远端反馈感应输入。

9、ILIM 电流限制门限调整。

10、LGATE 低端场管的控制信号。

11、OCSET 12v供电电路过流保护输入端。

12、OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连VCC 丧失过压保护功能。

13、PGOOD PG cpu内核供电电路正常工作信号输出。

14、PHASE 相电压引脚连接过压保护端。

15、REF 基准电压输出。

16、RESET 复位输出V1-0v跳变,低电平时复位。

17、RT 定时电阻。

18、RUN SD SHDN EN 不同芯片的开始工作引脚。

19、SET 调整电流限制输入。

20、SS 芯片启动延时控制端,一般接电容。

21、SEQ 选择PWM电源电平轮换器的次序:SEQ接地时5v输出在3.3v之前。

SEQ 接REF22、SKIP 静音控制,接地为低噪声。

22、STEER 逻辑控制第二反馈输入。

上,3.3v 5v各自独立。

SEQ接v1上时 3.3v输出在5v之前。

23、SYNC 振荡器同步和频率选择,150Khz操作时,sync连接到GND, 300Khz 时连接到REF上,用0-5v驱使sync 使频率在340-195Khz.24、TIME/ON 5 双重用途时电容和开或关控制输入25、TON 计时选择控制输入。

26、UGATE 高端场管的控制信号。

27、VCC 电源管理芯片供电28、VCNTL 供电29、VDD 门驱动器供电电压输入或初级控制信号供电源30、VID-4 CPU与CPU供电管理芯片VID信号连接引脚,主要指示芯片的输出信号,使两个场管输出正确的工作电压。

S3C2440中文翻译之引脚描述

S3C2440译者:☆翔子★OM[1:0] I 这两bit用于把2440设置成TEST模式,也用于设置nGCS0总线的宽度。

00:nand-boot;01:16bit;10:32bit11:test modeADDR[26:0] O 地址总线。

存储器输出的对应bank的地址线,27bit刚好128M空间。

DATA[31:0] IO 数据总线。

存储器读的时候输入,写的时候输出。

总线宽度可编程:8/16/32bit。

nGCS[7:0] O 通用芯片选择。

当一个存储器的地址命中某个bank的地址范围内时,对应的nGCS[7:0]就被激活。

访问周期号和bank大小可编程。

nWE O 写使能。

指示当前总线周期是一个写周期nOE O 读(输出)使能。

指示当前总线周期是一个读周期nXBREQ I 总线保持请求。

允许其他的总线master去请求本地总线的控制。

BACK有效指示总线控制已经生效(批准了)。

nXBACK I 总线保持应答。

指示2440交出总线控制权给另一个总线master。

nWAIT I 请求延长当前总线周期。

只要该信号是L电平,当前总线周期不能被完成。

SD R A M/SR A MnSRAS O SDRAM行地址strobe (行地址最大限制数)nSCAS O SDRAM列地址strobe (列地址最大限制数)nSCS[1:0] O SDRAM芯片选择DQM[3:0] O SDRAM数据mask(掩码)SCLK[1:0] O SDRAM时钟SCKE O SDRAM时钟使能nBE[3:0] O 高字节/低字节使能(在16bit SRAM情况下使用) nBWE[3:0] O 写字节使能N A N D Fl as hCLE O 命令锁存使能ALE O 地址锁存使能nFCE O Nand flash 芯片使能nFRE O Nand flash读使能nFWE O Nand flash写使能NCON I Nand flash配置FRnB I Nand flash 准备好/忙信号(ready/busy)如果没有使用Nand flash控制器,必须为高电平(VDDMOP)LC DVD[23:0] O STN/TFT/SEC TFT :LCD数据总线LCD_PWREN O STN/TFT/SEC TFT :LCD面板电源使能控制信号VCLK O STN/TFT:LCD时钟信号VFRAME O STN:LCD帧信号VLINE O STN:LCD行信号VM O STN:VM交替行列电压极性。

引脚

谢谢观看

引脚

从芯片内部引出外围电路的接线

目录

01 解释

03

高压电容断裂失效分 析

02 功能

引脚,又叫管脚,英文叫Pin。就是从集成电路(芯片)内部电路引出与外围电路的接线,所有的引脚就构成 了这块芯片的接口。引线末端的一段,通过软钎焊使这一段与印制板上的焊盘共同形成焊点。引脚可划分为脚跟 (bottom)、脚趾(toe)、脚侧(side)等部分。

对涂胶工序进行细化,要求环氧胶固定电容高度达到电容本体的1/3,并在两肋形成山脊状支撑,使高压电容 与E-4X一体,振动中不再颤振,引程,发现是先装配高压电容再装配其它元件,这样立式高压电容为最高点,周 转或放置时,电容易受到磕碰或外力而造成歪斜,每批电路板测试或固定前发现部分高压电容有歪斜现象,固定 前人工进行了扶正。更改工序即先装配其它元件和粘接立柱再装配高压电容。这样周转或放置时比高压电容稍高 的立柱受力,保护了高压电容。改进工序前,先对电路板真空涂覆(在电容陶瓷面上形成约15 μm厚的派埃林薄膜 材料),再涂硅橡胶固定。改进后,先在电容上涂环氧胶,再在整个电路板真空涂覆,这样在电容和胶外表面一体 形成派埃林薄膜。由于派埃林薄膜表面粗糙度小于陶瓷面,胶在派埃林薄膜表面的接触角大于陶瓷表面(接触角越 小润湿效果越好),改进后固定效果更好。

电路板(试验件)换胶后通过了加强考核的随机振动试验,随后大批量正式产品进行返修。新投产的整流器电 路板按照改进后的流程生产,用E-4X环氧树脂胶固定高压电容。返修后的产品和按改进措施新生产的产品在组件、 舱段、全弹三级的ESS试验均未再发生高压电容引脚断裂故障,表明问题得到解决。

1)高压电容引脚断裂性质是疲劳断裂; 2)装配方式设计不合理,固定胶粘接强度不够和工艺不完善是导致引脚断裂的原因; 3)改用环氧胶和调整生产流程从工程上简单、有效、经济地解决了问题。

电源芯片引脚定义-范本模板

电源管理芯片引脚定义1、VCC 电源管理芯片供电2、VDD 门驱动器供电电压输入或初级控制信号供电源3、VID-4 CPU与CPU供电管理芯片VID信号连接引脚,主要指示芯片的输出信号,使两个场管输出正确的工作电压。

4.RUN SD SHDN EN 不同芯片的开始工作引脚。

5、PGOOD PG cpu内核供电电路正常工作信号输出.6、VTTGOOD cpu外核供电正常信号输出.7、UGATE 高端场管的控制信号。

8、LGATE 低端场管的控制信号.9、PHASE 相电压引脚连接过压保护端。

10、VSEN 电压检测引脚。

11、FB 电流反馈输入即检测电流输出的大小。

12、COMP 电流补偿控制引脚。

13、DRIVE cpu外核场管驱动信号输出.14、OCSET 12v供电电路过流保护输入端。

15、BOOT 次级驱动信号器过流保护输入端。

16、VIN cpu外核供电转换电路供电来源芯片连接引脚。

17、VOUT cpu外核供电电路输出端与芯片连接。

18、SS 芯片启动延时控制端,一般接电容.19、AGND GND PGND 模拟地,地线,电源地20、FAULT 过耗指示器输出,为其损耗功率:如温度超过135度时高电平转到低电平指示该芯片过耗.21、SET 调整电流限制输入。

22、SKIP 静音控制,接地为低噪声.23、TON 计时选择控制输入。

24、REF 基准电压输出.25、OVP 过压保护控制输入脚,接地为正常操作和具有过压保护功能,连VCC丧失过压保护功能.26、FBS 电压输出远端反馈感应输入。

27、STEER 逻辑控制第二反馈输入.28、TIME/ON 5 双重用途时电容和开或关控制输入29、RESET 复位输出V1-0v跳变,低电平时复位。

30、SEQ 选择PWM电源电平轮换器的次序:SEQ接地时5v输出在3.3v之前。

SEQ接REF上,3。

3v 5v各自独立。

SEQ接v1上时3。

3v输出在5v之前。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

引脚名称引脚定义CSH 高端电流检测正向输入CSL 低端电流检测反向输入FB 电压反馈输入端VDD 电压回馈输入端SYNC

同步电压频率选择/频率设置/同步信号TIME/ON5延时电容/开关控制端SKIP 低噪音模式控制器/跳频冲输入RST 基准电压输出端SEQ 电压转换模式控制DH 高端场管驱动方波信号输出端LX 电感连接反馈输入/电感检测输入端BST 自举端/高低端激放电路输入端DL 低端场管驱动方波信号输出端VL 线性基准电压V+供电SHDN 总关闭模式/总控制信号RUN/ON3开关控制SUS 挂起输入/待机电压OFS 偏移控制分压器输入ILIM 电流限制调节CCV 电压积分电容CCI 电流均衡补偿OAIN-运算放大器反相输入OAIN+运算放大器同相输入VROK 电源好信号BSTM 自举电容LXM 主电感连接端CMP 主电感电流正输入CMN 主电感电流负输入CSN 副电感电流正输入CSP 副电感电流负输入ON3电压开关控制脚ADD 地址线AFC

自动频率控制AGC 自动增益控制

AVCC音频供电BACKLIGHT背光灯开启

BAT_VOLT电压检测

Boost-En升压启动

BUZZER振铃

CS FLASH字库片选

CS ROM版本片选

CSRAM暂存片选

DATA数据线

LCD_CS显示屏片选

LCD-EN显示屏启动

MIC-本机话筒负极

MIC+本机话筒正极

ON_OFF开机触发

POWER ON开机启动

Reset复位

VBATT电池电压

TIME频率设置

TON导通时间选择

S0挂起模式

DLM低端管驱动

EC嵌入式控制器THRMTRIP温度控制

VRON开机电源电压控制信号VSB待机

VCCP总线供电

EMI电磁抗干扰电路MOSFET方波切割组件

PWM脉宽调制

定义说明

用于逻辑控制电路。