三种高速乘法器的FPGA实现及性能比较

基于FPGA的乘法器实现结构分析与仿真

・大规模集成电路设计、制造与应用・基于FPGA 的乘法器实现结构分析与仿真伞景辉,常 青(湖南省长沙市国防科大A TR 实验室,长沙410073) 摘 要:现场可编程门阵列(FPGA )的快速发展为数字信号处理(D SP )系统设计提供了一种新的解决方案,而乘法运算是D SP 领域内的一种基本运算,应用极为广泛,对乘法运算基于FPGA 的实现结构进行研究具有重要意义。

本文分析乘法运算的特点,给出了几种适应FPGA 实现的乘法器结构。

并在X ilinx 公司的ISE 4.1i 软件环境下,采用V HDL 和V I R ELO G 硬件描述语言进行了设计实现并对其性能进行了比较分析。

关键词:D SP ;乘法器;FPGA中图分类号:TN 47 文献标识码:A 文章编号:1002-2279(2004)03-0003-05The A na lys is a nd S i m ula ting fo r FPGA -B a s e d M ultip lie rI m p lem e nta tion S truc ture sSAN J ing -hu i ,CHAN G Q ing(A T R -3L ab ,N ational U niversity of D ef ense T echnology ,Chang sha 410073,Ch ina ) Abstract :T he p rogress in field p rogramm ab le gate arrays (FPGA s )p rovides new op ti on s fo rD SP design engineers .A nd the m u lti p licati on is one of the m o st i m po rtan t operati on s in the field of digital signal p rocessing (D SP ).H ence ,in th is pap er ,the characteristic of m u lti p licati on is analyzed and som e differen t types of m u lti p lier structu res are offered .A nd the perfo r m ance evaluati on and com parison (area and sp eed )fo r these m u lti p lier i m p lem en tati on structu res have been carried ou t by u tilizing the H ard D escribe L anguage (V HDL and V I R ELO G )and ISE softw are p ackage V 4.1i from X ilinx .Key words :D igital signal p rocessing (D SP );M u lti p lier ;F ield p rogramm ab le gate array (FPGA )1 前 言传统上,数字信号处理系统(D SP )的构建在较低速率要求下是以通用D SP 芯片为核心的,如果要求速率较高的话,则要使用专用的D SP 芯片或者专用集成电路(A S I C s )来设计实现。

fpga中做乘法

FPGA中的乘法引言FPGA(现场可编程门阵列)是一种可重构的硬件设备,可以通过编程来实现各种功能。

其中,乘法是FPGA中的常见操作之一。

本文将详细介绍FPGA中的乘法实现方法、应用场景以及优势。

FPGA中的乘法实现方法在FPGA中,乘法可以通过多种方式实现。

下面将介绍两种常见的乘法实现方法。

1. 串行乘法器串行乘法器是一种简单的乘法器实现方法。

它将两个乘数的每一位逐位相乘,并将乘积相加得到最终结果。

具体实现步骤如下:1.将两个乘数进行拆分,得到每一位的值。

2.逐位相乘,得到每一位的乘积。

3.将乘积相加,得到最终结果。

串行乘法器的优点是实现简单,适用于乘数位数较少的情况。

然而,由于每一位的乘积需要逐位相加,因此计算速度较慢。

2. 并行乘法器并行乘法器是一种高效的乘法器实现方法。

它将两个乘数同时拆分成多个部分,并行计算每一部分的乘积,最后将所有部分的乘积相加得到最终结果。

具体实现步骤如下:1.将两个乘数进行拆分,得到多个部分。

2.并行计算每一部分的乘积。

3.将所有部分的乘积相加,得到最终结果。

并行乘法器的优点是计算速度快,适用于乘数位数较多的情况。

然而,实现相对复杂,需要更多的硬件资源。

FPGA中乘法的应用场景乘法在FPGA中有广泛的应用场景,下面将介绍几个常见的应用场景。

1. 信号处理在信号处理中,乘法常用于滤波器和变换器等算法中。

FPGA中的乘法器可以高效地执行这些算法,提供快速且准确的信号处理能力。

2. 数字信号处理在数字信号处理中,乘法器广泛应用于调制解调、编码解码和信号分析等领域。

FPGA中的乘法器可以实现高速且低功耗的数字信号处理算法。

3. 图像处理在图像处理中,乘法器用于实现像素级运算,如图像增强、边缘检测和图像变换等。

FPGA中的乘法器可以并行计算多个像素的乘积,提高图像处理的效率。

4. 科学计算在科学计算中,乘法器用于矩阵运算、向量运算和复数运算等。

FPGA中的乘法器可以并行计算多个元素的乘积,提供高性能的科学计算能力。

基于fpga的乘法器和除法器

任务书:1、十六位硬件乘法器电路2、八位硬件除法器电路摘要:设计一个16位硬件乘法器电路。

要求2位十进制乘法,能用LED数码管同时显示乘数,被乘数和积的值.本设计利用Quartus II软件为设计平台,通过移位相加的乘法原理:即从被乘数的最低位开始,若为1,则乘数左移后与上一次的和相加;若为0,左移后以全零相加,直至被乘数的最高位。

经软件仿真和硬件测试验证后,以达到实验要求。

设计一个8位硬件除法器电路。

要求2位十进制除法,能用LED数码管显示结果、除数和被除数的值。

根据被除数(余数)和除数的大小来上商,被除数低位补零,再减去右移后的除数也可以改为左移余数,减去除数,这样可以确保参与运算的寄存器具有相同位数。

商写到寄存器的低位,然后再左移一位。

经软件仿真和硬件验证后,以达到实验要求。

目录2.任务书 (2)3.摘要 (2)4.目录 (3)5.正文 (4)5.1.1 乘法器系统设计 (4)5.1.1.1 设计要求 (4)5.1.2.2系统设计方案 (4)5.1.2 单元电路设计 (4)十进制计算模块 (5)BCD码转二进制模块 (5)8位右移寄存器模块 (6)8位加法器模块 (7)1位乘法器multi_1模块 (7)16位移位寄存器reg_16模块 (8)16位二进制转BCD码B_BCD模块 (9)8位乘法器multi_8x8顶层设计 (10)5.1.3 乘法器的系统测试 (14)仿真分析 (14)硬件验证 (15)5.2.1 除法器系统设计………………………………………………5.2.2单元电路设计………………………………………………5.2.3 除法器的系统设计………………………………………………仿真分析………………………………………………硬件验证………………………………………………6. 结论 (15)7. 参考文献 (15)8. 分工 (15)5.正文题目要求设计基于fpga的乘法器和除法器。

本小组想出的方案是利用位移相加和相减来制作乘法器和除法器。

fpga中做乘法

fpga中做乘法摘要:一、FPGA 简介二、FPGA 中乘法运算的重要性三、FPGA 中乘法运算的原理四、FPGA 中实现乘法运算的方法五、乘法运算在FPGA 中的应用六、总结正文:FPGA(现场可编程门阵列)是一种集成电路,它允许用户根据需要对硬件进行编程。

FPGA 具有高度的可定制性和灵活性,广泛应用于各种领域,如通信、计算机、图像处理等。

在FPGA 中,乘法运算是一个基本的操作,它在数字信号处理、滤波器设计、矩阵运算等方面具有重要的应用价值。

为了提高FPGA 中乘法运算的性能,需要对其原理和实现方法有深入的了解。

FPGA 中的乘法运算原理与普通的数字乘法相同,即将两个二进制数相乘并产生一个结果。

然而,在FPGA 中,乘法运算需要通过硬件描述语言(HDL)实现。

HDL 是一种用于描述数字电路和模拟电路的文本格式,它可以描述FPGA 中的逻辑功能、结构和行为。

在FPGA 中实现乘法运算的方法有很多,常见的有级联法、查找表法、数字流水线法等。

这些方法各有优缺点,例如,级联法实现简单,但速度较慢;查找表法速度快,但容量有限;数字流水线法速度快且容量大,但实现复杂。

因此,在实际应用中,需要根据具体需求选择合适的方法。

乘法运算在FPGA 中的应用举不胜举。

例如,在数字信号处理中,乘法运算可用于数字滤波器的设计;在图像处理中,乘法运算可用于矩阵乘法,从而实现图像的缩放、旋转等操作。

通过深入了解乘法运算在FPGA 中的原理和实现方法,可以更好地利用FPGA 实现各种功能。

总之,FPGA 中的乘法运算是数字电路设计中的一个基本操作,它在各种应用领域具有广泛的应用价值。

基于FPGA的乘法器设计

基于FPGA的乘法器设计乘法运算在数字信号处理、图像处理、通信系统等领域中非常常见。

传统的乘法运算通常是通过乘法器件(如芯片)来实现,这样的乘法器件通常是专用定制的,功耗高、成本昂贵。

而基于FPGA的乘法器设计可以通过编程的方式,在硬件级别上实现乘法运算,具有灵活性高、性能可调的优势。

1. 确定乘法算法:乘法运算的算法有很多种,比如简单乘法、Booth 算法、Wallace树算法等。

根据实际需求,选择适合的乘法算法。

2.确定数据位宽:乘法器设计需要根据给定的乘法算法确定输入数据的位宽和输出结果的位宽。

位宽的选择对乘法器的性能有重要影响,过小的位宽可能导致精度不足,过大的位宽则会增加硬件资源的使用。

3.设计乘法核心:乘法核心是乘法器设计的核心部分,根据选择的乘法算法和数据位宽,设计乘法核心的逻辑电路。

乘法核心通常包括乘法器和累加器。

4.优化设计:乘法器的设计需要考虑优化性能和资源利用率。

常见的优化方法包括流水线设计、并行计算、减少不必要的运算等。

5. 编写硬件描述语言(HDL)代码:HDL是一种用于描述硬件电路的语言,比如Verilog和VHDL。

根据设计的乘法器模块,编写HDL代码来描述乘法器的功能和电路结构。

6.仿真和调试:通过利用仿真工具对设计好的乘法器进行功能验证和调试,发现并修复存在的问题。

1.灵活性高:FPGA的可编程性使得乘法器的设计可以根据实际需求进行灵活调整和修改,而不需要重新设计和生产乘法器芯片。

2.性能可调:FPGA的资源(逻辑单元)可以根据需要配置使用,可以通过增加逻辑单元和优化设计来提高乘法器的性能。

3.低功耗:相比于专用乘法器件,基于FPGA的乘法器通常具有更低的功耗,可以在一定程度上减少系统能耗。

4.成本低:由于FPGA是可编程设备,相对于专用乘法器件的生产成本要低,尤其适用于小批量生产和特定需求。

综上所述,基于FPGA的乘法器设计具有灵活性高、性能可调和成本低的优势,能够满足不同领域对于乘法运算的需求。

fpga中做乘法

fpga中做乘法

FPGA中可以使用各种方法进行乘法,下面列举了几种常用的方法:

1. 逻辑门级乘法器:可以利用AND、OR、XOR等逻辑门实现简单的乘法运算。

例如,使用一系列AND运算将两个输入位相乘,再使用逻辑门将它们相加得到结果。

这种方法的优点是简单易实现,缺点是速度较慢。

2. Booth编码乘法器:Booth编码乘法器是一种基于查找表的乘法器,利用Booth编码对乘数进行编码,根据编码结果进行查表并得到部分积,再将部分积相加得到最终结果。

这种方法的优点是速度较快,缺点是复杂度较高。

3. 数字信号处理(DSP)乘法器:FPGA中通常会包含一些专门设计用于进行高速乘法运算的DSP乘法器。

这些乘法器通常具有高速、低功耗和占用较少逻辑资源等特点,非常适合在FPGA中实现乘法运算。

4. 基于硬件乘法器的乘法:某些FPGA芯片可能包含硬件乘法器,可以直接使用硬件乘法器进行乘法运算。

硬件乘法器通常具有非常高的速度和低的功耗,但会占用较多的资源。

需要根据具体的应用场景和性能要求选择适合的乘法方法。

基于FPGA的数字乘法器性能比较

wh n Mut l rh slre aawit hl h hf.d lpirc n eo o z e o re n c i. e l pi a ag rd t dh w i te s i a d mut l a c n miersu c si hp i e e t i e

基 于 F G 的数 字 乘 法 器 性 能 比较 米 PA

鞠 芳 , 昕 , 岚 马 田

( 山东大学信息科学与工程学院 , 济南 200 ) 510

摘 要 : 详细描述了四种基本的 F G P A数字乘法器设计方法即阵列法、 查找表法、 移位相加法、 o h Bo 法的原理和实现过程。 t

以 4 4和 1x 6数字乘法器的设 计为例 , x 61 通过在 At aP A芯片上 的仿真与综合 , lrF G e 给出了这 四种数字乘法器 的运算速度和 占

用逻辑资源情况 。结果表明随着位宽的变化 , 各方法的相对效果会有变化 , 于具有较宽数据位 的乘 法器来说 , 对 使用 B oh方 ot 法有 明显 的优势 , 而移位相加法可明显的节省 片上硬件资源 。

( ol eo n r tnSi c C lg f mai c ne&E gnen S a dn nvrt,i n20 0 , hn ) e fI o o e n i r g,h n ogU i sy Jn 5 10 C ia c i ei a Ab t a t T rn i ls a d r a ii g p o e s so o rk n fF s r c : he p i c p e n e l n r c se ff u i dso PGA iia li ir c r a d a r y z dgt lmu t e s whih a e n me ra pl

基于FPGA的高速流水线浮点乘法器设计与实现

基于FPGA的高速流水线浮点乘法器设计与实现

摘要:设计了一种支持IEEE754浮点标准的32位高速流水线结构浮点乘法器。

该乘法器采用新型的基4布思算法,改进的4:2压缩结构和部分积求和电路,完成Carry Save形式的部分积压缩,再由Carry Look-ahead加法器求得乘积。

时序仿真结果表明该乘法器可稳定运行在80M的频率上,并已成功运用在浮点FFT处理器中。

1 引言

在数字化飞速发展的今天,人们对微处理器的性能要求也越来越高。

作为衡量微处理器性能的主要标准,主频和乘法器运行一次乘法的周期息息相关。

因此,为了进一步提高微处理器性能,开发高速高精度的乘法器势在必行。

同时由于基于IEEE754 标准的浮点运算具有动态范围大,可实现高精度,运算规律较定点运算更为简捷等特点,浮点运算单元的设计研究已获得广泛的重视。

本文介绍了32 位浮点乘法器的设计,采用了基4 布思算法,改进的4:2 压缩器及布思编码算法,并结合FPGA 自身特点,使用流水线设计技术,在实现高速浮点乘法的同时,也使是系统具有了高稳定性、规则的结构、易于FPGA 实现及ASIC 的HardCopy 等特点。

基于FPGA的高速流水定点乘法器的设计

end multiply ; architecture multiply of multiply is signal p1 :std - logic - vector (47 downto 0) ; signal p2 :std - logic - vector (45 downto 0) ; signal p3 :std - logic - vector (43 downto 0) ; signal p4 :std - logic - vector (41 downto 0) ; signal p5 :std - logic - vector (39 downto 0) ; signal p6 :std - logic - vector (37 downto 0) ; signal p7 :std - logic - vector (35 downto 0) ; signal p8 :std - logic - vector (33 downto 0) ; signal p9 :std - logic - vector (31 downto 0) ; signal p10 :std - logic - vector (29 downto 0) ; signal p11 :std - logic - vector (27 downto 0) ; signal p12 :std - logic - vector (25 downto 0) ; signal pa :std - logic - vector (47 downto 0) ; signal pb :std - logic - vector (43 downto 0) ; signal pc :std - logic - vector (39 downto 0) ; signal pd :std - logic - vector (35 downto 0) ; signal pe :std - logic - vector (31 downto 0) ; signal pf :std - logic - vector (27 downto 0) ; signal pg :std - logic - vector (47 downto 0) ; signal ph :std - logic - vector (39 downto 0) ; signal pi :std - logic - vector (31 downto 0) ; signal pj :std - logic - vector (47 downto 0) ; signal pk :std - logic - vector (47 downto 0) ; begin

基于FPGA的16位乘法器的实现

目录引言....................................................................................................................................... - 1 - 摘要....................................................................................................................................... - 2 -一、乘法器概述....................................................................................................................... - 3 -1.1 EDA技术的概念........................................................................................................ - 3 -1.2 EDA技术的特点........................................................................................................ - 3 -1.3 EDA设计流程............................................................................................................ - 5 -1.4硬件描述语言(Verilog HDL)................................................................................ - 5 -二、16位乘法器的设计要求与设计思路.............................................................................. - 6 -2.2 设计要求.................................................................................................................... - 6 -三、16位乘法器的总体框图.................................................................................................. - 6 -四、16位乘法器的综合设计.................................................................................................. - 7 -4.1 16位乘法器功能........................................................................................................ - 7 -4.2 16位乘法器设计思路................................................................................................ - 8 -4.3 基于Verilog HDL 硬件语言的乘法器设计 ............................................................ - 8 -(1)输入模块......................................................................................................... - 8 -(2)乘法模块......................................................................................................... - 9 -五、总体调试与仿真结果..................................................................................................... - 10 -5.1乘法器的RTL Viewer .......................................................................................... - 10 -5.2 16位乘法器的系统程序:....................................................................................... - 11 -5.3计算结果仿真结果................................................................................................... - 12 -5.3.1仿真测试程序(a=6,b=10).............................................................................. - 12 - 总结......................................................................................................................................... - 16 - 参考文献................................................................................................................................. - 16 -引言随着微电子技术的飞速发展,集成电路工艺进入深亚微米阶段,特征尺寸变得越来越小。

基于FPGA的乘法器设计和实现

高速乘法器的性能比较简介对基于阵列乘法器修正布斯算法(mba)乘法

高速乘法器的性能比较简介:对基于阵列乘法器、修正布斯算法(MBA)乘法器、华莱士(WT)乘法器和MBA-WT混合乘法器的四种架构的32位乘法器性能进行了比较,在选择乘法器时,应根据实际应用,从面积、速度、功耗等角度权衡考虑乘法是数字信号处理中重要的基本运算。

在图像、语音、加密等数字信号处理领域,乘法器扮演着重要的角色,并在很大程度上左右着系统性能。

随着实时信号处理的提出和集成电路工艺水平的进步,人们开始致力于高速乘法器设计。

最 初,阵列乘法采用移位与求和算法,部分乘积项(Partial Product, PP)数目决定了求和运算的次数,直接影响乘法器的速度。

修正布斯算法(Modified Booth Algorithm, MBA)对乘数重新编码,以压缩PP。

华莱士树(Wallace Tree, WT)结构改变求和方式,将求和级数从O(N)降为O(logN),提高了运算速度,但是WT存在结构不规整,布线困难的缺点。

用4:2压缩器(4:2 compressor)代替全加器(FA)可以解决这一问题。

将MBA算法和WT结构的优点相结合,形成了MBA-WT乘法器。

以下1~4节将分别介绍阵列乘法器、MBA乘法器、WT乘法器、MBA WT乘法器。

最后对四种乘法器的性能进行比较,并总结全文。

1 阵列乘法器阵 列乘法器基于移位与求和算法。

被乘数与乘数中的某一位相乘,产生一组PP,将该组PP移位,使LSB与乘数对应位对齐;求出全部PP,并相应移位;对所有 PP 求和,得到乘积。

因此,加法阵列结构非常重要。

CRA (Carry Ripple Adder)存在进位问题,运算速度慢。

CSA (Carry Save Adder)将本级进位传至下级,求和速度快,且速度与字长无关。

阵列乘法器中,CSA把PP阵列缩减至Sum和Carry两项,再用高速加法 器求和得积。

阵列乘法器结构规范,利于布局布线。

因 为乘数和被乘数可正、可负,所以一般用二进制补码表示,以简化加、减运算。

fpga中做乘法

fpga中做乘法摘要:一、FPGA 简介二、FPGA 中的乘法运算三、FPGA 乘法器的优化方法四、总结正文:FPGA(现场可编程门阵列)是一种集成电路,它可以通过编程实现数字电路的设计与实现。

随着现代数字信号处理技术的不断发展,FPGA 在通信、图像处理、人工智能等领域得到了广泛应用。

在FPGA 中进行乘法运算是一项基本任务,本文将介绍FPGA 中乘法运算的相关知识。

在FPGA 中进行乘法运算,首先要了解FPGA 的基本结构和原理。

FPGA 内部由大量的可编程逻辑单元(LE)、输入输出模块(IOB)、时钟管理模块(CPM)等组成。

通过对这些模块的配置和编程,可以实现各种数字逻辑电路,包括乘法器。

在FPGA 中实现乘法运算,主要有以下几种方法:1.使用查找表(LUT)实现乘法器:查找表是一种具有多个输入和输出的存储单元,可以通过编程实现输入与输出之间的映射。

利用查找表可以将乘法运算分解为加法运算,从而实现乘法器的快速计算。

2.使用数字信号处理(DSP)模块实现乘法器:FPGA 中通常集成了数字信号处理模块,这些模块专为处理数字信号而设计,具有高速度和低功耗的特点。

通过使用DSP 模块,可以实现高效、低功耗的乘法器。

3.使用乘法器IP 核:为了减少乘法器设计的复杂度,可以直接使用FPGA 厂商提供的乘法器IP 核。

这些IP 核经过优化,性能和面积都得到了很好的平衡。

为了提高FPGA 乘法器的性能,可以采用以下优化方法:1.流水线技术:通过将乘法运算分解为多个阶段,并行执行,可以提高乘法器的运行速度。

2.优化乘法算法:可以对乘法算法进行优化,例如使用快速傅里叶变换(FFT)等高效算法,降低乘法器的计算复杂度。

3.资源复用:通过合理分配FPGA 资源,实现乘法器的资源共享,可以提高乘法器的性能。

总之,FPGA 中乘法运算的设计与优化是数字电路设计中的一个重要环节。

通过了解FPGA 的基本原理,掌握乘法运算的方法和优化技巧,可以实现高效、低功耗的乘法器设计。

乘法器模块在FPGA中的实现

计非常灵活。因此 , 考虑到 F G P A的资源一般还算丰富的条件下 , 自己编写乘法器模块。 对于乘法器的设计 , 此前 已有很多相关的算法产生 , 但主流的乘法器归纳起来 主要有以下几类 , 包括传 统乘法器 , 移位相加乘法器 ,U L T乘法器 ,ot 算法乘法器。本文对传统乘法器 ,U Bo h L T乘法器 ,ot 算法乘 Bo h 法器 进行 了软 件设 计 , 用 Moe i 仿真 软件 进行 了仿 真 , Q ats 开 发平 台上基 于 ccoeI 利 dlm s 在 ur l uI yl l器件 对 程 n 序进 行 了综合 验证 , 最后 对几 种算 法 的乘 法器 的时钟 消耗 以及 器 件逻 辑 资源 的 占用 等情 况 进行 了 比较 和 分

传统乘 法器 和 B o ot h乘法 器 , 是这 是 以牺 牲硬 件资 源为前 提 的 , 以这种方 法 比较 适 于位 宽 较小 的乘法 的 但 所

运算 。虽然 此处 的 B oh算法 的运算 速度没 有体 现 出其优势 , 是经过 验 证 , 于 1 ot 但 对 6位 的乘法 运算 , ot B o 乘 法器 的运算 速度要 远 远高于 L T乘法 器 , 且此 种算 法 的硬 件 资源 的耗用 也 是可 以接受 的 。可见 , ot U 并 B oh算 法 的综 合优 势 明显 , 因此得 到更广 泛 的应 用 。

fpga中做乘法

FPGA中实现乘法运算的优化策略与方法在FPGA(Field-Programmable Gate Array,可编程逻辑门阵列)中实现乘法运算是一项基本但重要的任务。

乘法是数字信号处理、图像处理、通信系统等领域中常见的操作。

以下是在FPGA中实现乘法运算的详细讨论。

一、基本概念乘法运算通常是指两个数或变量相乘。

在二进制表示中,乘法被看作是位操作的一种,它逐位地对两个数进行相乘,然后将结果加在一起。

因此,乘法运算在硬件实现中通常涉及到二进制数的位操作。

二、硬件实现在FPGA中,乘法可以通过查找表(LUT)、加法器、移位器等硬件资源来实现。

1.查找表(LUT): 查找表是一种存储了预先计算结果的数据结构,可以用于快速查找和执行乘法。

例如,如果我们要实现一个4位乘以4位的乘法器,我们可以创建一个16行的查找表,其中每一行都存储了对应输入组合的乘法结果。

这样,我们只需要通过查找输入来获取乘法结果,大大提高了计算速度。

2.加法器和移位器: 对于非预计算乘法(例如大数乘法),我们通常使用加法和移位操作来逐步计算乘积。

在这种实现中,加法器用于计算中间的和,而移位器用于调整进位和数据的位置。

三、实现方法在FPGA中实现乘法有几种常见的方法:1.内嵌乘法器: 许多FPGA都提供了内嵌的硬件乘法器,可以直接使用这些乘法器来实现乘法操作。

这通常是最简单和最直接的方法,但可能不适合大规模或特定需求的乘法实现。

2.定制逻辑设计: 如果你需要大规模、高效率或者特定模式的乘法实现,你可能需要利用硬件描述语言(如VHDL或Verilog)来设计定制的乘法逻辑。

这需要深入理解数字电路设计和FPGA编程,但可以提供更高的性能和灵活性。

3.IP核(Intellectual Property Core): 一些FPGA供应商提供了预先设计好的IP核,这些核可以作为模块用于设计。

这些IP核通常经过优化以提供高性能和低功耗,但可能需要付费购买。

基于FPGA的阵列乘法器的设计与实现

基于FPGA的阵列乘法器的设计与实现本文先对乘法器进行了分析,然后用现场可编程门阵列(FPGA)实现了阵列乘法器,并分析了设计原理。

0 引言乘法是运算中的基本算法,应用也最为广泛。

在计算机中乘法最基本的操作就是移位相加,各类乘法最终都要归结为这一点。

早期计算机中为了简化硬件结构,采用串行的移位乘法方案,即多次执行“加法-移位”操作来实现。

这种方法并不需要很多器件。

然而串行方法毕竟太慢,自从大规模集成电路问世以来,出现了各种形式的并行乘法器,一部分即为流水式阵列乘法器。

1 二进制乘法器设有两个不带符号的M×N位二进制整数:点击图片查看大图点击图片查看大图它们的乘积用X和表示,按“手工计算”的方法给出就是:点击图片查看大图从中可以看出,只要a k≠0,输入量X就随着k的位置连续地变化,然后累加X2k。

如果a k=0,就可以忽略相应的转换相加。

以201×9为例,可以知道N=8,X=9,A=11001001。

当k由0开始递增时,对A的a k位进行分析,a0=1,则X20=9;a1=0,则X21=0;…a7=1,则X27=9×128=1152。

同时,将计算结果X2k:9,0,0,72,0,0,576,1152进行累加。

最终各部分结果之和即为201×9的乘积1809。

1.1 移位乘法器移位乘法器计算过程为:将A依次向右移一位,并检查其最低位a0,如果不为零,则将X与部分和相加,然后将X向左移一位;如果为零,则仅仅将X向左移一位。

移位时,X的低端和A的高端均补零。

可以看出由于第一个操作数X是并行形式的,而第二个操作数A是逐位形式的,所以刚才描述的乘法器也称为串行/并行乘法器。

如果两个操作数都是串行的,那么这一结构称为串行/串行乘法器。

这样的乘法器只需要一个全加器,但是计算乘积所需的时间更长。

1.2 阵列乘法器移位乘法器是通过牺牲时间来降低复杂性,还有一种方法通过增加复杂性来换取速度,称之为“阵列”,或者叫并行/并行乘法器。

基于FPGA的自顶向下乘法器电路设计

基于FPGA的自顶向下乘法器电路设计自顶向下乘法器电路设计基于现场可编程门阵列(Field-Programmable Gate Array,FPGA)技术,可以实现高速乘法运算。

本文将介绍自顶向下乘法器电路设计的原理和步骤,并对FPGA的优势进行探讨。

首先,需要了解自顶向下乘法器的原理。

自顶向下乘法器是一种通过将待乘数和乘数分解为高位和低位来进行连续乘法运算的方法。

该方法可以将两个N位的二进制数相乘,得到一个2N位的二进制数。

整个乘法过程可以分为以下步骤:1. 将乘数和待乘数分解为高位和低位,例如将N位的乘数A分解为A_high(高N/2位)和A_low(低N/2位),将N位的待乘数B分解为B_high和B_low。

2. 将A_high和B_high相乘得到P13. 将A_low和B_low相乘得到P24. 将A_high和B_low相乘得到P35. 将A_low和B_high相乘得到P46.将P1和P4相加得到P57.将P2和P3相加得到P68.将P5、P6和左移N/2位的P6相加得到结果。

接下来,我们将基于FPGA技术设计自顶向下乘法器电路。

首先,在设计中需要确定N的大小。

这取决于待乘数和乘数的位数。

假设待乘数和乘数的位数都为8位,则N为8然后,我们需要使用HDL(Hardware Description Language)语言(如VHDL或Verilog)来描述自顶向下乘法器的逻辑功能。

在设计中,我们将乘法器分割为多个模块,每个模块负责其中的一部分计算。

接下来,需要将HDL代码综合成逻辑电路,并进行约束和布局。

FPGA设备提供了专用的开发工具,可以将HDL代码综合成逻辑网表文件。

最后,验证设计的正确性和性能。

可以通过给定一组输入数据,对乘法器进行仿真,并检查输出是否与预期结果一致。

可以使用仿真工具或FPGA开发板上的调试接口进行仿真。

FPGA的优势在于其可编程性和并行性。

与专用的ASIC(Application-Specific Integrated Circuit)相比,FPGA可以在设计中进行修改和重编程,更加灵活。

基于FPGA的高速流水定点乘法器的设计

wad am eh d o e l ig hgh se d mutpirb sd o l x Vitx Fe a p aauswhc o d i po e t es e d t 5 M Hz. r to frai n i p e l il ae n Xin re l z e i a p rt ih c u m r v h p e o 1 0 l Ha el tt eVHDL o efrt ee e l f 4 2 i mutpira d ter uto y t ei h e t Th ut l rdein d h sb e v i h s cd o h x mpeo x 4 bt l il n h el fssh si t etx . em l i i sg e a en 2 e s s n pe

B O H编码部分 , O T 部分 积产生 , 分积压 缩 以及平 方 部

根求和 电路。乘数 首先 进行 BX) H编 码 , ( T 同时被 乘 数进行移位操作 , 完成 与 { , , , , } 一2 一1 0 12 的相乘 。然 后在部分 积产生模块 中根据 B OT 编码值选 择被乘 O H 数产生相应 的部分积 。部分积压缩模块将 部分积压缩 成两行 , 最后 由高速求 和 电路进行 求和 相加得 到最 终

维普资讯

第

" 期 2 0 9 月 0 年 7

计 算 机 技 术 与 发 展

COM PUTER TECHNOL OGY AND DEVELOPM ENT

Vo . 7 No. 【1 9 S p 2 0 e. 07

基于 F G P A的高 速流 水定 点乘 法器 的设计

吉 伟 , 士 坦 黄

( 西安微 电子技 术研 究所 , 西 西安 7 0 7 ) 陕 10 5

各种乘法器比较

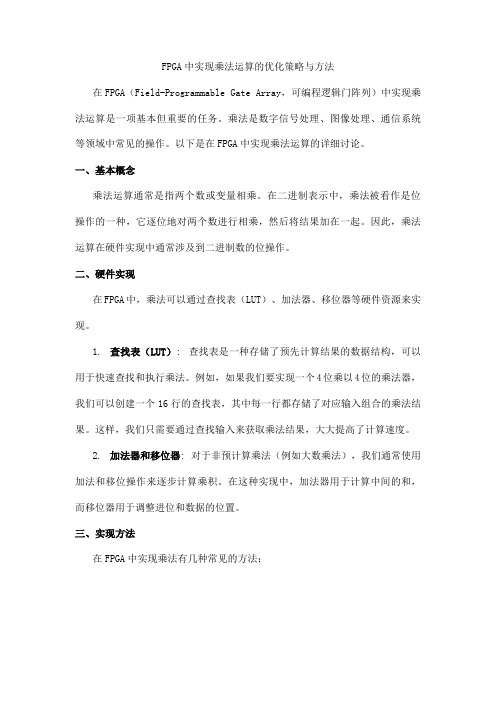

各种乘法器比较韦其敏08321050引言:乘法器频繁地使用在数字信号处理和数字通信的各种算法中,并往往影响着整个系统的运行速度。

如何实现快速高效的乘法器关系着整个系统的运算速度和资源效率。

本位用如下算法实现乘法运算:并行运算、移位相加、查找表、加法树。

并行运算是纯组合逻辑实现乘法器,完全由逻辑门实现;移位相加乘法器将乘法变为加法,通过逐步移位相加实现;查找表乘法器将乘积结果存储于存储器中,将操作数作为地址访问存储器,得到的输出数据就是乘法运算结果;加法树乘法器结合移位相加乘法器和查找表乘法器的优点,增加了芯片耗用,提高运算速度。

注:笔者使用综合软件为Quartus II 9.1,选用器件为EP2C70,选用ModelSim SE 6.1b进行仿真,对于其他的软硬件环境,需视具体情况做对应修改。

汇总的比较:详细实现过程:1.并行乘法器源代码:module Mult1(outcome,a,b);parameter MSB=8;input [MSB:1] a,b;output [2*MSB:1] outcome;assign outcome=a*b;endmodule资源耗用情况:ModelSim测试激励文件源代码:`timescale 10ns/1nsmodule Mult1_test();reg [8:1] a,b;wire [16:1] outcome;Mult1 u1(outcome,a,b); parameter delay=2;initialbegina=1;b=0;endinitial foreverbegin#delaya=a+1;b=b+1;if(outcome>=16'h0FFF)$stop;endendmodule仿真时序波形:结果分析:DE2-70拥有300个嵌入式硬件乘法器单元,Quartus II综合并行乘法器时自动采用嵌入式乘法器来实现,因此中和报表中仅耗用了一个LE单元和一个九位的嵌入式乘法器单元。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

三种高速乘法器的FPGA实现及性能比较

摘要:乘法是数字信号处理中重要的基本运算,在很大程度上影响着系统的性能。

本文将介绍三种高速乘法器实现原理:阵列乘法器、华莱士(WT)乘法器、布斯华莱士树超前进位乘法器。

而且通过FPGA技术实现了这三种乘法器,并对基于以上三种架构的乘法器性能进行了分析比较。

关键字:阵列乘法器,华莱士乘法器,超前进位乘法器,FPGA

1、引言

随着3G技术的发展,关于图像、语音、加密等数字信号处理技术随处可见,而且信号处理的实时性也要求越高。

实时性即是要求对信号处理的速度要快,而乘法器是数字信号处理中重要的基本运算,在很大程度上影响着系统的性能。

人们开始开发高速的乘法器。

以下将对三种乘法器:阵列乘法器、华莱士(WT)乘法器、布斯华莱士树超前进位乘法器进行原理分析,并用FPGA技术实现了这三种乘法器,对其结果进行了仿真,得出相应的性能比较。

2、阵列乘法器

2.1 阵列乘法器原理

硬件乘法器的常规设计是适用“串行移位”和“并行加法”相结合的方法,这种方法并不需要很多器件。

然而串行方法毕竟太慢,执行一次乘法的时间至少是执行一次加法时间的n倍,不能满足科学技术对高速乘法所提出的要求。

自从大规模集成电路问世以来,高速的单元阵列乘法器应运而生,出现了各种形式的流水线阵列乘法器,它们属于并行乘法器,提供了极快的速度。

阵列乘法器的运算过程如下:

第一:当乘数的位数字为1 时,我们可以将被乘数的值直接放置适当的位置。

而适当的位置是依乘数的第几个位和被乘数做运算之后所放的位置。

第二:当乘数的位数字为0 时,我们可以将0 放置适当的位置, 以作为部分乘积。

第三:我们利用笔和纸计算的乘法,在硬件中使用与门来实现。

例如:1000 ×1中,乘数1 和每一个被乘数的位都个别做与运算,其结果为1000 正是我们所要的结果。

由此可知我们只需用与门就可以完成我们所要的乘法。

第四:当部分乘积都运算完成后,使用加法来完成最终的乘法结果运算。

根据以上四点的说明,我们可以运用最简单、最直观的方式来描述固定点乘法器的电路描述。

我们使用与门来做部分积运算,使用全加器(Full adder)来运算部分积的最终结果。

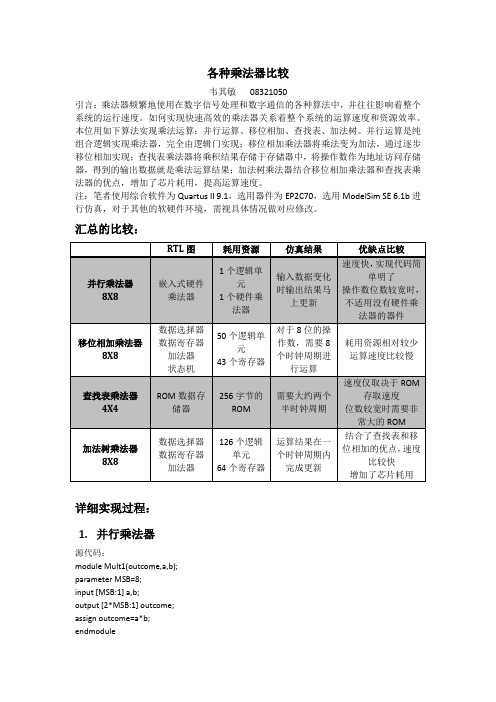

图1所示为有符号位的6×6固定点乘法器的架构图。

HA

FA HA

FA

FA

HA

FA FA FA

HA FA FA FA FA HA

FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA

FA

图1 6×6有符号位阵列乘法器乘法器架构图

2.2 阵列乘法器FPGA 仿真

在名为comult 的实体中设置mulc 和mulp 两个输入端口和一个prod 输出端口。

其中

mulc 代表被乘数,mulp 为乘数,二者均为6位。

乘积prod 是一个12位的结果,输入与输出端口的数据类型均为std_logic_vector 。

流程图如图2所示,仿真如图3所示。

图2 6x6有符号阵列乘法器流程图

图3 6x6有符号阵列乘法器仿真

3、华莱士乘法器原理

部分积相加, 若采用累加移位的方法, 速度太慢。

华莱士树算法(Wallace Tree

Algorithm )是部分积化简的一种树形算法。

它使乘法器的延时得到最大限度的缩短,但全加阵列的布局布线复杂度大为增加。

一个全加器有三个输入: A , B , C (进位) 和两个输出S , C ′(输出进位) , 3个输入对2个输

出而言是对称的, 即它们互相交换位置, 结果不会受影响。

如果把一串全加器简单排成一行, 它们之间进位线不连, 把这样一串全加器称为保留进位加法器(CSA ) , 它有以下特性: 三个输入数之和等于二个输出数之和, 即3个相加数每通过一次保留进位加法器, 其个数就减少1个。

Wallace 最早提出的方案就利用了这一特点:第一步将每列的部分积按三位进行分组,

每组通过使用全加器构成的CSA 部件,将加数的数目减少;第二步对第一步产生的结果仍按三位分组的方式将同权的伪和与局部进位信号通过CSA 部件进行处理,再次减少加数的数目,这种处理一直进行到最后只有两个输出为止。

对最后的伪和与局部进位通过进位传递加法器相加得出真正的结果。

在这种处理方式中,每列中求伪和的操作是并行完成的。

由于采用全加器作为加法部件,每次能将3个权为20的输入信号经处理后得到一个权为21的局部进位信号和一个权为20的伪和信号,这样操作数的数目减少1/ 3,将产生的中间伪和也按照这种方式处理,经过时间为O(log 3/ 2 N ) 的处理后可以得到最后的伪和与局部进位信号。

图16 华莱士树加法树示意图

我们来考虑一个44 位华莱士树乘法器的结构。

设被乘数为0123x x x x ,乘数为

0123y y y y 。

65432106543210Partial products

First stage Bit position

6

54321

06543210

Second stage Final adder FA

HA (a)

(b)(c)(d)

图17 44⨯位华莱士树乘法器实现图

图18 44⨯位华莱士树乘法器架构图

Full Adder (CSA)A B

Cout S Cin Cin A

B

S A

B

A Cin

B Cin Cout

图19 保留进位加法器(CSA)

Half Adder

A B

Cout S

图20 半加器 布斯算法(Booth ’s Algorithm )的做法是对乘数编码以计算出乘法运算的结果,主要

的想法在于乘数中连续的1,这些1会造成被乘数的连加。

但是,乘数01110又可表示为10000-00010,这样可将部分积减少为2个。

当我们遇到

乘数中连续的’1’时(从右往左看),第一个’1’减去被乘数,最后一个’1’后面的’0’则加上被乘数。

01111110001001000

000001001010010000000000010010

00000

111001001-+

+

+

-

+⨯部分积部分积乘数被乘数

布斯编码的核心在于对连续的’1’字串进行头、中、尾三段的分段处理(从右往左看)。

当然,’0’字串由于本身就无须进行运算,所以不必理会。

4、华莱士乘法器

先介绍阵列乘法器,我们用笔计算乘法时,第一个操作数为被乘数(multiplicand),第二个操作数为乘数(multiplier)。

而乘数中的每一个位和被乘数做相乘的运算后的结果称之为部分乘积(partial product),而将所有的部分乘积相加之后,其运算结果称为乘积(product)。

如:1000×1001为例,

multiplicand 1000

× multiplier × 1001

partial product 1000

partial product 0000

partial product 0000

partial product 1000

product 1001000

通过以上的示例我们可以发现如下四点:

第一:当乘数的位数字为1 时,我们可以将被乘数的值直接放置适当的位置。

而适当的

位置是依乘数的第几个位和被乘数做运算之后所放的位置。

第二:当乘数的位数字为0 时,我们可以将0 放置适当的位置, 以作为部分乘积。

第三:我们利用笔和纸计算的乘法,在硬件中使用与门来实现。

例如:1000 ×1中,

乘数1 和每一个被乘数的位都个别做与运算,其结果为1000 正是我们所要的结果。

由此可知我们只需用与门就可以完成我们所要的乘法。

第四:当部分乘积都运算完成后,使用加法来完成最终的乘法结果运算。

根据以上四点的说明,我们可以运用最简单、最直观的方式来描述固定点乘法器的电路

描述。

我们使用与门来做部分积运算,使用全加器(Full adder)来运算部分积的最终结果。

因为作加法时,会有进位问题,且上一位所产生的进位也非常重要,所以只有全加器能满足我们的加法要求。

图13所示为有符号位的6×6固定点乘法器的架构图。

HA FA HA FA FA HA FA FA FA HA FA FA FA FA HA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA FA 图13 6×6固定点乘法器架构图。