加法树乘法器

各种乘法器比较

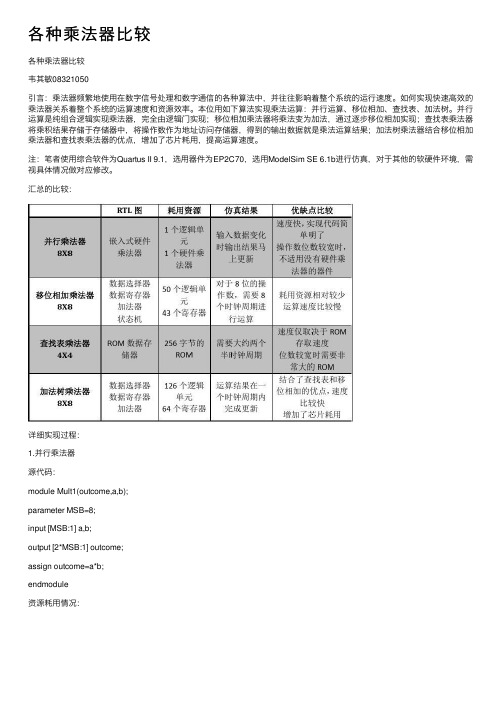

各种乘法器⽐较各种乘法器⽐较韦其敏08321050引⾔:乘法器频繁地使⽤在数字信号处理和数字通信的各种算法中,并往往影响着整个系统的运⾏速度。

如何实现快速⾼效的乘法器关系着整个系统的运算速度和资源效率。

本位⽤如下算法实现乘法运算:并⾏运算、移位相加、查找表、加法树。

并⾏运算是纯组合逻辑实现乘法器,完全由逻辑门实现;移位相加乘法器将乘法变为加法,通过逐步移位相加实现;查找表乘法器将乘积结果存储于存储器中,将操作数作为地址访问存储器,得到的输出数据就是乘法运算结果;加法树乘法器结合移位相加乘法器和查找表乘法器的优点,增加了芯⽚耗⽤,提⾼运算速度。

注:笔者使⽤综合软件为Quartus II 9.1,选⽤器件为EP2C70,选⽤ModelSim SE 6.1b进⾏仿真,对于其他的软硬件环境,需视具体情况做对应修改。

汇总的⽐较:详细实现过程:1.并⾏乘法器源代码:module Mult1(outcome,a,b);parameter MSB=8;input [MSB:1] a,b;output [2*MSB:1] outcome;assign outcome=a*b;endmodule资源耗⽤情况:ModelSim测试激励⽂件源代码:`timescale 10ns/1ns module Mult1_test();reg [8:1] a,b;wire [16:1] outcome;Mult1 u1(outcome,a,b); parameter delay=2;initialbegina=1;b=0;endinitial foreverbegin#delaya=a+1;b=b+1;if(outcome>=16'h0FFF)$stop;endendmodule仿真时序波形:DE2-70拥有300个嵌⼊式硬件乘法器单元,Quartus II综合并⾏乘法器时⾃动采⽤嵌⼊式乘法器来实现,因此中和报表中仅耗⽤了⼀个LE单元和⼀个九位的嵌⼊式乘法器单元。

8位wallace树乘法器

8位wallace树乘法器Wallace树是一种常见的乘法器,它可以用于高效地执行大数乘法运算。

它的名字来源于其发明者Wallace。

Wallace树乘法器是通过将乘法运算分解为多个部分,然后以并行的方式计算每个部分的结果来实现的。

每个部分接收两个部分乘积(Partial Product)和一个进位位(Carry-in),并计算出一个部分积(Partial Product)和一个进位位(Carry-out)。

具体来说,Wallace树乘法器由三个主要部分组成:部分乘法器(Partial Multiplier)、部分积生成器(Partial Product Generator)和部分积压缩器(Partial Product Compressor)。

部分乘法器是Wallace树乘法器的基本单元,用于计算两个二进制数的部分积。

每个部分乘法器由两个二进制数位相乘得到两个部分积和一个进位位。

部分乘法器之间通过进位位进行连接。

部分积生成器用于生成所有的部分乘积。

它接收两个输入数和多个进位位,并生成部分积。

部分积压缩器将多个部分乘积和进位位进行压缩,以得到最终的乘积。

它使用一种特殊的编码方式来表示乘积,并通过对部分积和进位位的运算进行压缩。

压缩后的结果被输出作为乘法器的最终输出。

Wallace树乘法器的优势在于它可以最大限度地提高乘法运算的并行性,从而提高乘法器的计算速度。

同时,它还可以减少乘法器所需的芯片面积和功率消耗。

然而,由于Wallace树乘法器存在部分积生成和部分积压缩的过程,因此它的面积和延迟仍然会受到影响。

为了 further enhance 实现的效率,还有一些改进的Wallace树结构,如Dadda树乘法器和Wallace树的变种。

这些改进可以进一步减少乘法器的延迟和面积。

另外,还可以使用Wallace树乘法器来实现更高位数的乘法运算,例如16位、32位甚至更高位数。

构建更高位数的Wallace树乘法器需要合理地设计其结构和逻辑电路,以确保乘法运算的正确性和高效性。

FPGA加法器乘法器

FPGA加法器设计加法作为一种基本运算,大量运用在数字信号处理和数字通信的各种算法中。

由于加法器使用频繁,因此其速度往往影响着整个系统的运行速度。

如果可以实现快速加法器的设计,则可以提高整个系统的处理速度。

加法运算是最基本的算数运算,在多数情况下,无论是乘法、除法还是减法以及FFT等运算,最终都可以分解为加法运算来实现,因此对加法运算的实现进行一些研究是非常必要的。

实现加法运算有如下一些方法:(1)级连加法器;(2)并行加法器;(3)超前进位加法器;(4)流水线加法器。

1、级连加法器级连加法器是由1位全加器级连构成的,本位的进位输出作为下一级的进位输入。

级连加法器的结构简单,但N位级连加法运算的延时是1为全加器的N倍,延时主要是由于进位信号级连造成的。

在需要高性能的设计中,这种结构不宜采用。

module add_jl(sum,cout,a,b,cin);output [3:0] sum;output cout;input [3:0] ina,inb;input cin;wire [3:1] c;full_add1 f0 (ina[0],inb[0],cin, sum[0],c[1]); //级连描述full_add1 f1 (ina[1],inb[1],c[1],sum[1],c[2]);full_add1 f2 (ina[2],inb[2],c[2],sum[2],c[3]);full_add1 f3 (ina[3],inb[3],c[3],sum[3],cout);module full_add1(ina,inb,cin,sum,cout); //1位全加器input ina,inb,cin;output sum,cout;wire s1,m1,m2,m3;and (m1,ina,inb),(m2,inb,cin),(m3,ina,cin);xor (s1,a,b),(sum,s1,cin);or (cout,m1,m2,m3);endmodule2、并行加法器并行加法器可采用Verilog语言的加法运算符直接描述,或称为数据流描述方式,实现容易,其运算速度快,但耗费资源多,尤其是当加法运算的位数较宽时,其耗用资源将会大大增加。

乘法器的工作原理

乘法器的工作原理

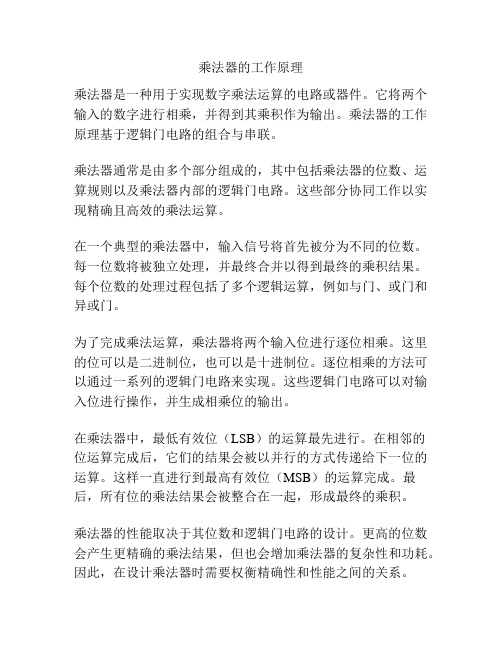

乘法器是一种用于实现数字乘法运算的电路或器件。

它将两个输入的数字进行相乘,并得到其乘积作为输出。

乘法器的工作原理基于逻辑门电路的组合与串联。

乘法器通常是由多个部分组成的,其中包括乘法器的位数、运算规则以及乘法器内部的逻辑门电路。

这些部分协同工作以实现精确且高效的乘法运算。

在一个典型的乘法器中,输入信号将首先被分为不同的位数。

每一位数将被独立处理,并最终合并以得到最终的乘积结果。

每个位数的处理过程包括了多个逻辑运算,例如与门、或门和异或门。

为了完成乘法运算,乘法器将两个输入位进行逐位相乘。

这里的位可以是二进制位,也可以是十进制位。

逐位相乘的方法可以通过一系列的逻辑门电路来实现。

这些逻辑门电路可以对输入位进行操作,并生成相乘位的输出。

在乘法器中,最低有效位(LSB)的运算最先进行。

在相邻的

位运算完成后,它们的结果会被以并行的方式传递给下一位的运算。

这样一直进行到最高有效位(MSB)的运算完成。

最后,所有位的乘法结果会被整合在一起,形成最终的乘积。

乘法器的性能取决于其位数和逻辑门电路的设计。

更高的位数会产生更精确的乘法结果,但也会增加乘法器的复杂性和功耗。

因此,在设计乘法器时需要权衡精确性和性能之间的关系。

总之,乘法器是一种通过组合逻辑门电路来实现数字乘法运算的电路或器件。

它将输入信号分解为不同的位数,并使用逻辑门电路逐位相乘。

最后,将每个位的乘法结果合并在一起,得到总体的乘积输出。

相加器 相乘器

相加器相乘器

相加器和相乘器是数字电路中常见的两种基本电路。

相加器用于将两个或多个二进制数相加,而相乘器则用于将两个或多个二进制数相乘。

它们都是数字电路中非常重要的组件,被广泛应用于各种数字系统中。

相加器的基本原理是将两个二进制数的每一位相加,得到一个结果和一个进位。

这个结果和进位再参与下一位的计算,直到所有位都被计算完成。

相加器可以用于实现加法器、减法器和比较器等功能。

相乘器的基本原理是将两个二进制数的每一位相乘,得到一个结果和一个进位。

这个结果和进位再参与下一位的计算,直到所有位都被计算完成。

相乘器可以用于实现乘法器、除法器等功能。

现代数字系统中常常使用带符号数、浮点数等,这些都需要更加复杂的相加器和相乘器来实现。

此外,相加器和相乘器在硬件实现上也有不同的方案,例如使用二进制加法器或绝对值器来实现加法器,使用 Booth编码或Wallace树来实现乘法器等。

总的来说,相加器和相乘器是数字电路中非常重要的基本电路,其应用广泛,其实现方式也多种多样,因此对于数字系统的学习和应用来说,了解和掌握相加器和相乘器的原理和实现方法是非常必要的。

- 1 -。

乘法器工作原理

乘法器工作原理

乘法器是一种电子设备,用于实现两个数字(或模拟)信号的乘法运算。

其工作原理可以简单地描述如下:

1. 输入信号:乘法器通常有两个输入端,分别用于接收待相乘的数字信号A和B。

2. 位展开:乘法器将输入信号A和B进行位展开操作,即将

每一个输入位(或字节)进行分离和独立处理。

这可以通过触发器、逻辑门电路等实现。

3. 部分乘积计算:对每一对输入位进行乘法运算,并将结果存储在部分乘积寄存器中。

这可以通过加法器电路来实现,其中每一个乘积被加到累加器中。

4. 乘积累加:将所有的部分乘积相加得到最终的乘积结果。

这可以通过多级加法器电路来实现。

一般来说,乘法器采用树形结构或布斯-舍乘法算法(Booth's algorithm)来提高计算效率。

5. 结果输出:输出端给出乘法运算的结果。

根据需求,这个结果可以是数字信号,模拟电压或电流等形式。

乘法器的工作原理可以根据底层电路和算法的不同而有所变化。

现代的乘法器采用复杂的电路设计和优化算法,以实现更高的运算速度和精度。

乘法器原理

乘法器原理

乘法器是一种用于执行乘法运算的数字电路。

它通常由多个逻辑门、寄存器和时钟信号组成。

乘法器的主要原理是将两个输入数(被乘数和乘数)进行相乘,然后输出它们的乘积。

乘法器的输入是一系列位(比特),每个位代表一个二进制数。

这些输入位通过逻辑门来实现不同位上的相乘。

一般来说,较高位的输入乘数与较低位的被乘数相乘后,得到的乘积需要左移若干位。

这个左移操作可以通过使用寄存器和时钟信号来完成。

乘法器可以分为多种类型,其中最常见的是布斯乘法器和Wallace树乘法器。

布斯乘法器通过将被乘数和乘数进行分割,并使用部分积和约化乘法器来实现乘法运算。

Wallace树乘法

器是一种高效的乘法器类型,它通过将乘法操作转化为加法操作来提高运算速度。

这种乘法器通常使用布斯乘法器和连锁加法器来实现。

乘法器的输出是乘法的结果,通常也是一系列位(比特)。

输出可以进一步用于其他计算或者存储在寄存器中。

同时,乘法器也可以进一步扩展为多位乘法器,用于执行更大位数的乘法操作。

综上所述,乘法器是一种将两个输入数进行相乘的数字电路。

它的原理是利用逻辑门、寄存器和时钟信号来实现乘法运算。

乘法器可以分为不同类型,其中最常见的是布斯乘法器和

Wallace树乘法器。

乘法器的输出是乘法的结果,通常用于其他计算或者存储在寄存器中。

乘法器

0

1 0 1 1

1

1

1

1

1

Company Logo

一位全加器的实现(表达式) 由真值表,可得: S=Add_1 xor Add_2 xor cin; cout=(Add_1 and Add_2) or (Add_1 and cin )or (Add_2 and cin);

所以,一位全加器的实现需要的器件有: 3输入的异或门(1个) 3输入的或门(1个);2输入的与门(3个)

Company Logo

Company Logo

串并乘法原理与步骤

假设被乘数X=1101,乘数Y=1011,步骤如下: ①1101*1=1101 ,result=1 1 0 1(放在锁存器中) ②1101*1=1101 sum=1101,把result的值左移 一位,即0 1 1 0,结果与sum相加(一位相加)

Company Logo

一位全加器的实现(电路)

Company Logo

串-并乘法器的实现

LOGO

Company Logo

加法树乘法器 加法树乘法器的基本 思想也是移位相加,不 过,它是先移位(*2), 后相乘.而且它是同时移 位。 优点:速度快 缺点:耗资源

Company Logo

混合加法器

混合加法器就是把移位相加与查找表结合起来。假设 现在把1101与1011相乘。用两位相乘实现。步骤如下: 1. 1101与11相乘,把1101看成1100+01。这样, 1101*11=(11*11)>>2+01*11; 两位乘法直接在查找表中找到,不用进行运算。所以,只 需 进行加法运算; 2.1101与10(高位)相乘,方法与1相同; 3.把2的结果移2位,再与1的结果相加。 这样,在查找表中只需保存22 *22,同样是4位的乘法 器,比单纯用查找表法( 24 * 24 ),资源少了不少。当 然在速度也要慢一下。所以混合加法器的速度与资源的利 用都是介于查找表与移位加法这两种方法之间

8位wallace树乘法器

8位wallace树乘法器Wallace树是一种高效的乘法器结构,可用于实现大规模数字乘法运算。

该结构最早由英国工程师Chris Wallace在1964年提出,被广泛应用于数字信号处理、图像处理和通信等领域。

一、Wallace树的原理Wallace树的核心思想是通过将乘法操作分解为多个部分并行处理的方式来提高运算速度。

它将输入的两个乘数进行划分,生成不同位数的中间乘积,并通过级联的全加器树将这些中间乘积相加得到最终结果。

1. 乘数划分Wallace树将乘数划分为几个部分,通常是三位一组或四位一组。

每个部分的位数必须相等或相差不超过1位。

划分后的乘数通过与被乘数相乘,得到中间的部分积。

2. 部分积压缩为了减少运算的复杂度,Wallace树采用了Booth编码来压缩部分积。

Booth编码是一种将乘数表示为一组位编码的方法,可以有效减少乘法操作的次数。

通过Booth编码,可以将多个部分积合并为更少的部分积。

3. 全加器树将压缩后的部分积进行累加,采用级联的全加器树结构。

全加器树将中间部分积按位相加,并将进位传递到下一级。

这样,可以在每个时钟周期中完成多个位的相加操作,从而提高计算速度。

二、Wallace树的优势1. 并行计算:通过将乘法操作分解为多个部分,并行处理每个部分,提高了计算效率。

2. 低延迟:Wallace树的计算延迟比传统的乘法器结构更低,能够在更短的时间内完成乘法运算。

3. 较低的资源占用:相比于其它乘法器结构,Wallace树所需的逻辑门数量和面积较小,对硬件资源的占用较少。

4. 支持多种数据宽度:Wallace树可以灵活地适应不同位宽的乘法运算,可扩展性较好。

5. 可用于流水线设计:Wallace树可以很好地与流水线技术结合,进一步提高计算速度。

三、应用领域1. 数字信号处理:Wallace树广泛用于数字信号处理算法中,如快速傅里叶变换(FFT)和离散余弦变换(DCT)等。

2. 图像处理:在图像处理算法中,如图像变换、图像滤波等操作中,需要大量的乘法运算,Wallace树可以提供高效的乘法器实现。

乘法器工作原理

乘法器工作原理

乘法器是一种用于进行乘法运算的电子元件或电路。

它的工作原理基于二进制乘法算法,并通过逻辑门、触发器、加法器等组合逻辑电路的实现。

乘法器通常由多个部分组成,包括乘法操作单元、加法器、部分积生成器和积累器。

乘法操作单元是乘法器的核心部分,它用于对输入的两个二进制数进行逐位相乘。

乘法操作单元通常由与门、异或门和与非门组成,通过对二进制数的各位进行与、异或和与非运算,生成乘积的各位。

加法器用于对乘积的各位进行相加。

在乘法操作单元中,生成的各位乘积在加法器中进行相加,并将进位传递给下一位。

这样,就可以得到完整的乘法结果。

部分积生成器的作用是将乘法操作单元的输出整理成方便相加的形式。

它常使用位移寄存器或移位寄存器来实现,对每一位的乘积进行相应的位移,以便将乘法操作单元输出的部分积加到正确的位置上。

积累器用于存储并累加相乘后的部分积,最终得到完整的乘法结果。

积累器通常是一组触发器或寄存器,每一位保存一个位乘积,并通过时钟信号进行更新和累加操作。

通过组合以上的部件,乘法器可以按照二进制乘法算法对输入

的两个二进制数进行相乘,并输出对应的乘积。

乘法器可以应用于各种数字电路和计算机系统中,例如乘法指令执行、信号处理和图像处理等领域。

乘法器

乘法器简介乘法器在当今数字信号处理以及其他诸多应用领域中起着十分重要的作用。

随着科学技术的发展,许多研究人员已经开始试图设计一类拥有更高速率和低功耗,布局规律占用面积小,集成度高的乘法器。

这样,就能让它们更加适用于高速率,低功耗的大规模集成电路的应用当中。

通常的乘法计算方法是添加和位移的算法。

在并行乘法器当中,相加的部分乘积的数量是主要的参数。

它决定了乘法器的性能。

为了减少相加的部分乘积的数量,修正的Booth算法是最常用的一类算法。

为了实现速度的提高Wallace树算法可以用来减少序列增加阶段的数量。

我们进一步结合修正的booth算法和Wallace树算法,可以看到将它们集成到一块乘法器上的诸多优势。

但是,随着并行化的增多,大量的部分乘积和中间求和的增加,会导致运行速度的下降。

不规则的结构会增加硅板的面积,并且由于路由复杂而导致中间连接过程的增多继而导致功耗的增大。

另一方面串并行乘法器牺牲了运行速度来获得更好的性能和功耗。

因此,选择一款并行或串行乘法器实际上取决于它的应用性质。

在本文中,我们将介绍乘法算法以及在应用结构方面的速度比较,占用面积,功率和这些情况的组合绩效指标。

乘运算对于一个N比特的被乘数和一个N比特的乘数相乘的算法如下图所示:Y=Yn-1 Yn-2.....................Y2 Y1 Y0 被乘数X=Xn-1 Xn-2.....................X2 X1 X0 乘数例如: 1101 4-bits1101 4-bits110100001101110110010101一般来说Y=Yn-1Yn-2....................... Y2Y1Y0X=Xn-1Xn-2 (X2X1X0)2Yn-1X0 Yn-2X0 Yn-3X0 ……Y1X0 Y0X0Yn-1X1 Yn-2X1 Yn-3X1 ……Y1X1 Y0X1Yn-1X2 Yn-2X2 Yn-3X2 ……Y1X2 Y0X2… … … ……. …. …. …. ….Yn-1Xn-2 Yn-2X0 n-2 Yn-3X n-2 ……Y1Xn-2 Y0Xn-2Yn-1Xn-1 Yn-2X0n-1 Yn-3Xn-1 ……Y1Xn-1 Y0Xn-1---------------------------------------------------------------------------------------------------------------------- P2n-1 P2n-2 P2n-3 P2 P1 P0“与”门被用来产生部分乘积,如果被乘数是N比特,乘数是M比特,那么就会产生N*M个部分积,然而在不同结构和类型的乘法器当中,部分乘积的产生方式是不同的。

乘法器原理

乘法器原理在现代科技中,乘法器是非常重要的一种电子元件,它可以实现数字信号的乘法运算,广泛应用于各种计算机、通信、控制等领域。

本文将介绍乘法器的工作原理、分类以及应用。

一、乘法器的工作原理乘法器是一种数字电路,它的主要作用是实现数字信号的乘法运算。

在乘法器中,输入信号经过一系列的逻辑门电路处理后,输出结果为两个输入信号的乘积。

乘法器的基本原理可以用以下公式表示: A × B = C其中,A和B为输入信号,C为输出结果。

乘法器的工作原理可以分为两种类型:串行和并行。

串行乘法器是将两个输入信号分别进行位移和加法运算,最终得到输出结果。

而并行乘法器则是将两个输入信号分别进行分解和加法运算,最终得到输出结果。

两种类型的乘法器均采用逻辑门电路实现,具体实现方式有多种。

二、乘法器的分类根据乘法器的不同实现方式,可以将其分为以下几种类型:1. 串行乘法器串行乘法器是一种最简单的乘法器,它采用逐位相乘的方式实现。

串行乘法器的输入信号经过位移和加法运算后,得到输出结果。

串行乘法器的优点是结构简单,适合于低速应用。

但是,由于其逐位相乘的方式,其速度较慢,不适合于高速应用。

2. 并行乘法器并行乘法器是一种较为复杂的乘法器,它采用分解和加法运算的方式实现。

并行乘法器的输入信号分别进行分解,然后进行加法运算,得到输出结果。

并行乘法器的优点是速度快,适合于高速应用。

但是,由于其结构较为复杂,相对于串行乘法器来说,成本较高。

3. Booth乘法器Booth乘法器是一种改进的串行乘法器,它采用位移和加减运算的方式实现。

Booth乘法器的输入信号经过位移和加减运算后,得到输出结果。

Booth乘法器的优点是速度快,适合于高速应用。

但是,由于其结构较为复杂,相对于串行乘法器来说,成本较高。

4. Wallace树乘法器Wallace树乘法器是一种改进的并行乘法器,它采用分解和加法运算的方式实现。

Wallace树乘法器的输入信号分别进行分解,然后进行加法运算,得到输出结果。

算术逻辑运算部件构造

算术逻辑运算部件构造算术逻辑运算部件是指在计算机硬件中用于实现算术和逻辑运算的部件。

这些部件可以执行各种算术运算(如加法、减法、乘法、除法)和逻辑运算(如与、或、非)。

在计算机中,算术逻辑运算部件是非常重要的,它们负责执行各种数学运算和逻辑判断,是计算机运行的基础。

这些部件通常由逻辑门电路组成,可以实现各种复杂的数学运算和逻辑判断。

算术逻辑运算部件通常包括加法器、减法器、乘法器、除法器、逻辑门电路等。

这些部件可以单独使用,也可以组合在一起实现更复杂的功能。

下面来详细介绍一下几种常见的算术逻辑运算部件。

1. 加法器加法器是计算机中常用的算术逻辑运算部件之一,用于实现两个数的加法运算。

加法器一般由半加器和全加器组成。

半加器用于实现单位数的二进制加法,而全加器可以实现多位数的二进制加法。

加法器的输入是两个二进制数和一个进位位,输出是一个二进制数和一个进位位。

2. 减法器减法器也是计算机中常用的算术逻辑运算部件之一,用于实现两个数的减法运算。

减法器一般由半减器和全减器组成。

半减器用于实现单位数的二进制减法,而全减器可以实现多位数的二进制减法。

减法器的输入是两个二进制数和一个借位位,输出是一个二进制数和一个借位位。

3. 乘法器乘法器是计算机中用于实现两个数的乘法运算的部件。

乘法器可以实现各种乘法操作,如加法器和减法器一样,乘法器也可以由多个乘法位相加器组成。

乘法器的输入是两个二进制数,输出是一个二进制数。

4. 除法器除法器是计算机中用于实现两个数的除法运算的部件。

除法器需要实现除法的所有步骤,包括除法法则、被除数和除数的对齐、试商、加减、取商和取余等操作。

除法器的输入是一个二进制被除数和一个二进制除数,输出是一个二进制商和一个二进制余数。

5. 逻辑门电路逻辑门电路是计算机中用于实现逻辑运算的部件,包括与门、或门、非门等。

与门实现逻辑与运算,或门实现逻辑或运算,非门实现逻辑非运算。

逻辑门电路一般由晶体管、集成电路等元器件组成,可以实现各种逻辑运算。

wallace树结构乘法器

wallace树结构乘法器摘要:1.概述:Wallace 树结构乘法器2.原理:Wallace 树结构和二进制数乘法3.应用:高效地实现二进制数乘法4.优势:降低乘法器的硬件复杂度5.总结:Wallace 树结构乘法器的重要性正文:1.概述:Wallace 树结构乘法器Wallace 树结构乘法器是一种基于Wallace 树结构的二进制数乘法器,它可以高效地实现二进制数乘法。

在计算机科学和工程领域,乘法器的设计和实现至关重要,因为它们直接影响到计算速度和硬件复杂度。

Wallace 树结构乘法器正是为了解决这些问题而提出的。

2.原理:Wallace 树结构和二进制数乘法Wallace 树,又称为Wallace-Kerr 树、Kerr-McMillan 树或Wallace-Kerr-McMillan 树,是一种特殊的树结构,用于实现二进制数乘法。

它的原理是利用树的层级结构,将二进制数的乘法转化为加法。

具体来说,Wallace 树结构乘法器将两个二进制数按位进行相乘,并通过树的层级结构逐级计算乘积,最终得到结果。

3.应用:高效地实现二进制数乘法Wallace 树结构乘法器在计算机科学和工程领域具有广泛的应用。

它可以高效地实现二进制数乘法,尤其是在大规模并行计算中,可以显著提高计算速度。

此外,Wallace 树结构乘法器还可以降低乘法器的硬件复杂度,减少硬件资源消耗,提高系统性能。

4.优势:降低乘法器的硬件复杂度Wallace 树结构乘法器相较于传统的二进制数乘法器具有明显的优势。

它能够降低乘法器的硬件复杂度,减少乘法器的门电路数量。

这使得Wallace 树结构乘法器在实际应用中具有更高的性能和更低的成本。

5.总结:Wallace 树结构乘法器的重要性Wallace 树结构乘法器作为一种高效的二进制数乘法器,对于计算机科学和工程领域具有重要的意义。

它不仅可以提高计算速度,还可以降低硬件复杂度和成本。

8位wallace树乘法器

8位wallace树乘法器Wallace树乘法器是一种高效且快速的乘法器,可以在数字信号处理和数字信号通信系统中广泛应用。

它能够从两个输入数中计算出它们的乘积,此外还可以扩展到更多输入。

Wallace树乘法器的理论基础是将两个二进制数字相乘时的竖式乘法过程进行优化。

这个过程可以分解为三个步骤:部分积生成、部分积压缩和部分积的加法。

首先是部分积生成。

在竖式乘法中,每个输入数的每个位都要与另一个输入数的每个位相乘。

在Wallace树乘法器中,这个步骤的计算是由多个列决定的,因此需要将输入数分为列,每一列只与另一列相乘。

这个过程可以通过一个加2、除3的运算来完成。

接下来是部分积压缩。

在部分积生成之后,会有很多位被计算出来,其中有一些位是不需要的,需要通过压缩过程来减少所需位数。

压缩过程可以通过适当的数码约减和移位操作来完成。

最后是部分积的加法。

这个过程需要将部分积中的所有位相加,得出最终的乘积结果。

在Wallace树乘法器中,这个过程由多个加法器级联组成,可以在同一时间完成多个加法操作。

除了上述三个步骤,还需要考虑如何组成Wallace树乘法器的逻辑电路。

Wallace树乘法器的核心是一个数位矩阵,其中每个位置都对应于不同的组合。

矩阵的行列数取决于输入数的位数,因此需要在设计中灵活选择相应的行列数。

在Wallace树乘法器中,还需要考虑信号的流向和数据的缓存。

信号应该只在特定的时间和位置上才能传输,而数据的缓存可以减少电路的延迟和功耗。

总之,Wallace树乘法器是一种高效且快速的乘法器,能够广泛应用于数字信号处理和数字信号通信系统中。

它的实现需要考虑许多因素,包括部分积生成、部分积压缩、部分积的加法、逻辑电路的构建、信号的流向和数据缓存等。

通过合理的设计和优化,可以实现高效的Wallace树乘法器。

加法树乘法器原理

加法树乘法器原理咱们先来说说乘法是个啥。

你看啊,乘法其实就是相同加数求和的简便运算。

比如说3×4,那就是4个3相加,或者3个4相加嘛。

但是呢,要是数字大一点,一个一个加可就太麻烦啦,这时候加法树乘法器就闪亮登场啦。

加法树乘法器就像是一个超级智慧的小助手,它把乘法运算变成了一种有规律的加法组合。

想象一下,咱们有两个数字要相乘,比如说5和6。

加法树乘法器可不是傻乎乎地把5加6次或者6加5次哦。

它会把这个过程变得特别巧妙。

这个加法树乘法器呢,它会先把这两个数字拆分开来。

就像把5拆成1 + 1+ 1+ 1+ 1,把6拆成1+ 1+ 1+ 1+ 1+ 1。

然后呢,它开始像搭积木一样构建这个加法树。

它会先把小的加法组合起来,比如说先把两个1加起来得到2,然后再把这个2和其他的1相加,慢慢构建出更大的和。

这个过程就像是一群小数字在开派对,它们一个一个地组合起来,从最小的单元开始,最后变成一个大大的结果。

比如说,在计算5×6的时候,它可能先算出2×3,然后再通过一些巧妙的加法组合,把这个结果扩大到5×6的结果。

你可以把加法树乘法器想象成一个超级有耐心的厨师。

他要做一道乘法大餐,但是他不是一股脑地把所有食材都扔进去,而是先把小食材组合成小配菜,然后再把小配菜组合成大菜。

比如说,他先把一个小洋葱和一个小胡萝卜组合成一个小菜,然后再把几个小菜组合成一道完整的菜。

而且哦,加法树乘法器还有一个很厉害的地方,就是它可以根据数字的特点来调整自己的组合方式。

如果是两个偶数相乘,它可能就会先把这两个数字都除以2,然后算出结果再乘以4呢。

就像走捷径一样,特别聪明。

再说说这个加法树的结构吧。

它就像是一棵倒着的树,树根就是最后的结果,而树枝呢,就是那些小的加法组合。

每个树枝都是从最小的1开始慢慢生长起来的,最后汇聚到树根。

这个原理其实也体现了一种化繁为简的智慧。

它告诉我们,即使是看起来很复杂的乘法运算,也可以通过巧妙的分解和组合变成一系列简单的加法。