SOPC实验报告

sopc实验心得

sopc实验心得

在进行SOPC(系统级可编程器件)实验的过程中,我深刻体会到了它的强大和灵活性。

SOPC是一种基于现场可编程门阵列(FPGA)技术的系统设计方法,它将硬件与软件相结合,可以实现高度集成和可重构的设计。

在实验中,我首先学习了SOPC的基本概念和原理,了解了它的组成部分以及各个组件之间的连接方式。

然后,我利用Quartus II软件进行了仿真和综合,将设计的硬件描述语言(HDL)代码转化为FPGA可以理解的形式。

通过仿真,我可以预先验证设计的正确性,并对其进行修改和优化。

接着,我进行了FPGA的编程和配置,将设计好的逻辑电路加载到FPGA芯片中。

通过这一步骤,我可以将自己的设计直接在硬件上实现,并进行实时的测试和调试。

这种即时性和灵活性是SOPC的一个重要优点,它使得我们能够更加高效地进行系统级设计和验证。

在SOPC实验中,我还学习了使用Nios II软核处理器进行嵌入式系统设计。

Nios II是一款可编程的32位RISC处理器,可以根据需求进行定制和配置。

通过Nios II,我可以在FPGA上实现复杂的嵌入式系统,并编写C语言程序进行控制和操作。

总的来说,SOPC实验让我深入了解了系统级可编程器件的原理和应用。

通过实践,我学会了使用Quartus II软件进行FPGA设计和配置,掌握了硬件描述语言

和嵌入式系统的开发方法。

这些知识和技能对我未来的学习和工作都具有重要的意义,我相信在不久的将来,SOPC技术将会在各个领域得到广泛应用。

EDA技术——SOPC设计“hello world”

昆明理工大学信息工程与自动化学院学生实验报告( 201—201学年 第 学期 )课程名称:EDA 技术 开课实验室: 年 月 日 年级、专业、班 学号 姓名 成绩 实验项目名称 SOPC 设计“hello world ”实验 指导教师教师评语教师签名:年 月 日一、实验目的通过本实验具体学习SOPC 开发流程。

二、实验设备1、 带有windows 操作系统,quartusII ,niosII 软件的PC 机台。

2、 FPGA 实验箱及电源线,下载线。

三、实验要求熟悉SOPC 从定制cpu 到nios 软核内程序编写的整个流程。

四 实验原理利用QuartusII 中的SOPCbuilder 来定制cpu ,然后配合niosII ,来实现一个完整的嵌入式系统功能,这是不同于FPGA 的开发方式。

五、实验步骤1、 按照前面实验在QuartusII 中建立工程,在TOOLs 菜单中选择SOPC Builder ,如图 3.1。

图3.1 建立工程✧新工程名命名为SOPC。

✧建完这个工程后,首先建一个原理图文件。

✧File->new->Block Diagram/Schematic File,通过此操作建好一个原理图文件,如图3.2所示。

图3.2 建立原理图文件2、定制CPU,参照上图,有一个图标,点击它打开SOPC builder,打开后,在弹出的界面system name后填写名字,这里写的是cpu,自己可以起其他名字,然后点ok,如图 3.3。

图 3.3 SOPC builder 界面1) 构建处理器模块:处理器就是用来做解释程序,运算等操作,图中左栏可以看到,Nios II Processer选项,双击后弹出处理器的属性选项框,我们自己设置参数,来定制所需的处理器,如图 3.4。

图 3.4 处理器属性框✧这里为我们提供了三种类型的CPU,Nios II/e 占用资源最少600-800LEs,功能也最简单,速度最慢。

《SOPC技术》课程实验报告模板

《SOPC技术》课程实验报告姓名:学号:班级:同组者:指导教师:高金定信息科学与工程学院2013-2014学年第一学期《SOPC技术》课程实验报告学生姓名:所在班级:指导教师:高金定老师记分及评价:一、实验名称实验1:基于LPM的正弦信号发生器的设计二、任务及要求【任务】在QuartusII平台上,采用查找表的设计方法,利用LPM兆功能模块,完成64点(8位)的正弦信号发生器的设计。

正弦信号发生器结构框图如下:【要求】1.数据存储ROM和地址信号发生器均由LPM模块实现。

2.在Quartus II软件上进行时序仿真。

3.利用Signal Tap II嵌入式逻辑分析仪进行在线测试与分析。

(此步需使用实验箱,并且要确保实验箱与电脑处于在线可下载状态)【思考】1.编写DAC0832数模转换程序,利用示波器观察输出信号波形。

2.如何在此基础上设计方波、三角波等信号发生器?如何实现波形幅度等参数可调?三、实验程序(原理图)四、仿真及结果分析五、硬件验证1、选择模式:2、引脚锁定情况表:六、小结《SOPC技术》课程实验报告学生姓名:所在班级:指导教师:高金定老师记分及评价:一、实验名称实验2:基于DSP Builder正弦信号发生器的设计二、任务及要求【任务】采用DSP Builder系统建模的方法,设计正弦信号发生器,要求采用查找表的方法,完成正弦信号发生器模块的建模、仿真。

Signal Compiler【要求】:1.完成模型构建及仿真,得到如下波形图。

2.将模型转换成VHDL硬件描述语言,利用Modelsim软件进行RTL仿真。

3.再在Quartus II软件上进行编译、时序仿真与时序分析。

4.利用Signal Tap II嵌入式逻辑分析仪进行在线测试与分析。

(此步需使用实验箱,并且要确保实验箱与电脑处于在线可下载状态)三、仿真模型及参数四、仿真及结果分析五、小结《SOPC技术》课程实验报告学生姓名:所在班级:指导教师:高金定老师记分及评价:一、实验名称实验3:基于DSP Builder的FIR数字低通滤波器的设计二、任务及要求【任务】:调用DSP Builder模块,设计FIR低通数字滤波器,完成建模与仿真。

SOPC实验讲稿

2、实验内容

本实验通过使用 NiosII SDK Shell 、 QuartusII 和 SOPC Builder 共同建立

本开发板的目“ UP_AR2000_board ”。 然后新建工程“ USB_test ”,使用

SOPC Builder 定制一个标准的 NiosII 系统,该系统是“ UP_AR2000_board ” 为目标板建立的。从而完成硬件开发。用QuartusII 分配管脚,编译、生成 sof 文件。然后,使用 NiosII IDE 移植 uClinux 操作系统、 编译、 烧写。 建立根 文件系统编译、 烧写。 建立应用程序工程, 编译生成 .exe 文件。把 exe 文 件拷贝到根文件系统中的 bin 文件夹下。 再重新编译根文件系统, 烧写。 最 后 sof 文件。 运行通过超级终端我们就可以运行位于 bin 文件夹下的应用程 序命令了。

2在sopcbuilder上完成niosii硬件系统配置然后完成硬件系统生成3在quartusii上完成硬件引脚的添加与硬件锁定综合3在quartusii上完成硬件引脚的添加与硬件锁定综合4在niosiiide上完成中建立的linux内核工程和linux根文件系统工程然后新建应用工程5添加应用程序到应用工程

仿真波形图

4、实验要求 (1)记录调试与验证的结果 (2 )记录实验过程中出现的问题及解决办法

(3) 实验结束,保持实验室整洁

实验二

1、实验目的

LED实验

(1)学习使用 SOPC Builder 定制 一个最小NiosII 硬件系统的设计。

(2)学习使用 NiosII IDE 软件完成应用程序开发。

(6)将实验箱的JTAG与主机连接好,在Quartus II完成 .sof文件编程, 在NiosII上运行硬件调试,观察实验箱上LED的显示 (7)对 makefile 进行修改, 保存。指定 Rules.mak 的路径。改为: TOPDIR=E:\example\cheng\example\USB_test\software\Linux_app1

SOPC实验报告

SOPC系统设计技术实验报告姓名:学号:院系: 信息科学与工程学院专业:电子科学与技术指导老师:完成日期: 2015年04月25日实验二、NIOSII实现串口收发数据及LCD显示一、实验目的(1)进一步熟悉Quartus II、SOPC Builder、NIOS II IDE的操作;(2)掌握SOPC硬件系统及NIOS II软件的开发流程。

二、实验内容(1)、实验平台:硬件:PC级、SmartSOPC+教学实验开发平台;软件:Quartus II 9.0, SOPC Builder 9.0, NIOS II IDE 9.0。

(2)、实验内容:建立包含SDRAM、JTAG_UART、Timer、LCD的NIOS II处理器系统,通过JTAG_UART从IDE的控制端窗口读取输入值N,计算1至N的累加值,并将计算结果及计算花费时间的显示在LCD中。

三、实验步骤3.1硬件设计根据实验内容,可以得出本次实验的硬件结构图如图3.1所示:图3.1 硬件设计结构图具体硬件设计步骤如下:1)、在Quartus II中建立一个工程命名为:smallCore,器件设置为EP3C55F484C8;2)、以原理图输入方式建立空白顶层模块,并保持;3)、打开SOPC Builder,命名SOPC系统名称为nios2system,开始建立NIOS II 系统。

4)、双击SOPC Builder主界面左侧中的“Nios II Processor”,出现Nios II CPU 的配置向导对话框,如图1.4所示,在这里可以有三种Nios II CPU选择,我们选择快速型的Nios II/f,不使用硬件乘法器及除法器。

然后单击Next进入下一步配置;Instruction Cache项中选择2 Kbytes,在Data Cache项中选择512 Bytes,单击Next 进行下一步配置;在“Advanced Features”和“MMU and MPU Settings”选项卡中选择默认参数,然后单击Next,到了“JTAG Debug Module”选项卡,如图1.6所示。

sopc课程设计

SoPC课程设计(报告)题目:液晶控制显示器学院:电子工程学院系部:微电子学系专业:集成电路设计与集成系统班级: 1002 学生姓名:曹松松指导教师:曾泽沧起止时间: 2013年6月17日——2013年6月28日目录1 课程设计要求 (2)基本要求 (2)2 实验使用平台 (2)3 题目:选题2 (2)4 课程设计总结 (5)5 附件 (5)1课程设计要求基本要求课程设计要求所有题目采用Quartus II 工具提供的图形输入或者VerilogHDL语言输入方式作为电路设计工具,在NiosII上采用C语言实现编程,自定向下正向设计方法,先设计硬件系统,再进行软件编程,能够生成正确的FPGA下载代码和NiosII执行的软件代码。

硬件功能仿真和时序仿真采用第三方工具(建议为:modelsim),综合与布局布线工具为:Quartus II,SOPC Builder建立软件运行环境,具体要求为:1)根据课设题目,进行总体设计方案(10分);2)硬件电路顶层设计、模块划分、引脚定义(10分);3)电路设计及NiosII设计,提交电路设计源代码或电路图(10分);4)综合与布局布线,提交综合与布局布线报告(10分);5)FPGA下载代码和引脚分布(10分);6)软件总体设计及画出流程图(10分);7)程序设计,提交程序代码(10分);8)程序编译下载及仿真调试(10分)。

2实验使用平台实验平台使用Altera的DE2开发板,开发工具使用Altera的Quartus II和Nios II IDE。

3 题目:选题2在字符型液晶显示器上移动显示“XIAN UNIVERSITY POST AND TELECOMMUNICATIONS YOUR NAME 2013-6”,要求FPGA 设计硬件,内嵌NiosII,液晶显示采用软件实现。

1)根据课设题目,进行总体设计方案;(10分)此次sopc课程设计选题2,题目相对比较简单。

sopc8 段数码管显示实验

实验2、8 段数码管显示实验1、实验目的学习并行输入/输出(PIO)内核是如何提供从N ios II 软核处理器到通用输入/输出端口之间的寄存器映射接口。

2、实验环境PC机、Quartus II 13.0、Nios II EDS 13.03、实验内容按照书上介绍的方法和流程,完成8段数码管显示实验,包括N ios II 软核处理器系统的产生、编译、综合、Nios II EDS 工程创建、C 语言源文件的编辑及编译、配置目标F PGA 器件、下载观察实验结果。

4、实验步骤(1)启动Quartus II 13.0,新建工程将其命名为seg,选择好目标芯片,然后设置没有用的引脚。

(2)进入Tool-Qsys,进行如下图所示的硬件构架如上图双击seg7 组件中 export 栏输入 seg7_external 。

并将文件保存命名为 seg7.qsys ,点击 g enerate 生成硬件。

如图所示:(3)添加q ip 文件,新建如图所示的b df(Block Schematic File)文件,编译分配引脚,(注意引脚名的规范书写,有利于快速匹配引脚)再编译。

接着进入T ool-NIOSII SBT,选择你的工程目录作为你的工作空间,由N ios II C/C++菜单F ile-New- Nios II Application and BSP from Template 打开新工程设置窗口,找到seg7.sopcinfo 文件,将软件工程命名为SEG7,并选择空白模板blank project。

然后在S EG7 文件夹下新建s eg_pio.c 文件。

输入代码,Ctrl+s 保存,Ctrl+b 进行全编译,编译完成进行,进行板上运行,观察结果。

如run as 时出现如下错误,该问题是由于系统组件没有添加s ystem ID 组件。

将下方红圈处打勾即可。

5、实验心得与体会通过本次实验我基本了解了数码管显示的基本原理,但开始连接试验箱未成功。

实验七 SOPC 基础实验

实验七SOPC 基础实验SOPC即System-On-a-Programmable-Chip(可编程片上系统),本章通过一系列的实验,使学习者对SOPC的应用有较为深刻的认识,并对FPGA的仿真与设计环境有深入的了解,为进一步的工作奠定基础。

7.1 SOPC概述SOPC是PLD和ASIC技术融合的结果,它是一种特殊的嵌入式系统。

首先它是片上系统(SOC),即由单个芯片完成整个系统的主要逻辑功能;其次,它是可编程系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。

由于FPGA无论在逻辑门密度还是在运行频率等诸多方面都取得了长足进步,基于FPGA的嵌入式系统成为SOPC的热点。

目前已经可以把处理器软核、ASIC硬核、数字信号处理器件以及网络控制等各种数字逻辑控制器以IP核的形式集成到FPGA芯片里,构成嵌入式系统。

7.2 基本硬件设计实验嵌入式开发环境EDK是用于设计嵌入式处理系统的集成软件,是利用嵌入式PowerPC™硬处理器核和/或Xilinx MicroBlaze™软处理器核进行Xilinx平台FPGA设计时所需的全部技术文档和IP。

EDK包括硬件部分和软件部分:1. 硬件部分:Xilinx Platform Studio (XPS)XPS是设计嵌入式处理器系统硬件部分的开发环境和用户图形界面。

可使用底层系统生成器BSB(Base System Builder )创建XPS工程,BSB能够快速和有效地创建工程设计。

Xilinx推荐使用BSB向导来创建任何新的嵌入式设计工程,BSB能够满足你所有设计的需要,并且可以帮助你节省很多时间。

使用BSB创建XPS的过程如下:创建顶层工程文件(*.xmp File)选择板型选择和配置处理器选择和配置多重I/O口添加内部的外围设备设置软件观看系统摘要页2. 软件部分:Software Development Kit (SDK)SDK是综合的开发环境,是对XPS的补充,可用C/C++进行嵌入式软件应用的编写和验证。

SOPC实验系统的开发与研究的开题报告

SOPC实验系统的开发与研究的开题报告一、选题背景及意义数字系统设计平台(SOPC)已成为数字电路系统设计的重要基础。

SOPC系统是由可编程逻辑器件(如FPGA)和微处理器软件相互融合组成的。

这种系统的优势在于其具有高性能、低成本、快速产品更新、易于维护等特性。

在实际应用中,SOPC可以用于工业控制、军事装备、医疗器械等领域,其应用十分广泛。

因此,对SOPC系统的研究和开发具有重要的理论和实际意义。

本选题旨在对SOPC系统进行探讨,通过对不同实验系统的开发与研究,让学生更深入了解SOPC系统的基本原理和应用。

此外,SOPC系统的研究也可帮助学生掌握数字电路的设计方法和技术,提升其工程实践能力,并为学生将来从事相关领域的工作打下基础。

二、研究内容和技术路线1. 硬件平台搭建:选定FPGA平台,根据具体需求选择不同的芯片型号和开发板,进行SOPC系统的硬件平台搭建。

2. 软件开发:选择VHDL、Verilog等硬件描述语言,结合FPGA开发平台进行程序编写和仿真,达到对系统的操作控制效果。

选择C语言、汇编语言等作为协处理器程序和驱动程序开发工具,进行开发。

3. 实验系统设计:根据实验需求不同,确定系统的功能模块和硬件电路,进行电路设计和验证,并根据实验系统的需要做相应的调试和优化。

4. 实验系统研究:分析实验系统的性能和优缺点,优化其功能和性能特点,进一步提高实验系统的稳定性和可靠性。

5. 实验结果分析:对SOPC系统实验平台的开发和实验结果进行分析总结,评估其在不同应用场景中的优劣性,提出改进意见和建议。

三、预期的研究成果1. 搭建基于FPGA的SOPC系统硬件平台。

2. 设计实验(如数字时钟、闹钟、图像处理系统、音频处理系统等)需求的SOPC系统,并实现相应的功能。

3. 发表学术论文或科技论文,并在学术或行业会议上做相应的展示和汇报。

四、可能遇到的困难及解决方法1. 硬件系统集成难度大,需要克服模块之间相互影响的问题。

SOPC实验报告

SOPC设计基础实验报告学院:电子与信息工程学院学号:姓名:实验一开发软件使用练习一实验目的实验目的:掌握基于SOPC硬核处理器的设计流程。

二实验设备安装Quartu II的PC、实验箱三实验内容和步骤1)打开Quarts II 11.1,建立工程2)在菜单栏的File中选择New选项3)默认是New Quartus II Project,选OK4)选择Next,工程目录选择自己新建的文件夹,工程名输入E_Play5)源文件添加,点击Next直接跳过6)选择编号为EP4CE6E22C8的器件7)EDA工具选择,直接点击Next跳过8)项目信息显示,点击Finish完成空工程的建立9)配置无用引脚:在主页面菜单栏点击Assignments,接着在下拉框中选择Device选项,出现如下窗口:As input tri-stated with weak pull-up.点击OK完成。

创建软核处理器系统1)点击菜单栏的Tools,在下拉框中选择SOPC Builder选项,将System Name定为E_Play,下方的Target HDL选VHDL,最后点击OK确认。

2)Device Family选择Cylone IV E,Clock Frequency定为50MHz3)配置软核处理器系统点开左侧Processors总选项,双击Nios II Processor,选择Nios II/e另外在JTAG Debug Module选项中选择第一项,点击Finish完成配置4)配置存储器点开左侧Memories and Memory Controllers总选项,点开第二个On-Chip分选项,双击On-Chip-Memory,在Total memory sizes后输入4096点击Finish,在Onchip-memory2_0上右击,Rename为onchip-memory5)点开左侧Interface Protocols总选项,点开Serial分选项,双击JTAG UART,点击Finish完成6)在jtag_uart_0上右击,Rename为jtag_uart产生软核处理器系统1)双击cpu_0,将Reset Vector和Exception Vector的Memory均设置为onchip_memory,点击Finish完成。

SOPC实验报告要求课件.doc

注意:实验报告不能雷同。

一、实验仪器:

1、用到实验箱的模块及模块功能描述等。

2、接线说明。

二、实验内容及目标:

根据教学大纲的内容(部分内容有修改,请仔细填写)

例:用Nios II 设计并实现Hello 实验(需修改为点亮LED实验)。

学会用Quartus II 开发SOPC的流程;学会用SOPC Builder 进行CPU 开发的流程;学会用Nios SDK Shell 进行C 语言编译和下载。

三、实验内容任务

根据教学大纲的内容(有部分修改)

四、实验内容实现:

1、分析该实验用到的部件。

2、建立最小系统的较为详细步骤(包括结果)

3、分析程序代码的含义(最好有自己的代码)

4、问题及心得。

对应后面的时间如:实验六,实验七:

主要是实验四部分跟修改为如下:

四:实验内容实现:

1分析该实验用到的部件。

(主要是新增部分)

2系统建立及配置(可只列出跟实验五不同的步骤说明)

3分析程序代码的含义(最好有自己的代码)

4问题及心得。

sopc实验报告

xx 学院实验题目VGA接口实验学院名称:电子与信息工程学院专业:电信101 嵌入式方向姓名:x x姓名:x x指导教师:xVGA接口实验一.实验目的了解VGA显示原理,熟悉VGA核的使用方法。

二.实验设备硬件:PC机,SmartSOPC教学实验开发平台,带VGA接口的显示器,SmartCore_VGA_PS2_lc6 Nios II系统;软件:Nios II IDE 5.0。

三.实验内容熟悉使用光盘中提供的VGA核(zlg_avalon_vga)。

VGA核(zlg_avalon_vga)采用了SRAM(IS61V25616AL)来做显存,每个像素点的RGB用一位字节来存放,则显示为256色,显存大小为640x480=300KB,格式如表5.2所列。

VGA接口的时序控制由FPGA 完成,主要有4个模块组成:行、场同步信号产生模块、FIFO缓冲模块、显存读/写仲裁模块及SRAM读/写操作模块。

其中后面3个模块主要是用SRAM来构成一个双口RAM。

其他还有一些控制测试模块,如鼠标指针显示模块。

VGA核使用外部SRAM作为显示缓冲。

对VGA进行操作时,也就是对显示缓冲区进行数据填充。

根据不同的数据显示不同的图形或字符。

显示缓冲区共有480行,每一行有640个像素点,使用低10为地址做列地址(0~639),高9位地作为行地址(0~479)。

这样做方便于显示区的数据更改和管理。

但是对现实缓冲区进行操作时要注意地址组合。

实验模板位于:配套光盘\SmartSOPC\SmartSOPC_Software_Template\VGA_test。

四.实验预习要求(1)预习光盘中提供的VGA核(zlg_avalon_vga)的Verilog代码,位于:配套光盘\SmartSOPC\SmartSOPC_Component\ zlg_avalon_vga文件夹中。

(2)熟悉第1章介绍的VGA硬件电路。

五.实验步骤(1)使用试验箱提供的排线按照引脚分配情况从核心板上PACK的45、43、41、23、20、18、16、14、15和17引脚连接到COM1(VGA_COM)的R2、R1、R0、G2、G0、B1、B0、VSYNC、HSYNC。

sopc学号显示电路设计实验报告

学号显示电路设计一.实验目的:1、练习使用Verilog HDL语言设计实现数字电路。

2、练习利用Verilog HDL语言和状态机设计电路。

3、熟悉EDA开发基本流程。

4、掌握多个数码管动态扫描显示的原理及设计方法。

二.设计源程序和说明://this program displays strings "A11070511"//by yangqingyun 2011-4//modified by xinyi 2011-4-28module xuehao_display(clk,rst,out);input clk,rst;output reg[6:0] out;reg [3:0] state;parameters0=4'd0,s1=4'd1,s2=4'd2,s3=4'd3,s4=4'd4,s5=4'd5,s6=4'd6,s7=4'd7,s8=4' d8;always@(negedge clk or negedge rst)beginif(!rst) begin out=7'b1111111;state=s0;endelsecase(state)s0:begin out=7'b0001000;state<=s1;end//显示As1:begin out=7'b1111001;state<=s2;end//显示1s2:begin out=7'b1111001;state<=s3;end//显示1s3:begin out=7'b1000000;state<=s4;end//显示0s4:begin out=7'b111000;state<=s5;end//显示7s5:begin out=7'b100000;state<=s6;end//显示0s6:begin out=7'b0010010;state<=s7;end//显示5s7:begin out=7'b1111001;state<=s8;end//显示1s8:begin out=7'b1111001;state<=s0;end//显示1default:state<=0;EndcaseEndEndmodule程序详解:这是一个非常简单的程序,定义8个输出变量,然后给他们赋值,使他们分别为A11070511,然后通过数码管显示出来功能仿真结果说明:从波形图可以看出a b c d e f g的值对应着计数器的 1 2 3 4 5 6 7 8 9依次为0001000(A) 1111001 (1) 1111001 (1)1 000000 (0)1111000(7) 1 000000 (0)0010010 (5) 1111001 (1) 1111001 (1)。

SOPC按键控制LED灯亮灭实验报告

课程设计报告设计课题:SOPC按键控制LED灯亮灭按键控制LED灯泡亮灭一、设计任务与要求1.实现按键控制小灯泡的亮灭;2.学习并掌握Quartus II 9.0软件3.学会SOPC和FPGA电路设计方法二、方案设计与论证在Quartus II 9.0软件里利用Nios II完成对软核CPU的设计,设计完成后再搭建外围电路,后在Nios II IDE里完成代码的编写,最后将设计的电路和编写的代码下片后观察实验现象并调试直至成功。

方案一:1.新建一个New Quartus II Project,并命名为led_lab2.选择Cyclone III系列的EP3C25F324C8芯片3.CPU内核的设计:3.1新建一个SOPC Builder System,并命名为lab_led3.2将所要设计的CPU模块添加进来,并选择Nios II/e核心3.3再添加jtag和on-chip memory,并将内存设置为20KB3.4添加两个PIO(并行输入输出),将其中一个设置为Output ports only,并命名为led_pio,用作输出模块,另一个设置为Input ports only,并命名为key_pio,用作输入模块3.5保存好设计编译后无误4.外围电路的设计4.1新建一个Block Diagram/Schematic File文件,并命名为led_lab4.2将上一步设计好的CPU模块添加进来4.3自动生成好管脚后进行编译4.4对输入输出管脚进行分配,完成后再次进行编译5.Nios II代码控制CPU5.1点击Nios II IDE,新建一个lab_led.c文件5.2编写能够实现按键控制LED灯的代码,后编译、调试6.打开SOPC实验箱,将设计好的电路和编写好的代码下片,观察实验现象并调试四、总原理图及子模块结构图1.CPU内核的设计2.外围电路的搭建3.电路管脚的分配4.实验代码的编写及调试五、综合与调试最终实验代码:#include "sys/alt_stdio.h"#include "system.h"#include "altera_avalon_pio_regs.h"#include "alt_types.h"#include<unistd.h>alt_u8 K;int main(void){alt_putstr("\n Lab2_2 - LED key polling!\n");while(1){K= IORD_ALTERA_A VALON_PIO_DATA(KEY_PIO_BASE);IOWR_ALTERA_A VALON_PIO_DA TA(LED_PIO_BASE,K); usleep(10000);}return 0;}六、结果性能分析当按下KEY1后第一个LED点亮,松开后第一个LED熄灭当按下KEY2后第二个LED点亮,松开后第二个LED熄灭当按下KEY3后第三个LED点亮,松开后第三个LED熄灭当按下KEY4后第四个LED点亮,松开后第四个LED熄灭七、设计作品图片[八、结论与心得]因为有了前两次实验的经验和教训,所以这次实验并没有遇到多少障碍。

SOPC综合实验报告

基于SOPC的数字钟设计学院:计控学院班级:计本121学号:***********名:***指导老师:***一、设计概述用Nios II DE2开发板的LCD显示电子钟的日期和时间,LCD分两行显示,第一行显示年月日,第二行显示时分秒。

用输入按钮BUTTON来控制LCD行修改,通过Nios II IDE进行软件设计。

二、设计要求1.掌握Nios II系统的设计和使用方法;2.学习通过Nios II IDE进行软件设计的方法;3.实现在液晶屏上显示时间和日期,并可以对其进行设置。

三、实验环境DE2 开发板QuartusII 7.2SOPC Builder 7.2NiosII IDE 7.2四、设计方案(总体设计、软件设计、硬件设计)1. 总体设计要实现以下两个功能:(1). 在液晶屏上显示时间,日期(2). 对时间、日期能够进行设置建立新工程clock2. 硬件系统组成设计根据系统要实现的功能和开发板配置,需要用到的DE2开发板上的外围器件有:LCD:电子钟显示屏幕按钮:电子钟设置功能键CFI Flash存储器:存储软、硬件程序SDRAM存储器:程序运行时将其导入SDRAM根据所用到的外设和器件特性,在SOPC Builder中建立系统要添加的模块包括:NiosII CPU定时器,按键PIO,LCD,外部存储器总线(Avalon三态桥),外部SDRAM控制器,外部Flash接口。

打开SOPC Buider,系统名称为sopc_clock 加入SDRAM组件加入Flash Memory 组件加入外部存储器总线(Avalon三态桥)加入按键PIO加入LCD加入NiosII CPU定时器,选择标准型的元件添加完后,要为每个外设分配及地址和中断请求优先级(IRQ),在System中选择Auto-Assign Base Address和Auto-Assign IRQs命令,这两个命令可分别简单分配外设基地址和中断优先级。

SOPC课程设计实验报告--电子琴

FPGA-CPLD原理及应用课程设计报告题目:电子琴学院: 信息与电子工程学院专业: 电子科学与技术学号:姓名:指导老师:时间:2013-7-15~2013-7-20一、摘要电子琴是数字电路中的一个典型应用。

在实际的硬件设计中用到的器件非常多,连线比较复杂,同时会产生比较大的延时,从而造成测量误差较大,可靠性不好。

以EDA工具作为开发手段,运用VHDL硬件描述语言将使整个系统大大简化,提高了电子琴整体的性能和可靠性。

关键词:电子琴 SOPC SOPC Builder Nios II DE2 音符二、设计要求方案一:采用数字逻辑电路制作,用IC拼凑焊接实现。

其特点是直接用现成的IC组合而成,简单方便,但本系统需用到许多分频器,这就使得需要用到相当多的IC,从而造成了体积过于庞大,而且连线也会比较复杂。

方案二:采用单片机实现,通过软件编程,仿真后将程序用编程器写入到单片机芯片上,该方案成本低,稳定度也比较好,但外围电路多,特别是播放音乐时需要用到大容量的外部存储器,这样就增加了编程难度,调试不够直观,也不够灵活方便。

方案三:采用可编程逻辑器件(FPGA)制作,将所有器件集成在一块芯片上,大大减小了电子琴的体积,用VHDL编程实现时更加方便,而且易于进行功能扩展,并可调试仿真,制作时间大大缩短,因此选用了方案三进行设计。

电子琴设计原理乐曲都是由一连串的音符组成,按照乐曲的乐谱依次输出这些音符所对应的频率,就可以在扬声器上连续地发出各个音符的音调。

为了准确地演奏出一首乐曲,仅仅让扬声器能够发出声音是远远不够的,还必须准确地控制乐曲的节奏,即每个音符的持续时间。

由此可见,乐曲中每个音符的发音频率以及音符持续的时间是乐曲能够连续演奏的两个关键因素。

乐曲的12平均率规定:每2个八度音之间的频率要相差1倍,比如简谱中的中音2与高音2。

在2个八度音之间,又可分为12个半音。

另外,音符A(简谱中的低音5)的频率为392Hz,音符E到F之间、B到C之间为半音,其余为全音。

SOPC课程设计实验报告万年历的设计

目录摘要 (2)Abstract (2)一、设计要求 (3)1、构建的模型 (3)2、设计的主要内容 (3)三、设计步骤 (4)第一步:硬件部分设计 (4)第二步:软件部分设计 (15)四、运行情况 (19)五、问题分析与解决的方法 (19)六、心得体会 (19)摘要本次设计从系统硬件出发(CPU,系统总线,RAM,外接设备等)以此来构成SOPC Builder 的硬件系统,再通过Nios II IDE开发的嵌入式软件,编写且嵌入SOPC Builder的硬件中,实现万年历的整体开发。

通过应用SOPC Builder开发工具,设计者可以摆脱传统的、易于出错的软硬件设计细节,从而达到加快项目开发、缩短开发周期、节约开发成本的目的。

AbstractThe design of the system hardware from starting (CPU, RAM, bus, external equipment) constitute the SOPC Builder hardware system,and then, through ,the Nios II IDE development of embedded software, and hardware of the embedded SOPC Builder realize the integral development of the calendar. Through the application SOPC Builder development tools, designers can get rid of details of traditional and easy to go wrong the design of the software and hardware, so as to speed up the project development, to shorten the development cycle, save the purpose of development pays.关键词:SOPC Builder 嵌入式硬件开发一、设计要求用Nios II DE2开发板的LCD 显示电子钟的日期和时间。

SOPC实验报告

SOPC系统设计技术实验报告姓名:学号:院系: 信息科学与工程学院专业:电子科学与技术指导老师:完成日期: 2015年04月25日实验二、NIOSII实现串口收发数据及LCD显示一、实验目的(1)进一步熟悉Quartus II、SOPC Builder、NIOS II IDE的操作;(2)掌握SOPC硬件系统及NIOS II软件的开发流程。

二、实验内容(1)、实验平台:硬件:PC级、SmartSOPC+教学实验开发平台;软件:Quartus II ,SOPC Builder ,NIOS II IDE 。

(2)、实验内容:建立包含SDRAM、JTAG_UART、Timer、LCD的NIOS II处理器系统,通过JTAG_UART从IDE的控制端窗口读取输入值N,计算1至N的累加值,并将计算结果及计算花费时间的显示在LCD中。

三、实验步骤硬件设计根据实验内容,可以得出本次实验的硬件结构图如图所示:图硬件设计结构图具体硬件设计步骤如下:1)、在Quartus II中建立一个工程命名为:smallCore,器件设置为EP3C55F484C8;2)、以原理图输入方式建立空白顶层模块,并保持;3)、打开SOPC Builder,命名SOPC系统名称为nios2system,开始建立NIOS II系统。

4)、双击SOPC Builder主界面左侧中的“Nios II Processor”,出现Nios II CPU的配置向导对话框,如图所示,在这里可以有三种Nios II CPU选择,我们选择快速型的Nios II/f,不使用硬件乘法器及除法器。

然后单击Next进入下一步配置;Instruction Cache项中选择2 Kbytes,在Data Cache项中选择512 Bytes,单击Next进行下一步配置;在“Advanced Features”和“MMU and MPU Settings”选项卡中选择默认参数,然后单击Next,到了“JTAG Debug Module”选项卡,如图所示。

sopc实验报告

实验一[FPGA]基于 Qsys 的第一个 Nios II 系统设计一、基本说明1、软件平台: Quartus II 13.0(64-bit) Nios II 13.0 Software Build Tools for Eclipse2、硬件平台: Altera Cyclone II EP2C8Q208C8N二、设计目标完成 FPGA 平台上的“ Hello Word”实现,实现方式:基于 Qsys 的 Nios II 系统设计。

三、具体步骤1、打开 Quartus II 13.0(64-bit),新建一个工程, File -> New Project Wizard…,忽略Introduction,之间单击 Next> 进入下一步。

2、添加已经存在的文件,这里我们没有需要添加的文件,直接单击 Next> 进入下一步。

然后单击 Finish 完成即可。

3、新建 Block Diagram/Schematic File (方块图/原理图文件)。

单击 File -> New..,选择 Design Files 中的 Block Diagram/Schematic File,单击 OK 即可。

4、启动 Qsys 工具,进行硬件部分设计。

单击 Tools -> Qsys ,进入 Qsys 设置界面。

系统已经默认添加了时钟模块,名称为 clk_0 ,这里我们选中clk_0,右击,选择 Rename,将其名称更改为 clk。

5、添加软核处理器的各部分模块。

我们总共需要添加 Nios II Processor、On_ChipMemory(RAM or ROM)、 JTAG UART、 System ID Peripheral 这 4 个模块。

最终的完成效果如图 1 所示。

图 1 Qsys Connections 完成效果6、进行软核的相关设置。

首先双击 nios2_qsys,进入处理器设置模块。

SOPC实验报告(不含综合实验)要点

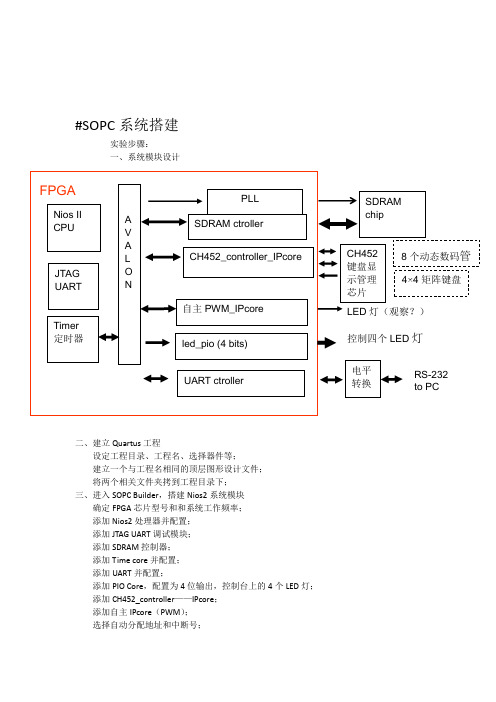

#SOPC 系统搭建实验步骤:一、系统模块设计二、建立Quartus 工程设定工程目录、工程名、选择器件等;建立一个与工程名相同的顶层图形设计文件; 将两个相关文件夹拷到工程目录下; 三、进入SOPC Builder ,搭建Nios2系统模块确定FPGA 芯片型号和和系统工作频率; 添加Nios2处理器并配置; 添加JTAG UART 调试模块; 添加SDRAM 控制器; 添加Time core 并配置; 添加UART 并配置;添加PIO Core ,配置为4位输出,控制台上的4个LED 灯; 添加CH452_controller ——IPcore ; 添加自主IPcore (PWM ); 选择自动分配地址和中断号;FPGA Nios IICPUJTAG UARTTimer定时器 A V A L O N SDRAM ctroller SDRAM chipCH452_controller_IPcore 4×4矩阵键盘led_pio (4 bits) 8个动态数码管 UART ctroller 电平转换RS-232 to PCCH452 键盘显示管理芯片PLL自主PWM_IPcore LED 灯(观察?) 控制四个LED 灯设定CPU启动地址和异常处理地址;Generate生成Nios2模块;四、在Quartus顶层图形设计文件中添加(insert symbol)Nios2系统模块;添加alt_pll并配置;添加Timer_out辅助电路;添加(insert symbol)input、output、bidir引脚并连线;设定未用引脚状态为三态,编译工程;进行引脚分配(如下所示);再次编译;下载.sof文件下为引脚分配示意图:系统搭建完毕后的硬件核截图:实验小结:系统搭建其实是本次实验中最难倒我们的部分,主要是在搭建过程中我们组与老师的进度脱节,以至于出现了不切实际的设计部分而我们又不自知。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SOPC系统设计技术实验报告姓名:学号:院系: 信息科学与工程学院专业:电子科学与技术指导老师:完成日期: 2015年04月25日实验二、NIOSII实现串口收发数据及LCD显示一、实验目的(1)进一步熟悉Quartus II、SOPC Builder、NIOS II IDE的操作;(2)掌握SOPC硬件系统及NIOS II软件的开发流程。

二、实验内容(1)、实验平台:硬件:PC级、SmartSOPC+教学实验开发平台;软件:Quartus II 9.0,SOPC Builder 9.0, NIOS II IDE 9.0。

(2)、实验内容:建立包含SDRAM、JTAG_UART、Timer、LCD的NIOS II处理器系统,通过JTAG_UART从IDE的控制端窗口读取输入值N,计算1至N的累加值,并将计算结果及计算花费时间的显示在LCD中。

三、实验步骤3.1硬件设计根据实验内容,可以得出本次实验的硬件结构图如图3.1所示:图3.1 硬件设计结构图具体硬件设计步骤如下:1)、在Quartus II中建立一个工程命名为:smallCore,器件设置为EP3C55F484C8;2)、以原理图输入方式建立空白顶层模块,并保持;3)、打开SOPC Builder,命名SOPC系统名称为nios2system,开始建立NIOS II系统。

4)、双击SOPC Builder主界面左侧中的“Nios II Processor”,出现Nios II CPU的配置向导对话框,如图1.4所示,在这里可以有三种Nios II CPU选择,我们选择快速型的Nios II/f,不使用硬件乘法器及除法器。

然后单击Next进入下一步配置;Instruction Cache项中选择2 Kbytes,在Data Cache项中选择512 Bytes,单击Next进行下一步配置;在“Advanced Features”和“MMU and MPU Settings”选项卡中选择默认参数,然后单击Next,到了“JTAG Debug Module”选项卡,如图1.6所示。

这里是选择JTAG调试接口,选择默认的模式Level 1,然后单击Next,到了“Custom Instruction”选项卡,也选择默认参数,最后单击Finish完成对Nios II CPU的配置。

5)、添加了Nios II CPU内核后,选中Module Name下的cpu_0,单击鼠标右键,在Rename 项中可以重命名cpu_0的名称为cpu,并在“Clock Settings”一栏中将clk_0名称改为clk。

6)、双击在SOPC Builder主界面左侧中的Bridges and Adapters→Memory Mapped→Avalon-MM Clock Crossing Bridge,出现Clock Crossing Bridge的配置向导对话框,在“Slave-to-Master FIFO”中的FIFO depth中选择64。

单击“finish”退出配置对话框,并重命名clock_crossing_0的名称为clock_crossing。

7)、双击在SOPC Builder主界面左侧中的Memories and Memory Controllers→SDRAM→DDR SDRAM High Performance Controller,出现DDR SDRAM High Performance Controller 的配置向导对话框。

修改“General Settings”选项卡的参数配置,参数修改如下:Speed grade:8PLL reference clock frequency:85Memory clock frequency:100Local interface clock frequency:full修改“Modify Parameters”: DDR SDRAM控制器参数,参数修改如下:Total Memory interface DQ width:16Memory vendor:otherColumn address width:98)、修改DDR SDRAM的控制器ddr_sdram_0的名称为ddr_sdram,并在ddr_sdram左侧中取消cpu.instruction_master和cpu.data_master中的实点,选择clock_crossing.m1的实点,将ddr_sdram控制器连接到Clock Crossing Bridge的m1中。

9)、双击在SOPC Builder主界面左侧中的Bridges and Adapters→Memory Mapped→Avalon-MM Pipeline Bridge,出现Pipeline Bridge的配置向导对话框,选择默认参数,单击“finish”添加到SOPC Builder中,并重命名pipeline_bridge_0为pipeline_bridge。

10)、双击在SOPC Builder主界面左侧中的Peripherals→Microcontroller Peripherals →PIO(Parallel I/O),出现PIO外设配置的对话框,在Wide一栏中选择8bit,在Direction 一栏中选择Output ports only,如图1.13所示,最后单击Finish完成对PIO的设置,此时在SOPC Builder中出现pio_0的外设,修改该名称为LED_PIO,并把LED_PIO外设连接到pipeline_bridge.m1上。

11)、双击在SOPC Builder主界面左侧中的Peripherals→Debug and Performance→System ID Peripheral,直接在SOPC Builder中添加sysid的外设,修改sysid_0名称为sysid,并把sysid外设连接到pipeline_bridge.m1上。

12)、双击在SOPC Builder主界面左侧中的PLL→PLL,单击“Launch Altera’s ALTPLL MegaWizard”,出现PLL配置对话框1。

在“what is the frequency of the inclock0 input”一栏中设置输入的频率为50MHz,单击Next,进行下一步的设置。

在PLL配置对话框2中的“Lock output”中选择“Create ‘locked’ output”,PLL配置对话框的page3、4、5都选择默认参数,在page6中Clock Tap Settings一栏中选择“Enter output clock frequency”,将c0时钟输出为85MHz,单击Next,进行下一步的设置。

PLL配置对话框的page7-11都选择默认参数,在page12中单击“finish”退出PLL配置对话框,最后再单击“finish”退出。

在SOPC Builder中重命名pll_0为sys_pll,并把sys_pll外设连接到pipeline_bridge.m1上。

13)、在“Clock Settings”一栏中将sys_pll_c0名称改为system_clk,并在SOPC Builder 中的Clock一栏中为每一个外设选择合适的clock信号。

需要特别注意的是sys_pll中的s1时钟需要选择clk,clock_crossing中的s1需要选择system_clk,m1需要选择ddr_sdram_sysclk,ddr_sdram对应选择system_clk,ddr_sdram中的s1需要选择ddr_sdram_sysclk,其它的外设选择system_clk。

14)、添加JTAG_UART:使用缺省设置,命名为jtag_uart,对应system_clk,连接至pipeline_bridge;15)、添加Timer: Initial Period改为20ms,命名为sys_clock_timer, 对应system_clk,连接至pipeline_bridge;16)、添加Avalon-MM Tristate bridge: 使用缺省设置,命名为ext_bus,对应system_clk,连接至cpu;17)、添加zlg_avalon_lcd240_128: 命名为lcd240_128,对应system_clk,连接至ext_bus;18)、添加pio: 1位输出,output only, 命名为lcd_light,对应system_clk,连接至pipeline_bridge;19)、单击SOPC Builder菜单的system→Auto-Assign Base Address,进行自动分配地址,单击SOPC Builder菜单的system→Auto-Assign IRQs,进行自动分配中断号。

20)、双击SOPC Builder中的cpu,确认在Reset Address一栏中选择ddr_sdram,在Exception Address一栏中选择ddr_sdram。

完整的nios2系统如图3.2所示:图3.2 nios2系统构造图时钟设制如图3.3所示:图3.3 系统时钟设置图21)、生成系统。

在之前建立好的原理图文件中添加NIOS II 系统至顶层模块,保存原理图文件。

22)、定制delay_reset_block模块:原理图如图3.4所示:图3.4 delay_reset_block模块原理图23)、在smallCore原理图中添加delay_reset_block模块原理图,并且添加输入输出端口,得到系统原理图,如图3.5所示:图3.5系统原理图24)、在Quartus II主界面中选择Assignments→Device。

在“Available devices”一栏中选择“EP3C55F484C8”器件。

对器件和引脚进行配置。

配置项有:Unused Pins设置为:As input tri-stated;configuration device设置为:EPCS16;Default I/O standard配置为:3.3-V LVTTL电平;Dual-Purpose Pins中的所有引脚设置为“Use as regular I/O”。

25)、将DDR SDRM引脚约束文件中的“YES”改为“NO”,运行DDR SDRM引脚约束文件。

26)、对系统进行引脚分配:新建引脚约束文件:”set up.tcl”。

setup.tcl文件见附录。

运行set.up.tcl引脚约束文件。

27)、编译整个工程,编译成功之后将系统下载到 FPGA 中去。