异步FIFO设计

FPGA异步fifo设计完整报告

FPGA异步fifo设计完整报告1、名目一、技术规范31、设计完成的功能:32、系统整体框图:33、I/O管脚的描述:34、验证和测试工具选择:45、说明关键模块:46、拟选用的FPGA类型:4二、FIFO总体设计方案5系统功能描述:5电路结构图:5系统的总体输入输出设定6系统时序分析:6关键模块设计分析:7三、FIF0验证方案8FIFO功能:81、概述:82、预确认:83、模块运行确认:94、系统运行确认:9四、仿真激励代码10五、电路设计FIFO源代码11六、FPGA设计FIF0综合布局布线报告:16综合引脚安排:16电路布局布线:16七、时序仿真报告17时序仿真波形:17八、FIFO下载代码和引脚分布17系统输入输出引 2、脚分布:21九、心得体会21技术规范1、设计完成的功能:本试验完成的是8位异步FIFO的设计,其中写时钟100MHz,读时钟为5MHz,其中RAM的深度为256。

当写时钟脉冲上升沿到来时,推断写信号是有效,则写一个八位数据到RAM中;当读时钟脉冲上升沿到来时,推断读信号是有效,则从RAM中把一个八位数据读出来。

当RAM中数据写满时产生一个满标志,不能再往RAM再写数据;当RAM 中数据读空时产生一个满标志,不能再从RAM读出数据。

2、系统整体框图:3、I/O管脚的描述:管脚名称方向H/L电平位宽功能描述rst_ninput3.3V/01全局复位信号rd_eninput3.3V/01读使能低有3、效wr_eninput3.3V/01写使能低有效rd_emptyoutput3.3V/01读空标志高有效wr_fuIIoutput3.3V/01写满标志高有效rd_dataoutput3.3V/08数据输出wr_datainput3.3V/08数据写入cIk_1OOMinput3.3V/01写数据时钟cIk_5Minput3.3V/01读数据时钟4、验证和测试工具选择:ModelsimSE6.If进行前仿真和后仿。

异步FIFO的VHDL设计

异步FIFO的VHDL设计下面是一个异步FIFO的VHDL设计示例:```vhdllibrary ieee;use ieee.std_logic_1164.all;entity AsyncFIFO isgenericDATA_WIDTH : natural := 8; -- 数据宽度FIFO_DEPTH : natural := 16 -- FIFO深度portclk : in std_logic; -- 时钟信号rst : in std_logic; -- 复位信号read_en : in std_logic; -- 读使能write_en : in std_logic; -- 写使能read_data : out std_logic_vector(DATA_WIDTH-1 downto 0); -- 读数据write_data : in std_logic_vector(DATA_WIDTH-1 downto 0); -- 写数据full : out std_logic; -- FIFO满标志empty : out std_logic -- FIFO空标志end AsyncFIFO;architecture Behavioral of AsyncFIFO istype buffer_array is array (FIFO_DEPTH-1 downto 0) ofstd_logic_vector(DATA_WIDTH-1 downto 0);signal buffer : buffer_array; -- 数据缓冲区signal wr_ptr : natural range 0 to FIFO_DEPTH-1; -- 写指针signal rd_ptr : natural range 0 to FIFO_DEPTH-1; -- 读指针signal count : natural range 0 to FIFO_DEPTH-1; -- 缓冲区中数据个数beginprocess (clk)beginif rising_edge(clk) thenif rst = '1' thenwr_ptr <= 0;rd_ptr <= 0;count <= 0;elseif write_en = '1' and full = '0' then -- 写使能且FIFO非满buffer(wr_ptr) <= write_data;wr_ptr <= wr_ptr + 1;count <= count + 1;end if;if read_en = '1' and empty = '0' then -- 读使能且FIFO非空read_data <= buffer(rd_ptr);rd_ptr <= rd_ptr + 1;count <= count - 1;end if;end if;end if;end process;full <= '1' when count = FIFO_DEPTH-1 else '0';empty <= '1' when count = 0 else '0';end Behavioral;```在上面的代码中,`DATA_WIDTH`和`FIFO_DEPTH`是异步FIFO的泛型参数,可以根据实际需求进行配置。

异步fifo设计及时序约束设置

一、前言跨时钟域的同步处理,使用异步FIFO是常用的方式之一,对于异步FIFO的设计,网上的大部分资料来源于《Simulation and Synthesis Techniques for Asynchronous FIFO Design》一文其异步FIFO的结构如下图所示本文不是介绍上图描述的设计。

我从基本的数字电路时序开始,介绍异步FIFO的相关问题。

最后介绍如何用时序约束保证设计的正确性二、数字电路时序对于数字电路来讲,我们的信号在时钟边沿发生变化,Dat1信号是一种理想情况,而Dat2是实际情况,其特点是一、相对时钟边沿有延时二、信号变化有一段时间(电平转换时间),在这段时间就是亚稳态在亚稳态期间进行数据采样,不能获得稳定的值。

数字电路中经过时序约束,在T1产生的信号,在T2一定稳定(否则就是不满足时序),所以对于只有一个时钟的数字电路来说,它在T1和T2都能获得稳定的信号(T1时刻的值为0、T2时刻的值为1)三、跨时钟域时序问题对于异步时钟而言(相位不同),对于CLK1产生的信号,CLK2有可能在任意时刻进行数据采样在FIFO的设计中,将会产生2种信号,一种是数据本身(用Data表示),另外一种是指示数据是否有效(用valid表示),注意(valid不一定是一个比特的寄存器,可以是由FIFO中的读写指针产生而来,例如fifo的full或empty状态)异步FIFO的问题在于,如果CLK2在时钟T2进行采样,那么有可能得到valid有效,而数据无效的情况。

这样在CLK2采样取得的设计就是错误的数据。

四、处理异步FIFO的valid和data(理论基础)我们假设valid为低电平表示没有数据,高电平为有数据,解决的办法就是,当CLK对valid进行采样时,即使valid处于亚稳态期间,数据信号也是稳定的如上图所以,在T1时刻进行上升沿采样,虽然valid是一个亚稳态状态,但是此时Data 是一个稳定的值,如果在T1时刻采样的valid为1,那么可以得到稳定的Data信号,如果在T1时刻采样的valid为0,那么控制逻辑认为在T1无法获得数据,从而在下一个时钟获取注意:T2时刻是在下降沿进行采样,而此时的Data信号也是稳定的五、如何实现为了让valid和Data处于上面的状态,我们可以对valid进行延时处理,即使用时钟对其进行采样,必须使用2个寄存器依次采样,才能保证至少有一个时钟的延时valid1是CLK2对valid进行采样产生的,如果采样的时机不好,那么valid1相对valid只有一点点延时,valid2是CLK2对valid1的采样,这样valid2相对于valid至少有CLK2一个周期的延时,也就满足了第二节的条件。

高速异步FIFO的设计与实现

高速异步FIFO的设计与实现2 异步FIFO的实现读时钟2.1 FIFO设计的难点如何同步异步信号,使触发器不产生亚稳态是设计异步FIFO的难点。

国内外解决此问题的较成熟方法是对写地址膜地址采纳格雷码,本文也挺直采纳格雷码。

异步FIFO设计的另一个难点是如何推断FIFO的空/满状态。

为了保证数据正确的写入或读出。

必需保证异步FIFO在满的状态下.不能举行写操作:在空的状态下不能举行读操作。

通常状况下将存储器组织成一个环形链表。

满/空标记产生的原则是:写满不溢出.读空不多读。

即无论在什么状况.都不应浮现读写地址同时对一个存储器地址操作的状况。

在读写地址相等或相差一个或多个地址的时候,满标记应当有效。

表示此时FIFO 已满,外部电路应停止对FIFO发数据。

在满信号有效时写数据应按照设计的要求,或保持、或抛弃重发。

同理,空标记的产生也是如此。

为了更好的推断满/空标记。

采纳在FIFO本来深度的基础上增强一位的办法,而由该位组成的格雷码并不代表新的地址。

也就是说3位格雷码可表示8位的深度,若再加一位最高位MSB,则这一位加其他三位组成的格雷码并不代表新的地址,也就是说格雷码的0100表示7,而1100仍然表示7,只不过格雷码在经过一个以0位MSB的循环后进入一个以1为MSB的循环,然后又进入一个以0位MSB的循环。

其他的三位码仍然是格雷码。

举例解释:一个深度为8字节的FIFO怎样工作(用法已转换为二进制的指针),N=3,指针宽度为N+I=4。

开头rd_ptr_bin和wr_ptr_bin均为“0000”。

此时FIFO中写入8个字节的数据。

wr_ptr_bin=“1000",rd_ptr_bin=“0000”。

固然,这就是满条件。

现在,假设执行了8次的读操作.使得rd_ptr_bin=“1000”,这就是空条件。

另外的8次写操作将使wr_ptr_bin等于“0000”,但rd_ptr_bin仍然等于“1000”,因此,FIFO为满条件。

异步FIFO设计

异步FIFO设计2011.6.22摘要本文采用格雷码设计了一个异步FIFO,经过DC综合的结果如下:时钟频率:1.1GHz面积:10744.447um2功耗:7.791mw目录1. 异步FIFO的设计 (2)1.1 异步FIFO简介 (2)1.2 FIFO的参数 (2)1.3 FIFO的设计原理 (2)1.4 FIFO的设计模块 (6)1.5 用modelsim仿真FIFO (11)1.6 用DC对FIFO进行综合 (13)2.参考文献 (15)1. 异步FIFO的设计1.1 异步FIFO简介FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,它与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

根均FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。

同步FIFO是指读时钟和写时钟为同一个时钟。

在时钟沿来临时同时发生读写操作。

异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

异步FIFO(Asynchronous FIFO),一般用于不同时钟域之间的数据传输,比如FIFO 的一端连接频率较低的AD数据采样信号,另一端与计算机的频率较高的PCI总线相连。

另外,对于不同宽度的数据接口也可以用AFIFO,例如单片机为8位数据输出,而DSP可能是16位数据输入,在单片机与DSP连接时就可以使用AFIFO来达到数据匹配的目的。

由于实际中,异步FIFO比较常见。

为了便于描述,在后面的章节中将异步FIFO 简称为FIFO.1.2 FIFO的参数FIFO的宽度:进行一次读写操作的数据的位宽。

FIFO的深度:双口存储器中能容纳的数据的总数。

满标志:FIFO已满或将要满时由FIFO的状态电路送出的一个信号,以阻止FIFO的写操作继续向FIFO中写数据而造成溢出。

异步FIFO的设计与实现

摘要随着数字系统规模的不断增大,单时钟域设计会极大地限制数字系统性能,现代数字系统为了提升性能,常采用多时钟域的设计。

跨时钟域的信号在传输时会遇到亚稳态现象,如何保持系统稳定地传输数据是多时钟域系统设计者重点关注的问题,在跨时钟域传递数据的系统中,常采用异步FIFO(First In First Out,先进先出队列)口来缓冲传输的数据,以克服亚稳态产生的错误,保证数据的正确传输。

常规的异步FIFO 设计采用先同步读写指针后比较产生空/满标志和用先比较读写指针产生空/满标志,再同步到相应时钟域的方法,但由于常规异步FIFO 模块中的RAM 存储器读写寻址指针常采用格雷码计数器以及“空满”控制逻辑的存在,工作频率低,面积大,将使通过这两个模块的信号通路延时对整个模块的工作频率造成制约。

本文提出了一种新型异步FIFO 的设计方法,该方法省略“了满”信号产生模块和多余的存储器位深来简化常规的FIFO 模块,而只保留“空”信号产生模块,避免使用大量的同步寄存器,减少了面积空间。

FPGA 验证的结果表明,改进后的异步 FIFO 性能有了显著的提高。

关键词:现场可编程门阵列(FPGA )亚稳态空/满标志产高速FIFOABSTRACTWith the increasing of digital system size, a single clock domain design will greatly limit the digital system performance. To enhance the performance of modern digital systems, multiple clock domain design is conventionally adopted. While being transmitted, Cross-clock domain signals will come across the phenomenon of metastability, hence it will be a major concern for the multi -clock domain system designers to probe how to maintain the system stability and to have data transmission conducted smoothly. As to the bus system data transmission in the system where the two data interface clocks don’t match, one of super and effective solutions is to use asynchronous FIFO buffer memory. How To solve the key and difficult issue that metastability and how to generate empty and full flag correctly in asynchronous FIFO design. Traditional FIFO design often synchronizes write/read address first, then compares them to generate empty/full signals or empty / full flag first compare the read and write pointer, and then synchronized to the clock domain, This design takes on too much area and can only work at a low frequency,this will allow the signaling pathways of these two modules delay caused by constraints of the operating frequency of the entire module. A new method of asynchronous FIFO is proposed to overcome these problems,omit the "full" signal generator module and redundant memory bit depth to simplify the conventional FIFO module, leaving only the "empty" signal generation module,avoid the use of a large number of synchronization registers, reducing the area of space. FPGA verification results show that the asynchronous FIFO improved performance has been significantly improved.Keywords: Field Programmable Gate Array (FPGA); Metastable; Mmpty / Full Flag production; High-speed FIFO目录摘要 (I)ABSTRACT (II)第一章绪论 (1)1.1研究背景和意义 (1)1.2研究现状 (1)1.3本文的主要工作 (3)1.4论文结构 (3)第二章跨时钟域设计的挑战与实现方法 (4)2.1跨时钟域设计的挑战 (4)2.1.1亚稳态问题 (4)2.1.2亚稳态产生的原因 (5)2.1.3亚稳态的危害 (5)2.2 跨时钟域的实现方法 (6)2.2.1同步器 (6)2.2.2握手机制 (9)第三章开发环境 (11)3.1硬件平台 (11)3.2软件平台 (11)第四章异步FIFO的设计与实现 (13)4.1异步FIFO (13)4.1.1异步FIFO工作原理 (13)4.1.2异步FIFO设计的难点 (14)4.2常见异步 FIFO 的设计 (16)4.2.1 读写地址产生逻辑 (18)4.2.2空/满标志的产生及代码的实现 (19)4.3.3改进的异步 FIFO 设计方法分析 (22)4.4高速异步FIFO的设计与实现 (23)4.4.1常见FIFO模块分析 (23)4.4.2高速异步FIFO 设计 (25)第五章结论 (28)第六章参考文献 (29)致谢 (30)附录高速异步FIFO设计仿真分析 (31)附1. 设计工作流程 (31)附.1.1 设计输入 (31)附.1.2 设计编译 (35)附.1.3 设计仿真 (36)第一章绪论1.1研究背景和意义作为21 世纪最重要的科学领域之一,超级计算机是体现科技竞争力和综合国力的重要标志。

异步FIFO的设计文档

异步FIFO的设计版本v1.02011-05-06异步FIFO的设计一.功能描述本设计用16*8 RAM实现一个异步FIFO,具体功能定义如下:1. 异步复位。

2. FIFO不为满时,当写使能有效时,在写时钟的上升沿向FIFO中写入数据。

3. FIFO不为空时,当读使能有效时,在读时钟的上升沿从FIFO中读出数据。

4. 当FIFO写满的时候,产生满信号;当FIFO读空的时候,产生空信号。

5. FIFO一旦空或者满时候,复位FIFO;二.输入输出信号描述信号名输入/输出目标/源功能描述Rclk Input Pin 读时钟频率,10M ,占空比1:1。

Wclk Input Pin 写时钟,频率10M ,占空比1:1。

data_in[7:0] Input Pin 8位的输入数据rd_en Input Pin 读使能,高电平有效,在FIFO非空时,CLK上升沿读入数据;wr_en Input Pin 写使能,高电平有效,在FIFO非满时,CLK上升沿写入数据;Rst Input Pin 异步清零,低电平有效,低电平时读地址,写地址,计数器都清零。

三顶层划分图1 系统框图顶层模块说明:1.RAM :存储器模块,用于存放及输出数据;2.Waddr_Reg : 保存访问RAM的写地址;3.Raddr_Reg : 保存访问RAM的写地址;4.Wbin_addr : 计算RAM下一个写地址;5.Rbin_addr : 计算RAM下一个读地址;6.Gwaddr_reg : 将写地址的二进制编码转换成格雷码,并保存;7.Graddr_reg : 将读地址的二进制编码转换成格雷码,并保存;8.Syn_Rfield : 将写地址同步到读时钟域,并产生空标志;9.Syn_Wfield : 将读地址同步到写时钟域,并产生满标志;10、Reset_Unit : 复位信号产生单元设计思想说明:1、由于实现的异步FIFO,分别用不同的读、写时钟产生读写地址,因此FIFO 的判空和判满是本设计中的一个难点。

最新-一种异步FIFO的设计方法 精品

一种异步FIFO的设计方法摘要使用同步源自不同时钟域的数据是在数字设计中经常使用的方法,设计功能正确的会遇到很多问题,探讨了两种不同的异步的设计思路。

两种思路都能够实现功能正确的。

关键词异步握手同步二进制格雷码本文所研究的,从硬件的观点来看,就是一块数据内存。

它有两个端口,一个用来写数据,就是将数据存入;另一个用来读数据,也就是将数据从当中取出。

与操作相关的有两个指针,写指针指向要写的内存部分,读指针指向要读的内存部分。

控制器通过外部的读写信号控制这两个指针移动,并由此产生空信号或满信号。

对于异步而言,数据是由某一个时钟域的控制信号写入,而由另一个时钟域的控制信号将数据读出。

也就是说,读写指针的变化动作是由不同的时钟产生的。

因此,对空或满的判断是跨时钟域的。

如何根据异步的指针信号对的满状态或空状态进行正确的判断是本文研究的重点。

此外,设计过程中的一些细节问题也将在文中涉及到。

1指针以及满空信号的产生为了更好地说明问题,先探讨一下同步指针移动以及满空信号的产生过程。

对于同步,读写指针都指向一个内存的初始位置,每进行一次读写操作,相应的指针就递增一次,指向下一个内存位置。

当指针移动到了内存的最后一个位置时,它又重新跳回初始位置。

在非满或非空的情况下,这个过程将随着读写控制信号的变化一直进行下去。

如果处于空的状态,下一个读动作将会导致向下溢出,一个无效的数据被读人;同样,对于一个满了的,进行写动作将会导致向上溢出,一个有用的数据被新写入的数据覆盖。

这两种情况都属于误动作,因此需要设置满和空两个信号,对满信号置位表示处于满状态,对满信号复位表示非满,还有空间可以写入数据;对空信号置位表示处于空状态,对空信号复位表示非空,还有有效的数据可以读出。

当读指针和写指针相等也就是指向同一个内存位置的时候,可能处于满或空两种状态。

可以通过不同的方法判断或区分究竟是处于满状态还是空状态,也就是究竟是写指针从后赶上了读指针,还是读指针从后赶上了写指针。

高速异步FIFO设计-

课程设计报告高速异步FIFO设计目录技术规范 (3)FIFO的功能描述 (3)FIFO的引脚定义 (3)总体方案设计 (4)电路设计方框图 (4)电路设计连接图 (4)电路模块及其功能简介 (4)电路设计思想 (5)仿真方案及其仿真激励源代码 (8)仿真方案 (8)仿真激励源代码 (8)电路描述代码 (9)功能仿真 (14)分块仿真 (14)双口RAM仿真 (14)读数据控制电路仿真 (15)写数据控制电路仿真 (16)锁存器电路仿真 (16)满空标志电路仿真 (17)总体仿真 (18)综合与布局布线 (18)综合布局布线报告 (19)报告数据分析 (19)时序仿真 (19)实验心得 (20)一、技术规范1、FIFO的功能描述高速异步FIFO(First In First out)深度为256,数据宽度为8位(最大可存储256byte),可实时给出FIFO的满空标志,并可实现数据的平滑输出,其写时钟为带间隔的100MHz,读时钟为5MHz,从而实现了FIFO的异步数据传输。

2、FIFO的应交定义(3)写数据控制器引脚对照表:(4)读数据控制器引脚对照表:二、总体设计方案1、电路设计方框图(如图2.1所示)图2.12、电路设计连接图(如图2.2所示)3、电路模块及其功能简介双口256*8bit的RAM:用于存储FIFO的缓冲数据写数据控制器:用于控制FIFO中数据的写时序操作FIFO 读数据控制器:用于控制FIFO数据中的读时序操作锁存器:用于锁存上一个clock时的读写地址指针FIFO满空标志电路:用于实时标志FIFO的满空状态4、电路设计思想设计高速异步FIFO,首先,考虑如何实现数据的先进先出问题;为了解决这个问题,设计中就必须有一个可用于随机存取的存储器,又要实现异步,即异步读写,所以本设计中存储器选择采用双口RAM;其次,考虑如何实现在不同时钟下,实现读数据和写数据,在设计中,使用独立电路模块,分别控制读写操作;最后,一个要考虑的问题也是本设计中的难点,即对于高速异步FIFO来说,如何高速、实时判断FIFO的满和空。

异步FIFO

异 步 FIFO 结 构(第一部分)作者:Vijay A.Nebhrajani翻译:Adam Luo2006年7月设计一个FIFO是ASIC设计者遇到的最普遍的问题之一。

本文着重介绍怎样设计FIFO——这是一个看似简单却很复杂的任务。

一开始,要注意,FIFO通常用于时钟域的过渡,是双时钟设计。

换句话说,设计工程要处理(work off)两个时钟,因此在大多数情况下,FIFO工作于独立的两个时钟之间。

然而,我们不从这样的结构开始介绍—我们将从工作在单时钟的一个FIFO特例开始。

虽然工作在同一时钟的FIFO在实际应用中很少用到,但它为更多的复杂设计搭建一个平台,这是非常有用的。

然后再从特例推广到更为普通的FIFO,该系列文章包括以下内容:1.单时钟结构2.双时钟结构——双钟结构13.双时钟结构——双钟结构24.双时钟结构——双钟结构35.脉冲模式FIFO单时钟FIFO特例FIFO有很多种结构,包括波浪型(ripple)FIFO,移位寄存器型以及其他一些我们并不关心的结构类型。

我们将集中讨论包含RAM存储器的结构类型。

其结构如图1所示。

通过分析,我们看到图中有一个具有独立的读端口和独立的写端口的RAM 存储器。

这样选择是为了分析方便。

如果是一个单端口的存储器,还应包含一个仲裁器保证同一时刻只能进行一项操作(读或写),我们选择双口RAM(无需真正的双口RAM,因为我们只是希望有一个简单的相互独立的读写端口)是因为这些实例非常接近实际情况。

读、写端口拥有又两个计数器产生的宽度为log2(array_size)的互相独立的读、写地址。

数据宽度是一个非常重要的参数将在在稍后的结构选择时予以介绍,而现在我们不必过分的关心它。

为了一致,我们称这些计数器为“读指针”(read pointer)和“写指针”(write pointer)。

写指针指向下一个将要写入的位置,读指针指向下一个将要读取的位置。

每次写操作使写指针加1,读操作使读指针加1。

高速异步FIFO的设计和实现

万方数据路中,这一信号最终会朝着0和1两个稳态转换,变成稳定的信号。

这一变换所需的时间取决于寄存器的结构和参数,通常在一个时钟周期内可以完成这一从亚稳态到稳态的转换。

所以,在设计中普遍采用两级寄存器串接的同步器来对信号进行同步,如图1所示。

图1解决亚稳态的同步器电路2.2毛刺单根信号的同步采用图1所示的同步电路即可消除亚稳态问题。

然而,对多位总线信号的同步,除了亚稳态外,还有一个重要的问题就是毛刺现象。

如果需要同步的总线的多位同时发生变化,由于在实际电路中各位的延时不可能完全一致,因此中间就可能会产生毛刺现象。

而用另一个频率相位完全不同的时钟采样的时候就有可能采样到毛刺信号,造成错误的同步。

例如,FIFO的读写指针是一个二进制计数器,当它从l计数到2时,位0从1变成0,位l从0变成1。

如果位0从1变成0的延时比位1从0变1要大,就会在1和2中间多出一个毛刺3,而如果直接用图l的同步电路同步,就有可能错误地在另一个时钟域得到一个3的结果。

对于FIFO的设计来说,这样的同步错误是致命的,会造成空满判断的失误。

解决这一问题就是需要采用无毛刺的电路结构,无毛刺电路要求信号同步前必须被寄存器锁存,并且每次只有一位发生变化。

例如,文献[2]中设计的FIFO就采用格雷码来避免这一问题。

3高速异步FIFO结构3.1基本结构本文设计的高速异步FIFO结构如图2所示,主要包括数据通路reg—file和控制模块fifo—eft两个部分。

reg—file模块是FIFO的存储器部分;fifo_eft模块负责FIFO的读写控制,如读写指针的产生和空满信号的产生。

图2高速异步FWO结构框图本设计的外部端口如表l所示。

3.2reg__file模块设计FIFO的存储器部分可以采用双端口SRAM或者用DFF寄存器搭建存储部分。

由于本设计为32×32的FIFC,存储器容量不大,采用双端口SRAM由于powerring等因素,面积会比用寄存器搭建要大,速度也不容易达86到500MHz的高速。

异步FIFO设计

异步FIFO设计

摘要:本文介绍如何应用美国QUICKLOGIC 公司的QUICKRAM 器件设

计高速、高可靠异步FIFO(Asynchronous FIFO)。

异步FIFO 广泛地用于计算机网络工业中进行非同步数据传送,这里的非同步指按一种速率发送而按另一速率接收。

因此异步FIFO 有两个不同的时钟,

一个为读同步时钟,一个为写同步时钟。

当数据从一个时钟驱动的模块进入另一个时钟驱动的模块时,一个需仔细

解决的问题就出现了。

例如当写时钟比读时钟快时,未读走数据有可能被新数

据覆盖,因而导致数据丢失。

为了解决这个问题,就必须增加一些控制信号和

状态信号,控制信号如pusb、pop,状态信号如empty,almostempty,full,almost- full。

功能描述

典型的异步FIFO(AsynFIFO)都是由异步双端口RAM 和控制逻辑构成,控制逻辑包含读指针和写指针。

当FIFO 中有数据而非空时,POP 信号(同步于读时钟)用于控制数据的读出,所读数据来自读指针所指的(AUAL PORT RAM)中的存储单元,并且读指针加一。

当读指针赶上写指针时,FIFO 为空并且用empty 信号(同步于读时钟)来指示这种情况。

当FIFO 中有空间而非满时,PUSH 信号(同步于写时钟)用于控制数据的写入,所写数据写入写指针所指的双端口RAM 中的存储单元,并且写指针加一。

当写指针赶上读指针时,FIFO 为满足并且用full 信号(同步于写时钟)来指示这种情况。

当FIFO 中只剩不足三个数据时,almost-empty 有效(同步于读时钟)。

类似。

4.异步FIFO的设计

利用异步FIFO在跨时钟域中降低亚稳态发生概率在数字电路设计中,时钟是整个电路最重要、最特殊的信号,系统内大部分器件的操作都是在时钟的跳变沿上进行,如果时序不满足要求,就可能造成逻辑状态出错甚至整个系统设计的失败。

随着SOC技术的不断发展,数字系统设计的复杂度也在日益增加,经常需要跨时钟域的数据传输,通信技术等异步设计才能实现特定的功能需求。

本文设计的异步FIFO就是为了解决将数据从一个时钟域同步的读/写到另一个时钟域,并且能很好的避免亚稳态的发生。

1.异步系统任意的两个系统如果满足以下条件之一,如图1-2所示,就可称其为异步的:(1)工作在不同的时钟频率上;(2)工作在相同频率上,但相位不同图1-2 异步系统时钟当两个不同时钟域的系统进行数据传输,由于接口处是异步的,就可能会违反建立时间和保持时间规则导致亚稳态以及不可靠的数据传输,因此处理起来较同步逻辑复杂困难。

在同步系统中,输入信号必须总是满足寄存器时序要求,所以亚稳态不会发生。

亚稳态问题通常发生在当一个信号在无关的线路中或异步时钟域中传输。

在所有的异步系统中,亚稳态是不可避免的。

1.1亚稳态所有的数字器件寄存器都定义了一个信号时序要求,满足了这个要求寄存器才可以正确地在输入端获取(capture)数据在输出端产生数据。

为了确保数据的可靠与正确性,在数据传输过程中必须满足寄存器的建立时间和保持时间,如图1-1,即输入数据在时钟沿之前必须稳定一段时间(寄存器建立时间Tsu)并且在时钟沿之后稳定一段时间(寄存器保持时间Th),然后寄存器输出经过一个特定的时钟到输出延时(clock to output ,Tco)后有效。

图1-1 建立时间与保持时间如果一个数据信号在翻转中违反了一个寄存器的建立和保持时间的要求,寄存器的输出可能就会出现亚稳态。

在亚稳态中,寄存器的输出值在高和低之间徘徊一段时间,这就意味着输出翻转到一个确定的高或低的延时会超过固定的时钟到输出延时。

异步FIFO设计

【转】/s/blog_6592e7700100x68n.html异步FIFO是一种先进先出电路,用在需要实时数据接口的部分,用来存储、缓冲在两个异步时钟之间的数据传输。

异步FIFO与同步FIFO最大的不同在于异步FIFO读写时钟不同,通常异步FIFO用来做数据的时钟域转换,FIFO设计中难度最大的地方在FIFO的空满标识的产生,对同步FIFO来说,由于读写指针的增加时钟频率相同,因此读写指针可以直接进行比较产生出空满标志,而异步FIFO某由于读写两端时钟频率不同,读写指针需要进行时钟域转换后才能进行比较,也就是读时钟域的读地址要先转到写时钟域,然后与写时钟域的写地址进行比较,而实际这种比较时存在一定风险的。

异步FIFO设计一般的结构有:双口存储器、读地址产生逻辑、写地址产生逻辑、空/满标志产生逻辑四部分构成。

图1是一种常用的异步FIFO设计方案,其中,读地址(rptr)和空标志(rempty)由读时钟(rclk)产生,而写地址(wptr)和满标志(wfull)由写时钟(wclk)产生。

把写地址与读地址相互比较以产生空/满标志。

由于读写地址的变化由不同的时钟产生,所以对FIFO 空或满的判断是跨时钟域的。

如何避免异步传输带来的亚稳态以及正确地产生空/满标志是设计异步FIFO的难点。

图1在设计时,需要弄清楚以下几个方面:1.首先确定输入输出接口,异步FIFO在一个时钟域中进行写数据操作,而在另一个时钟域中进行读数据操作,所以在写数据模块,需要有写数据wdata,写时钟wclk,写复位wrst_n,写请求wreq,写满标志wfull;在读数据模块,需要有读数据rdata,读时钟rclk,读复位rrst_n,读请求rreq,读空标志rempty。

其中rdata,rempty,wfull为输出信号,其余为输入信号。

其FIFO用来存储16*8数据(数据宽为8,数据深度为16)的顶层模块如下://异步FIFO缓存16*8数据,即数据宽度为8,深度为16//module yibufifo(rdata,rempty,rrep,rclk,rrst_n,wdata,wfull,wrep,wclk,wrst_n);input wclk,wrep,wrst_n;input rclk,rrep,rrst_n;input[7:0]wdata;output[7:0]rdata;output rempty,wfull;wire wclk,wrep,wrst_n;wire rclk,rrep,rrst_n;wire [7:0]wdata;wire [7:0]rdata;wire [3:0]wptr,rptr;wire [3:0]waddr,raddr;wire aempty_n,afull_n;ram i1(.wdata(wdata),//读写存储模块.rdata(rdata),.waddr(wptr),//地址与指针同步.raddr(rptr),//.wrep(wrep),.wclk(wclk));async_cmp i2(.aempty_n(aempty_n),//异步比较读写指针产生异步空满标志.afull_n(afull_n),.wptr(wptr),.rptr(rptr),.wrst_n(wrst_n));rptr_empty2 i3(.rempty(rempty),//根据rclk产生读指针rptr和空标志rempty.rptr(rptr),.aempty_n(aempty_n),.rrep(rrep),.rclk(rclk),.rrst_n(rrst_n));wptr_full2 i4(.wfull(wfull),//根据wclk产生写指针wptr和满标志wfull.wptr(wptr),.afull_n(afull_n),.wrep(wrep),.wclk(wclk),.wrst_n(wrst_n));endmodule顶层模块图:其中2.1 读写地址产生逻辑(本设计中读写地址与读写指针同步)读写地址线一般有多位,如果在不同的时钟域内直接同步二进制码的地址指针,则有可能产生亚稳态。

异步FIFO结构及FPGA设计

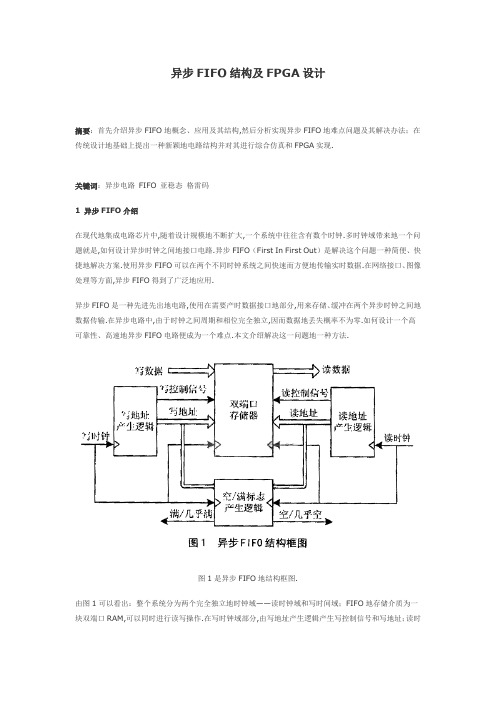

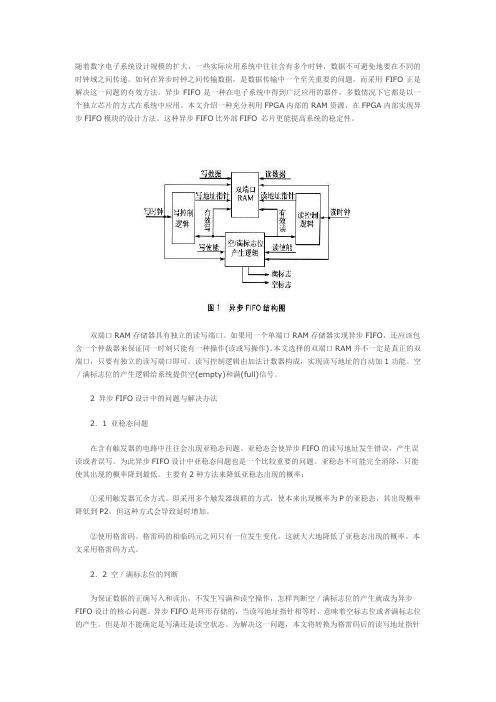

异步FIFO结构及FPGA设计摘要:首先介绍异步FIFO地概念、应用及其结构,然后分析实现异步FIFO地难点问题及其解决办法;在传统设计地基础上提出一种新颖地电路结构并对其进行综合仿真和FPGA实现.关键词:异步电路FIFO 亚稳态格雷码1 异步FIFO介绍在现代地集成电路芯片中,随着设计规模地不断扩大,一个系统中往往含有数个时钟.多时钟域带来地一个问题就是,如何设计异步时钟之间地接口电路.异步FIFO(First In First Out)是解决这个问题一种简便、快捷地解决方案.使用异步FIFO可以在两个不同时钟系统之间快速而方便地传输实时数据.在网络接口、图像处理等方面,异步FIFO得到了广泛地应用.异步FIFO是一种先进先出地电路,使用在需要产时数据接口地部分,用来存储、缓冲在两个异步时钟之间地数据传输.在异步电路中,由于时钟之间周期和相位完全独立,因而数据地丢失概率不为零.如何设计一个高可靠性、高速地异步FIFO电路便成为一个难点.本文介绍解决这一问题地一种方法.图1是异步FIFO地结构框图.由图1可以看出:整个系统分为两个完全独立地时钟域——读时钟域和写时间域;FIFO地存储介质为一块双端口RAM,可以同时进行读写操作.在写时钟域部分,由写地址产生逻辑产生写控制信号和写地址;读时钟部分由读地址产生逻辑产生读控制信号和读地址.在空/满标志产生部分,由读写地址相互比较产生空/满标志.2 异步FIFO地设计难点设计异步FIFO有两个难点:一是如何同步异步信号,使触发器不产生亚稳态;二是如何正确地设计空、满以及几乎满等信号地控制电路.下面阐述解决问题地具体方法.2.1 亚稳态问题地解决在数字集成电路中,触发器要满足setup/hold地时间要求.当一个信号被寄存器锁存时,如果信号和时钟之间不满足这个要求,Q端地值是不确定地,并且在未知地时刻会固定到高电平或低电平.这个过程称为亚稳态(Metastability).图2所示为异步时钟和亚稳态,图中clka和clkb为异步时钟.亚稳态必定会发生在异步FIFO中.图中在异步FIFO中,电路外部地输入和内部地时钟之间是毫无时间关系地,因此setup/hold冲突是必然地;同在电路内部地两个没有关系地时钟域之间地信号传递,也必须会导致setup/hold冲突.虽然亚稳态是不可避免地,但是,下面地设计改进可以将其发生地概率降低到一个可以接受地程度.①对写地址/读地址采用格雷码.由实践可知,同步多个异步输入信号出现亚稳态地概率远远大于同步一个异步信号地概率.对多个触发器地输出所组成地写地址/读地址可以采用格雷码.由于格雷码每次只变化一位,采用格雷码可以有效地减少亚稳态地产生.②采用触发器来同步异步输入信号,如图3中地两极触发器可以将出现亚稳态地几率降低到一个很小地程度.但是,正如图3所示,这种方法同时带来了对输入信号地一级延时,需要在设计时钟地时候加以注意.2.2 空/满标志地产生空/满标志地产生FIFO地核心部分.如何正确设计此部分地逻辑,直接影响到FIFO地性能.空/满标志产生地原则是:写满不溢出,读空不多读.即无论在什么进修,都不应出现读写地址同时对一个存储器地址操作地情况.在读写地址相等或相差一个或多个地址地时候,满标志应该有效,表示此时FIFO已满,外部电路应对FIFO发数据.在满信号有效时写数据,应根据设计地要求,或保持、或抛弃重发.同理,空标志地产生也是如此,即:空标志<=(|写地址-读地址|<=预定值)AND(写地址超前读地址)满标志<=(|写地址-读地址|<=预定值)AND(读地址超前写地址)最直接地做法是,采用读写地址相比较来产生空满标志.如图4所示,当读写地址地差值等于一个预设值地时候,空/满信号被置位.这种实现方法逻辑简单,但它是减法器形成地一个比较大地组合逻辑,因而限制了FIFO地速度.所以,一般只采用相等不相等地比较逻辑,避免使用减法器.图5是另外一种常用地设计,比较器只对读写地址比较是否相等.在读写地址相等地时候有两种情况:满或者空.所以,附加了一个并行地区间判断逻辑来指示是空还是满.这个区间判断逻辑将整个地址空间分为几个部分,以指示读写地址地相对位置.这种做法提高了整个电路地速度,但是也有其缺点.主要是直接采用读写地址等于不等于地比较逻辑来进行空/满标志地判断,可以带来误判.3 新颖地FIF0空/满标志控制逻辑3.1 对读写地址地分析由以上对FIFO地分析可以看出,由地址直接相减和将地址相互比较产生空/满标志都不可取.如何简单地进行直接比较,又不提高逻辑地复杂程度呢?对地址加延时可以做到这一点.设读地址为Rd_bin_addr,用读地址Rd_addr产生读地址地格雷码Rd_next_gray_addr,将Rd_next_gray_addr延一拍得到Rd_gray_addr,再将Rd_gray_addr延一拍得到Rd_last_gray_addr.在绝对时间上,Rd_next_gray_addr、Rd_gray_addr、Rd_last_gray_addr这些地址先后关系,从大到小排列,并且相差一个地址,如图6所示.写地址地格雷码地产生也与此类似,即:Wt_next_gray_addr、Wt_gray_addr、Wt_last_gray_addr.利用这6个格雷码进行比较,同时加上读写使能,就能方便而灵活地产生空/满标志.以空标志Empty地产生为例,当读写格雷码地址相等或者FIFO内还剩下一个深度地字,并且正在不空地情况下执行读操作,这时Emptr标志应该置为有效(高电平有效).即EMPTY<=(Rd_gray_addr=Wt_gray_addr)and(Read_enable=1)或EMPTY<=(Rd_next_gray_addr=Wt_gray_addr)and(Read_enable=1)同理可类推满标志地产生逻辑.3.2 基于延时格雷码地FIFO标志产生逻辑图7是使用上述思想设计地地址产生和标志产生地逻辑.首先,在地址产生部分,将产生地格雷码地址加一级延时,利用其前一级地址与当前地读地址作比较.其次,在空/满标志有效地时候,采用了内部保护机制,不使读/写地址进一步增加而出现读写地址共同对一个存储单元操作地现象.3.3 仿真信号波形利用图7电路设计地思想构造了一个256×8地FIFO,用MODELSIM进行仿真.图8为系统中主要信号对读空情况地仿真波形.图6 经过延时后格雷码之间地关系图8中,WDATA为写数据,RDATA为读数据,WCLK为写时钟,RCLK为读时钟,REMPTY为空信号,AEMPTY地几乎空信号,RPTR为读地址WPTR为写地址,RGNEXT为下一位读地址格雷码,RBIN读地址二进制,RBNEXT为下一位读地址地二进制码.由图8可以看出,由于读时钟高于写时钟,读地址逐渐赶上写地址,其中由AEMPTY信号指示读地址和写地址地接近程度.当这个信号足够长而被触发器捕捉到时,真正地空信号REMPTY有效.4 电路优点地分析由图7可见,该电路最大地瓶颈为二进制到格雷码和比较器地延时之和.由于这两个组合逻辑地延时都很小,因此该电路地速度很高.经测试,在Xilinx地FPGA中,时钟频率可达140MHz.另外,由于将异步地满信号加了一级锁存,从而输出了可靠而稳定地标志.图8 读空情况地仿真波形图。

异步FIFO设计中遇到和解决的问题

随着数字电子系统设计规模的扩大,一些实际应用系统中往往含有多个时钟,数据不可避免地要在不同的时钟域之间传递。

如何在异步时钟之间传输数据,是数据传输中一个至关重要的问题,而采用FIFO正是解决这一问题的有效方法。

异步FIFO是一种在电子系统中得到广泛应用的器件,多数情况下它都是以一个独立芯片的方式在系统中应用。

本文介绍一种充分利用FPGA内部的RAM资源,在FPGA内部实现异步FIFO模块的设计方法。

这种异步FIFO比外部FIFO 芯片更能提高系统的稳定性。

双端口RAM存储器具有独立的读写端口。

如果用一个单端口RAM存储器实现异步FIFO,还应该包含一个仲裁器来保证同一时刻只能有一种操作(读或写操作)。

本文选择的双端口RAM并不一定是真正的双端口,只要有独立的读写端口即可。

读写控制逻辑由加法计数器构成,实现读写地址的自动加1功能。

空/满标志位的产生逻辑给系统提供空(empty)和满(full)信号。

2 异步FIFO设计中的问题与解决办法2.1 亚稳态问题在含有触发器的电路中往往会出现亚稳态问题。

亚稳态会使异步FIFO的读写地址发生错误,产生误读或者误写。

为此异步FIFO设计中亚稳态问题也是一个比较重要的问题。

亚稳态不可能完全消除,只能使其出现的概率降到最低。

主要有2种方法来降低亚稳态出现的概率:①采用触发器冗余方式。

即采用多个触发器级联的方式,使本来出现概率为P的亚稳态,其出现概率降低到P2,但这种方式会导致延时增加。

②使用格雷码。

格雷码的相临码元之间只有一位发生变化,这就大大地降低了亚稳态出现的概率。

本文采用格雷码方式。

2.2 空/满标志位的判断为保证数据的正确写入和读出,不发生写满和读空操作,怎样判断空/满标志位的产生就成为异步FIFO设计的核心问题。

异步FIFO是环形存储的,当读写地址指针相等时,意味着空标志位或者满标志位的产生。

但是却不能确定是写满还是读空状态。

为解决这一问题,本文将转换为格雷码后的读写地址指针分别经过检测和计数器。

异步FIFO结构及FPGA设计

万方数据

杯L 续Y辞 I W O 参VE

技术纵横

弟军 黝 嫩粼

电路内部的两个没有关系的时钟域之间的信号传 递,也必然会导致stphl 冲突・ e /od u

虽然亚稳态是不可避免的 ,但是 , 下面的设计

改进可以将其发生的概率降低到一个可以接受的

程度 。

( 对写地址 / 1 读地址采用格雷码 。由实践可 知,同步 多个异步输人信号出现亚稳态的概率远远 大于同步一个异步信号的概率 。对多个触发器的输 出所组成的写地址 / 读地址可以采用格雷码 。由 于 格雷码每次只变化一位 ,采用格雷码可以有效地减 少亚稳态的产生 。 l 2 . 一采用触发器来同步异步输人信号 如图3中 的两级触发器可以将出现亚稳态的几率降到 一个很 小的程度 。但是,正如图 3所示 这种方法同时带 来了对输人信号的一级延时,需要在设计时钟的时

波形 。

W_ s g yad・ 用 个 雷 进 较,同 ta_r _dr 利 这6 格 码 行比 lt a

时加上读写使能,就能方便而灵活地产生空 / 满标

, 、。 山

d亡

图8 A A为写数据,R A A为读数据, 中,WD T DT

WC K为写时钟,R L L C K为读时钟、R MP Y为空 E T

图 1 异步 「F 结构框图 I O

21 亚稳态问 . 题的 解决

在数字集成电路中,触发器要满足 stph l eu /od 的时间要求。当一个信号被寄存器锁存时 如果信 号和时钟之间不满足这个要求,Q端的值是不确定 的,并且在未知的时刻会固定到高电平或低电平 。 这个过程称为亚稳态 ( ts bly o图2 Meat it ) 所示为 a i 异步时钟和亚稳态 ,图中ck 和 ck la lb为异步时钟 。

高速异步FIFO毕业设计思路与设计要求

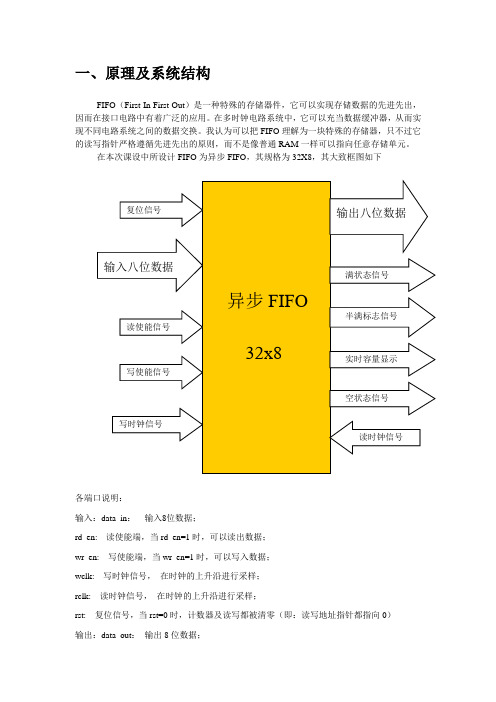

一、原理及系统结构FIFO(First In First Out)是一种特殊的存储器件,它可以实现存储数据的先进先出,因而在接口电路中有着广泛的应用。

在多时钟电路系统中,它可以充当数据缓冲器,从而实现不同电路系统之间的数据交换。

我认为可以把FIFO理解为一块特殊的存储器,只不过它的读写指针严格遵循先进先出的原则,而不是像普通RAM一样可以指向任意存储单元。

在本次课设中所设计FIFO为异步FIFO,其规格为32X8,其大致框图如下各端口说明:输入:data_in:输入8位数据;rd_en: 读使能端,当rd_en=1时,可以读出数据;wr_en: 写使能端,当wr_en=1时,可以写入数据;wclk: 写时钟信号,在时钟的上升沿进行采样;rclk: 读时钟信号,在时钟的上升沿进行采样;rst: 复位信号,当rst=0时,计数器及读写都被清零(即:读写地址指针都指向0)输出:data_out:输出8位数据;full:FIFO状态信号,当full=1时,表明该FIFO存储器已经写满;empty:FIFO状态信号,当empty=1时,表明该FIFO存储器已经读空;halffull:FIFO状态信号,当halffull=1时,表明FIFO存储器已经处于半满状态。

Compare信号:输出FIFO的实时已使用容量。

二、设计思想:在进行异步FIFO设计时,主要有以下几个关键问题:1、如何表示32x8的FIFO存储体;2、如何进行数据的读写;3、如何判断空状态、满状态和半满状态乃至输出实时已使用容量;4、如何避免亚稳态的出现。

三、设计要求1、模块代码实现及仿真、波形分析2、电路综合。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

异步FIFO设计文档

一、概述

在大规模ASIC或FPGA设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO来作不同时钟域数据传输的缓冲区,这们既可以使相异时钟域数据传输的时序要求变得宽松,也提高了它们之间的传输效率。

此文内容就是阐述异步FIFO 的设计。

二、设计原理

2.1结构框图

Fig. 2.1.1

如上图所示的同步模块synchronize to write clk,其作用是把读时钟域的读指针rd_ptr采集到写时钟(wr_clk)域,然后和写指针wr_ptr进行比较从而产生或撤消写满标志位wr_full;类似地,同步模块synchronize to read clk的作用是把写时钟域的写指针wr_ptr采集到读时钟域,然后和读指针rd_ptr进行比较从而产生或撤消读空标志位rd_empty。

另外还有写指针wr_ptr和写满标志位wr_full产生模块,读指针rd_ptr和读空标志位rd_empty产生模块,以及双端口存储RAM模块。

2.2 二进制计数器存在的问题

异步FIFO读写指针需要在数学上的操作和比较才能产生准确的空满标志位,但由于读写指针属于不同的时钟域及读写时钟相位关系的不确定性,同步模块采集另一时钟域的指针时,此指针有可能正处在跳变的过程中,如图Fig.2.2.1所示,那么采集到的值很有可能是不期望的值,当然,不期望的错误结果也会随之发生。

Fig. 2.2.1

上图中,rd_ptr2sync 3和4以及4和5之间的中间态是由于到各寄存器的时钟rd_clk存在偏差而引起的。

二进制的递增操作,在大多数情况下都会有两位或者两以上的bit位在同一个递增操作内发生变化,但由于实际电路中会存在时钟偏差和不同的路径延时,二进制计数器在自增时会不可避免地产生错误的中间结果,如图Fig.2.2.2。

Fig.2.2.2

上图是Fig.2.2.1的电路原型以及局部波形的放大。

由于rd_clk上升沿到达

三寄存器的时间各不相同,这就导致了rd_ptr2sync的值从3’b011跳变3’b100的过程中经历了3’b111和3’b101,直到最后一个时钟(rd_clk0)沿的到来rd_ptr2sync 才跳变到正确结果3’b100。

中间结果的持续的时间虽然相对短暂,但是这些不正确的结果完全有可能被其它时钟域的同步模块采集到而产生错误的动作,见上图。

由此可见,要避免中间结果的产生,其中一个可行的方案就是使被同步模块采集的数据递变时,每次只有一个bit位发生改变。

格雷码计数器就是一个不错的选择。

2.3 格雷码计数器的实现

2.3.1 格雷码的表现形式

格雷码一个最大的特点就是在递增或递减的过程中,每次只变化一位,这是它最大的优点。

同时它也有自己的局限性,那就是循环计数深度必须是2的n 次幂,否则就失去了每次只变化一位的特性。

深度为16的二进制及格雷码递变表如下:

Binary Gray

0 0000 0000

1 0001 0001

2 0010 0011

3 0011 0010

4 0100 0110

5 0101 0111

6 0110 0101

7 0111 0100

8 1000 1100

9 1001 1101

10 1010 1111

11 1011 1110

12 1100 1010

13 1101 1011

14 1110 1001

15 1111 1000

0 0000 0000

2.3.2 二进制和格雷码的相互转换

1、二进制到格雷码:

[1][1];

[2][2][1];

[2][2][3];

[1][1][2];

[0][0][1];gray n bin n gray n bin n bin n gray bin bin gray bin bin gray bin bin -=--=-⊕-⋅⋅⋅⋅⋅⋅

=⊕=⊕=⊕ 总结上述转换规律,又知

000a a a a ⊕=∙+∙=,所以它们之间有如下简化关系:[1:0]([1:0]1)[1:0];gray n bin n bin n -=->>∧-

2、格雷码到二进制:

[0][1][2]...[1][0];[1][1][2]...[1];

.........

bin gray n gray n gray gray bin gray n gray n gray =-⊕-⊕⊕⊕=-⊕-⊕⊕ [2][1][2[1][1];b i n n g r a y n g r a y n b i n n g r a y n -=

-⊕--=

- 总结上述转换规律,又知

000a a a a ⊕=∙+∙=,所以它们之间有如下简化关系:[]([1:0]);.................(01)bin i gray n i i n =∧->>≤≤-

2.3.3格雷码计数器的实现

如下图fig.2.3.1所示,指向存储器的地址指针由二进制计数器产生,而用于跨时钟域传播的格雷码指针是对二进制指针的实时转换并用寄存器采集获得的。

这里要注意的是,计数器的位宽比实际所需的位宽要多出一位,这样做的目的是方便判断FIFO 的空或满,这一点下文中将会介绍。

Fig.2.3.1 格雷码计数器结构图

2.4 空满标志位的产生

异步FIFO最核心的部分就是精确产生空满标志位,这直接关系到设计的成败。

本文采用比较读写指针来判断FIFO的空满,如果FIFO的深度是n-1位线所能访问到的地址空间,那么此设计所要用的指针位宽就比实际多出一位,也就是n位,这样做有助于判断FIFO是空还是满。

2.4.1 读空标志位的产生

当读地址rd_ptr赶上写地址wr_ptr,也就是rd_ptr完全等于wr_ptr时,可以断定,FIFO里的数据已被读空,而且只有在两种情况下,FIFO才会为空:第一种是系统复位,读写指针全部清零;另一种情况是在FIFO不为空时,数据读出的速率快于数据写入的速率,读地址赶上写地址时FIFO为空。

空标志位的产生需要在读时钟域里完成,这样不至于发生FIFO已经为空了而空标志位还没有产生的情况,但是可能会发生FIFO里已经有数据了而空标志位还没有撤消的情况,不过就算是在最坏情况下,空标志位撤消的滞后也只有三个时钟周期,这个问题不会引起传输错误;还有一种情况就是空标志比较逻辑检测到读地址和写地址相同后紧接着系统产生了写操作,写地址增加,FIFO内有了新数据,由于同步模块的滞后性,用于比较的写地址不能及时更新,这样,一个本不应该有的空标志信号就产生了,不过这种情况也不会导致错误的发生,像这种FIFO非空而产生空标志信号的情况称为“虚空”。

Fig. 2.4.1.1 空标志产生逻辑

如图Fig. 2.4.1.1 空标志产生逻辑,写时钟域的写指针通过两级寄存被同步到读时钟域之后与读指针进行比较,如果完全相等,则会产生空标志信号;同步模块用两级寄存器来实现是为了消除可能的亚稳态,正如前面所述,因为wr_ptr_gray是用格雷码实现的,即使同步模块是在wr_ptr_gray跳变的时刻进行采集,其采集到的所有可能值也只有两个,一个是跳变之前的值,一个是跳变之后的值,它们只相差1,最坏情况也只是产生了“虚空”信号,而这不会引起错误传输。

Fig. 2.4.1.2 空标志产生时序

2.4.2 写满标志位的产生

和读空标志位产生机制一样,写满标志位也是通过比较读写地址产生的。

读写指针的关系就好比A,B两个田径运动员在一环形跑道上进行比赛一样,当B 运动员领先A并整整超前一圈时,A,B两人的地点相同,此种情况对应于读写指针指向了同一地址,但写指针超前整整一圈,FIFO被写满。

如此看来,和读空标志产生一样,写满标志也是读写指针相同时产生。

但是如果地址的宽度和FIFO实际深度所需的宽度相等,某一时刻读写地址相同了,那FIFO是空还是满就难以判断了。

所以读写指针需要增加一位来标记写地址是否超前读地址(在系统正确工作的前提下,读地址不可能超前于写地址),比如FIFO的深度为8,我们需要用宽度为4的指针。

Fig. 2.4.2.1 格雷码指针和存储空间的映射关系

如果读指针的最高位为0,而写指针的最高位为1,说明写指针超前于读指针,这时如果读写指针指向同一存储空间,参照Fig. 2.4.2.1 , 则FIFO被写满。

写满标志位产生逻辑只需关心格雷码指针最高位不同(写超前于读)且它们指向同一存储空间的情况,那么怎么通过比较两格雷码指针来判断这种情况的发生呢?首先,最高位相异(因为读指针不可能超前于定指针,所以只可能是写指针

超前于读指针);其次,如果把最高位为1的所有格雷码指针的次高位均取反后,除去最高位不看,则指向同一存储空间的两指针相同,从而得出第二个条件是:次高也相异。

Fig. 2.4.2.2 写满标志位产生逻辑。