异步fifo设计及时序约束设置

异步fifo的sdc约束

异步fifo的sdc约束

异步FIFO的时序约束是设计异步FIFO时非常重要的一步,它确保了数据在FIFO中的稳定传输。

在进行时序约束时,需要考虑时钟域的转换、数据传输的延迟以及时序分析等因素。

以下是针对异步FIFO的SDC约束的多角度回答:

1. 时钟域转换,在异步FIFO中,往往会涉及到不同时钟域之间的数据传输,因此需要在时序约束中明确指定数据从一个时钟域到另一个时钟域的延迟限制。

这样可以确保数据在时钟域之间的稳定传输。

2. 时钟频率,在SDC约束中,需要指定异步FIFO所使用的时钟频率。

这有助于综合工具正确地分析和优化FIFO的时序性能。

3. 数据传输延迟,对于异步FIFO的写入和读取操作,需要在SDC约束中指定数据传输的延迟限制。

这有助于确保数据能够按时到达目的地,并且在读取时能够正确地被采样。

4. 时序分析,在SDC约束中,需要进行综合和时序分析,以确保异步FIFO在不同工艺、温度和电压条件下都能正常工作。

这包括

时序收敛、时序边界的定义等方面的约束。

5. 时序路径约束,在异步FIFO的时序约束中,需要指定关键

路径和时序收敛路径,以确保FIFO的关键路径能够满足时序要求,

并且各个路径能够在设计规定的时钟周期内完成。

综上所述,异步FIFO的SDC约束涉及到时钟域转换、时钟频率、数据传输延迟、时序分析以及时序路径约束等方面。

合理设置这些

约束可以确保异步FIFO在实际应用中能够稳定可靠地工作。

Quartus II LPM使用指南(FIFO篇)

下图中是 SCFIFO 和 DCFIFO 的框图,其中,SCFIFO 中读写双方信号与时钟 clock 同步,DCFIFO 读写双方信号分别与读写时钟同步。

表一中列出 FIFO 中各个 IO 的详细描述: 表一 端口描述

端口

类型 是否必选

描述

Clock

输入

是

上升沿触发时钟

Wrclk

当该信号有效时,FIFO 会被认为已经读空,此时不能 再进行读操作;

准装满信号,当 usedw 大于参数 almost_full_value 或 相同时,该信号被激活,即是 full 信号被激活的预示; 准读空信号,当 usedw 小于参数 almost_empty_value 或相同时,该信号被激活,即是 empty 信号被激活的 预示; 显示当前 FIFO 中数据存量。

Rdreq

输入

是

Sclr

输入

非

Aclr

Q

输出

是

Full Wrfull Rdfull Empty Wrempty Rdempty Almost_full

输出

非

输出

非

输出

非

Almost_empty

输出

否

Usedw Wrusedw Rdusedw

输出

否

FIFO 篇

第 -5- 页

Rdreq Rdfull Rdempty Rdusedw 当 wrreq 有效时数据线上的数据通过 DATA 端口被写 入 FIFO 中 写请求信号,激发写入操作。 1.当 full(对于 SCFIFO)或 wrfull(对于 DCFIFO)有 效时,不能激活 wrreq 信号,参数 overflow_checking 设置为 ON,即在 full 状态下 FIFO 会自动无视写请求; 2.不能再 aclr 有效期间激活 wrreq 信号; 3. 使 用 Stratix 和 Cyclone 系 列 器 件 ( 除 了 Stratix, Stratix GX, 和 Cyclone 系 列 以 外 ) 需 要 将 write_aclr_synch 参数选择位 ON,确保符合限制条件。 读请求信号,激发读出操作。 1. 该信号 的作用在正 常模式下和 在预读模式 下的作用 有很多不同(详情见后文); 2.当 empty(对于 SCFIFO)或 rdempty(对于 DCFIFO) 有效时,不能激活 rdreq 信号,参数 underflow_checking 设置为 ON,即在 full 状态下 FIFO 会自动无视读请求; 清零端口,详情见后文

一种高性能异步FIFO的设计与实现

27卷 第8期2010年8月微电子学与计算机M ICROELECTRONICS &COM PUTERVol.27 No.8August 2010收稿日期:2010-05-13;修回日期:2010-06-08一种高性能异步FIFO 的设计与实现李 冬1,赵志凯2(1中国矿业大学信息与电气工程学院,江苏徐州221008;2中国矿业大学计算机科学与技术学院,江苏徐州221008)摘 要:提供了一种全新的高性能异步FIF O 设计方案.首先定义了F IFO 的通信协议和总体结构设计,然后围绕如何提高FIF O 性能依次论述了存储阵列设计、读写控制逻辑和空/满判断逻辑的设计方法.通过与FPGA 本身的F IF O 模块比较,该方案可以提高FI FO 性能30%以上.关键词:异步F IFO ;亚稳态;多时钟中图分类号:T P302 文献标识码:A 文章编号:1000-7180(2010)08-0145-04Design and Implementation of High Performance Asynchronous FIFOLI Dong 1,ZHAO Zhi kai 2(1School of I nformation and Electr ical Engineering,China U niversity of M ining and T echnolog y,Xuzhou 221008,China;2School of Co mputer Science and T echnolo gy,China U niversity of M ining and T echnology ,Xuzhou 221008,China)Abstract:T hi s paper presents a high performance FIF O desig n t hat interfaces subsystems on a chip working at different speeds.T he communication protocol and the ar chitecture of F IFO are pr oposed at first.A im at improving its operation speed,the design of stor ag e array,read/w rite control logic and full/empty status logic are described par ed with the ex isting F IFO block,the desig n s performance improv ement r atio is more than 30percent.Key words:asy nchr onous FIF O;meta stability;multiple clock1 引言随着计算机及电子器件的飞速发展,高速处理器中的逻辑越来越复杂,芯片规模不断扩大,在一个芯片中常常含有多个不同的高速时钟.当数据从一个时钟域传输到另一个时钟域时,确保数据在高速状态下的可靠传输就成为一个重要问题.异步FIFO (First In First Out)单元成为解决这类跨时钟域的数据可靠传输问题的不可缺少的元件.异步FIFO 是一个缓冲存储部件,用于在两个不同时钟域之间进行数据交换.数据从一个时钟域生成并写入FIFO,然后从另外的时钟域读出并被使用.为了提高FIFO 的性能,需要精心设计FIFO 的体系结构和电路实现.为此,文中对已有的工作进行了仔细研究.不同的设计有不同的读写控制策略和空/满逻辑判断方法.有些方法会导致性能降低,比如存储阵列会严重影响系统性能[1]、在设计中使用减法器来进行空/满逻辑判断也会降低系统性能[2].文中基于FIFO 存储电路的功能和特点,讨论了FIFO 设计的关键技术,重点探讨了高性能异步FIFO 的设计和实现方法.2 总体结构2.1 外部端口FIFO 是一种用来作为缓冲的存储器,它能对数据进行快速顺序的存储和发送,主要用来解决不同速率器件间的速率匹配问题.图1是采用FIFO 连接的数据通信系统.图1中,数据发送系统和数据接收系统采用不同的工作时钟.数据发送系统产生数据,数据接收系统使用数据.FIFO 模块通过不同的端口分别与数据发送系统和数据接收系统连接,其中与数据发送系统连接的端口统称为 写端口!,与数据接收系统图1 采用F IFO 连接的数据通信系统连接的端口统称为 读端口!.写端口包括四组信号,分别是:(1)req put 来自数据发送系统的发送请求信号;(2)data put 数据发送总线;(3)full 该值为1时表示FIFO 存储空间满;(4)clk put 数据发送系统工作时钟.读端口包括五组信号:(1)req get 来自数据接收系统的数据请求信号;(2)valid get 标志接收的数据是否有效;(3)empty 该值为1时表示FIFO 存储空间空;(4)data get 数据接收总线;(5)clk get 数据接收系统工作时钟.2.2 通信协议FIFO 的写端口和读端口分别遵循不同的通信协议.写端口的数据通信协议如下:当数据发送系统有数据需要传输时,在clk put 时钟上升沿来临之前,数据需要放在dataput总线上,并给出req put 信号,如果在时钟上升沿来临时,full 信号为低电平,则数据被写入FIFO.如果时钟上升沿来临时,full 为高电平,则数据发送系统需要一直等待full 信号变为低电平,数据才能正常发送.如图2所示,在时钟沿A,数据被正确写入FI FO;在时钟沿B,数据不能被写入FIFO,需要等待FIFO 腾空.图2 F IFO 写端口的时序图读端口的数据通信协议如下:当数据发送系统有数据需要传输时,在clk get 时钟的上升沿来临之前,数据接收系统首先发送req g et 信号,如果FIFO 中存在有效数据,那么数据将被放在data get 数据总线上,同时valid g et 和em pty 信号也被置为相应的值.在clkget 的下一个时钟沿来临时,数据接收系统可以根据后两个信号来决定数据总线上的data get 数据是否有效.valid get 表示当前读取的数据是否有效,empty 表示当前数据读取之后,FIFO 是否为空,在系统初始化时,empty 的初值置为0.2.3 结构设计FIFO 的总体结构如图3所示.与RAM 相比,FIFO 对存储阵列按顺序读写,不需要额外的地址端口.图3 FI FO 的总体结构FIFO 的存储阵列类似于一片双端口的RAM,可以同时执行读操作和写操作,读写操作受控于不同的时钟.空/满状态判断逻辑根据读、写指针的变化实时检测当前FIFO 的空/满状态.读控制和写控制逻辑分别根据相应的读写信号,控制存储存储阵列执行读操作和写操作.3 存储阵列与读写控制逻辑改善存储阵列与读、写控制逻辑是提高FIFO 性能的有效途径.3.1 存储阵列设计当前广泛使用的片上存储单元有SRAM 、DRAM 和Flash 等多种形式.由于对FIFO 进行读、写操作的性能与存储阵列的性能密切相关,因此我们选择SRAM 来构建存储整列.SRAM 是静态随机存取存储器,它的每一个单元由6个尺寸不同的晶体管构成[1],它存储数据是依靠晶体管之间的正反馈结构.在执行读写操作时,由于它既不需要像DRAM 那样的预充电-求值过程,也不需要Flash 那样的编程-擦除过程,因而效率较高.146微电子学与计算机2010年通过对晶体管尺寸的优化,读写性能可以得到较大改善.为了加快读操作的时间,SRAM采用了灵敏放大单元,以便加快读操作的时间并提高数据的可靠性.多个SRAM单元排列在一起构成了存储阵列.为了便于同时优化读、写性能,阵列的排列需要尽量接近方形.3.2 读写控制逻辑FIFO的读写控制逻辑控制读写指针和存储阵列进行工作.FIFO对存储阵列按地址依次读写.系统初始化之后,FIFO的读写指针均指向0地址,每执行一次读操作或者写操作,相应的读写指针顺序加1.当指针移到存储阵列的最后一个位置后,下一个操作会使指针返回地址0.读写指针如此周而复始地变化,FIFO空间得到了最有效的运用.写指针总是指向下一个要写入的单元,每执行完一次写操作后,写指针指向下一个将要写入的存储单元.在写操作之前,需要判断写指针指向的单元是否可以写入,这需要空/满判断逻辑的信号支持.在clk put时钟的上升沿,如果req put信号有效,并且full无效,那么数据data put在这一时钟沿被写入存储阵列,同时写指针加1指向下一个将要被写入的单元.如果full信号有效,那么req put信号需要一直保持,直到full信号无效数据才能被写入.与此类似,读指针总是指向当前被读出的单元.每执行完一次读操作后,读指针指向下一个将要读出的存储单元.在读操作之前,需要判断读指针指向的单元是否可以读出,这需要空/满判断逻辑的信号支持.在clk get时钟的上升沿,如果req get信号有效,并且empty无效,那么数据在这一时钟沿被放在data g et数据总线上,同时读指针加1指向下一个将要被写入的单元,valid get信号置为有效.如果empty信号有效,那么valid get信号被置为无效,req get信号需要一直保持,直到empty信号无效数据才能被读出.对于数据量比较大的异步通信系统来说,上述读写控制逻辑可以实现每个时钟周期写入或者读出一个数据项,大大提高了数据读写的效率.同时,时序控制逻辑简单,便于实现.我们采用verilog语言实现了上述读写控制逻辑,并通过逻辑综合在FP GA中进行了实现.4 空/满判断逻辑分析4.1 空/满判断逻辑在FIFO进行读写操作之前,需要正确判断FI FO的存储状态,以免出现误读或者误写.正确判断FIFO的空/满状态是FIFO设计的关键点之一.空/满状态判断的原则是写满而不溢出,读空而不多读[3],以免造成数据丢失或者误用.如何设计FIFO[4]的空/满状态判断逻辑关系FIFO的读写性能.当读写指针在同一时刻指向同一个内存位置时,FIFO处于空或者满状态,否则为非空非满状态,FIFO可以随意执行读写操作.然而,当读写指针重合时,具体是空还是满要通过逻辑进行分析.传统的判断方法是另外设置一个状态位[5],作为最高位,其余作为地址位.当系统初始化时,状态位和地址位均置0.当读写指针的地址位和状态位全部吻合时,FIFO处于空状态;当读写指针的地址位相同而状态位不同时,说明写指针比读指针多循环一次,FIFO处于满状态.这种状态判断逻辑工作频率低且占面积大,不适用于高度集成化和快速数据处理的场合[3].为了快速判断空/满状态,我们采用为每个存储单元附加一个锁存器来标志单元的存储状态.当某个单元被写入数据时,锁存器被置1表示单元处于满状态.当某单元的数据被读出时,锁存器的状态被置0,表示单元处于空状态.假设第i个单元的满状态用f i表示,空状态用ei表示.对于含有N个存储单元的FIFO来说,可以分别采用式(1)和式(2)来进行空/满状态判断.公式中的AND和OR分别表示逻辑与!操作和逻辑或!操作.full=ANDNi=1(f i)(1)em pty=ORNi=1(ei)(2)以上判断逻辑如果用组合逻辑实现,虽然运行效率较高,但是逻辑规模大,需要占用较大的芯片面积.为了克服这个缺点,采用动态逻辑来实现状态判断,从而在减小芯片面积的同时获得更高的运行效率.图4是采用动态逻辑来判断含有4个存储单元的FIFO的空/满状态判断的电路图.从图中可以看出,空/满判断逻辑只需要较少的芯片资源.对于含有更多存储单元的FIFO来说,判断逻辑可以进行相似的扩充.4.2 亚稳态的避免异步电路设计需要妥善处理亚稳态的问题.当异步信号在不同的时钟域中传输时,由于工作时钟不同,如果某信号在变化的过程中恰好被采样,那么采样信号的状态变得不可确定,这种现象称为亚稳态[1].147第8期李冬,等:一种高性能异步FI FO的设计与实现图4 采用动态逻辑的空/满状态检测电路在异步FIFO的设计中,发送端口和接收端口采用不同的工作时钟.而空/满判断逻辑与两个时钟均密切相关,因而可能产生亚稳态的问题.一旦产生亚稳态,说明信号电平不稳定.如果这种状况持续的时间大于一个时钟周期,不稳定的数据状态就会造成下一级的触发器错误接收或者发送电平信号,从而影响整个FIFO的数据传输.在异步FIFO数据传输过程中,由于发送端和接收端的时钟不同,建立时间和保持时间的冲突不可避免,因而一定会产生亚稳态的问题.解决亚稳态的问题需要从分析时序电路的特性入手.对于时序器件来说,信号相对于时钟满足建立时间和保持时间是保证信号被可靠采样的前提.根据亚稳态产生的条件,可以对不同时钟域输入的信号采用双所存器连续锁存两次.如果第一个锁存器锁存到一个不稳定的电平信号,在经过一个时钟后可能趋于稳定,从而得到一个稳态的信号值.虽然亚稳态不可避免,但采用这种双所存结构之后,电路出现亚稳态的概率可以将到非常低的程度.5 实验验证采用FPGA对文中设计的FIFO的控制逻辑和状态检测逻辑进行了验证.数字逻辑部分采用了Verilog硬件描述语言进行实现.验证实验在Falcon -E25T G开发平台上进行,使用的FPGA为Xilinx 的SPARTAN3E.设计和仿真环境采用Xilinx的ISE9.1i.FIFO的存储体部分例化了FPGA提供的块RAM.FIFO的数据宽度为8位,深度为4096.通过实验,文中设计的FIFO单元的读写性能可以达到400MH z左右,比ISE工具自动生成的FIFO单元的工作频率提高了约100MH z,FIFO性能提高幅度达到30%以上.与ISE自动生成的FIFO相比,本文中FIFO所占用的FPGA资源有所增加,约增加15%左右.在高性能设计中,在增加少许资源的情况下获得显著的性能提升是值得的.6 结束语文中讨论了高速异步FIFO电路的设计方法,通过精心设计FIFO体系结构、读写电路和状态检测电路,可以实现FIFO工作性能的大幅提升.文中的设计用于FPGA设计,可以有效解决多时钟域之间的高速数据通信问题.参考文献:[1]Rabaey J M,Chandrakasan A,Nikolic B.数字集成电路∀∀∀电路、系统与设计[M].2版.周润德,译.北京:清华大学出版社,2004.[2]刘洪波,龙娟,郝晓莉,等.异步状态判断的研究与设计[J].微电子学与计算机,2007,24(3):81-84.[3]徐海铭,程月东.高速异步FI FO设计[J].电子与封装,2009(6):14-16.[4]Chelcea T,N owick S M.A low-latency FIF O for mix ed-clock systems[C]//Pro ceedings of the IEEE Computer Societ y A nnual W orkshop on VL SI(W VL SI 00).Orlan do,2000:119.[5]于海,樊晓桠.基于F PGA异步F IFO的研究与实现[J].微电子学与计算机,2007,24(3):210-213.作者简介:李 冬 女,(1989-).研究方向为电子电路.赵志凯 男,(1983-),博士研究生.研究方向为机器学习、模式识别.148微电子学与计算机2010年。

quartus 异步fifo用法 -回复

quartus 异步fifo用法-回复quartus异步FIFO用法引言:在数字电路设计中,FIFO(First In First Out)是一种常见的数据存储器,它允许数据以先进先出的顺序进出。

在使用Quartus进行FPGA设计时,异步FIFO是一种非常有用的工具,它可以帮助我们处理不同速度的数据流,并实现数据的缓冲和流量控制。

本文将介绍Quartus异步FIFO的基本概念和使用方法,并给出一些实例。

第一部分:Quartus异步FIFO概述1.1 什么是异步FIFO?异步FIFO是一种数据存储器,在其中数据可以以不同速度进入和退出。

与同步FIFO不同,异步FIFO的读写时钟可以是不同的,这使得它可以处理速度不匹配的数据流。

Quartus提供了异步FIFO的库函数和IP核,使得它可以在FPGA设计中方便地使用。

1.2 Quartus异步FIFO的特点Quartus异步FIFO具有以下特点:- 可以使用不同的时钟频率进行读写操作。

- 可以配置不同的缓冲深度来满足特定的设计需求。

- 可以实现流量控制和数据的重排序。

- 可以支持并行读写和读写使能信号。

- 可以适应不同的数据宽度和时钟域要求。

第二部分:Quartus异步FIFO的使用方法2.1 创建异步FIFO在Quartus中创建异步FIFO的方式有两种:使用库函数和使用IP核。

使用库函数创建异步FIFO的步骤如下:- 首先,在Quartus中打开设计工程,并创建一个新的源文件。

- 然后,将异步FIFO的库函数导入到源文件中,以便在设计中调用它。

- 接着,实例化异步FIFO,并通过参数配置其属性,例如宽度,深度,时钟域等。

- 最后,将异步FIFO连接到其他逻辑模块,完成设计。

使用IP核创建异步FIFO的步骤如下:- 首先,在Quartus中打开设计工程,并创建一个新的IP核。

- 然后,在IP核的界面中选择合适的FIFO类型和配置参数。

- 接着,将异步FIFO实例化到设计中,将其连接到其他逻辑模块。

fpga中异步信号处理

fpga中异步信号处理

在FPGA中进行异步信号处理是一项重要的任务,因为许多

输入信号可能以不同的时钟信号、频率或相位到达FPGA。

处

理这些异步信号需要特殊的技术和电路设计。

以下是一些常用的异步信号处理方法:

1. 异步复位器:在FPGA中,可以使用异步复位器来处理异

步复位信号。

异步复位器可确保在输入复位信号到达时立即将FPGA重置为初始状态,而不需要等待时钟信号。

2. 异步触发器:通过使用异步触发器,可以将异步输入信号转换为同步的信号。

异步触发器具有单独的时钟信号和数据输入,当触发信号到达时,会将数据输入传递到输出。

这样,异步信号就可以与FPGA中的同步逻辑一起使用。

3. FIFO缓冲器:FIFO(First-In-First-Out)缓冲器用于将异步

信号转换为同步信号,并进行缓冲。

当异步输入信号到达时,它会存储在FIFO中,然后由同步时钟信号按顺序输出。

这样

可以确保异步信号按照正确的顺序被处理。

4. 时序分析和约束:在设计FPGA中的异步信号处理电路时,需要进行时序分析和约束。

时序分析可以帮助确定异步信号到达的时机、时钟边沿等。

时序约束可以确保异步信号处理电路能够按照预期的时序工作。

需要注意的是,异步信号处理在FPGA设计中需要特别小心,

因为异步信号可能导致不稳定的或不确定的行为。

因此,正确设计和验证异步信号处理电路是至关重要的。

异步FIFO的VHDL设计

异步FIFO的VHDL设计下面是一个异步FIFO的VHDL设计示例:```vhdllibrary ieee;use ieee.std_logic_1164.all;entity AsyncFIFO isgenericDATA_WIDTH : natural := 8; -- 数据宽度FIFO_DEPTH : natural := 16 -- FIFO深度portclk : in std_logic; -- 时钟信号rst : in std_logic; -- 复位信号read_en : in std_logic; -- 读使能write_en : in std_logic; -- 写使能read_data : out std_logic_vector(DATA_WIDTH-1 downto 0); -- 读数据write_data : in std_logic_vector(DATA_WIDTH-1 downto 0); -- 写数据full : out std_logic; -- FIFO满标志empty : out std_logic -- FIFO空标志end AsyncFIFO;architecture Behavioral of AsyncFIFO istype buffer_array is array (FIFO_DEPTH-1 downto 0) ofstd_logic_vector(DATA_WIDTH-1 downto 0);signal buffer : buffer_array; -- 数据缓冲区signal wr_ptr : natural range 0 to FIFO_DEPTH-1; -- 写指针signal rd_ptr : natural range 0 to FIFO_DEPTH-1; -- 读指针signal count : natural range 0 to FIFO_DEPTH-1; -- 缓冲区中数据个数beginprocess (clk)beginif rising_edge(clk) thenif rst = '1' thenwr_ptr <= 0;rd_ptr <= 0;count <= 0;elseif write_en = '1' and full = '0' then -- 写使能且FIFO非满buffer(wr_ptr) <= write_data;wr_ptr <= wr_ptr + 1;count <= count + 1;end if;if read_en = '1' and empty = '0' then -- 读使能且FIFO非空read_data <= buffer(rd_ptr);rd_ptr <= rd_ptr + 1;count <= count - 1;end if;end if;end if;end process;full <= '1' when count = FIFO_DEPTH-1 else '0';empty <= '1' when count = 0 else '0';end Behavioral;```在上面的代码中,`DATA_WIDTH`和`FIFO_DEPTH`是异步FIFO的泛型参数,可以根据实际需求进行配置。

高速异步FIFO的设计与实现

高速异步FIFO的设计与实现2 异步FIFO的实现读时钟2.1 FIFO设计的难点如何同步异步信号,使触发器不产生亚稳态是设计异步FIFO的难点。

国内外解决此问题的较成熟方法是对写地址膜地址采纳格雷码,本文也挺直采纳格雷码。

异步FIFO设计的另一个难点是如何推断FIFO的空/满状态。

为了保证数据正确的写入或读出。

必需保证异步FIFO在满的状态下.不能举行写操作:在空的状态下不能举行读操作。

通常状况下将存储器组织成一个环形链表。

满/空标记产生的原则是:写满不溢出.读空不多读。

即无论在什么状况.都不应浮现读写地址同时对一个存储器地址操作的状况。

在读写地址相等或相差一个或多个地址的时候,满标记应当有效。

表示此时FIFO 已满,外部电路应停止对FIFO发数据。

在满信号有效时写数据应按照设计的要求,或保持、或抛弃重发。

同理,空标记的产生也是如此。

为了更好的推断满/空标记。

采纳在FIFO本来深度的基础上增强一位的办法,而由该位组成的格雷码并不代表新的地址。

也就是说3位格雷码可表示8位的深度,若再加一位最高位MSB,则这一位加其他三位组成的格雷码并不代表新的地址,也就是说格雷码的0100表示7,而1100仍然表示7,只不过格雷码在经过一个以0位MSB的循环后进入一个以1为MSB的循环,然后又进入一个以0位MSB的循环。

其他的三位码仍然是格雷码。

举例解释:一个深度为8字节的FIFO怎样工作(用法已转换为二进制的指针),N=3,指针宽度为N+I=4。

开头rd_ptr_bin和wr_ptr_bin均为“0000”。

此时FIFO中写入8个字节的数据。

wr_ptr_bin=“1000",rd_ptr_bin=“0000”。

固然,这就是满条件。

现在,假设执行了8次的读操作.使得rd_ptr_bin=“1000”,这就是空条件。

另外的8次写操作将使wr_ptr_bin等于“0000”,但rd_ptr_bin仍然等于“1000”,因此,FIFO为满条件。

基于FPGA的异步FIFO设计与实现

基于FPGA的异步FIFO设计与实现王伟国;张振东【摘要】随着现代数字电路系统密度和规模的不断扩大,一个系统中通常会包含多个时钟,因此不同时钟之间的数据传输成为亟待解决的问题.而一种可靠易行的解决方案就是异步FIFO.异步FIFO需要非常严格的多时钟技术,难以作出正确的设计合成和分析.本文提出了一种利用格雷码作为读写地址计数器的异步FIFO的设计方法,有效的避免了数据在不同时钟时间传输时遇到的亚稳态问题.并给出了综合仿真结果.%With the expanding of the density and scale of modern digital circuitry,a system will contain multiple clock.Therefore,the transfer of data between different clock becomes a serious problem needs to be solved.A reliable and feasible solution is asynchronous FIFO.Asynchronous FIFO require very strict clock technology,it is difficult to make the correct design of synthesis and analysis.This paper presents a design method of asynchronous FIFO which based on read/write counter in terms of gray code.This method effectively avoid the metastable state in the data transmission between different clock and given a comprehensive simulation results.【期刊名称】《聊城大学学报(自然科学版)》【年(卷),期】2012(025)003【总页数】6页(P79-84)【关键词】多时钟;异步fifo;verilog;HDL;格雷码【作者】王伟国;张振东【作者单位】中国科学院长春光学精密机械与物理研究所,吉林长春130033;中国科学院长春光学精密机械与物理研究所,吉林长春130033/中国科学院研究生院,北京100039【正文语种】中文【中图分类】TN4330 引言随着现代数字电路系统的实时数据处理能力的不断提高,逻辑电路的复杂程度和内核处理器的运算速度也快速增长,在使得一些复杂算法得以实现的同时也加剧了快速CPU与慢速外设之间的冲突.异步FIFO大量数据缓存的能力成功的解决了这一问题,但专用的高速异步FIFO芯片价格昂贵,且容量受限,随着现场可编程逻辑器件容量和速度的不断提高,利用现场可编程逻辑器件设计异步FIFO成为可行的方法.本文首先讨论了异步FIFO设计中经常出现的亚稳态问题和二进制计数器多位同时改变的问题,并给出解决办法,然后讨论了两种格雷码计数器的形式并作出比较,最后给出一种以格雷码为读写地址计数器的异步FIFO的设计方法和在设计异步FIFO时必须要注意的细节.1 多时钟电路中的亚稳态问题在一个时序电路中,合理的建立时间和保持时间是触发器正常工作的前提条件.对于下降沿触发的触发器而言,下降沿触发之前输入数据持续的最短时间是建立时间(setup time),下降沿触发之后输入数据持续的最短时间是保持时间(hold time).当电路时序不能满足setup time/hold time的要求时,系统时序就会出现混乱.在异步时序电路中,不同时钟之间是不存在任何关系的,必然会产生建立时间和保持时间冲突.解决系统时序问题常用双锁存器法如下图1所示,即在不同时钟之间传输数据时连续锁存两次.但是这种方法只是保证了电平的稳定,而在实际的系统中还需要FIFO作为不同时钟之间传输多位数据的接口.图1 避免亚稳态出现的双锁存器法2 异步FIFO指针对于同步FIFO来说,使用一个计数器计算读出和写入到FIFO缓存器中的数据量,计数器在只有写没读是递增,只读没写是递减,既读又写和没读也没写时保持不变.当计数器到达设定值时FIFO满信号置位,为零时空信号置位.在异步FIFO中,由于这种计算数据个数增减的计数器会被两个不同的时钟控制,因此这种计数器不能使用.所以,为了决定FIFO“空”和“满”状态,读指针和写指针必须相互比较.设计FIFO最主要的困难是生成FIFO指针和找到一个决定FIFO“空”和“满”状态的可靠方法.在FIFO设计中,读指针和写指针总是指向下一个要读和写的地址空间.当读或写操作完成后指针自动递增,当FIFO是空时读指针和写指针相等,当FIFO满时读指针和写指针也是相等.一种解决的方法是增加一个多余的MSB位来区分两种状态,当写指针递增超过地址范围时,写指针会递增MSB位,其他位清零,读指针同样也是.当读指针和写指针的MSB位不同时,意味着写指针比读指针多走了一圈,当MSB位相同时意味着走的圈数相等(如图2所示)图2 增加多余MSB后区分FIFO空和FIFO满的方法示意图当FIFO存储缓冲区需要(n-1)位地址时,地址指针用n位,当指针相等(包括MSB位)时空标志置位,当指针低(n-1)位相等且MSB位不等时满标志置位.2.1 二进制FIFO指针的情况二进制地址计数量会有多个位同时变化,因此在把二进制量在不同时钟域之间同步时会出现问题.一个解决的方法是取样并把周期计数量寄存在一个保持寄存器中,并发出一个ready信号,新时钟域收到信号并发出确认信号,这样变化的计数量就安全的传送到新时钟域.用这种方法不会产生上溢和下溢,因为当读指针递增到与写指针相等时,空信号置位,取样的写指针不反映当前写指针的值,而是小于当前值,故永远不能产生下溢,满信号也是如此.最常用的解决方法是用格雷码计数器,格雷码在每个时钟只有一位变换可以极大的减少在同步计数时错误的发生.3 格雷码计数器设计格雷码计数器的方法有很多,这里介绍二种简单直接的方法.下面详细介绍两种方法.3.1 格雷码计数器中的问题为了更好的理解把n-bit计数器转换成(n-1)-bit计数器时出现的问题,先考虑一下一个双重4-bit和3-bit格雷码计数器的例子如图3.图3 4-bit格雷码计数器示例及转换成3-bit格雷码时出现的问题在4-bit计数器中除了MSB位其余位关于中间对称,我们把2nd MSB位反相后,上半部分与下半部分的LSBs便相等.但是经过反相操作后整体便不是格雷码了,例如15(1100)到0(0000)的转变过程有两个bits变化,在下面的第一种格雷码计数器中会有解决方法.3.2 第一种格雷码计数器图4是第一种计数器的框图并是双重格雷码计数器中两个bits同时跳变的解决方法.其中假设输出寄存器的值是格雷码(ptr),此格雷码被输出到格雷码到二进制的转换器中,然后通过一个有条件递增的加法器并输出下一个格雷码值(gnext),连接到输出寄存器的输入端,如框图上半部分所示.(n-1)-bit格雷码简单地通过n-bit格雷码的2个MSBs的异或操作产生,(n-2)个LSBs不变.图4 第一种格雷码计数器示意图及其如何避免了两位同时跳变问题3.3 第二种格雷码计数器此种风格的格雷计数器(如图5所示)用了两组寄存器避免了把格雷码转换成二进制数的步骤.而且第二组寄存器也可以直接用来寻址FIFO存储器.n-bit格雷码指针仍然需要同步到不同的时钟域中.二进制指针可以更容易的通过计算产生“几乎满”和“几乎空”信号.因此在本论文的设计中用此种风格的格雷码计数器.图5 第二种格雷码计数器工作示意图4 总体设计及“空”和“满”信号的产生总体设计如图6所示,本设计方案共有四个模块,双口RAM模块,读控制模块,写控制模块,格雷码同步模块.写控制模块主要是当写使能信号有效且写满信号无效时产生写地址并实行地址递增功能,读控制模块实现相似功能,双口RAM模块用来使缓冲数据其读写动作可同时进行.4.1 “空”和“满”信号的产生“空”信号的产生比较简单,只需同步到读时钟域的写地址格雷码与n-bit的读指针的格雷码完全相等即可代码如下图6 异步FIFO总体设计框图及其信号说明但是,“满”信号的产生就没那么容易,简单地用n-bit格雷码作比较判断“满”信号是不可靠的.因为格雷码除了MSB位外是对称的如图3所示.在图3中假如写指针和读指针都指向地址7,此时写指针递增一次后,写指针指向地址8,读指针和写指针相比较,除了MSB位不同外其余各位均相等,满信号此时有效,但这是不符合实际情况的,错误的.这也是为什么在图4中应用双重n-bit格雷码计数器的一个原因.正确判断满信号的条件是:读写指针的n-bit格雷码的前两个MSBs都不相等,其余的写指针和同步读针相等.代码如下4.2 不同时钟速度因为异步FIFO被两个不同的时钟控制,很明显两个时钟运行在不同的速度下.当把较快的时钟同步到较慢的时钟时,会有一些计数值被跳过.当被同步的格雷码递增两次只被取样一次时也不会出现亚稳态问题,因为亚稳态出现在同步时钟上升沿附近有多位同时跳变时,而在两个同步时钟沿之间有格雷码跳变两次,第一次跳变距离同步时钟条边沿较远,只有第二次跳变在同步时钟沿附近,故不会产生亚稳态.当较快的格雷码计数器在较慢时钟沿之间递增多于一次,不会出现已经溢出却没有检测到的现象,因为同步到写时钟域的读指针滞后于当前的读指针,而写指针只会小于或等于同步读指针,故不会出现溢出.5 设计仿真及总结本设计采用Xilinx公司Spartan3A系列的XC3S1400A,封装时PG484,速度是-4,仿真器是ISE Simulator(VHDL/Verilog),硬件描述语言是Verilog,开发工具是ISE.最后对电路进行时序分析,结果为该FIFO运行速度可达到90.63MHz.wclk、rclk时钟周期分别为:75MHz、80MHz.先向FIFO中写入18个数据,当第16个数据被读入后wfull立即被置位如下图7.图7 写满仿真结果同时向FIFO中写入和读出数据,由于wptr要经过两个读周期才能同步到读时钟域,故在waddr递增后的第二个rclk的上升沿rempty才清零如下图8所示.本文对异步FIFO的结构和重要时序问题给予了详细的阐述,并得到了可靠的仿真结果.在高速数据采集系统中,采用高性能FPGA作为数据预处理和高速异步FIFO 作为数据采集缓存的应用都十分广泛.把FIFO集成在FPGA中简化了电路设计的复杂程度,增加了电路的集成化程度和可靠性,是未来高速数据采集系统的重要发展方向.图8 同时写入读出时的仿真结果参考文献【相关文献】[1] Clifford E.Cummings,Synthesis and Scrip ting Techniques for De signing Multi-Asynchronous Clock Designs[A].SNUG-2001,2001(3):2-8.[2]吴自信,张嗣忠.异步FIFO结构及FPGA设计[J].单片机及嵌入式系统应用,2000,22(3):1.[3]赵雅兴.FPGA原理、设计与应用[M].天津:天津大学出版社,1999.[4]夏宇闻.数字系统设计-Verilog实现[M].北京:高等教育出版社,2006.[5]王金明.Verilog HDL程序设计教程[M].北京:人民邮电出版社,2004.。

最新-一种异步FIFO的设计方法 精品

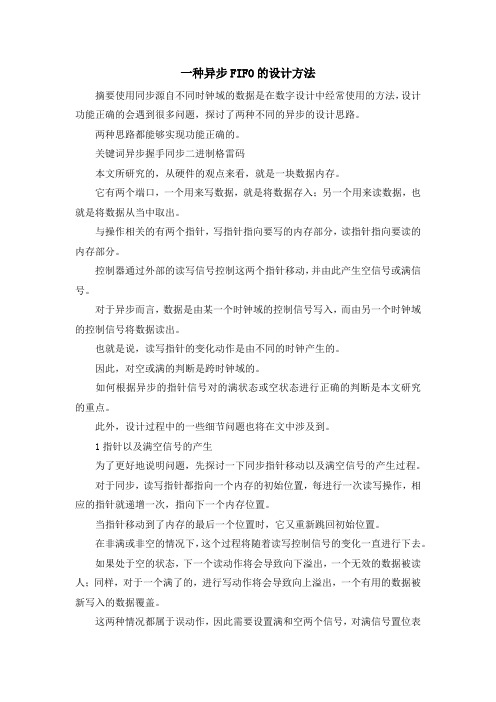

一种异步FIFO的设计方法摘要使用同步源自不同时钟域的数据是在数字设计中经常使用的方法,设计功能正确的会遇到很多问题,探讨了两种不同的异步的设计思路。

两种思路都能够实现功能正确的。

关键词异步握手同步二进制格雷码本文所研究的,从硬件的观点来看,就是一块数据内存。

它有两个端口,一个用来写数据,就是将数据存入;另一个用来读数据,也就是将数据从当中取出。

与操作相关的有两个指针,写指针指向要写的内存部分,读指针指向要读的内存部分。

控制器通过外部的读写信号控制这两个指针移动,并由此产生空信号或满信号。

对于异步而言,数据是由某一个时钟域的控制信号写入,而由另一个时钟域的控制信号将数据读出。

也就是说,读写指针的变化动作是由不同的时钟产生的。

因此,对空或满的判断是跨时钟域的。

如何根据异步的指针信号对的满状态或空状态进行正确的判断是本文研究的重点。

此外,设计过程中的一些细节问题也将在文中涉及到。

1指针以及满空信号的产生为了更好地说明问题,先探讨一下同步指针移动以及满空信号的产生过程。

对于同步,读写指针都指向一个内存的初始位置,每进行一次读写操作,相应的指针就递增一次,指向下一个内存位置。

当指针移动到了内存的最后一个位置时,它又重新跳回初始位置。

在非满或非空的情况下,这个过程将随着读写控制信号的变化一直进行下去。

如果处于空的状态,下一个读动作将会导致向下溢出,一个无效的数据被读人;同样,对于一个满了的,进行写动作将会导致向上溢出,一个有用的数据被新写入的数据覆盖。

这两种情况都属于误动作,因此需要设置满和空两个信号,对满信号置位表示处于满状态,对满信号复位表示非满,还有空间可以写入数据;对空信号置位表示处于空状态,对空信号复位表示非空,还有有效的数据可以读出。

当读指针和写指针相等也就是指向同一个内存位置的时候,可能处于满或空两种状态。

可以通过不同的方法判断或区分究竟是处于满状态还是空状态,也就是究竟是写指针从后赶上了读指针,还是读指针从后赶上了写指针。

高速异步FIFO的设计和实现

万方数据路中,这一信号最终会朝着0和1两个稳态转换,变成稳定的信号。

这一变换所需的时间取决于寄存器的结构和参数,通常在一个时钟周期内可以完成这一从亚稳态到稳态的转换。

所以,在设计中普遍采用两级寄存器串接的同步器来对信号进行同步,如图1所示。

图1解决亚稳态的同步器电路2.2毛刺单根信号的同步采用图1所示的同步电路即可消除亚稳态问题。

然而,对多位总线信号的同步,除了亚稳态外,还有一个重要的问题就是毛刺现象。

如果需要同步的总线的多位同时发生变化,由于在实际电路中各位的延时不可能完全一致,因此中间就可能会产生毛刺现象。

而用另一个频率相位完全不同的时钟采样的时候就有可能采样到毛刺信号,造成错误的同步。

例如,FIFO的读写指针是一个二进制计数器,当它从l计数到2时,位0从1变成0,位l从0变成1。

如果位0从1变成0的延时比位1从0变1要大,就会在1和2中间多出一个毛刺3,而如果直接用图l的同步电路同步,就有可能错误地在另一个时钟域得到一个3的结果。

对于FIFO的设计来说,这样的同步错误是致命的,会造成空满判断的失误。

解决这一问题就是需要采用无毛刺的电路结构,无毛刺电路要求信号同步前必须被寄存器锁存,并且每次只有一位发生变化。

例如,文献[2]中设计的FIFO就采用格雷码来避免这一问题。

3高速异步FIFO结构3.1基本结构本文设计的高速异步FIFO结构如图2所示,主要包括数据通路reg—file和控制模块fifo—eft两个部分。

reg—file模块是FIFO的存储器部分;fifo_eft模块负责FIFO的读写控制,如读写指针的产生和空满信号的产生。

图2高速异步FWO结构框图本设计的外部端口如表l所示。

3.2reg__file模块设计FIFO的存储器部分可以采用双端口SRAM或者用DFF寄存器搭建存储部分。

由于本设计为32×32的FIFC,存储器容量不大,采用双端口SRAM由于powerring等因素,面积会比用寄存器搭建要大,速度也不容易达86到500MHz的高速。

基于VHDL的异步FIFO设计

基于VHDL的异步FIFO设计2011年7月15日第34卷第14期现代电子技术ModernElectronicsTechniqueJuI.2011V o1.34No.14基于VHDL的异步FIFO设计李辉,王晖(中国空空导弹研究院,河南洛阳471009)摘要:FIFO经常应用于从一个时钟域传输数据到另一个异步时钟域.为解决异步FIFO设计过程中空满标志判断难以及FPGA亚稳态的问题,提出一种新颖的设计方案,即利用格雷码计数器(每次时钟到来仅有1位发生改变)表示读/写指针,设计二级同步链为跨越不同时钟域的读/写指针,以提供充足的稳定时间,并通过对比格雷码指针产生空满标志位.该设计采用VHDL语言进行设计,利用ALTERA公司的FPGA得以实现.经验证进一步表明,模块化的设计不仅避免了亚稳态的产生,增大平均无故障工作时间(MBTF),也使工作效率大为提升.关键词:FIrO;异步;亚稳态;格雷码中图分类号:TN402—34文献标识码:A文章编号:1004—373X(2011)14—0154—03 AsynchronousFIFODesignBasedonVHDLIIHui,WANGHui(ChinaAirborneMissileAcademy,Luoyang471009,China)Abstract:FIFOisoftenusedtOsafelypassdatafromoneclockdomaintoanotherasynchronou sclockdomain.InordertO solvetheconundrumsofcorrectlyjudging"full"or"empty"intheFIF0designandmetastabilityofFPGA,anewdesignusinggraycounterpointers(onlyonebitchangedwhenclockedgearrived)tOdenotereadand writepointersisproduced,dualstagesynchr0nizationisusedtOprovideadequatestabilizationtimeforthereadandwritepoin tersacrosstWOdifferentclock domains."full"or"empty"flagsareproducedbycomparingthetWOpointers.Thedesignisac hievedusingVHDLinAITERAFPGA.Themoduledesignusestheerrorsofmetastabilitygracefullythroughverifi cation.TheMTBFhasbeenin—creasedgreatlyandtheworkefficiencyhasbeenimprovedextraordinarny.Keywords:FIF0;asynchronous;metastabi1ity;Graycode先进先出缓存电路读/写(FIFO)在大规模逻辑设计中被广泛应用,几乎每个芯片都要涉及,同样在空空导弹的数据传输体系中也得以大量应用.FIFO类型可以分为两种,第一种为同步FIFO,即读/写时钟是同步的,这里的同步不仅仅是指读/写时钟为同一个时钟,即属于同一个时终域.当读/写时钟频率为倍数关系,即相位关系确定时,也归属同步FIFO的范畴.另一种为异步FIFO,读/写时钟频率不成倍数关系或相位关系不确定,即跨时钟域.异步FIFO可以在不同的时钟域之间快速方便地传输实时数据,因此在遥测数据传输中,异步FIFO实用性更好.然而如何正确地产生空满标志以及如果解决亚稳态问题是异步FIFO设计的难点_1].1FIFO结构首先,典型的FIFO结构框图如图1所示.FIFO的数据存储在具有独立写端I=1和读端口的RAM中.读指针rd—pointer指向下一个将要读取的位置,写指针wrpointer指向下一个将要写入的位置,每1次写操作收稿日期:201卜02—14后写指针加1,读操作使读指针加1.状态产生模块中, full和empty表示FIFO读/写的临界状态.FIFO设计的关键是产生读/写地址和空满标志.空满标志是基于引起指针相等的操作.如果是复位或者读操作引起读/写指针相等,FIFO认为是空;如果原因是写操作,那么FIFO认为是满.异步FIFO设计的难点是如何同步跨时钟域的指针以及空满标志的产生.r_datJrd出fa双端[_=】RAM"addrrdaddr一]l写指针lvalid_rd读指针valid1vrwrA)trrd~tr状态产生——一fde"●ful】图1F1FO原理框图第14期李辉等:基于VHDL的异步FIFO设计1552亚稳态亚稳态是当信号在无关的电路中或异步时钟域之间传输时导致FPGA系统失效的一种现象.包括FPGA在内的所有数字器件的寄存器都定义了信号时序要求,以保证每一个寄存器都能够从输入端获取数据和在输出端产生数据.为了确保可靠的操作,输入信号必须在时钟沿之前稳定一段时间(寄存器建立时间t.),并且在时钟沿之后稳定一段时间(寄存器保持时间t),然后寄存器输出经过一个特定的时钟到输出延时后有效.满足此要求寄存器才可以正确的在输入端获取数据在输出端产生数据,否则输出有可能是亚稳态].在亚稳态时,寄存器的输出电压在高低电平之间摇摆,即输出将有可能是逻辑0(0V)或者逻辑1(+5V),或者是介于0~5V中间的某个值.亚稳态产生机制图如图2所示,当建立时间或者保持时间不满足时序要求时便会产生亚稳态.在同步系统中,输入信号必须总是满足寄存器时序要求,所以亚稳态不会发生.亚稳态问题通常发生在当一个信号在无关的线路中或异步时钟域中传输.一个寄存器进入亚稳态和从亚稳态进入稳态的时间依赖于制造商的制造工艺和使用环境.大部分情况下,寄存器会很快的进入一个定义的稳态中.在异步FIFO设计中就要避免亚稳态的产生.ico!!一j…一…一0一一lco!:!!竺竺.L一—一——一——]二三二二二l0窖ic0型旦塑塑型——0———一——一————logicIlogic0一一一——1————…——MetastableoutputB,——k图2亚稳态的产生机制图3解决问题的方法3.1同步寄存器当信号在不相关或者异步时钟域传输时,在新的时钟域使用这个信号之前必须进行同步,比如异步FIFO的读指针被同步到写时钟域或写指针被同步到读时钟域[6].新时钟域里的第一个寄存器的作用就是一个同步寄存器.同步装置中寄存器到寄存器路径上的时序裕量可以为亚稳态信号提供稳定时间.由两个寄存器组成的二级同步链如图3所示,它大大的提高了系统的平均无故障工作时间(MTBF),减少了信号传输过程中亚稳态问题的风险.此外,可以通过三级同步进一步增加MTBF值,但在实际中很少需要.3.2格雷码(Graycode)计数器设计异步FIFO的原则是安全可靠地把数据从一个时钟域传输到另一个时钟域.如果用一个相对于计数器时钟是异步的时钟来取样计数器的值,就要考虑计数器的每一位在哪个范围内变化,每一位都有机会同时发生变化,比如从FFFF变化到0000,这时每个单独的位都处于亚稳态.这种变化意味着读数有可能是0000~FFFF之间的任意一个值.这种情况下FIFO将无法正常工作,于是设计一个格雷码来表示的计数器,因为格雷码是最小距离码,相邻的码元只有1位不同,它可以避免因延迟不一致而引起的毛刺现象. SYNCHRONIZATIONCHAINClockldomainf一一一一一一一一一一一一一一一一一一一] I………………一图3二级同步链二进制码转格雷码:g=b,G:b④b件l,Vi≠格雷码转二进制码:b一g,b一g①b斗1,Vi≠计数器由触发器组和累加器组成,处理格雷码计数器的办法为:将格雷码转换为二进制码元,然后加1,再将它转换回格雷码并存储,这是解决产生N位格雷码算法棘手问题的一个办法].异步FIFO的写地址和读地址由格雷码计数器来实现计数,读/写指针均用格雷码来表示,格雷码计数器指针原理如图4所示,当FIFO非空或者非满时,读指针或者写指针实现加1操作.图4格雷码计数器指针原理3.3一种新颖的设计方法产生空满标志空满标志位是通过比较读/写指针来判断的,空满标志的判断方法:对于二进制地址来说,如果RAM大小为M,那么它需要的地址位宽度为N—logM.假设156现代电子技术2011年第34卷双口RAM大小是8B,所需寻址地址位宽度是3b.如果读/写指针均用3位来表示的话,那么当读/写指针相等时,无法判别是读时针追上了写时针造成读空还是写时针追上了读时针造成写满,这样就无法正确判断空, 满标志.为了方便的区分空,满,读/写指针各增加1位,取地址指针宽度为logM+1,寻址中没有使用的最高位地址标记为MSB,即读/写指针为N+1位,寻址范围为2".表1为格雷码表示的4位地址指针.衰1四位二进制与格雷码对比表二进制格雷码指针寻址次数X+1个循环寻址仔细观察表1并分析数据,一种新颖的判断空满标志的方法为:当读/写指针的最高位(MSB)不相等且读/写指针的次高位不相等,剩余的N一2位地址相等时,此时写指针追上了读指针,即写指针比读指针多转一圈,状态模块输出满标志;当读/写指针N+1位都相等时,状态模块输出空标志.判断满标志部分的VHDL代码:process(reset,clk)beginif(reset=O)thenwfull~一0:elsif(clkeventandclk一1)thenif(wgnext(addrsize){一wq2一rptr(addrsize)andwgnext(ad—drsize-1)/一wq2一rptr(addrsize-1)andwgnext(addrsize一2downto o)/一wq2~rptr(addrsize-2downto0))thenwfull<一1:elsewfull<一0:endif;endif;endprocess;判断空标志产生部分的VHDL代码:process(reset,clk)beginif(reset一0)thenrempty<一0:elsif(clkeventandclk=1)thenif(rgraynext=rq2一wptr)thenrempty<一1:elsewfull<一0;endif:endif;endprocess;3.4异步FIFO总体设计通过时针比较产生的异步FIFO框图如图5所示. WCLK和RCLK分别为读时钟和写时钟,wrst—n和rrst—n分别为读/写模块的复位信号.rdata为数据输出端口,wdata为数据输人端口.异步FIFO通过读/写指针来寻址一个双口RAM来实现对数据的读/写, 双口RAM的大小为2"B.读指针被二级同步链到写时钟域,然后与写时针比较产生满标志,读指针产生读地址raddress;写时针被二级同步链同步到读时钟域, 然后与读时钟比较产生空标志,写指针产生写地址waddress.需要注意的是此异步FIFO设计中,空满标志是保守的空满标志,比如满标志,当读时针通过二级同步链同步到写时钟域且满足满标志的条件时,写指针停止加1操作,而同步读指针的过程中,读时针则移动到了其他的地址,同样的适合于空标志,当输出空,满时,其实FIFO的真实状态是还有空间没被写满或者读空,这就是保守的空和满,而这正保证了FIFO不会向上会向下溢出,进一步提高了FIFO工作的可靠性.图5同步时针比较构成异步FIFO框图表2为平均无故障工作时间的对比,c,和C.依赖于器件工艺.表2平均无故障工作时间不采用格雷采用格雷码计数器码指针8L二级同步装置妻无R故100h100年F工作时间(MBT)0占用逻辑单元/个1400860计算公式MTBF一Ⅲ_I_寒软件环境VHDIINALTERAFPGA4结语一个高的平均无故障工作时间表明一个设计是优秀的,提高亚稳态的平均无故障工作时问减少信号传输(下转第16O页)址争环循个^^-}1)¨""¨l.∞∞∞∞吡∞叽如n∞∞n∞∞∞∞阻叽∞叫¨u∞Uu¨n如16O现代电子技术2O11年第34卷相邻系统的发射线上加了不同频率的方波信号,避免了相邻系统间的干扰.本设计中,选用了3kHz,5kHz,7kHz的方波信号,相邻系统的发射端得到不同的发射信号.接收端收到信号以后采用了以发射端信号频率为中心频率,带宽为1kHz的带通滤波,滤波后去掉干扰信号得到有用信号.3.3.3单系统防护距离随着感应线圈长度的变化,线圈和地之间的分布电容也会产生相应的变化,感应线圈越长,分布电容越大. 在感应线很长时,人接近感应线后,分布电容的变化较小,会导致系统灵敏度下降,所以单系统的防护距离不宜太长,限定150m内为宜.4结语经过软件仿真和现场测试,得到了正确的数据.在进行了详细的数据分析以后,证明整个系统的设计思路和计算方法是正确的.基于虚拟仪器及DSP的静电感应式电子围栏系统的前端围栏带有高压脉冲电给入侵者极大威慑,有形围栏给入侵者带来了很多阻碍,若强行入侵,则系统自动发出声,光报警,并可以与其他安防系统联动(如防盗报警主机,视频监控系统,l10报警等).该电子围栏能适应各种环境,且误报率极低,克服了传统的红外,微波等技术的缺陷,报警基本不受气候,地形,树木,小动物等影响.参考文献[1]郭为民.视频监控系统软件现状与技术分析[J].科技致富向导,2010(7):5-7.[2]张俊才,刘树聃.基于计算机控制的红外监控系统的设计与实现[J].微计算机信息,2010(12):35—37.[3]Anon.AudioprocessingsystembasedOnDSPandTIV320CAIC23BrJ].Automation&.Instrumentation, 2009,24(8):57—60.[4]蔡宁果,雷杭州,张毓.用LABWINDOWS/CVI实现分布式数据采集系统[J].继电器,2001,29(4):36—38.[5]桑国明,刘智.数字滤波器的DSP实现[J].大连大学, 2001,22(44):69—72.[6]孙祥娥,李永全.基于Matlab的Chebyshev数字滤波器设计[J].现代电子技术,2004,27(20):109—110.[7]孙洪,余翔宇.数字信号处理[M].北京:电子工业出版社,2005.[8]吴杰康,龙军,王辑祥.基于数字微分算法的系统频率快速准确测量[J].电工技术,2004,19(4):93—97.[9]鞠苏民,陈文华.FIR滤波器的MA TIAB设计与DSP算法实现[J].通信与广播电视,2005(4):l5—2O.Elo]王创业.电子围栏在变电站周界防护中的应用[J].安徽科技,2010(6):48—49.[11]赵亮,张应亮,杨国清,等.基于DSP的电机磁控式智能软起动研究I-J].电网与清洁能源,2009(1):72—75.作者简介:李向东男,1983年出生,硕士研究生.主要研究方向为光电检测和图像处理.(上接第156页)中导致亚稳态问题的风险[1.本文通过研究FIFO的基本结构以及FPGA亚稳态的产生机理,提出了利用二级同步链和格雷码计数器指针解决了同步以及空满状态判断的难题,给出了VHDL软件代码,且该设计已经通过QuartusII的时序仿真验证,作为独立模块可以应用到需要异步时钟域传输数据的电路中,大大提高异步数据传输效率及平均无故障工作时间.参考文献[1]赵永建,段国东,李苗.集成电路中的多时钟域同步设计技术[J].计算机工程,2008,34(9):246—248.[2]许盛,易浩勇.异步FIFO在USB2.0控制器中的应用[J].电子测量技术,2009,32(8):137—140.1-3]许新新,赵雷.可编程逻辑器件亚稳态的分析与测试[J].电子质量,2006(2):3-6.[4]房海东,潘长勇,杨知行.处理整帧数据的FIF()的巧妙控制设计[J].电讯技术,2003,43(4):63—67.I-5]CUMMINGSCliffordE.Synthesisandscriptingtechniques fordesigningmulti—asynchronousclockdesigns[c].SanJo—se,CA:SynopsysUsersGroupConference,2001.[6]雷伏容.VHDL电路设计[M].北京:清华大学出版社,2007.[7]王念旭.DSP基础与应用系统设计[M].北京:电子工业出版社,2003.[8]田志明,杨军,罗岚.异步复位设计中的亚稳态问题及其解决方案[J].电子器件,2002,25(4):435—439.r9]CUMMINGSCliffordE,MIIISDon.SynchronousRe—sets?AsynchronousResets?IamSoConfused!HOWWⅢI EverKnowWhichtOUseEc].SanJose,CA:Synopsys UsersGroupConference,2002.[1o]罗吴.一种异步FIFO的设计方法[J].电子技术应用,2004(8):70—74.作者简介:李辉男,1983年出生,硕士研究生.研究方向为数据通信领域.。

异步复位时序约束-概述说明以及解释

异步复位时序约束-概述说明以及解释1.引言概述部分的内容可以如下编写:1.1 概述异步复位是数字电路设计中的一种重要功能,它用于将电路恢复到初始状态,以确保系统在启动时处于可控状态。

与同步复位相比,异步复位不依赖于时钟信号,可以在任何时刻激活。

本文将讨论异步复位的概念、原理和实践中的时序约束。

在日常的电路设计中,了解异步复位的重要性以及如何正确应用时序约束是至关重要的。

在接下来的章节中,我们将首先介绍异步复位的概念,讨论其作用以及与同步复位的区别。

然后,我们将深入探讨异步复位的原理,包括它是如何实现电路的复位功能的。

最后,我们将探讨异步复位的重要性,并详细讨论在实践中如何设计和应用异步复位时序约束。

通过阅读本文,读者将能够全面了解异步复位的概念和原理,并学会正确地设计和应用异步复位时序约束。

这将帮助读者在数字电路设计中更好地应用异步复位,并提高系统的稳定性和可靠性。

文章结构部分的内容如下:1.2 文章结构本文主要分为三个部分,分别为引言、正文和结论。

引言部分将首先给出异步复位的概述,介绍其基本概念和作用。

随后,将阐明文章的结构和目的,以便读者能够更好地理解和掌握异步复位时序约束的相关知识。

正文部分将详细探讨异步复位的原理,包括其工作原理、触发条件以及相应的电路设计。

通过分析实际案例和例子,将说明异步复位的一些关键问题和挑战,以及如何解决这些问题。

同时,还将介绍一些常见的异步复位电路设计方案和技巧,以提高系统的可靠性和稳定性。

结论部分将总结整篇文章的核心内容,并强调异步复位的重要性。

结合实践经验,将探讨异步复位时序约束的实践方法和技巧,以帮助读者更好地应用异步复位时序约束在实际项目中的设计和实现。

此外,还将展望异步复位技术的未来发展方向,并指出可能的应用领域和研究方向。

通过以上三个部分的内容,本文将全面介绍异步复位时序约束的相关知识和技术,帮助读者理解和运用异步复位时序约束来提升系统性能和可靠性。

4.异步FIFO的设计

利用异步FIFO在跨时钟域中降低亚稳态发生概率在数字电路设计中,时钟是整个电路最重要、最特殊的信号,系统内大部分器件的操作都是在时钟的跳变沿上进行,如果时序不满足要求,就可能造成逻辑状态出错甚至整个系统设计的失败。

随着SOC技术的不断发展,数字系统设计的复杂度也在日益增加,经常需要跨时钟域的数据传输,通信技术等异步设计才能实现特定的功能需求。

本文设计的异步FIFO就是为了解决将数据从一个时钟域同步的读/写到另一个时钟域,并且能很好的避免亚稳态的发生。

1.异步系统任意的两个系统如果满足以下条件之一,如图1-2所示,就可称其为异步的:(1)工作在不同的时钟频率上;(2)工作在相同频率上,但相位不同图1-2 异步系统时钟当两个不同时钟域的系统进行数据传输,由于接口处是异步的,就可能会违反建立时间和保持时间规则导致亚稳态以及不可靠的数据传输,因此处理起来较同步逻辑复杂困难。

在同步系统中,输入信号必须总是满足寄存器时序要求,所以亚稳态不会发生。

亚稳态问题通常发生在当一个信号在无关的线路中或异步时钟域中传输。

在所有的异步系统中,亚稳态是不可避免的。

1.1亚稳态所有的数字器件寄存器都定义了一个信号时序要求,满足了这个要求寄存器才可以正确地在输入端获取(capture)数据在输出端产生数据。

为了确保数据的可靠与正确性,在数据传输过程中必须满足寄存器的建立时间和保持时间,如图1-1,即输入数据在时钟沿之前必须稳定一段时间(寄存器建立时间Tsu)并且在时钟沿之后稳定一段时间(寄存器保持时间Th),然后寄存器输出经过一个特定的时钟到输出延时(clock to output ,Tco)后有效。

图1-1 建立时间与保持时间如果一个数据信号在翻转中违反了一个寄存器的建立和保持时间的要求,寄存器的输出可能就会出现亚稳态。

在亚稳态中,寄存器的输出值在高和低之间徘徊一段时间,这就意味着输出翻转到一个确定的高或低的延时会超过固定的时钟到输出延时。

异步FIFO的设计与实现

摘要随着数字系统规模的不断增大,单时钟域设计会极大地限制数字系统性能,现代数字系统为了提升性能,常采用多时钟域的设计。

跨时钟域的信号在传输时会遇到亚稳态现象,如何保持系统稳定地传输数据是多时钟域系统设计者重点关注的问题,在跨时钟域传递数据的系统中,常采用异步FIFO(First In First Out,先进先出队列)口来缓冲传输的数据,以克服亚稳态产生的错误,保证数据的正确传输。

常规的异步FIFO 设计采用先同步读写指针后比较产生空/满标志和用先比较读写指针产生空/满标志,再同步到相应时钟域的方法,但由于常规异步FIFO 模块中的RAM 存储器读写寻址指针常采用格雷码计数器以与“空满”控制逻辑的存在,工作频率低,面积大,将使通过这两个模块的信号通路延时对整个模块的工作频率造成制约。

本文提出了一种新型异步FIFO 的设计方法,该方法省略“了满”信号产生模块和多余的存储器位深来简化常规的FIFO 模块,而只保留“空”信号产生模块,避免使用大量的同步寄存器,减少了面积空间。

FPGA 验证的结果表明,改进后的异步 FIFO 性能有了显著的提高。

关键词:现场可编程门阵列(FPGA )亚稳态空/满标志产高速FIFOABSTRACTWith the increasing of digital system size, a single clock domain designwill greatly limit the digital system performance. To enhance the performance of modern digital systems, multiple clock domain design is conventionally adopted. While being transmitted, Cross-clock domain signals will come across the phenomenon of metastability, hence it will be a major concern for the multi -clock domain system designers to probe how to maintain the system stability and to have data transmission conducted smoothly. As to the bus system data transmission in the system where the two data interface clocks don’t match, one of super and effective solutions is to use asynchronous FIFO buffer memory. How To solve the key and difficult issue that metastability and how to generate empty and full flag correctly in asynchronous FIFO design. Traditional FIFO design often synchronizes write/read address first, then compares them to generate empty/full signals or empty / full flag first compare the read and write pointer, and then synchronized to the clock domain, This design takes on too much area and can only work at a low frequency,this will allow the signaling pathways of these two modules delay caused by constraints of the operating frequency of the entire module. A new method of asynchronous FIFO is proposed to overcome these problems,omit the "full" signal generator module and redundant memory bit depth to simplify the conventional FIFO module, leaving only the "empty" signal generation module,avoid the use of a large number of synchronization registers, reducing the area of space. FPGA verification results show that the asynchronous FIFO improved performance has been significantly improved.Keywords: Field Programmable Gate Array (FPGA); Metastable; Mmpty / Full Flag production; High-speed FIFO目录摘要 (I)ABSTRACT (I)第一章绪论 (1)1.1研究背景和意义 (1)1.2研究现状 (1)1.3本文的主要工作 (3)1.4论文结构 (3)第二章跨时钟域设计的挑战与实现方法 (3)2.1跨时钟域设计的挑战 (4)2.1.1亚稳态问题 (4)2.1.2亚稳态产生的原因 (5)2.1.3亚稳态的危害 (5)2.2 跨时钟域的实现方法 (6)2.2.1同步器 (6)2.2.2握手机制 (9)第三章开发环境 (11)3.1硬件平台 (11)3.2软件平台 (11)第四章异步FIFO的设计与实现 (13)4.1异步FIFO (13)4.1.1异步FIFO工作原理 (13)4.1.2异步FIFO设计的难点 (14)4.2常见异步 FIFO 的设计 (16)4.2.1 读写地址产生逻辑 (18)4.2.2空/满标志的产生与代码的实现 (19)4.3.3改进的异步 FIFO 设计方法分析 (22)4.4高速异步FIFO的设计与实现 (23)4.4.1常见FIFO模块分析 (23)4.4.2高速异步FIFO 设计 (25)第五章结论 (28)第六章参考文献 (29)致谢 (30)附录高速异步FIFO设计仿真分析 (31)附1. 设计工作流程 (31)附.1.1 设计输入 (31)附.1.2 设计编译 (35)附.1.3 设计仿真 (36)第一章绪论1.1研究背景和意义作为21 世纪最重要的科学领域之一,超级计算机是体现科技竞争力和综合国力的重要标志。

异步fifo的读写

异步fifo的读写这⾥不讨论异步fifo是如何实现的,⽽是在实现fifo的前提下,对fifo的读写。

现在遇到的问题是:总线的数据不能写⼊fifo中,但是地址能加⼀。

代码如下:if( !fifo_tx_full && cpu_write_fifo_en ) beginfifo_r[ write_addr[ADDR_SIZE - 1'b1 : 0] ] <= cpu_2_fifo;write_addr <= write_addr + 1'b1;end接收到的数据位00.可能是时序约束问题,在之前我确实没有约束。

改了译码的编写后就好了,在此,没有译码必须是1个1的译码,不然就会出错。

但是,地址不够,我要如何改,现在还不确定。

但是译码必须是1 个 1.//控制三态always @(cpu_read_req or intrp_en_en or fifo_con_en) beginif(cpu_read_req)en_tri = 1'b1;elseen_tri = 1'b0;end由于read和write是同⼀地址,所以这样总线就冲突了。

这样读总线上的读数据就都是0.always @(cpu_read_req or intrp_en_en or fifo_con_en) begin if(cpu_read_req && cpu_read_clk ) en_tri = 1'b1; else en_tri = 1'b0;end修改后的代码,读请求和cpu_read_clk同时有效,才使能输出。

这样总线就不会冲突了。

结果正确。

注:通过这个,知道总线上只能有⼀个是发数据,其他的设备只能是接收数据。

不然就会冲突,且此时接收可能为0。

异步FIFO设计

【转】/s/blog_6592e7700100x68n.html异步FIFO是一种先进先出电路,用在需要实时数据接口的部分,用来存储、缓冲在两个异步时钟之间的数据传输。

异步FIFO与同步FIFO最大的不同在于异步FIFO读写时钟不同,通常异步FIFO用来做数据的时钟域转换,FIFO设计中难度最大的地方在FIFO的空满标识的产生,对同步FIFO来说,由于读写指针的增加时钟频率相同,因此读写指针可以直接进行比较产生出空满标志,而异步FIFO某由于读写两端时钟频率不同,读写指针需要进行时钟域转换后才能进行比较,也就是读时钟域的读地址要先转到写时钟域,然后与写时钟域的写地址进行比较,而实际这种比较时存在一定风险的。

异步FIFO设计一般的结构有:双口存储器、读地址产生逻辑、写地址产生逻辑、空/满标志产生逻辑四部分构成。

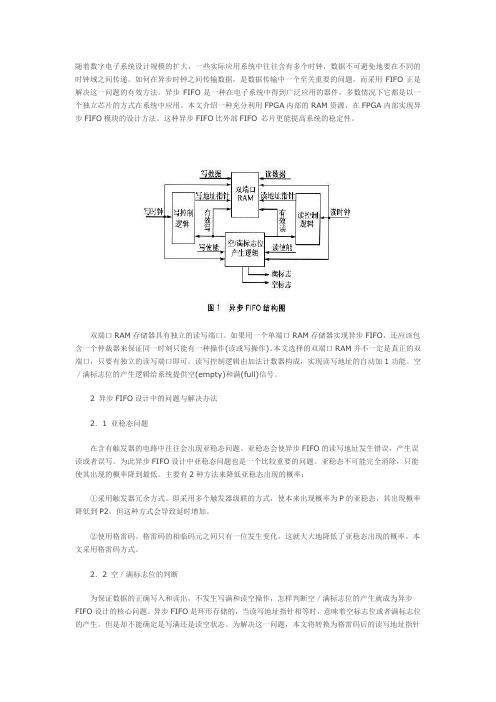

图1是一种常用的异步FIFO设计方案,其中,读地址(rptr)和空标志(rempty)由读时钟(rclk)产生,而写地址(wptr)和满标志(wfull)由写时钟(wclk)产生。

把写地址与读地址相互比较以产生空/满标志。

由于读写地址的变化由不同的时钟产生,所以对FIFO 空或满的判断是跨时钟域的。

如何避免异步传输带来的亚稳态以及正确地产生空/满标志是设计异步FIFO的难点。

图1在设计时,需要弄清楚以下几个方面:1.首先确定输入输出接口,异步FIFO在一个时钟域中进行写数据操作,而在另一个时钟域中进行读数据操作,所以在写数据模块,需要有写数据wdata,写时钟wclk,写复位wrst_n,写请求wreq,写满标志wfull;在读数据模块,需要有读数据rdata,读时钟rclk,读复位rrst_n,读请求rreq,读空标志rempty。

其中rdata,rempty,wfull为输出信号,其余为输入信号。

其FIFO用来存储16*8数据(数据宽为8,数据深度为16)的顶层模块如下://异步FIFO缓存16*8数据,即数据宽度为8,深度为16//module yibufifo(rdata,rempty,rrep,rclk,rrst_n,wdata,wfull,wrep,wclk,wrst_n);input wclk,wrep,wrst_n;input rclk,rrep,rrst_n;input[7:0]wdata;output[7:0]rdata;output rempty,wfull;wire wclk,wrep,wrst_n;wire rclk,rrep,rrst_n;wire [7:0]wdata;wire [7:0]rdata;wire [3:0]wptr,rptr;wire [3:0]waddr,raddr;wire aempty_n,afull_n;ram i1(.wdata(wdata),//读写存储模块.rdata(rdata),.waddr(wptr),//地址与指针同步.raddr(rptr),//.wrep(wrep),.wclk(wclk));async_cmp i2(.aempty_n(aempty_n),//异步比较读写指针产生异步空满标志.afull_n(afull_n),.wptr(wptr),.rptr(rptr),.wrst_n(wrst_n));rptr_empty2 i3(.rempty(rempty),//根据rclk产生读指针rptr和空标志rempty.rptr(rptr),.aempty_n(aempty_n),.rrep(rrep),.rclk(rclk),.rrst_n(rrst_n));wptr_full2 i4(.wfull(wfull),//根据wclk产生写指针wptr和满标志wfull.wptr(wptr),.afull_n(afull_n),.wrep(wrep),.wclk(wclk),.wrst_n(wrst_n));endmodule顶层模块图:其中2.1 读写地址产生逻辑(本设计中读写地址与读写指针同步)读写地址线一般有多位,如果在不同的时钟域内直接同步二进制码的地址指针,则有可能产生亚稳态。

异步fifo时序约束

异步FIFO时序约束在数字电路设计中,异步FIFO(First-In First-Out)是一种常见的同步和异步信号之间的缓冲器。

由于FIFO是在不同的时钟域上操作,因此需要考虑时序约束以确保数据正确传输。

本文将介绍异步FIFO的时序约束及其重要性。

一、异步FIFO简介异步FIFO是一种存储器,它可以在不同的时钟域上读写数据。

在数字电路设计中,FIFO被广泛应用于解决不同时钟域之间的数据传输问题。

由于异步FIFO 涉及跨时钟域的操作,因此需要特别注意时序约束,以避免数据冲突和亚稳态问题。

二、异步FIFO时序约束异步FIFO的时序约束主要包括以下几个方面:1.读/写时钟域的约束:为了保证数据的正确传输,读/写时钟域必须满足一定的时序要求。

具体来说,写时钟域的频率应该高于读时钟域的频率,以避免数据在FIFO中溢出。

同时,两个时钟域之间的相位差也应该控制在一定的范围内,以避免数据读写时出现冲突。

2.读/写指针的约束:读/写指针是FIFO中用于追踪读写位置的变量。

为了保证数据的正确读写,读/写指针必须满足一定的时序要求。

具体来说,写指针的更新应该发生在写时钟域的上升沿,而读指针的更新应该发生在读时钟域的上升沿。

这样可以确保在正确的时钟周期内进行数据读写操作。

3.数据有效性的约束:由于异步FIFO涉及跨时钟域的操作,因此需要考虑数据的有效性。

具体来说,当读指针小于写指针时,FIFO中的数据是有效的;而当读指针大于或等于写指针时,FIFO中的数据是无效的。

因此,需要根据实际情况对数据的读写进行控制,以确保数据的正确性。

4.空/满标志的约束:空/满标志是用于指示FIFO是否为空或满的标志位。

为了保证数据的正确传输,空/满标志必须满足一定的时序要求。

具体来说,当FIFO为空或满时,相应的标志位应该被及时更新;而当FIFO不为空或满时,相应的标志位应该保持不变。

这样可以确保在正确的时钟周期内进行数据读写操作。

三、结论异步FIFO时序约束是数字电路设计中需要考虑的重要问题之一。

异步FIFO设计中遇到和解决的问题

随着数字电子系统设计规模的扩大,一些实际应用系统中往往含有多个时钟,数据不可避免地要在不同的时钟域之间传递。

如何在异步时钟之间传输数据,是数据传输中一个至关重要的问题,而采用FIFO正是解决这一问题的有效方法。

异步FIFO是一种在电子系统中得到广泛应用的器件,多数情况下它都是以一个独立芯片的方式在系统中应用。

本文介绍一种充分利用FPGA内部的RAM资源,在FPGA内部实现异步FIFO模块的设计方法。

这种异步FIFO比外部FIFO 芯片更能提高系统的稳定性。

双端口RAM存储器具有独立的读写端口。

如果用一个单端口RAM存储器实现异步FIFO,还应该包含一个仲裁器来保证同一时刻只能有一种操作(读或写操作)。

本文选择的双端口RAM并不一定是真正的双端口,只要有独立的读写端口即可。

读写控制逻辑由加法计数器构成,实现读写地址的自动加1功能。

空/满标志位的产生逻辑给系统提供空(empty)和满(full)信号。

2 异步FIFO设计中的问题与解决办法2.1 亚稳态问题在含有触发器的电路中往往会出现亚稳态问题。

亚稳态会使异步FIFO的读写地址发生错误,产生误读或者误写。

为此异步FIFO设计中亚稳态问题也是一个比较重要的问题。

亚稳态不可能完全消除,只能使其出现的概率降到最低。

主要有2种方法来降低亚稳态出现的概率:①采用触发器冗余方式。

即采用多个触发器级联的方式,使本来出现概率为P的亚稳态,其出现概率降低到P2,但这种方式会导致延时增加。

②使用格雷码。

格雷码的相临码元之间只有一位发生变化,这就大大地降低了亚稳态出现的概率。

本文采用格雷码方式。

2.2 空/满标志位的判断为保证数据的正确写入和读出,不发生写满和读空操作,怎样判断空/满标志位的产生就成为异步FIFO设计的核心问题。

异步FIFO是环形存储的,当读写地址指针相等时,意味着空标志位或者满标志位的产生。

但是却不能确定是写满还是读空状态。

为解决这一问题,本文将转换为格雷码后的读写地址指针分别经过检测和计数器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、前言跨时钟域的同步处理,使用异步FIFO是常用的方式之一,对于异步FIFO的设计,网上的大部分资料来源于《Simulation and Synthesis Techniques for Asynchronous FIFO Design》一文其异步FIFO的结构如下图所示本文不是介绍上图描述的设计。

我从基本的数字电路时序开始,介绍异步FIFO的相关问题。

最后介绍如何用时序约束保证设计的正确性二、数字电路时序对于数字电路来讲,我们的信号在时钟边沿发生变化,Dat1信号是一种理想情况,而Dat2是实际情况,其特点是一、相对时钟边沿有延时二、信号变化有一段时间(电平转换时间),在这段时间就是亚稳态在亚稳态期间进行数据采样,不能获得稳定的值。

数字电路中经过时序约束,在T1产生的信号,在T2一定稳定(否则就是不满足时序),所以对于只有一个时钟的数字电路来说,它在T1和T2都能获得稳定的信号(T1时刻的值为0、T2时刻的值为1)三、跨时钟域时序问题对于异步时钟而言(相位不同),对于CLK1产生的信号,CLK2有可能在任意时刻进行数据采样在FIFO的设计中,将会产生2种信号,一种是数据本身(用Data表示),另外一种是指示数据是否有效(用valid表示),注意(valid不一定是一个比特的寄存器,可以是由FIFO中的读写指针产生而来,例如fifo的full或empty状态)异步FIFO的问题在于,如果CLK2在时钟T2进行采样,那么有可能得到valid有效,而数据无效的情况。

这样在CLK2采样取得的设计就是错误的数据。

四、处理异步FIFO的valid和data(理论基础)我们假设valid为低电平表示没有数据,高电平为有数据,解决的办法就是,当CLK对valid进行采样时,即使valid处于亚稳态期间,数据信号也是稳定的如上图所以,在T1时刻进行上升沿采样,虽然valid是一个亚稳态状态,但是此时Data 是一个稳定的值,如果在T1时刻采样的valid为1,那么可以得到稳定的Data信号,如果在T1时刻采样的valid为0,那么控制逻辑认为在T1无法获得数据,从而在下一个时钟获取注意:T2时刻是在下降沿进行采样,而此时的Data信号也是稳定的五、如何实现为了让valid和Data处于上面的状态,我们可以对valid进行延时处理,即使用时钟对其进行采样,必须使用2个寄存器依次采样,才能保证至少有一个时钟的延时valid1是CLK2对valid进行采样产生的,如果采样的时机不好,那么valid1相对valid只有一点点延时,valid2是CLK2对valid1的采样,这样valid2相对于valid至少有CLK2一个周期的延时,也就满足了第二节的条件。

所以在《Simulation and Synthesis Techniques for Asynchronous FIFO Design》的设计中,将写时钟域写指针使用2级寄存器同步到读时钟域,然后使用该同步后的写指针和读时钟域读指针产生valid状态,(备注:写时钟域写指针发生改变就和上图中valid发生变化是一个道理,代表数据写入,使用读时钟域同步后想当于产生valid2信号,相信不难理解),写指针是多比特数据,无法在亚稳态获取数据,必须使用一次只有一个比特变化的格雷码,然后再使用格雷码产生valid状态(即FIFO中的full或者empty),同样的道理,将读时钟域的读指针使用2级寄存器同步写时钟域。

其目的是判断数据是否已经被读取。

这就是《Simulation and Synthesis Techniques for Asynchronous FIFO Design》中的理论支持,其它的逻辑就是格雷码的设计、FIFO的状态产生等逻辑,本文不再进行详细说明。

六、问题产生《Simulation and Synthesis Techniques for Asynchronous FIFO Design》的设计中是否能绝对保证异步FIFO的正确性?如上图所示,在T1时刻CLK1产生了valid和Data信号,它是满足时序要求的,在T2时刻是稳定的,只是valid比Data先稳定。

我们对valid进行采样延时,产生的valid1是可以出现上面的状态,但此时valid1和Data都是亚稳态,不满足关系需要说明的是1、上述出现的概率较小,取决数字后端布局2、如果进行采样的同步时钟比CLK1慢(即写时钟快于读时钟),不会出现问题3、后端布局后,还可以进行多时钟时序仿真,也可以发现问题七、改进设计在异步FIFO设计中,我们必须要保证valid和data的相对关系。

我们可以通过下面的逻辑设计再加上时序约束来保证这一点。

一、逻辑设计控制逻辑,在T1时刻准备好数据,在T2时刻产生valid二、时序约束将读写2个时钟设置为同一个时钟,频率设置使用最高频率的那个时钟。

(可以单独将这个FIFO做块,或者和高频率的那个模块一起做块)经过上面的逻辑设计和时序约束,对于要采样valid和data的异步时钟而言:1、由于是采用最高频率的时钟进行约束,即使采样时钟频率低,也能满足时序要求2、通过逻辑设计和时序约束,对于采样时钟而言,valid和Data也一定是满足相对关系八、参考代码module Mfifo(input rst_n,input wr_clk,input wr_req,input[7:0]wr_data,output wr_ready,input rd_clk,input rd_req,output[7:0]rd_data,output rd_ready);reg[7:0]fifo_r[3:0];reg[1:0]wp_r;reg wp_valid_r;reg[3:0]wp_flag_r;reg[1:0]rp_r;reg rp_valid_r;reg[3:0]rp_flag_r;//=================================================================== //WR CLK//=================================================================== always@(posedge wr_clk)beginif(~rst_n)wp_r<=2'b00;else if(wr_req&wr_ready)wp_r<=wp_r+2'b01;endalways@(posedge wr_clk)beginif(wr_req&wr_ready)fifo_r[wp_r]<=wr_data;endalways@(posedge wr_clk)beginif(~rst_n)wp_valid_r<=1'b0;else if(wr_req&wr_ready)wp_valid_r<=1'b1;else if(wp_valid_r)wp_valid_r<=1'b0;endalways@(posedge wr_clk)beginif(~rst_n)wp_flag_r<=4'b0000;else if(wp_valid_r)wp_flag_r[wp_r-2'b01]<=~wp_flag_r[wp_r-2'b01];end//=================================================================== //RD CLK//=================================================================== always@(posedge rd_clk)beginif(~rst_n)rp_r<=2'b00;else if(rd_req&rd_ready)rp_r<=rp_r+2'b01;endalways@(posedge rd_clk)beginif(~rst_n)rp_valid_r<=1'b0;else if(rd_req&rd_ready)rp_valid_r<=1'b1;else if(rp_valid_r)rp_valid_r<=1'b0;endalways@(posedge rd_clk)beginif(~rst_n)rp_flag_r<=4'b0000;else if(rp_valid_r)rp_flag_r[rp_r-2'b01]<=~rp_flag_r[rp_r-2'b01];end//=================================================================== //FIFO STATE//=================================================================== assign wr_ready=wp_flag_r[wp_r]==rp_flag_r[wp_r];assign rd_ready=wp_flag_r[rp_r]!=rp_flag_r[rp_r];assign rd_data=fifo_r[rp_r];endmodule九、其它补充1、异步fifo的主要目的是跨时钟同步,不应该有复杂的控制逻辑和fifo深度,(复杂的控制逻辑可以放在其它地方实现,如果实在需要深度较大fifo来缓冲数据,可以用同步fifo接在异步fifo的输入或输出端,以此达到目的)2、不管异步FIFO如何设计,一定要做时序仿真(下图是在fpga上的布局后的时序仿真)。