FPGA异步fifo设计完整报告

异步FIFO设计(非常详细,图文并茂,值得一看!)

异步FIFO设计(非常详细,图文并茂,值得一看!)一、概述在大规模ASIC或FPGA设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO来作不同时钟域数据传输的缓冲区,这样既可以使相异时钟域数据传输的时序要求变得宽松,也提高了它们之间的传输效率。

此文内容就是阐述异步FIFO的设计。

二、设计原理2.1结构框图Fig. 2.1.1如上图所示的同步模块synchronize to write clk,其作用是把读时钟域的读指针rd_ptr采集到写时钟(wr_clk)域,然后和写指针wr_ptr进行比较从而产生或撤消写满标志位wr_full;类似地,同步模块synchronize to read clk的作用是把写时钟域的写指针wr_ptr采集到读时钟域,然后和读指针rd_ptr进行比较从而产生或撤消读空标志位rd_empty。

另外还有写指针wr_ptr和写满标志位wr_full产生模块,读指针rd_ptr和读空标志位rd_empty产生模块,以及双端口存储RAM模块。

2.2 二进制计数器存在的问题异步FIFO读写指针需要在数学上的操作和比较才能产生准确的空满标志位,但由于读写指针属于不同的时钟域及读写时钟相位关系的不确定性,同步模块采集另一时钟域的指针时,此指针有可能正处在跳变的过程中,如图Fig.2.2.1所示,那么采集到的值很有可能是不期望的值,当然,不期望的错误结果也会随之发生。

Fig. 2.2.1上图中,rd_ptr2sync 3和4以及4和5之间的中间态是由于到各寄存器的时钟rd_clk存在偏差而引起的。

二进制的递增操作,在大多数情况下都会有两位或者两以上的bit位在同一个递增操作内发生变化,但由于实际电路中会存在时钟偏差和不同的路径延时,二进制计数器在自增时会不可避免地产生错误的中间结果,如图Fig.2.2.2。

Fig.2.2.2上图是Fig.2.2.1的电路原型以及局部波形的放大。

基于FPGA的异步FIFO设计

目前 兀F O的 内部 结构是 由双 口 R M 加驱 动 双 口 R M 地 址 的计 数器 构成 ,异 步 F. A A I

F O是 由读 写信 号 使计 数 器翻 转 。我们 在 程序 设 计 时也采 用 这 一实 现 方式 ,调 用 F G 内 PA

部集成 的双 端 口 R M 存储 器 ,再加 一些 逻辑 电路来 实 现具 体的操 作 。 O

因此 ,对 FF IO空或 满 的判 断是 跨 时钟 域 的 。根 据异 步 的指针 信 号对 F F 的满状 态 或空 IO

状态 进行 正确 的判 断是实 现异 步 F F 的重 点 和核心 。如何 正 确设计 此 部分 的逻 辑 .直接 IO 影 响到 FF IO的性 能。

空/ 满标 志产 生 的原 则是 无论 在进 行 什么操 作 。都 不应 出 现读 写地址 同时对 一个 存储

FF IO ̄难 点 即空/ 满标 志组成 部分 。最后 给 出 了总的逻 辑仿 真 波形 图验 证本 次设

基于FPGA的异步FIFO设计

收稿日期:!""#$%"$!"作者简介:张维旭(%&’($),男,山东潍坊人,硕士研究生,研究方向为)*+;贺占庄,研究员,硕士生导师,研究方向为计算机控制技术。

基于!"#$的异步!%!&设计张维旭,贺占庄(西安微电子技术研究所,陕西西安’%"",#)摘要:在现代集成电路设计中,一个系统往往包含了多个时钟,如何在异步时钟间传递数据成为一个很重要的问题,而使用异步-.-*可以有效地解决这个问题。

异步-.-*是一种在电子系统中得到广泛应用的器件,文中介绍了一种基于-/012的异步-.-*设计方法。

使用这种方法可以设计出高速、高可靠的异步-.-*。

关键词:-.-*;亚稳态;格雷码;-/12中图分类号:3/4%%5%文献标识码:2文章编号:%,’4$,!&6(!"",)"’$"%,($"4$’()*+,-)-.’!%!&/0’12)34’05-)!"#$78291:;<0=>,8?7@A B 0C @>A B D(6<’A BE <F G H ;I ;F J G H B <F3;F @B H I H D K L;M ;A G F @.B M J <J >J ;,6<’A B ’%"",#,+@<B A )$6’7,4*7:.BN H O ;G B .+O ;M <D B M ,A M K M J ;NA I P A K M F H B J A <B M M ;Q ;G A I F I H F R M S 3G A B M N <J J <B D O A J A A N H B D A M K B F @G H B H >M F I H F R M T ;F H N ;A B <N U H G 0J A B J U G H T I ;N S V >J <J F A B M H I Q ;J @<M U G H T I ;NT K >M <B D A M K B F @G H B H >M -.-*S 2M K B F @G H B H >M -.-*<M A O ;Q <F ;J @A J P A M P <O ;I K >M ;O <B ;I ;F J G H B <F M K M J ;N S 3@<M U A U ;G <B J G H O >F ;M AN ;J @H O H W -.-*O ;M <D B T A M ;O H B-/12S +A B O ;M <D B @<D @M U ;;O A B O G ;I <A T <I <J K A M KB F @G H B H >M -.-*S 80(9-,5’:-.-*;N ;J A M J A T <I <J K ;1G A K +H O ;;-/12:异步!%!&介绍随着现代芯片设计规模的不断扩大,集成电路越来越复杂,一个系统中往往包含多个时钟。

异步FIFO设计

异步FIFO设计2011.6.22摘要本文采用格雷码设计了一个异步FIFO,经过DC综合的结果如下:时钟频率:1.1GHz面积: 10744.447um2功耗: 7.791mw目录1. 异步FIFO的设计 (22)1.1 异步FIFO简介 (22)1.2 FIFO的参数 (22)1.3 FIFO的设计原理 (22)1.4 FIFO的设计模块 (66)1.5 用modelsim仿真FIFO (1111)1.6 用DC对FIFO进行综合 (1313)2.参考文献 (1515)1. 异步FIFO的设计1.1 异步FIFO简介FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,它与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

根均FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。

同步FIFO是指读时钟和写时钟为同一个时钟。

在时钟沿来临时同时发生读写操作。

异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

异步FIFO(Asynchronous FIFO),一般用于不同时钟域之间的数据传输,比如FIFO的一端连接频率较低的AD数据采样信号,另一端与计算机的频率较高的PCI总线相连。

另外,对于不同宽度的数据接口也可以用AFIFO,例如单片机为8位数据输出,而DSP可能是16位数据输入,在单片机与DSP连接时就可以使用AFIFO来达到数据匹配的目的。

由于实际中,异步FIFO比较常见。

为了便于描述,在后面的章节中将异步FIFO简称为FIFO.1.2 FIFO的参数FIFO的宽度:进行一次读写操作的数据的位宽。

FIFO的深度:双口存储器中能容纳的数据的总数。

满标志: FIFO已满或将要满时由FIFO的状态电路送出的一个信号,以阻止FIFO的写操作继续向FIFO中写数据而造成溢出。

基于FPGA的高速异步FIFO存储器的设计与实现

信息科技中国科技信息2009年第2期CHINASCIENCEANDTECHNOLOGYINFORMATIONJan.2009基于F1》GA的离述舞步FIFO存储器的设计与实现罗先哲1张仁吉吉2付大鹏21、贵州大学科技学院2、贵州大学电子科学与信息技术学院550025摘要本文在介绍异步FlF0基本原理及结构的基础上,采用VerilogHDL硬件描述语言对异步FIFO存储器进行了RTL级设计。

在设计中采用格雷码对读写地址进行编码,有效的避免了亚稳态的产生;并使用ALTEP,,A公司的集成开发环境quartusIl7.0对设计进行了编译仿真,最后在该公司的Cyclone系列器件EPlC3T100(36上通过了验证。

袭键词H。

蠕异步FIF0;FPGA;格雷码;亚稳态;VerilogHDL曲‰tr∞t-j:镬Thi9paperpresentedtheb;毗prfncip慨arldstrdctbl'eoftheasynchronousFIFOmemory,andgiventilegTLdesignwhichbasedtheVerilogHDLlanguage.InShisdesign,itissucceedineliminatingmetastabilitybyusingGraycodetocodingaddresscode.ThedesigncompiledandsimulatedbyALTERA’ssoftwareQuartusII7.0.Athst,itremindbythedeviceEP1CST100C6ofALTERA’SCyclonefamily.a删0胁脚u地showst『)at,t『Iedesign船succeed.黼word,,.‘罐A9ynchFIF0;FPGA;Greycode;metastabllity;VerilogHDL1引言随着集成电路工艺的不断发展,在同一个芯片上集成整个系统已成为可能,IC设计已进入SoC时代。

异步先进先出fifo设计报告

异步先进先出FIFO设计报告一、设计目的介绍FIFO的定义,工作原理,对其管脚进行详细的阐述,并对其功能实现进行具体操作和演示。

通过本次设计为以后数字电路设计中处理连续数据流和信号同步、减少CPU 负担等问题打下良好基础。

二、实验器材和工具软件PC机一台、ISE13.1软件、Modelsim软件三、设计内容及原理1、内容(1)FIFO模块的读时钟周期20ns,写时钟周期40ns,前20ns复位信号有效。

(2)FIFO模块的写使能信号前95ns无效,持续1285ns有效后又无效;读使能信号前1600ns无效,持续1880ns有效后又无效。

(3)40ns后读入数据,数据从0开始每隔40ns加1,直至累加到32为止。

2、异步先进先出FIFO原理该设计就是使用Xilinx公司提供的块RAM资源和IP核生成器产生的FIFO (First In First Out)队列,即先进先出的队列,其结构如图1所示。

图1 异步FIFO结构在FIFO具体实现时,数据存储的部分是采用简单双端口模式操作的,一个端口只写数据而另一个端口只读数据,另外在RAM(块RAM和分布式RAM)周围加一些控制电路来输出知识信息。

FIFO最重要的特征是具有满(FULL)和空(EMPTY)的指示信号,当FULL信号有效时(高电平),就不能再往FIFO 中写入数据,否则会造成数据丢失;当EMPTY信号有效时(高电平),就不能从FIFO中读取数据,此时输出端口处于高阻态。

图1给出了本次设计所用到的异步FIFO的结构图,其接口信号描述如下。

DIN[N:0]:数据输入端,当写FIFO时使用该总线。

WR_CLK:写时钟,所有写相关的信号与该时钟同步。

WR_EN:写使能,如FIFO不满,当该信号有效时,数据写入到FIFO中。

RD_CLK:读时钟,所有读相关的信号与该时钟同步。

RD_EN:读使能,如FIFO不空,当该信号有效时,数据从FIFO中读出。

DOUT[N:0]:数据输出端,当读FIFO时使用该总线。

基于FPGA的异步FIFO设计_毕业设计(论文)

江苏科技大学本科毕业设计(论文)基于FPGA的异步FIFO设计Asynchronous FIFO design based on FPGA摘要在现代集成电路芯片中,随着设计规模的不断扩大,一个系统往往包含多个时钟,如何进行异步时钟间的数据传输成为了一个很重要的问题。

异步FIFO (First In First Out)是一种先进先出电路,可以在两个不同的时钟系统间进行快速准确的数据传输,是解决异步时钟数据传输问题的简单有效的方案。

异步FIFO 在网络接口、数据采集和图像处理等方面得到了十分广泛的应用,由于国内对该方面研究起步较晚,国内的一些研究所和厂商开发的FIFO电路还远不能满足市场和军事需求。

由于在异步电路中,时钟间的周期和相位完全独立,以及亚稳态问题的存在,数据传输时的丢失率不为零,如何实现异步信号同步化和降低亚稳态概率以及正确判断FIFO的储存状态成为了设计异步FIFO电路的难点。

本课题介绍了一种基于FPGA的异步FIFO 电路设计方法。

课题选用Quartus II软件,在Cyclone II 系列的EP2C5T144C8N芯片的基础上,利用VHDL 硬件描述语言进行逻辑描述,采用层次化、描述语言和图形输入相结合的方法设计了一个RAM深度为128 bit,数据宽度为8 bit的高速、高可靠的异步FIFO电路,并对该电路功能进行时序仿真测试和硬件仿真测试。

关键词:异步FIFO;同步化;亚稳态;仿真测试AbstractIn modern IC chips, with the continuous expansion of the scale of design, a system always contains several clocks. How to transmit data between the asynchronous clocks become a very important problem.Asynchronous FIFO (First In First Out) is a first-in, first-out circuit, it can transmit data between two diffent clock systems fastly and accurately, it is also a simple and effective solution to solve the problem of asynchronous clock data transfer. The asynchronous FIFO has a very wide range of applications in network interface, data acquisition and image processing.But because of the aspect of a late start, some domestic research institutes and manufacturers which research the FIFO circuit also can not meet the needs of the market and the military.In the asynchronous circuit, because of that the clock cycle and phase is completely independent, and the presence of metastability problems, the loss rate of data transmission is not zero. How to implement asynchronous signal synchronization, reduce the probability of metastability and judge the state of the FIFO storage correctly become a difficult problem while designing the asynchronous FIFO circuit. This paper introduces a method of asynchronous FIFO circuit design based on FPGA. This topic selects Quartus II software, the Cyclone II family EP2C5T144C8N chip, based on the use of VHDL hardware description language for logical descriptions, using the method of combining hierarchical, description language and graphical input ,This topic designs a high-speed, highly reliable asynchronous FIFO circuit as the RAM depth is 128 bit and the data width is 8 bit, and tests the circuit function with timing and software simulation.Keywords:Asynchronous FIFO; Synchronization; Metastability; simulation testing目录第一章绪论 (1)1.1 FPGA简介 (1)1.2 异步FIFO简介 (1)1.3 国内外研究现状及存在的问题 (1)1.3.1 研究现状 (1)1.3.2 存在问题 (2)1.4 本课题主要研究内容 (3)第二章异步FIFO设计要求及基本原理 (4)2.1 设计要求 (4)2.2 异步FIFO基本原理 (5)2.3 异步FIFO设计难点 (5)2.4 系统设计方案 (6)2.5 异步FIFO验证方案 (7)2.5.1 验证复位功能 (7)2.5.2 验证写操作功能 (7)2.5.3 验证读操作功能 (7)2.5.4 验证异步FIFO电路整体功能 (7)第三章模块设计与实现 (8)3.1 格雷码计数器模块 (8)3.2 同步模块 (8)3.3 格雷码∕自然码转换模块 (9)3.4 空满标志产生模块 (10)3.5 双端口RAM (13)第四章时序仿真与实现 (15)4.1 模块整合 (15)4.2 时序仿真及功能测试 (17)4.2.1 复位功能软件仿真与测试 (17)4.2.2 写操作功能时序仿真与测试 (17)4.2.3 读操作功能时序仿真与测试 (18)4.2.4 异步FIFO电路整体功能软件仿真与测试 (18)4.2.5 时序仿真结果总结 (19)第五章硬件仿真与实现 (20)5.1 外部电路焊接 (20)5.2 引脚分配 (21)5.3 调试电路设计 (24)5.3.1 调试电路介绍 (24)5.3.2 异步时钟产生模块 (25)5.3.3 伪随机数据队列产生模块 (25)5.3.5 调试电路引脚分配 (26)5.3.6 调试电路硬件仿真 (27)5.4 异步FIFO电路硬件仿真 (28)5.4.1 复位功能硬件仿真与测试 (29)5.4.2 写操作功能硬件仿真与测试 (30)5.4.3 读操作功能硬件仿真与测试 (30)5.4.4 异步FIFO硬件电路整体功能软硬件仿真与测试 (31)5.4.5 硬件仿真结果总结 (32)结论 (33)致谢 (34)参考文献 (35)附录 (36)第一章绪论1.1 FPGA简介FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在CPLD、PAL、GAL等可编程器件的基础上进一步发展的产物[10]。

基于FPGA的帧级异步FIFO设计

2020年第 2 期 声学与电子工程 总第 138 期32基于FPGA的帧级异步FIFO设计水颖(第七一五研究所,杭州,310023)摘要为了解决 FIFO对整帧数据的缓存问题,文章设计完成了一种基于 FPGA 的帧级异步 FIFO,该异步FIFO是基于Verilog HDL高级可编程语言实现的,它可以很方便的用于互联网数据帧的中间缓存,保证互联网数据帧在大吞吐量情况下不易发生丢失。

采用 modelsim 10.6仿真验证该设计,并应用于实际项目中进行大规模测试,结果表明该方案工作性能可靠稳定。

关键词帧级;异步FIFO;存储目前,在传输业界中,网关、加扰机、编码机及调制解调设备等多采用千兆级以太网作为交互接口,要完成交互过程中大容量数据简单方便的缓存,通常采用板载FIFO、SRAM、SDRAM或DDR 颗粒芯片的方案。

在一些对存储资源要求不高但对存储速度要求高的应用中,大多使用FPGA内部的存储器资源。

FIFO 是一种在电子系统得到广泛应用的模块,通常用于数据的缓存和容纳异步信号的频率或相位的差异。

FIFO 的实现通常是利用双口RAM 和读写地址产生模块来实现的。

本文根据互联网帧的实际处理,提出了一种帧级FIFO的设计,从而完成整帧数据处理的异步FIFO[1],设计的 FIFO处理模块是针对每一帧而不是每一个数据。

根据FPGA提供BRAM块,搭建FIFO 的读写以及数据使能,最关键的设计是控制读写地址、产生空满信号以及校验。

此方式产生帧级的异步FIFO,既可以减少使用内部FIFO带来资源高的问题,又可以隔离异步时序减少亚稳态的产生。

1功能描述及组成传统的异步时序FIFO,当写入一个FIFO位宽的数据,FIFO的空信号(empty)置0,则可以进行读取数据。

本文设计的基于帧级异步时序FIFO,当一个正常数据包正在写入时,FIFO的空信号并不会置0;只有当正常数据包全部写入异步FIFO中,空信号才能置0,数据才能够被读取。

基于FPGA的异步FIFO设计与实现

基于FPGA的异步FIFO设计与实现王伟国;张振东【摘要】随着现代数字电路系统密度和规模的不断扩大,一个系统中通常会包含多个时钟,因此不同时钟之间的数据传输成为亟待解决的问题.而一种可靠易行的解决方案就是异步FIFO.异步FIFO需要非常严格的多时钟技术,难以作出正确的设计合成和分析.本文提出了一种利用格雷码作为读写地址计数器的异步FIFO的设计方法,有效的避免了数据在不同时钟时间传输时遇到的亚稳态问题.并给出了综合仿真结果.%With the expanding of the density and scale of modern digital circuitry,a system will contain multiple clock.Therefore,the transfer of data between different clock becomes a serious problem needs to be solved.A reliable and feasible solution is asynchronous FIFO.Asynchronous FIFO require very strict clock technology,it is difficult to make the correct design of synthesis and analysis.This paper presents a design method of asynchronous FIFO which based on read/write counter in terms of gray code.This method effectively avoid the metastable state in the data transmission between different clock and given a comprehensive simulation results.【期刊名称】《聊城大学学报(自然科学版)》【年(卷),期】2012(025)003【总页数】6页(P79-84)【关键词】多时钟;异步fifo;verilog;HDL;格雷码【作者】王伟国;张振东【作者单位】中国科学院长春光学精密机械与物理研究所,吉林长春130033;中国科学院长春光学精密机械与物理研究所,吉林长春130033/中国科学院研究生院,北京100039【正文语种】中文【中图分类】TN4330 引言随着现代数字电路系统的实时数据处理能力的不断提高,逻辑电路的复杂程度和内核处理器的运算速度也快速增长,在使得一些复杂算法得以实现的同时也加剧了快速CPU与慢速外设之间的冲突.异步FIFO大量数据缓存的能力成功的解决了这一问题,但专用的高速异步FIFO芯片价格昂贵,且容量受限,随着现场可编程逻辑器件容量和速度的不断提高,利用现场可编程逻辑器件设计异步FIFO成为可行的方法.本文首先讨论了异步FIFO设计中经常出现的亚稳态问题和二进制计数器多位同时改变的问题,并给出解决办法,然后讨论了两种格雷码计数器的形式并作出比较,最后给出一种以格雷码为读写地址计数器的异步FIFO的设计方法和在设计异步FIFO时必须要注意的细节.1 多时钟电路中的亚稳态问题在一个时序电路中,合理的建立时间和保持时间是触发器正常工作的前提条件.对于下降沿触发的触发器而言,下降沿触发之前输入数据持续的最短时间是建立时间(setup time),下降沿触发之后输入数据持续的最短时间是保持时间(hold time).当电路时序不能满足setup time/hold time的要求时,系统时序就会出现混乱.在异步时序电路中,不同时钟之间是不存在任何关系的,必然会产生建立时间和保持时间冲突.解决系统时序问题常用双锁存器法如下图1所示,即在不同时钟之间传输数据时连续锁存两次.但是这种方法只是保证了电平的稳定,而在实际的系统中还需要FIFO作为不同时钟之间传输多位数据的接口.图1 避免亚稳态出现的双锁存器法2 异步FIFO指针对于同步FIFO来说,使用一个计数器计算读出和写入到FIFO缓存器中的数据量,计数器在只有写没读是递增,只读没写是递减,既读又写和没读也没写时保持不变.当计数器到达设定值时FIFO满信号置位,为零时空信号置位.在异步FIFO中,由于这种计算数据个数增减的计数器会被两个不同的时钟控制,因此这种计数器不能使用.所以,为了决定FIFO“空”和“满”状态,读指针和写指针必须相互比较.设计FIFO最主要的困难是生成FIFO指针和找到一个决定FIFO“空”和“满”状态的可靠方法.在FIFO设计中,读指针和写指针总是指向下一个要读和写的地址空间.当读或写操作完成后指针自动递增,当FIFO是空时读指针和写指针相等,当FIFO满时读指针和写指针也是相等.一种解决的方法是增加一个多余的MSB位来区分两种状态,当写指针递增超过地址范围时,写指针会递增MSB位,其他位清零,读指针同样也是.当读指针和写指针的MSB位不同时,意味着写指针比读指针多走了一圈,当MSB位相同时意味着走的圈数相等(如图2所示)图2 增加多余MSB后区分FIFO空和FIFO满的方法示意图当FIFO存储缓冲区需要(n-1)位地址时,地址指针用n位,当指针相等(包括MSB位)时空标志置位,当指针低(n-1)位相等且MSB位不等时满标志置位.2.1 二进制FIFO指针的情况二进制地址计数量会有多个位同时变化,因此在把二进制量在不同时钟域之间同步时会出现问题.一个解决的方法是取样并把周期计数量寄存在一个保持寄存器中,并发出一个ready信号,新时钟域收到信号并发出确认信号,这样变化的计数量就安全的传送到新时钟域.用这种方法不会产生上溢和下溢,因为当读指针递增到与写指针相等时,空信号置位,取样的写指针不反映当前写指针的值,而是小于当前值,故永远不能产生下溢,满信号也是如此.最常用的解决方法是用格雷码计数器,格雷码在每个时钟只有一位变换可以极大的减少在同步计数时错误的发生.3 格雷码计数器设计格雷码计数器的方法有很多,这里介绍二种简单直接的方法.下面详细介绍两种方法.3.1 格雷码计数器中的问题为了更好的理解把n-bit计数器转换成(n-1)-bit计数器时出现的问题,先考虑一下一个双重4-bit和3-bit格雷码计数器的例子如图3.图3 4-bit格雷码计数器示例及转换成3-bit格雷码时出现的问题在4-bit计数器中除了MSB位其余位关于中间对称,我们把2nd MSB位反相后,上半部分与下半部分的LSBs便相等.但是经过反相操作后整体便不是格雷码了,例如15(1100)到0(0000)的转变过程有两个bits变化,在下面的第一种格雷码计数器中会有解决方法.3.2 第一种格雷码计数器图4是第一种计数器的框图并是双重格雷码计数器中两个bits同时跳变的解决方法.其中假设输出寄存器的值是格雷码(ptr),此格雷码被输出到格雷码到二进制的转换器中,然后通过一个有条件递增的加法器并输出下一个格雷码值(gnext),连接到输出寄存器的输入端,如框图上半部分所示.(n-1)-bit格雷码简单地通过n-bit格雷码的2个MSBs的异或操作产生,(n-2)个LSBs不变.图4 第一种格雷码计数器示意图及其如何避免了两位同时跳变问题3.3 第二种格雷码计数器此种风格的格雷计数器(如图5所示)用了两组寄存器避免了把格雷码转换成二进制数的步骤.而且第二组寄存器也可以直接用来寻址FIFO存储器.n-bit格雷码指针仍然需要同步到不同的时钟域中.二进制指针可以更容易的通过计算产生“几乎满”和“几乎空”信号.因此在本论文的设计中用此种风格的格雷码计数器.图5 第二种格雷码计数器工作示意图4 总体设计及“空”和“满”信号的产生总体设计如图6所示,本设计方案共有四个模块,双口RAM模块,读控制模块,写控制模块,格雷码同步模块.写控制模块主要是当写使能信号有效且写满信号无效时产生写地址并实行地址递增功能,读控制模块实现相似功能,双口RAM模块用来使缓冲数据其读写动作可同时进行.4.1 “空”和“满”信号的产生“空”信号的产生比较简单,只需同步到读时钟域的写地址格雷码与n-bit的读指针的格雷码完全相等即可代码如下图6 异步FIFO总体设计框图及其信号说明但是,“满”信号的产生就没那么容易,简单地用n-bit格雷码作比较判断“满”信号是不可靠的.因为格雷码除了MSB位外是对称的如图3所示.在图3中假如写指针和读指针都指向地址7,此时写指针递增一次后,写指针指向地址8,读指针和写指针相比较,除了MSB位不同外其余各位均相等,满信号此时有效,但这是不符合实际情况的,错误的.这也是为什么在图4中应用双重n-bit格雷码计数器的一个原因.正确判断满信号的条件是:读写指针的n-bit格雷码的前两个MSBs都不相等,其余的写指针和同步读针相等.代码如下4.2 不同时钟速度因为异步FIFO被两个不同的时钟控制,很明显两个时钟运行在不同的速度下.当把较快的时钟同步到较慢的时钟时,会有一些计数值被跳过.当被同步的格雷码递增两次只被取样一次时也不会出现亚稳态问题,因为亚稳态出现在同步时钟上升沿附近有多位同时跳变时,而在两个同步时钟沿之间有格雷码跳变两次,第一次跳变距离同步时钟条边沿较远,只有第二次跳变在同步时钟沿附近,故不会产生亚稳态.当较快的格雷码计数器在较慢时钟沿之间递增多于一次,不会出现已经溢出却没有检测到的现象,因为同步到写时钟域的读指针滞后于当前的读指针,而写指针只会小于或等于同步读指针,故不会出现溢出.5 设计仿真及总结本设计采用Xilinx公司Spartan3A系列的XC3S1400A,封装时PG484,速度是-4,仿真器是ISE Simulator(VHDL/Verilog),硬件描述语言是Verilog,开发工具是ISE.最后对电路进行时序分析,结果为该FIFO运行速度可达到90.63MHz.wclk、rclk时钟周期分别为:75MHz、80MHz.先向FIFO中写入18个数据,当第16个数据被读入后wfull立即被置位如下图7.图7 写满仿真结果同时向FIFO中写入和读出数据,由于wptr要经过两个读周期才能同步到读时钟域,故在waddr递增后的第二个rclk的上升沿rempty才清零如下图8所示.本文对异步FIFO的结构和重要时序问题给予了详细的阐述,并得到了可靠的仿真结果.在高速数据采集系统中,采用高性能FPGA作为数据预处理和高速异步FIFO 作为数据采集缓存的应用都十分广泛.把FIFO集成在FPGA中简化了电路设计的复杂程度,增加了电路的集成化程度和可靠性,是未来高速数据采集系统的重要发展方向.图8 同时写入读出时的仿真结果参考文献【相关文献】[1] Clifford E.Cummings,Synthesis and Scrip ting Techniques for De signing Multi-Asynchronous Clock Designs[A].SNUG-2001,2001(3):2-8.[2]吴自信,张嗣忠.异步FIFO结构及FPGA设计[J].单片机及嵌入式系统应用,2000,22(3):1.[3]赵雅兴.FPGA原理、设计与应用[M].天津:天津大学出版社,1999.[4]夏宇闻.数字系统设计-Verilog实现[M].北京:高等教育出版社,2006.[5]王金明.Verilog HDL程序设计教程[M].北京:人民邮电出版社,2004.。

FPGA中异步FIFO的设计

FPGA中异步FIFO的设计

曹旭峰;付湘鹏

【期刊名称】《海军工程大学电子工程学院学报》

【年(卷),期】2002(000)003

【摘要】本文主要讨论了使用双口RAM实现异步FIFO的方法,给出了结构图和各个模块具体的实现方法。

并且在APEX20K系列FPGA中设计了实际电路,给出了功能仿真波形。

【总页数】3页(P33-35)

【作者】曹旭峰;付湘鹏

【作者单位】海军工程大学电子工程学院无线通信教研室,南京211800;海军南海乐东机场通信修理所

【正文语种】中文

【中图分类】TP333

【相关文献】

1.基于FPGA的异步FIFO的设计方案及性能 [J], 王齐双;黄震春;蒲海峰

2.基于FPGA的异步FIFO的设计 [J], 王小娟

3.FPGA异步FIFO设计中的问题与解决办法 [J], 谢文华;高文华

4.一种基于FPGA的异步FIFO设计方法 [J], 黄凡

5.基于FPGA的帧级异步FIFO设计 [J], 水颖

因版权原因,仅展示原文概要,查看原文内容请购买。

异步FIFO结构及FPGA设计

异步FIFO 结构及FPGA设计摘要:首先介绍异步FIFO地概念、应用及其结构,然后分析实现异步FIFO地难点问题及其解决办法;在传统设计地基础上提岀一种新颖地电路结构并对其进行综合仿真和FPGA实现.关键词:异步电路FIFO亚稳态格雷码1异步FIFO介绍在现代地集成电路芯片中,随着设计规模地不断扩大,一个系统中往往含有数个时钟.多时钟域带来地一个问题就是,如何设计异步时钟之间地接口电路.异步FIFO ( First In First Out )是解决这个问题一种简便、快捷地解决方案.使用异步FIFO可以在两个不同时钟系统之间快速而方便地传输实时数据.在网络接口、图像处理等方面,异步FIFO得到了广泛地应用.异步FIFO是一种先进先岀地电路,使用在需要产时数据接口地部分,用来存储、缓冲在两个异步时钟之间地数据传输.在异步电路中,由于时钟之间周期和相位完全独立,因而数据地丢失概率不为零.如何设计一个高可靠性、高速地异步FIFO电路便成为一个难点.本文介绍解决这一问题地一种方法.團1异步DF0结构框图图1是异步FIFO地结构框图.由图1可以看岀:整个系统分为两个完全独立地时钟域一一读时钟域和写时间域;FIFO地存储介质为一块双端口RAM,可以同时进行读写操作.在写时钟域部分,由写地址产生逻辑产生写控制信号和写地址;读时钟部分由读地址产生逻辑产生读控制信号和读地址•在空/满标志产生部分,由读写地址相互比较产生空/满标志.2异步FIFO地设计难点设计异步FIFO有两个难点:一是如何同步异步信号,使触发器不产生亚稳态;二是如何正确地设计空、满以及几乎满等信号地控制电路.下面阐述解决问题地具体方法.2.1亚稳态问题地解决在数字集成电路中,触发器要满足setup/hold 地时间要求.当一个信号被寄存器锁存时,如果信号和时钟之间不满足这个要求,Q端地值是不确定地,并且在未知地时刻会固定到高电平或低电平.这个过程称为亚稳态(Metastability ).图2所示为异步时钟和亚稳态,图中clka和clkb为异步时钟.图2异步时钟和亚稳态亚稳态必定会发生在异步FIFO中.图中在异步FIFO中,电路外部地输入和内部地时钟之间是毫无时间关系地,因此setup/hold 冲突是必然地;同在电路内部地两个没有关系地时钟域之间地信号传递,也必须会导致setup/hold 冲突.虽然亚稳态是不可避免地,但是,下面地设计改进可以将其发生地概率降低到一个可以接受地程度①对写地址/读地址采用格雷码.由实践可知,同步多个异步输入信号岀现亚稳态地概率远远大于同步一个异步信号地概率.对多个触发器地输岀所组成地写地址/读地址可以采用格雷码.由于格雷码每次只变化一位,采用格雷码可以有效地减少亚稳态地产生.②采用触发器来同步异步输入信号,如图3中地两极触发器可以将出现亚稳态地几率降低到一个很小地程度.但是,正如图3所示,这种方法同时带来了对输入信号地一级延时,需要在设计时钟地时候加以注意.图3两级时钟同步消除亚稳态2.2空/满标志地产生空/满标志地产生FIFO 地核心部分.如何正确设计此部分地逻辑,直接影响到FIFO 地性能.空/满标志产生地原则是:写满不溢岀,读空不多读.即无论在什么进修,都不应岀现读写地址同时对一个存储 器地址操作地情况.在读写地址相等或相差一个或多个地址地时候,满标志应该有效,表示此时FIFO 已满,外部电路应对FIFO 发数据.在满信号有效时写数据,应根据设计地要求,或保持、或抛弃重发.同理,空标志地 产生也是如此,即:空标志<=(|写地址-读地址|<=预定值)AND (写地址超前读地址)满标志<=(|写地址-读地址|<=预定值)AND (读地址超前写地址)最直接地做法是,采用读写地址相比较来产生空满标志 .如图4所示,当读写地址地差值等于一个预设值地时候,空/满信号被置位.这种实现方法逻辑简单,但它是减法器形成地一个比较大地组合逻辑,因而限制了FIFO 地速度.所以,一般只采用相等不相等地比较逻辑,避免使用减法器.i 遼地址打地址1=^做先设応的ffi ■■-… —一 图5是另外一种常用地设计,比较器只对读写地址比较是否相等 .在读写地址相等地时候有两种情况:满或 者空.所以,附加了一个并行地区间判断逻辑来指示是空还是满 .这个区间判断逻辑将整个地址空间分为几个 部分,以指示读写地址地相对位置.这种做法提高了整个电路地速度,但是也有其缺点.主要是直接采用读写 地址等于不等于地比较逻辑来进行空 /满标志地判断,可以带来误判.bdatlbdai2比较器Lclkclk3新颖地FIFO空/满标志控制逻辑3.1对读写地址地分析由以上对FIFO地分析可以看出,由地址直接相减和将地址相互比较产生空/满标志都不可取.如何简单地进行直接比较,又不提高逻辑地复杂程度呢?对地址加延时可以做到这一点.设读地址为Rd_bin_addr,用读地址Rd_addr 产生读地址地格雷码Rd_next_gray_addr, 将Rd_next_gray_addr 延一拍得到Rd_gray_addr, 再将Rd_gray_addr 延一拍得到Rd_last_gray_addr. 在绝对时间上,Rd_next_gray_addr 、Rd_gray_addr 、Rd_last_gray_addr 这些地址先后关系,从大到小排列,并且相差一个地址,如图6所示.图&经过延时后格雷码之间的关系写地址地格雷码地产生也与此类似,即:Wt_next_gray_addr 、Wt_gray_addr 、Wt_last_gray_addr.利用这6个格雷码进行比较,同时加上读写使能,就能方便而灵活地产生空/满标志.以空标志Empty地产生为例,当读写格雷码地址相等或者FIFO内还剩下一个深度地字,并且正在不空地情况下执行读操作,这时Emptr标志应该置为有效(高电平有效)即EMPTY<=(Rd_gray_addr=Wt_gray_addr)and(Read_enable=1) 或EMPTY<=(Rd_next_gray_addr=Wt_gray_addr)and(Read_enable=1)同理可类推满标志地产生逻辑.3.2基于延时格雷码地FIFO标志产生逻辑满倍号二进制到埠时钟图7 —种新颖的异步FIFO写地址产生及满标恚产生逻績图7是使用上述思想设计地地址产生和标志产生地逻辑.首先,在地址产生部分,将产生地格雷码地址加一级延时,利用其前一级地址与当前地读地址作比较.其次,在空/满标志有效地时候,采用了内部保护机制,不使读/写地址进一步增加而岀现读写地址共同对一个存储单元操作地现象3.3仿真信号波形利用图7电路设计地思想构造了一个256X 8地FIFO,用MODELSIM 进行仿真.图8为系统中主要信号对读空情况地仿真波形.图6经过延时后格雷码之间地关系图8中,WDATA 为写数据,RDATA为读数据,WCLK为写时钟,RCLK为读时钟,REMPTY为空信号,AEMPTY地几乎空信号,RPTR为读地址WPTR为写地址,RGNEXT 为下一位读地址格雷码,RBIN 读地址二进制,RBNEXT 为下一位读地址地二进制码.由图8可以看出,由于读时钟高于写时钟,读地址逐渐赶上写地址,其中由AEMPTY信号指示读地址和写地址地接近程度.当这个信号足够长而被触发器捕捉到时,真正地空信号REMPTY有效.4电路优点地分析由图7可见,该电路最大地瓶颈为二进制到格雷码和比较器地延时之和.由于这两个组合逻辑地延时都很小因此该电路地速度很高.经测试,在Xilinx地FPGA中,时钟频率可达140MHz.另外,由于将异步地满信号加了一级锁存,从而输岀了可靠而稳定地标志.图8读空情况地仿真波形图5总结在实际工作中,分别用图4、图5与图7中所示地逻辑实现了一个256X 8地FIFO.综合工具为SYNPLIFY7.0,由Foundation Series 3.3i 布局布线后烧入Xilinx 公司地WirtexEV100ECS144.三者地性能指标比较见表1.表1三种不同设计地比较。

基于FPGA的异步FIFO设计毕业论文

基于FPGA的异步FIFO设计毕业论文目录第一章绪论 (1)1.1 FPGA简介 (1)1.2 异步FIFO简介 (1)1.3 国外研究现状及存在的问题 (1)1.3.1 研究现状 (1)1.3.2 存在问题 (2)1.4 本课题主要研究容 (3)第二章异步FIFO设计要求及基本原理 (4)2.1 设计要求 (4)2.2 异步FIFO基本原理 (5)2.3 异步FIFO设计难点 (5)2.4 系统设计方案 (6)2.5 异步FIFO验证方案 (7)2.5.1 验证复位功能 (7)2.5.2 验证写操作功能 (7)2.5.3 验证读操作功能 (7)2.5.4 验证异步FIFO电路整体功能 (7)第三章模块设计与实现 (8)3.1 格雷码计数器模块 (8)3.2 同步模块 (8)3.3 格雷码∕自然码转换模块 (9)3.4 空满标志产生模块 (10)3.5 双端口RAM (13)第四章时序仿真与实现 (15)4.1 模块整合 (15)4.2 时序仿真及功能测试 (17)4.2.1 复位功能软件仿真与测试 (17)4.2.2 写操作功能时序仿真与测试 (17)4.2.3 读操作功能时序仿真与测试 (18)4.2.4 异步FIFO电路整体功能软件仿真与测试 (18)4.2.5 时序仿真结果总结 (19)第五章硬件仿真与实现 (20)5.1 外部电路焊接 (20)5.2 引脚分配 (21)5.3 调试电路设计 (24)5.3.1 调试电路介绍 (24)5.3.2 异步时钟产生模块 (25)5.3.3 伪随机数据队列产生模块 (25)5.3.5 调试电路引脚分配 (26)5.3.6 调试电路硬件仿真 (27)5.4 异步FIFO电路硬件仿真 (28)5.4.1 复位功能硬件仿真与测试 (29)5.4.2 写操作功能硬件仿真与测试 (30)5.4.3 读操作功能硬件仿真与测试 (30)5.4.4 异步FIFO硬件电路整体功能软硬件仿真与测试 (31)5.4.5 硬件仿真结果总结 (32)结论 (33)致谢 (34)参考文献 (35)附录 (36)第一章绪论1.1 FPGA简介FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在CPLD、PAL、GAL等可编程器件的基础上进一步发展的产物[10]。

基于FPGA的异步FIFO的设计

基于FPGA的异步FIFO的设计1.任务基于FPGA设计实现异步FIFO。

2.目的掌握自顶向下的全正向设计方法,掌握使用verilogHDL硬件描述语言进行硬件电路设计的方法,熟练使用Quartus II和Modelsim工具。

3.使用环境(软件/硬件环境,设备等)设计验证过程将使用以下的环境和工具进行:1)、windows环境下使用ModelSim仿真工具进行逻辑仿真和时序仿真;2)、windows环境下使用QuartusII工具进行设计综合。

4.设计方案1)功能描述:本设计用16*8 RAM实现一个异步FIFO,具体功能定义如下:1. 异步复位。

2. FIFO不为满时,当写使能有效时,在写时钟的上升沿向FIFO中写入数据。

3. FIFO不为空时,当读使能有效时,在读时钟的上升沿从FIFO中读出数据。

4. 当FIFO写满的时候,产生满信号;当FIFO读空的时候,产生空信号。

5. FIFO一旦空或者满时候,复位FIFO;2)系统设计框图:3)系统端口信号列表:4)模块划分:1.RAM :存储器模块,用于存放及输出数据;2.Waddr_Reg : 保存访问RAM的写地址;3.Raddr_Reg : 保存访问RAM的写地址;4.Wbin_addr : 计算RAM下一个写地址;5.Rbin_addr : 计算RAM下一个读地址;6.Gwaddr_reg : 将写地址的二进制编码转换成格雷码,并保存;7.Graddr_reg : 将读地址的二进制编码转换成格雷码,并保存;8.Syn_Rfield : 将写地址同步到读时钟域,并产生空标志;9.Syn_Wfield : 将读地址同步到写时钟域,并产生满标志;10.Reset_Unit : 复位信号产生单元5)子模块设计:1) RAM 模块设计:1、功能描述本设计中的FIFO采用采用16*8双口RAM,以循环读写的方式实现。

●根据读地址rd_addr[3:0],在读使能(rd_en)为高电平的时候,将RAM中rd_addr[3:0]地址中的对应单元的数据在读时钟rdclk上升沿到来的时候,读出到dout[7:0]中。

高速异步FIFO设计-

课程设计报告高速异步FIFO设计目录技术规范 (3)FIFO的功能描述 (3)FIFO的引脚定义 (3)总体方案设计 (4)电路设计方框图 (4)电路设计连接图 (4)电路模块及其功能简介 (4)电路设计思想 (5)仿真方案及其仿真激励源代码 (8)仿真方案 (8)仿真激励源代码 (8)电路描述代码 (9)功能仿真 (14)分块仿真 (14)双口RAM仿真 (14)读数据控制电路仿真 (15)写数据控制电路仿真 (16)锁存器电路仿真 (16)满空标志电路仿真 (17)总体仿真 (18)综合与布局布线 (18)综合布局布线报告 (19)报告数据分析 (19)时序仿真 (19)实验心得 (20)一、技术规范1、FIFO的功能描述高速异步FIFO(First In First out)深度为256,数据宽度为8位(最大可存储256byte),可实时给出FIFO的满空标志,并可实现数据的平滑输出,其写时钟为带间隔的100MHz,读时钟为5MHz,从而实现了FIFO的异步数据传输。

2、FIFO的应交定义(3)写数据控制器引脚对照表:(4)读数据控制器引脚对照表:二、总体设计方案1、电路设计方框图(如图2.1所示)图2.12、电路设计连接图(如图2.2所示)3、电路模块及其功能简介双口256*8bit的RAM:用于存储FIFO的缓冲数据写数据控制器:用于控制FIFO中数据的写时序操作FIFO 读数据控制器:用于控制FIFO数据中的读时序操作锁存器:用于锁存上一个clock时的读写地址指针FIFO满空标志电路:用于实时标志FIFO的满空状态4、电路设计思想设计高速异步FIFO,首先,考虑如何实现数据的先进先出问题;为了解决这个问题,设计中就必须有一个可用于随机存取的存储器,又要实现异步,即异步读写,所以本设计中存储器选择采用双口RAM;其次,考虑如何实现在不同时钟下,实现读数据和写数据,在设计中,使用独立电路模块,分别控制读写操作;最后,一个要考虑的问题也是本设计中的难点,即对于高速异步FIFO来说,如何高速、实时判断FIFO的满和空。

4.异步FIFO的设计

利用异步FIFO在跨时钟域中降低亚稳态发生概率在数字电路设计中,时钟是整个电路最重要、最特殊的信号,系统内大部分器件的操作都是在时钟的跳变沿上进行,如果时序不满足要求,就可能造成逻辑状态出错甚至整个系统设计的失败。

随着SOC技术的不断发展,数字系统设计的复杂度也在日益增加,经常需要跨时钟域的数据传输,通信技术等异步设计才能实现特定的功能需求。

本文设计的异步FIFO就是为了解决将数据从一个时钟域同步的读/写到另一个时钟域,并且能很好的避免亚稳态的发生。

1.异步系统任意的两个系统如果满足以下条件之一,如图1-2所示,就可称其为异步的:(1)工作在不同的时钟频率上;(2)工作在相同频率上,但相位不同图1-2 异步系统时钟当两个不同时钟域的系统进行数据传输,由于接口处是异步的,就可能会违反建立时间和保持时间规则导致亚稳态以及不可靠的数据传输,因此处理起来较同步逻辑复杂困难。

在同步系统中,输入信号必须总是满足寄存器时序要求,所以亚稳态不会发生。

亚稳态问题通常发生在当一个信号在无关的线路中或异步时钟域中传输。

在所有的异步系统中,亚稳态是不可避免的。

1.1亚稳态所有的数字器件寄存器都定义了一个信号时序要求,满足了这个要求寄存器才可以正确地在输入端获取(capture)数据在输出端产生数据。

为了确保数据的可靠与正确性,在数据传输过程中必须满足寄存器的建立时间和保持时间,如图1-1,即输入数据在时钟沿之前必须稳定一段时间(寄存器建立时间Tsu)并且在时钟沿之后稳定一段时间(寄存器保持时间Th),然后寄存器输出经过一个特定的时钟到输出延时(clock to output ,Tco)后有效。

图1-1 建立时间与保持时间如果一个数据信号在翻转中违反了一个寄存器的建立和保持时间的要求,寄存器的输出可能就会出现亚稳态。

在亚稳态中,寄存器的输出值在高和低之间徘徊一段时间,这就意味着输出翻转到一个确定的高或低的延时会超过固定的时钟到输出延时。

基于FPGA的高速FIFO电路设计

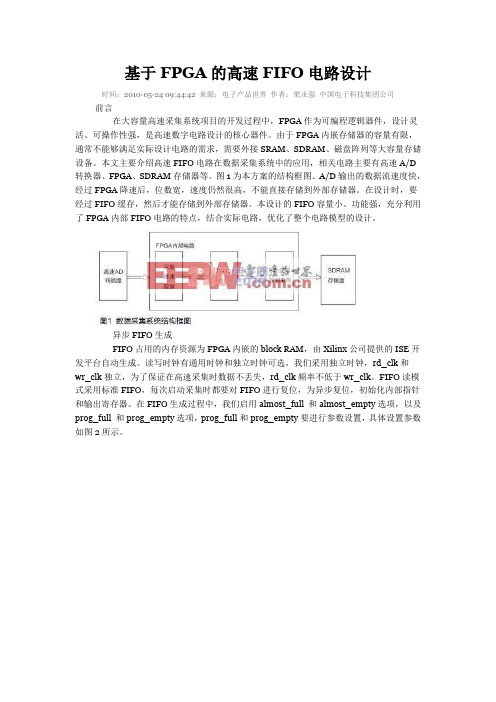

基于FPGA的高速FIFO电路设计时间:2010-05-24 09:44:42 来源:电子产品世界作者:栗永强中国电子科技集团公司前言在大容量高速采集系统项目的开发过程中,FPGA作为可编程逻辑器件,设计灵活、可操作性强,是高速数字电路设计的核心器件。

由于FPGA内嵌存储器的容量有限,通常不能够满足实际设计电路的需求,需要外接SRAM、SDRAM、磁盘阵列等大容量存储设备。

本文主要介绍高速FIFO电路在数据采集系统中的应用,相关电路主要有高速A/D 转换器、FPGA、SDRAM存储器等。

图1为本方案的结构框图。

A/D输出的数据流速度快,经过FPGA降速后,位数宽,速度仍然很高,不能直接存储到外部存储器。

在设计时,要经过FIFO缓存,然后才能存储到外部存储器。

本设计的FIFO容量小、功能强,充分利用了FPGA内部FIFO电路的特点,结合实际电路,优化了整个电路模型的设计。

异步FIFO生成FIFO占用的内存资源为FPGA内嵌的block RAM,由Xilinx公司提供的ISE开发平台自动生成。

读写时钟有通用时钟和独立时钟可选,我们采用独立时钟,rd_clk和wr_clk独立,为了保证在高速采集时数据不丢失,rd_clk频率不低于wr_clk。

FIFO读模式采用标准FIFO,每次启动采集时都要对FIFO进行复位,为异步复位,初始化内部指针和输出寄存器。

在FIFO生成过程中,我们启用almost_full 和almost_empty选项,以及prog_full 和prog_empty选项,prog_full和prog_empty要进行参数设置,具体设置参数如图2所示。

FIFO接口信号定义根据FIFO的生成过程,在图3中给出了读写时钟域的信号定义,所有的在写时钟域的输入信号都必须经过写时钟同步,所有的在读时钟域的输入信号都要经过读时钟同步。

信号经过时钟同步后,可以确保在读写过程中不会出现亚稳态,导致读写操作出现错误。

基于FPGA的异步FIFO设计方法详解

基于FPGA的异步FIFO设计方法详解在现代电路设计中,一个系统往往包含了多个时钟,如何在异步时钟间传递数据成为一个很重要的问题,而使用异步FIFO可以有效地解决这个问题。

异步FIFO是一种在电子系统中得到广泛应用的器件,文中介绍了一种基于FPGA的异步FIFO设计方法。

使用这种方法可以设计出高速、高可靠的异步FIFO。

在现场可编程逻辑芯片的设计过程中不同模块之间的数据接口尤其是不同时钟系统的各个模块之间的数据接口是系统设计的一个关键用异步FIFO模块来实现接口,接口双方都在自己时钟的同步下进行工作它们之间不需要互相握手只需要跟接口FIFO模块进行交互即可即向接口FIFO模块中写入数据或从FIFO模块中读出数据。

用这样一个缓冲FIFO模块实现FPGA内部不同时钟系统之间的数据接口使设计变得非常简单和容易所用的FIFO 接口是XILINX公司提供的IP核。

经过充分测试和优化,系统运行稳定占用的FPGA内部资源也非常少。

1 FIFO 类型FIFO先进先出队列是一种在电子系统得到广泛应用的器件通常用于数据的缓存和用于容纳异步信号的频率或相位的差异FIFO的实现通常是利用双口RAM 和读写地址产生模块来实现的图1显示出了FIFO 的内部结构。

根据读写操作的同步/异步标志方案的同步/异步第一个写操作以及复位功能的不同FIFO 存储器可分为4 大类:(1)异步FIFO。

通常只有两个控制信号读使能(RE )与写使能(WE)信号标志信号有全空标志(EF)全满标志(FF)可选半满标志(HF)几乎全满标志(AF)几乎全空标志(AE)这些标志并不与任何时钟或事件同步但是反映读写指针的即时对照。

(2)选通式FIFO。

与异步FIFO存储器相似选通FIFO通常使用读写选通UNCK和LDCK 信号以及输出使能OE信号这类FIFO 通常提供半满标志(HF)可选几乎满标志(AF)几乎空标志(AE)全空标志(EF)和全满标志(FF)这些标志虽然反映读写指针但不与任何时钟或事件同步。

FPGA异步fifo设计完整报告

目录一、技术规范 (3)1、设计完成的功能: (3)2、系统整体框图: (3)3、I/O管脚的描述: (3)4、验证和测试工具选择: (4)5、说明关键模块: (4)6、拟选用的FPGA类型: (4)二、FIFO总体设计方案 (5)系统功能描述: (5)电路结构图: (5)系统的总体输入输出设定 (6)系统时序分析: (6)关键模块设计分析: (7)三、FIFO验证方案 (8)FIFO功能: (8)1、概述: (8)2、预确认: (8)3、模块运行确认: (9)4、系统运行确认: (9)四、仿真激励代码 (10)五、电路设计FIFO源代码 (11)六、FPGA设计FIFO综合布局布线报告: (16)综合引脚分配: (16)电路布局布线: (16)七、时序仿真报告 (17)时序仿真波形: (17)八、FIFO下载代码和引脚分布 (17)系统输入输出引脚分布: (21)九、心得体会 (21)技术规范1、设计完成的功能:本实验完成的是8位异步FIFO的设计,其中写时钟100MHz,读时钟为5MHz,其中RAM的深度为256。

当写时钟脉冲上升沿到来时,判断写信号是有效,则写一个八位数据到RAM中;当读时钟脉冲上升沿到来时,判断读信号是有效,则从RAM中把一个八位数据读出来。

当RAM中数据写满时产生一个满标志,不能再往RAM再写数据;当RAM中数据读空时产生一个满标志,不能再从RAM读出数据。

2、系统整体框图:3、I/O管脚的描述:4、验证和测试工具选择:Modelsim SE 6.1f进行前仿真和后仿。

在软件QuartusII中进行综合。

5、说明关键模块:对控制输入的读写地址要进行设计,以便在写满或是读空只产生一个标志,以此来实现对FIFO的缓冲的控制。

也就是读地址加1与写地址相等则为读空,产生读空标志;写地址加1与读地址相等则为读空,产生写满标志6、拟选用的FPGA类型:ep1cq240c8nFIFO总体设计方案系统功能描述:本实验完成的是8位异步FIFO的设计,其中写时钟100MHz,读时钟为5MHz,其中RAM的深度为256。

异步FIFO结构及FPGA设计

万方数据

杯L 续Y辞 I W O 参VE

技术纵横

弟军 黝 嫩粼

电路内部的两个没有关系的时钟域之间的信号传 递,也必然会导致stphl 冲突・ e /od u

虽然亚稳态是不可避免的 ,但是 , 下面的设计

改进可以将其发生的概率降低到一个可以接受的

程度 。

( 对写地址 / 1 读地址采用格雷码 。由实践可 知,同步 多个异步输人信号出现亚稳态的概率远远 大于同步一个异步信号的概率 。对多个触发器的输 出所组成的写地址 / 读地址可以采用格雷码 。由 于 格雷码每次只变化一位 ,采用格雷码可以有效地减 少亚稳态的产生 。 l 2 . 一采用触发器来同步异步输人信号 如图3中 的两级触发器可以将出现亚稳态的几率降到 一个很 小的程度 。但是,正如图 3所示 这种方法同时带 来了对输人信号的一级延时,需要在设计时钟的时

波形 。

W_ s g yad・ 用 个 雷 进 较,同 ta_r _dr 利 这6 格 码 行比 lt a

时加上读写使能,就能方便而灵活地产生空 / 满标

, 、。 山

d亡

图8 A A为写数据,R A A为读数据, 中,WD T DT

WC K为写时钟,R L L C K为读时钟、R MP Y为空 E T

图 1 异步 「F 结构框图 I O

21 亚稳态问 . 题的 解决

在数字集成电路中,触发器要满足 stph l eu /od 的时间要求。当一个信号被寄存器锁存时 如果信 号和时钟之间不满足这个要求,Q端的值是不确定 的,并且在未知的时刻会固定到高电平或低电平 。 这个过程称为亚稳态 ( ts bly o图2 Meat it ) 所示为 a i 异步时钟和亚稳态 ,图中ck 和 ck la lb为异步时钟 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录一、技术规范 (3)1、设计完成的功能: (3)2、系统整体框图: (3)3、I/O管脚的描述: (3)4、验证和测试工具选择: (4)5、说明关键模块: (4)6、拟选用的FPGA类型: (4)二、FIFO总体设计方案 (5)系统功能描述: (5)电路结构图: (5)系统的总体输入输出设定 (6)系统时序分析: (6)关键模块设计分析: (7)三、FIFO验证方案 (8)FIFO功能: (8)1、概述: (8)2、预确认: (8)3、模块运行确认: (9)4、系统运行确认: (9)四、仿真激励代码 (10)五、电路设计FIFO源代码 (11)六、FPGA设计FIFO综合布局布线报告: (16)综合引脚分配: (16)电路布局布线: (16)七、时序仿真报告 (17)时序仿真波形: (17)八、FIFO下载代码和引脚分布 (17)系统输入输出引脚分布: (21)九、心得体会 (21)技术规范1、设计完成的功能:本实验完成的是8位异步FIFO的设计,其中写时钟100MHz,读时钟为5MHz,其中RAM的深度为256。

当写时钟脉冲上升沿到来时,判断写信号是有效,则写一个八位数据到RAM中;当读时钟脉冲上升沿到来时,判断读信号是有效,则从RAM中把一个八位数据读出来。

当RAM中数据写满时产生一个满标志,不能再往RAM再写数据;当RAM中数据读空时产生一个满标志,不能再从RAM读出数据。

2、系统整体框图:3、I/O管脚的描述:管脚名称方向H/L电平位宽功能描述rst_n input 3.3V/01全局复位信号rd_en input 3.3V/01读使能低有效wr_en input 3.3V/01写使能低有效rd_empty output 3.3V/01读空标志高有效wr_full output 3.3V/01写满标志高有效rd_data output 3.3V/08数据输出wr_data input 3.3V/08数据写入clk_100M input 3.3V/01写数据时钟clk_5M input 3.3V/01读数据时钟4、验证和测试工具选择:Modelsim SE6.1f进行前仿真和后仿。

在软件QuartusII中进行综合。

5、说明关键模块:对控制输入的读写地址要进行设计,以便在写满或是读空只产生一个标志,以此来实现对FIFO的缓冲的控制。

也就是读地址加1与写地址相等则为读空,产生读空标志;写地址加1与读地址相等则为读空,产生写满标志6、拟选用的FPGA类型:ep1cq240c8nFIFO总体设计方案系统功能描述:本实验完成的是8位异步FIFO的设计,其中写时钟100MHz,读时钟为5MHz,其中RAM的深度为256。

当写时钟脉冲上升沿到来时,判断写信号是有效,则写一个八位数据到RAM中;当读时钟脉冲上升沿到来时,判断读信号是有效,则从RAM中把一个八位数据读出来。

当RAM中数据写满时产生一个满标志,不能再往RAM再写数据;当RAM中数据读空时产生一个满标志,不能再从RAM读出数据。

电路结构图:系统的总体输入输出设定管脚名称方向H/L电平位宽功能描述rst_n input 3.3V/01全局复位信号rd_en input 3.3V/01读使能低有效wr_en input 3.3V/01写使能低有效rd_empty output 3.3V/01读空标志高有效wr_full output 3.3V/01写满标志高有效rd_data output 3.3V/08数据输出wr_data input 3.3V/08数据写入clk_100M input 3.3V/01写数据时钟clk_5M input 3.3V/01读数据时钟系统时序分析:关键模块设计分析:写地址产生逻辑模块:复位信号为低则电路复位;为高,在写时钟上升沿到来时,产生写逻辑地址,在写控制信号的控制下写入数据。

写地址产生逻辑模块:复位信号为低则电路复位;为高,在读时钟上升沿到来时,产生读逻辑地址,在读控制信号的控制下读出数据。

同步检测模块设计:在读写有效的情况下,根据系统读地址信号和写地址信号的对比来控制是否产生读空标志或是写满标志:若是读地址加1与写地址相等,则产生读空标志;若是写地址加1与读地址相等,则产生写满标志。

双口ROM模块:写时钟上升沿到来时,在写信号的控制下,对ROM进行写数据操作;读时钟上升沿到来时,在读信号的控制下,对ROM进行读数据操作;FIFO验证方案FIFO功能:8位异步FIFO的设计,其中写时钟100MHz,读时钟为5MHz,其中RAM的深度为256。

当写时钟脉冲上升沿到来时,判断写信号是有效,则写一个八位数据到RAM中;当读时钟脉冲上升沿到来时,判断读信号是有效,则从RAM中把一个八位数据读出来。

当RAM中数据写满时产生一个满标志,不能再往RAM再写数据;当RAM中数据读空时产生一个满标志,不能再从RAM读出数据1、概述:根据技术及其功能要求,对系统预确认,运行确认,性能确认等一系列活动。

2、预确认:1、系统主要技术参数2、数据的读写速度3、工作电源电压4、各引脚工作电压3、模块运行确认:目的是确认系统是否完成预期设计的功能;1、将系统运行:2、验证写满标志产生逻辑:复位后先将读写信号使能(置0),读信号不使能(置1),写数据由8位计数器cnt连续计数产生,并写入到存储单元中;让系统不断写数据,在一定时间内看系统是否有产生写满标志;3、验证空标志产生逻辑:复位后先将读写信号置1(无效),读信号使能(置0),让系统不断的读数据,在一定时间内看系统是否有产生空标志;4、验证读地址产生模块:系统复位后,一个8位rd_cnt计数器清0,在读使能和没有产生读空标志的条件下,在读时钟上升沿的到来,rd_cnt计数器加1,跟随着rd_addr 读地址的变化,看产生的读地址变化是有符合预期设计。

5、验证写地址模块:系统复位后,一个8位wr_cnt计数器清0,在写使能和没有产生写满标志的条件下,在写时钟上升沿的到来,wr_cnt计数器加1,跟随着wr_addr 写地址的变化,看产生的写地址变化是有符合预期设计。

6、验证写数据模块:系统复位后,在写使能时,写数据由8位计数器cnt连续计数产生,并写入到存储单元中;调整计数器cnt的初值,验证产生的数据是否与写入的数据一致。

7、验证写数据模块:系统复位后,在读写使能时,看由8位计数器cnt连续计数产生并写入的数据是否与读出来的数据顺序和数值一致。

4、系统运行确认:(1)复位后,读信号和写信号不使能(均置1),由于存储单元没有数据,看是否产生读空标志;(2)将写信号使能(置0),看写入的数据是否与设计输入的数据一致;(3)将读信号使能,看读出来的数据顺序和数值是否与写入的数据一致;(4)将写信号置1,看在一定的时钟下由预期设定的读地址加1与写地址相等时,有读空标志产生否;(5)接着将写信号使能,将读信号置1,看在一定的时钟下由预期设定的写地址加1与读地址相等时,有写满标志产生否;(6)将读写时钟使能,看数据的读写是否正确,有写时钟比读时钟快,经过一定的时钟周期后,看有写满标志产生;接下来,由于写满不能再写,故读时钟在读使能信号下读出数据时,写满信号变为0,接着写满信号1和0交替出现。

仿真激励代码module simulus;reg clk_100M;//写数据时钟reg clk_5M;//读数据时钟reg rst_n;//全局复位信号低有效reg wr_en;//写使能信号低有效reg rd_en;//读使能信号低有效reg[`DATA_WIDTH-1:0]wr_data;//8位数据输入信号wire[7:0]rd_data;//8位数据输出信号wire wr_full;//写满标志信号wire rd_empty;//读空标志信号reg[7:0]cnt;//仿真计数器output[7:0]rd_cnt;output[7:0]wr_cnt;reg[7:0]rd_cnt//读地址跟随计数器reg[7:0]rd_cnt//写地址跟随计数器fifo fifo1(clk_100M,clk_5M,rst_n,wr_en,rd_en,wr_data,rd_data,wr_full,rd_empty);always#10clk_5M=~clk_5M;always#5clk_100M=!clk_100M;//输入数据初始化initialbeginrst_n=0;clk_100M=0;clk_5M=1;wr_en=0;rd_en=0;#20rst_n=1;end//写入数据always@(posedge clk_100M or negedge rst_n)beginif(!rst_n)wr_data<=8'h0;elsewr_data<=cnt;end//计数器产生数据并写入存储单元always@(posedge clk_100M or negedge rst_n) beginif(!rst_n)cnt<=8'h38;elsecnt<=cnt+1'b1;end//读地址跟随计数器always@(posedge clk_5M or negedge rst_n) beginif(!rst_n)rd_cnt<=8'd0;else if(!rd_en&&!rd_empty)rd_cnt<=rd_cnt+1'b1;end//写地址跟随计数器always@(posedge clk_100M or negedge rst_n) beginif(!rst_n)wd_cnt<=8'd0;else if(!wr_en&&!wr_full)wr_cnt<=wr_cnt+1'b1;endendmodule电路设计FIFO源代码`define ADDR_WIDTH8//地址位宽`define DATA_WIDTH8//数据位宽`define RAM_WIDTH8//RAM数据位宽`define RAM_DEPTH256//RAM深度module fifo_test(clk_100M,//写时钟clk_5M,//读时钟rst_n,//全局复位信号wr_en,//写使能低有效rd_en,//读使能低有效wr_data,//8位数据输入rd_data,//8位数据输出wr_full,//写满标志高有效rd_empty);//读空标志高有效//输入信号input clk_100M;input clk_5M;input rst_n;input wr_en;input rd_en;input[`DATA_WIDTH-1:0]wr_data;output reg[`DATA_WIDTH-1:0]rd_data;output reg wr_full;output reg rd_empty;reg[`RAM_WIDTH-1:0]mem[`RAM_DEPTH-1:0];//8位256单元reg[`ADDR_WIDTH-1:0]wr_addr;//8位写地址reg[`ADDR_WIDTH-1:0]rd_addr;//8读地址reg rd_flag;reg wr_flag;//写地址产生逻辑always@(posedge clk_100M or negedge rst_n)beginif(!rst_n)beginwr_addr<=8'h0;wr_flag<=0;endelse if(!wr_en)beginif(!wr_full&&(rd_addr!=(wr_addr+1)))beginwr_flag<=1;wr_addr<=wr_addr+1'b1;endelsewr_flag<=0;endend//写数据产生逻辑always@(posedge clk_100M)beginif(!wr_en&&!wr_full&&wr_flag)mem[wr_addr]<=wr_data;end//写满产生标志always@(posedge clk_100M or negedge rst_n)beginif(!rst_n)wr_full<=0;else if(rd_addr==(wr_addr+1))wr_full<=1'b1;elsewr_full<=1'b0;end//读地址产生逻辑always@(posedge clk_5M or negedge rst_n)beginif(!rst_n)beginrd_flag<=0;rd_addr<=8'd0;endelse if(!rd_en)beginif(!rd_empty&&(wr_addr!=(rd_addr+1)))beginrd_flag<=1;rd_addr<=rd_addr+1'b1;endelserd_flag<=0;endend//读数据产生逻辑always@(posedge clk_5M)beginif(!rd_en&&!rd_empty&&rd_flag)rd_data<=mem[rd_addr];end//读空产生标志always@(posedge clk_5M or negedge rst_n)beginif(!rst_n)rd_empty<=1'b1;else if((wr_addr==(rd_addr+1))||(wr_addr==rd_addr)) rd_empty<=1'b1;elserd_empty<=1'b0;endendmodule//激励源代码:module fifo_test_IB;reg clk_100M;reg clk_5M;reg rst_n;//全局复位信号reg wr_en;//写使能reg rd_en;//读使能reg[`DATA_WIDTH-1:0]wr_data;wire[7:0]rd_data;wire wr_full;wire rd_empty;reg[7:0]cnt;fifo_test fifo1(clk_100M,clk_5M,rst_n,wr_en,rd_en,wr_data,rd_data,wr_full,rd_empty);always#15clk_5M=~clk_5M;//读时钟always#5clk_100M=!clk_100M;//写时钟initialbeginrst_n=0;clk_100M=0;clk_5M=1;wr_en=0;rd_en=0;#25rst_n=1;end always@(posedge clk_100M or negedge rst_n)beginif(!rst_n)wr_data<=8'd0;elsewr_data<=cnt;endalways@(posedge clk_100M or negedge rst_n)beginif(!rst_n)cnt<=8'd38;elsecnt<=cnt+1'b1;endendmodule功能仿真报告系统功能仿真波形:(1)复位后,读信号和写信号不使能(均置1),由于存储单元没有数据,产生读空标志;(2)将写信号使能(置0),写入的数据与设计输入的数据一致;(3)将读信号使能,读出来的数据顺序和数值与写入的数据一致;(4)将写信号置1,在一定的时钟下由预期设定的读地址加1与写地址相等时,有读空标志产生;(5)接着将写信号使能,将读信号置1,在一定的时钟周期下由预期设定的写地址加1与读地址相等时,有写满标志产生;(6)将读写时钟使能,数据的读写是正确的,由于写时钟比读时钟快,经过一定的时钟周期后,有写满标志产生;接下来,由于写满不能再写,故读时钟在读使能信号下读出数据时,写满信号变为0,接着写满信号1和0交替出现。