FPGA课程设计报告

fpga在线课程设计

fpga 在线课程设计一、教学目标本课程旨在通过FPGA(现场可编程门阵列)在线课程设计,让学生掌握FPGA的基本概念、原理及其在数字电路设计中的应用。

通过本课程的学习,学生将能够:1.知识目标:理解FPGA的工作原理、结构及编程方法;掌握FPGA在数字信号处理、通信、嵌入式系统等领域的应用。

2.技能目标:学会使用FPGA设计工具进行电路图绘制和编程;具备分析、解决实际工程问题的能力。

3.情感态度价值观目标:培养学生对电子技术的兴趣,提高创新意识和团队合作能力,使其意识到FPGA技术在现代社会中的重要性。

二、教学内容本课程的教学内容主要包括以下几个部分:1.FPGA基本概念:介绍FPGA的定义、发展历程、特点及应用领域。

2.FPGA结构和工作原理:讲解FPGA的内部结构、工作原理及其与外部电路的接口。

3.FPGA编程方法:介绍FPGA的编程语言、开发工具及编程过程。

4.FPGA应用案例分析:分析FPGA在数字信号处理、通信、嵌入式系统等领域的具体应用。

5.实践环节:安排学生进行FPGA设计实践,巩固所学知识,提高实际操作能力。

三、教学方法为了提高教学效果,本课程将采用以下教学方法:1.讲授法:讲解FPGA的基本概念、原理及其应用,使学生掌握相关理论知识。

2.案例分析法:通过分析实际案例,让学生了解FPGA在各个领域的应用,提高学生的实践能力。

3.实验法:安排实践环节,让学生亲自动手进行FPGA设计,培养学生的动手能力和创新意识。

4.讨论法:学生进行小组讨论,分享学习心得,提高团队合作能力。

四、教学资源为了支持本课程的教学,我们将准备以下教学资源:1.教材:选用权威、实用的FPGA教材,为学生提供系统的理论知识。

2.参考书:提供相关的FPGA技术参考书籍,丰富学生的知识体系。

3.多媒体资料:制作精美的PPT、教学视频等多媒体资料,提高学生的学习兴趣。

4.实验设备:准备FPGA开发板、编程器等实验设备,为学生提供实践操作的机会。

FPGA设计的报告课程设计

FPGA课程设计实验报告实验一:设计一个可控的100进制可逆计数器一、实验要求用DE2-115开发板下载。

(1)计数器的时钟输入信号周期为200ns。

(2)以十进制形式显示。

(3)有一个复位端clr和两个控制端plus和minus,在这些控制信号的作用clr plus minus 功能0 ××复位为01 1 0 递增计数1 0 1 递减计数1 1 1 暂停计数二、关键词可控制、可逆、100进制、复位、暂停、递增、递减三、内容摘要module updown_count(qout,reset,clk,plus,minus);output[7:0] qout;/*定义一个8位的输出,其目的是低四位和高四位分别表示计数器的个位和十位。

*/input clk,plus,minus,reset;//定义四个输入,时钟,加计数,减计数和清零reg[7:0] qout;//qout的数据类型为寄存器型always @(posedge clk)//当clk上升沿到来时执行一遍下列程序beginif(!reset) qout<=0;//当reset为低电平时,计数器执行清零功能,否则跳过elsebegincase({minus,plus})//case语句模块,包含加,减和暂停四个模块2'b10:if (qout[3:0]==0)//判断个位是否为零,若不为零,跳到个位减一beginqout[3:0]<=9;//给个位赋值if(qout[7:4]==0) qout[7:4]<=9;//判断十位是否为零,并且给十位赋值elseqout[7:4]<=qout[7:4]-1;//由于个位赋9,相当于向十位借一,因而十位减一endelseqout[3:0]<=qout[3:0]-1;//个位减一/*这一部分是减计数模块,其思路是:首先判断个位是否为零,若为零,则执行后面的程序,个位直接赋9,并且十位减一;否则个位减一*/ 2'b01:if (qout[3:0]==9)//判断个位是否为9,否则跳到个位加一beginqout[3:0]<=0;//若上面个位为9判断成立,则给个位赋值if(qout[7:4]==9) qout[7:4]<=0;//判断十位是否为9,若为9,则赋0elseqout[7:4]<=qout[7:4]+1;//若十位不为9,十位加一endelseqout[3:0]<=qout[3:0]+1;//个位加一/*这一部分是加计数模块,首先判断个位是否为9,若不为9,个位加1;否侧,再判断十位是否为9,若为9,十位赋0,否侧十位加1。

fpga技术课程设计

fpga技术课程设计一、教学目标本课程的教学目标分为三个维度:知识目标、技能目标和情感态度价值观目标。

1.知识目标:通过本课程的学习,学生将掌握FPGA技术的基本概念、原理和应用,了解FPGA技术的发展趋势及其在电子工程领域的广泛应用。

2.技能目标:学生将能够熟练使用FPGA开发工具,如ISE、Vivado等,掌握FPGA编程语言,如VHDL、Verilog等,并具备一定的FPGA硬件设计和验证能力。

3.情感态度价值观目标:培养学生对FPGA技术的兴趣和热情,使其认识到了解和掌握FPGA技术对于个人职业发展的重要性,树立正确的科学态度和创新精神。

二、教学内容教学内容将根据课程目标进行选择和,确保内容的科学性和系统性。

教学大纲如下:1.FPGA技术概述:介绍FPGA的基本概念、工作原理和分类,以及FPGA技术的发展历程和趋势。

2.FPGA硬件描述语言:讲解VHDL和Verilog两种主流的FPGA硬件描述语言,包括基本语法、语句结构和常用库函数。

3.FPGA设计与验证:介绍FPGA设计的基本流程,包括设计输入、综合、布局布线和仿真验证等环节。

4.FPGA应用案例:分析典型的FPGA应用案例,如数字信号处理、网络通信、嵌入式系统等,使学生了解FPGA技术在实际工程中的应用。

5.FPGA开发工具:介绍FPGA常用的开发工具,如ISE、Vivado等,以及这些工具的使用方法和技巧。

三、教学方法为了激发学生的学习兴趣和主动性,本课程将采用多种教学方法,包括讲授法、讨论法、案例分析法和实验法等。

1.讲授法:教师通过讲解、演示和举例等方式,向学生传授FPGA技术的基本概念、原理和应用。

2.讨论法:学生针对FPGA技术的相关话题进行讨论,培养学生的思考能力和团队协作精神。

3.案例分析法:分析典型的FPGA应用案例,使学生了解FPGA技术在实际工程中的应用,提高学生的实践能力。

4.实验法:安排学生进行FPGA实验,让学生亲自动手操作,巩固所学知识,提高实际操作能力。

基于fpga的简单课程设计

基于fpga的简单课程设计一、课程目标知识目标:1. 学生能理解FPGA的基本概念,掌握FPGA的基本结构和原理;2. 学生能描述数字电路的基本组成,了解数字电路在FPGA中的应用;3. 学生能掌握Verilog HDL语言的基本语法和编程方法,并运用其设计简单的数字电路。

技能目标:1. 学生能运用FPGA设计软件进行电路设计和仿真;2. 学生能通过Verilog HDL编程实现基本的数字电路功能;3. 学生能对设计的FPGA电路进行调试和优化,提高电路性能。

情感态度价值观目标:1. 培养学生积极主动探索新知识、新技术,增强其对电子工程领域的兴趣;2. 培养学生具备团队协作精神,学会与他人共同解决问题,提高沟通与表达能力;3. 培养学生具备工程素养,关注工程伦理,认识到科技发展对社会的重要意义。

课程性质:本课程为实践性课程,注重培养学生的动手能力和创新能力。

学生特点:学生具备一定的电子技术基础,对FPGA技术有一定了解,具备基本的计算机操作能力。

教学要求:教师需结合学生特点和课程性质,采用任务驱动、案例教学等方法,引导学生主动参与课堂实践,提高学生的实际操作能力。

同时,注重培养学生的自主学习能力和团队合作精神,提高学生的综合素质。

通过课程目标的分解与实施,使学生在知识、技能和情感态度价值观方面取得具体的学习成果。

二、教学内容1. 数字电路基础- 数字逻辑基础:逻辑门、逻辑函数、逻辑代数;- 组合逻辑电路:编码器、译码器、多路选择器、算术逻辑单元;- 时序逻辑电路:触发器、计数器、寄存器。

2. FPGA基本原理- FPGA结构:逻辑单元、查找表、寄存器、布线资源;- FPGA编程原理:配置、重配置、上电配置;- FPGA设计流程:设计输入、综合、布局布线、仿真、下载。

3. Verilog HDL编程- 基本语法:模块、端口、信号、数据类型;- 语句结构:顺序语句、并行语句;- 基本数字电路设计:组合逻辑电路、时序逻辑电路、状态机。

FPGA课程设计报告

FPG课程设计—256个8位计数器技术规范一、实现功能:用一个8×256的单口RAM完成256个8位计数器,计数器的初值分别为0-255,时钟频率为10MHz,计数器计数频率为5/256MHz。

具体功能描述如下:1、分频模块:时钟频率为10MHz,要实现计数器计数频率为5/256MHz,将其时钟频率进行2分频送入。

每来一个时钟,计数器计一个数。

第一个时钟来时,第一个计数器计1,此时,此计数器中的值变为1,其余的计数器中的值不变,以此类推,直到第256个时钟来时,第256个计数器计1,计数器中的值255变为0,以此类推,完成256个8位计数器,得到计数器计数频率即为5/256MHz。

2、8x256的单口RAM模块:定义一块内存为8x256的单口RAM,只有一条地址线,读写共用一个地址单元,当使能信号we=1时,写有效,可以将数据写入RAM,当使能信号we=0,读有效,可以将RAM中的值输出。

3、写模块:当时能信号we=1时,写有效,当clk的上升沿到来时,可以将数据写入寄存器,在时钟的上升沿和reset的下降沿时,如果reset=0,则地址addr=0,计数器a=0;否则,如果使能信号we=1,地址addr递加,当addr大于255时,addr=0,计数器a=a+1,将addr+a送入数据输入data_in.。

二、系统I/O管脚的描述:三、拟选用的FPGA类型:ep1cq240c8n总体设计方案一、整体设计方案我构想了如下两个总体设计方案:第一个总体设计方案:将10MHz的时钟clk_in通过分频器进行2分频送入系统clk,触发条件是clk的上升沿,这就可以实现计数器计数频率为5/256MHz。

由于是单口RAM,所以只有一条地址线,要么只能写入数据,要么只能读出数据。

因此,我先将所有的寄存器清零,将0—255这256个计数器初值分别送入256个寄存器,此时采用一个加法计数器完成。

然后每来一个时钟clk,计数器中的值计1,同时地址加1,即第一个寄存器的0变成1,地址加到第二个寄存器,以此类推,完成256个8位计数器的计数,并且将计数器的值读出。

fpga课程设计总结

fpga课程设计总结一、教学目标本课程的教学目标是使学生掌握FPGA的基本原理、设计和应用。

具体来说,知识目标包括:了解FPGA的基本结构和工作原理;掌握FPGA的编程语言和设计方法;熟悉FPGA在数字信号处理、嵌入式系统等方面的应用。

技能目标包括:能够使用FPGA设计简单的数字系统;能够使用FPGA进行嵌入式系统设计;能够进行FPGA的编程和调试。

情感态度价值观目标包括:培养学生的创新意识和团队合作精神;使学生认识到FPGA技术在现代科技中的重要地位和应用价值。

二、教学内容根据课程目标,教学内容主要包括FPGA的基本原理、设计和应用。

具体包括以下几个方面:1. FPGA的基本结构和工作原理;2. FPGA的编程语言和设计方法;3. FPGA在数字信号处理、嵌入式系统等方面的应用;4. FPGA的设计工具和实验方法。

三、教学方法为了达到课程目标,我们将采用多种教学方法,包括讲授法、讨论法、案例分析法和实验法等。

通过这些方法,我们将引导学生从不同角度理解和掌握FPGA技术和应用。

具体来说:1. 讲授法:通过讲解FPGA的基本原理、设计和应用,使学生掌握相关知识;2. 讨论法:通过分组讨论和课堂讨论,引导学生深入思考和理解FPGA技术;3. 案例分析法:通过分析实际案例,使学生了解FPGA在实际应用中的优势和局限;4. 实验法:通过FPGA实验,使学生掌握FPGA的设计和编程方法,提高实际操作能力。

四、教学资源为了支持教学内容和教学方法的实施,我们将选择和准备以下教学资源:1. 教材:选用权威、实用的教材,为学生提供系统、全面的学习材料;2. 参考书:推荐一些与FPGA相关的参考书,拓展学生的知识视野;3. 多媒体资料:制作课件、视频等多媒体资料,提高课堂教学效果;4. 实验设备:准备FPGA实验设备,为学生提供实践操作的机会。

五、教学评估本课程的评估方式包括平时表现、作业和考试等。

平时表现主要评估学生的课堂参与、提问和讨论等情况,占总评的20%。

FPGA课程设计实验报告

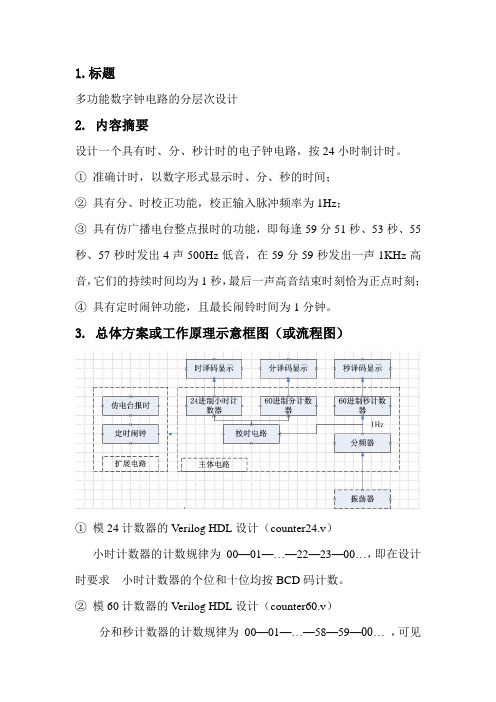

1.标题多功能数字钟电路的分层次设计2. 内容摘要设计一个具有时、分、秒计时的电子钟电路,按24小时制计时。

①准确计时,以数字形式显示时、分、秒的时间;②具有分、时校正功能,校正输入脉冲频率为1Hz;③具有仿广播电台整点报时的功能,即每逢59分51秒、53秒、55秒、57秒时发出4声500Hz低音,在59分59秒发出一声1KHz高音,它们的持续时间均为1秒,最后一声高音结束时刻恰为正点时刻;④具有定时闹钟功能,且最长闹铃时间为1分钟。

3. 总体方案或工作原理示意框图(或流程图)①模24计数器的Verilog HDL设计(counter24.v)小时计数器的计数规律为00—01—…—22—23—00…,即在设计时要求小时计数器的个位和十位均按BCD码计数。

②模60计数器的Verilog HDL设计(counter60.v)分和秒计数器的计数规律为00—01—…—58—59—00… ,可见个位计数器从0~9计数,是一个10进制计数器;十位计数器从0~5计数,是一个六进制计数器。

可以先分别设计一个十进制计数器模块(counter10.v)和一个六进制计数器模块(counter6.v),然后将这两个模块组合起来,构成六十进制计数器。

4. 顶层逻辑电路图组成及原理简单叙述仿真波形如下:分析结论:经仿真波形分析①走时正常;②能〝校时〞〝校分〞;③整点报时;④时段控制到位。

功能完全符合设计要求,可以下载。

5. 对应各模块功能仿真波形(数据分析)分析及结论1、小时计时模块:仿真波形:当小时的高四位为0、1时,小时的低四位为九时,在下一个时钟的上跳延来了之后,高四位加一;当小时的高四位为2,同时低四位为3时,小时的高低四位都清零。

实现从00到23的循环计数。

2、分钟计时模块:仿真波形:当分钟的高四位为0、1、2、3、4时,小时的低四位为九时,在下一个时钟的上跳延来了之后,高四位加一;当分钟的高四位为5时,同时低四位为9时,分钟的高低四位都清零,实现从00到59的循环计数。

fpga课程设计报告

第一部分 EDA技术的仿真1、奇偶校验位产生器1.1奇偶校验位的技术要求奇偶校验是通信中常用的一种数据校验方式,试设计一个奇偶校验位产生器,根据输入字节(8位)产生相应的奇偶校验位(1的个数为奇数时输出低电平,即奇校验位为1)和偶校验位(1的个数为偶数时输出高电平,即偶校验位为1)1.2奇偶校验位的原理通过计算数据中“1”的个数是奇数还是偶数来判断数据的正确性。

在被校验的数据后加一位校验位或校验字符用作校验码实现校验。

其生成方法是:奇校验:确保整个被传输的数据中“1”的个数是奇数个,即载荷数据中“1”的个数是奇数个时校验位填“0”,否则填“1”;偶校验:确保整个被传输的数据中“1”的个数是偶数个,即载荷数据中“1”的个数是奇数个时校验位填“1”,否则填“0”。

1.3奇偶校验位的功能及其仿真波形奇偶校验位的功能具体见下表所示:输入8位的二进制序列奇校验位even偶校验位odd1 1 0 1 0 0 1 1 1 0 1 0 0 0 1 1 1 0 0 1其具体实现程序如下所示:module parity(data,odd,even);input [0:7]data;output odd,even;assign odd=^data;assign even=~odd;endmodule根据程序我们得到如下的仿真波形:图1 奇偶校验位仿真波形中国计量学院信息工程学院课程设计报告P.22、十六位数据选择器2.1数据选择器的原理在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器,数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号。

在数据选择器中,我们设定一个控制输入端ENA ,当ENA=1时,电路不能工作,输出Y=0;而当ENA=0时,电路才处于工作状态。

由于我们设计的是16选1数据选择器,因而其有4个数据控制端,即S0,S1,S2,S3,根据这4个控制端的状态有选择性的输出。

fpga简单课程设计

fpga简单课程设计一、教学目标本课程旨在让学生了解FPGA(现场可编程门阵列)的基本概念、特性和应用,掌握FPGA的基本编程和设计方法,培养学生的创新意识和实践能力。

知识目标:使学生了解FPGA的基本原理、结构和工作原理,熟悉FPGA的编程语言和开发环境,掌握FPGA的基本设计方法和流程。

技能目标:培养学生使用FPGA相关软件进行简单程序设计和调试的能力,使学生具备分析和解决实际问题的能力。

情感态度价值观目标:培养学生对电子技术的热爱,激发学生创新和实践的兴趣,培养学生的团队合作意识和综合素质。

二、教学内容本课程的教学内容主要包括FPGA的基本概念、FPGA的编程语言和开发环境、FPGA的基本设计方法和流程、以及FPGA在实际应用中的案例分析。

具体包括以下几个部分:1.FPGA的基本概念:介绍FPGA的定义、特点和应用领域。

2.FPGA的编程语言:介绍VHDL和Verilog这两种常用的FPGA编程语言。

3.FPGA的开发环境:介绍FPGA开发过程中所使用的软件工具,如ISE、Altera等。

4.FPGA的基本设计方法:介绍FPGA设计的流程,包括硬件描述语言的编写、逻辑综合、布局布线、编程和调试等。

5.FPGA的应用案例:分析FPGA在实际应用中的案例,如数字信号处理、嵌入式系统等。

三、教学方法为了提高教学效果,本课程将采用多种教学方法,如讲授法、讨论法、案例分析法和实验法等。

1.讲授法:通过教师的讲解,使学生了解和掌握FPGA的基本概念、原理和方法。

2.讨论法:引导学生针对实际问题进行思考和讨论,培养学生的创新意识和解决问题的能力。

3.案例分析法:分析FPGA在实际应用中的案例,使学生了解FPGA的应用领域和设计方法。

4.实验法:让学生动手进行FPGA的设计和调试,提高学生的实践能力和动手能力。

四、教学资源为了支持本课程的教学,我们将准备以下教学资源:1.教材:选用国内外优秀的FPGA相关教材,为学生提供系统的理论知识和实践指导。

《FPGA系统设计》实验报告》时序逻辑电路的设计

《FPGA系统设计》实验报告》时序逻辑电路的设计

一、设计任务

分别设计并实现锁存器、触发器的VHDL模型。

二、设计过程

1、同步锁存器:

同步锁存器是指复位和加载功能全部与时钟同步,复位端的优先级较高。

下图为同步锁存器的VHDL程序及模型:

2、异步锁存器:

异步锁存器,是指复位与时钟不同步的锁存器。

下图为同步锁存器的VHDL程序及模型:

3、D触发器:

D触发器是最常用的触发器。

下图为简单D触发器的VHDL 模型:

4、T触发器:

T触发器的特点是在时钟沿处输出信号发生翻转。

按

照有无复位、置位信号以及使能信号等,T触发器也有多种类型。

下图为带异步复位T触发器的VHDL模型:

5、JK触发器:

JK触发器中,J、K信号分别扮演置位、复位信号的角色。

为了更清晰的表示出JK触发器的工作过程,以下给出JK触发器的真值表(如表1所示)。

表1 JK触发器真值表

按照有无复位、置位信号,常见的JK触发器也有多种类型,下图带异步复位(clr)、置位(prn)的JK触发器的VHDL模型:

三.总结

本次实验中较为顺利,在第一次课的时间内我就已经完成了必做实验与选作实验。

在实验的过程中,在防抖电路处有了较大的困难。

由于仿真中不存在此问题,在实际操作中参数选择时遇到了一定的困难。

在反复比对效果之后,我

确定了电路的参数,实现了防抖功能。

通过这次实验,我对时钟脉冲、计数器等有了更加深入的认识与理解。

FPGA课程设计报告

F PG A课程设计报告(实现多功能数字钟)专业班级: 07通信2班******学号:************时间:2009.12.30一、标题:设计多功能数字钟控制电路二、任务书:用MAX+PLU SⅡ软件及Verilog HDL语言设计一个多功能的数字钟,包括有时、分、秒的计时,以及校时(对小时、分钟和秒能手动调整以校准时间)、正点报时(每逢整点,产生“嘀嘀嘀嘀-嘟”,4短一长的报时音)等附加功能。

三、关键词:24进制、60进制、正点报时、校时、数字钟四、总体方案:多功能数字钟控制电路框图是由三部分组成的,即秒分时控制电路、整点报时控制电路、时段控制电路。

用Verilog HDL硬件描述语言完成编译和仿真。

五、原理框图如下:↓↓↓六、Verilog HDL硬件描述语言编写的功能模块:/*秒计数器m60*/module m60(M,CP60M,CPM,RD);output [7:0]M;output CP60M;input CPM;input RD;reg [7:0]M;wire CP60M;always@(negedge RD or posedge CPM)beginif(!RD)begin M[7:0]<=0;endelsebeginif((M[7:4]==5)&&(M[3:0]==9))beginM[7:0]<=0;endelsebeginif(M[3:0]==9)beginM[3:0]<=0;if(M[7:4]==5)begin M[7:4]<=0;endelse M[7:4]<=M[7:4]+1;endelse M[3:0]<=M[3:0]+1;endendendassign CP60M=~(M[6]&M[4]&M[3]&M[0]); endmodule/*分计数器m60*/module m60(M,CP60M,CPM,RD);output [7:0]M;output CP60M;input CPM;input RD;reg [7:0]M;wire CP60M;always@(negedge RD or posedge CPM) beginif(!RD)begin M[7:0]<=0;endelsebeginif((M[7:4]==5)&&(M[3:0]==9))beginM[7:0]<=0;endelsebeginif(M[3:0]==9)beginM[3:0]<=0;if(M[7:4]==5)begin M[7:4]<=0;endelse M[7:4]<=M[7:4]+1;endelse M[3:0]<=M[3:0]+1;endendendassign CP60M=~(M[6]&M[4]&M[3]&M[0]); endmodule/*小时计数器m24*/module m24(H,CPH,RD);output [7:0]H;input CPH,RD;reg [7:0]H;always@(negedge RD or posedge CPH) beginif(!RD) H[7:0]<=0;elsebeginif((H[7:4]==2)&&(H[3:0]==3))beginH[7:0]<=0;endelsebeginif(H[3:0]==9)begin H[3:0]<=0;H[7:4]<=H[7:4]+1;endelse H[3:0]<=H[3:0]+1;endendendendmodule/*秒分时控制计数器xiaoshi2*/module xiaoshi2(CPM,CPH,CPS,CP60M,CP60S,SWM,SWH);output CPM,CPH;input SWM,SWH;input CPS,CP60S,CP60M;reg CPM,CPH;always@(SWM or SWH or CPS or CP60S or CP60M)begincase({SWM,SWH})2'b01: begin CPM<=CPS;CPH<=CP60M;end2'b10: begin CPM<=CP60S;CPH<=CPS;enddefault: begin CPM<=CP60S;CPH<=CP60M;end endcaseendendmodule/*时段控制器sdkz*/module sdkz(h,sk);input [7:0]h;output sk;reg sk;always@(h)beginif((h<=5)||(h>=19))sk<=1;elsesk<=0;endendmodule/*报时计数器baoshi*/module baoshi(m6,m4,m3,m0,s6,s4,s3,s0,dy,gy,bshi); input m6,m4,m3,m0,s6,s4,s3,s0,dy,gy;output bshi;wire bm;reg bshi;assign bm=m6&m4&m3&m3&m0&s6&s4&s0; always@(bm or s3 or dy or gy)beginif(bm&s3)bshi<=gy;else if(bm)bshi<=dy;elsebshi<=0;endendmodule七:各模块原理图及仿真波形:24进制原理图:60进制原理图:电路原理图:时段控制:报时:1、秒计数器仿真波形2、分计数器的仿真波形3、小时计数器的仿真波形4、秒分时控制电路的仿真波形5、时段控制的仿真波形6、报时器的仿真波形八、顶层文件及仿真波形顶层文件的仿真波形:九:选用ACEX1K芯片中的EP1K30TC144-3型号,对芯片管脚号的分配如下:十:课程设计结论:此次课程设计通过最终下载及编译可实现以上功能,在七段显示器上可实现秒、分计数器60进制,时计数器24进制显示,以及调节CLK1、CLK2的频率可使计数器上数字延时显示。

FPGA设计的报告课程设计

FPGA课程设计实验报告实验一:设计一个可控的100进制可逆计数器一、实验要求用DE2-115开发板下载。

(1)计数器的时钟输入信号周期为200ns。

(2)以十进制形式显示。

(3)有一个复位端clr和两个控制端plus和minus,在这些控制信号的作用clr plus minus 功能0 ××复位为01 1 0 递增计数1 0 1 递减计数1 1 1 暂停计数二、关键词可控制、可逆、100进制、复位、暂停、递增、递减三、内容摘要module updown_count(qout,reset,clk,plus,minus);output[7:0] qout;/*定义一个8位的输出,其目的是低四位和高四位分别表示计数器的个位和十位。

*/input clk,plus,minus,reset;//定义四个输入,时钟,加计数,减计数和清零reg[7:0] qout;//qout的数据类型为寄存器型always @(posedge clk)//当clk上升沿到来时执行一遍下列程序beginif(!reset) qout<=0;//当reset为低电平时,计数器执行清零功能,否则跳过elsebegincase({minus,plus})//case语句模块,包含加,减和暂停四个模块2'b10:if (qout[3:0]==0)//判断个位是否为零,若不为零,跳到个位减一beginqout[3:0]<=9;//给个位赋值if(qout[7:4]==0) qout[7:4]<=9;//判断十位是否为零,并且给十位赋值elseqout[7:4]<=qout[7:4]-1;//由于个位赋9,相当于向十位借一,因而十位减一endelseqout[3:0]<=qout[3:0]-1;//个位减一/*这一部分是减计数模块,其思路是:首先判断个位是否为零,若为零,则执行后面的程序,个位直接赋9,并且十位减一;否则个位减一*/ 2'b01:if (qout[3:0]==9)//判断个位是否为9,否则跳到个位加一beginqout[3:0]<=0;//若上面个位为9判断成立,则给个位赋值if(qout[7:4]==9) qout[7:4]<=0;//判断十位是否为9,若为9,则赋0elseqout[7:4]<=qout[7:4]+1;//若十位不为9,十位加一endelseqout[3:0]<=qout[3:0]+1;//个位加一/*这一部分是加计数模块,首先判断个位是否为9,若不为9,个位加1;否侧,再判断十位是否为9,若为9,十位赋0,否侧十位加1。

fpga课程设计报告彩灯实验

fpga课程设计报告彩灯实验一、课程目标知识目标:1. 学生能理解FPGA的基本原理和结构,掌握彩灯实验相关的硬件描述语言(HDL)基础;2. 学生能描述数字电路设计的基本流程,并运用FPGA设计简单的数字电路;3. 学生掌握彩灯实验的原理,能够解释彩灯显示背后的逻辑控制过程。

技能目标:4. 学生能够运用所学知识,设计并实现一个基于FPGA的彩灯控制电路;5. 学生通过实际操作,提高问题解决能力和实验操作技能,包括电路调试和故障排查;6. 学生能够利用FPGA设计软件进行电路设计和仿真,并完成硬件的实现和测试。

情感态度价值观目标:7. 学生通过实验探究,培养对电子工程领域的兴趣,增强创新意识和实践能力;8. 学生在小组合作中,提升团队协作能力和沟通技巧,理解集体智慧的重要性;9. 学生能够在实验过程中,形成良好的工程伦理观念,认识到技术对社会发展的积极影响和责任。

二、教学内容本课程教学内容围绕FPGA的原理与应用,结合彩灯实验项目,进行以下组织和安排:1. FPGA基础知识:- 数字电路设计基础;- FPGA原理与结构;- 硬件描述语言(HDL)入门。

2. 彩灯实验原理与设计:- 彩灯显示原理;- FPGA在彩灯控制中的应用;- 彩灯控制电路设计流程。

3. 教学大纲与进度安排:- 第一周:FPGA基本原理学习,了解硬件描述语言;- 第二周:数字电路设计基础,学习彩灯显示原理;- 第三周:彩灯控制电路设计,进行FPGA编程与仿真;- 第四周:电路调试与测试,优化设计方案。

4. 教材关联内容:- 教材第3章:“数字电路设计基础”;- 教材第4章:“FPGA原理与结构”;- 教材第5章:“硬件描述语言(HDL)应用”;- 教材第6章:“数字电路设计实例”。

5. 实践环节:- 彩灯控制电路设计实践;- FPGA编程与仿真;- 电路调试与故障排查。

三、教学方法针对FPGA课程设计报告彩灯实验,采用以下多样化的教学方法,以激发学生的学习兴趣和主动性:1. 讲授法:- 对FPGA基本原理、数字电路设计基础和硬件描述语言(HDL)等理论知识进行系统讲解,为学生奠定扎实的理论基础。

FPGAverilog课程设计报告

FPGA verilog课程设计报告一、教学目标本课程旨在通过FPGA Verilog的学习,让学生掌握数字电路设计的基本原理和方法,学会使用Verilog硬件描述语言进行数字电路设计和仿真。

具体目标如下:1.理解FPGA的基本原理和结构。

2.掌握Verilog语言的基本语法和编程技巧。

3.熟悉数字电路的设计方法和流程。

4.能够使用Verilog语言编写简单的数字电路模块。

5.能够进行FPGA的配置和编程。

6.能够使用FPGA开发工具进行数字电路的仿真和测试。

情感态度价值观目标:1.培养学生的创新意识和团队合作精神。

2.增强学生对新技术的敏感性和学习兴趣。

3.培养学生对工程实践的热爱和责任感。

二、教学内容本课程的教学内容主要包括FPGA的基本原理和结构、Verilog语言的基本语法和编程技巧、数字电路的设计方法和流程。

具体安排如下:第1-2课时:FPGA的基本原理和结构1.FPGA的定义和发展历程。

2.FPGA的内部结构和组成。

3.FPGA的配置和编程方法。

第3-4课时:Verilog语言的基本语法和编程技巧1.Verilog语言的基本数据类型和操作符。

2.Verilog语言的逻辑表达式和语句。

3.Verilog语言的模块结构和参数传递。

第5-6课时:数字电路的设计方法和流程1.数字电路的设计原则和技巧。

2.数字电路的设计流程和步骤。

3.数字电路的仿真和测试方法。

三、教学方法本课程采用讲授法、案例分析法和实验法相结合的教学方法。

1.讲授法:通过讲解和演示,让学生掌握FPGA和Verilog的基本知识和技巧。

2.案例分析法:通过分析具体的数字电路设计案例,让学生熟悉设计方法和流程。

3.实验法:通过动手实验,让学生亲手配置FPGA、编写Verilog代码并进行仿真测试,提高学生的实际操作能力。

四、教学资源1.教材:《FPGA Verilog设计与实践》。

2.参考书:《数字电路与FPGA设计入门》、《Verilog HDL入门与提高》。

FPGA课程设计报告

课程设计开课学期: 2014年—2015年下学期课程名称:FPGA课程设计学院:信息科学与工程学院专业:集成电路设计与集成系统班级:集成1201班学号:20121221077姓名:蔚任课教师:涛2015 年 7 月 21 日基于FPGA的数字钟设计摘要本文介绍一种利用现场可编程逻辑器件FPGA产生多功能数字钟的设计方案。

数字钟是采用数字电路实现对时、分、秒数字显示的计时装置,是人们日常生活中不可少的必需品。

本设计采用EDA技术,以硬件描述语言Verilog为系统逻辑描述手段设计文件,在Quartus II工具软件环境下,由各个基本模块共同构建了一个基于FPGA的数字钟。

系统由时钟模块、控制模块、计时模块、数据译码模块、显示以及报时模块组成。

经编译和仿真所设计的程序,在可编程逻辑器件上下载验证。

开发板采用5CSEMA5F31C6N。

本次设计的多功能数字钟,具有时、分、秒的数码管显示功能,以24小时循环计数,具有整点报时功能,并有由按键输入进行数字钟的校时、清零、启停功能。

关键词:可编程逻辑器件 FPGA Verilog 数字钟 EDA技术AbstractThis paper introduces a kind of based on field programmable logic device FPGA design of multi-function digital clock, the digital clock is used in digital circuits, and seconds digital display timing device is in people's daily life necessities.This design using EDA technology, hardware description language Verilog logic system description method of design documents, in the Quartus II software environment, by all the basic modules together to build a a FPGA based digital clock.System consists of the clock module, control module, time module, data decoding module, display and broadcast module composition. Program after compilation and simulation design, programmable logic device to download verification. Development board using the multi-function digital clock 5CSEMA5F31C6N. this design, with time, points, the second digital tube display, to a 24-hour cycle count, with the whole point timekeeping function and input by the key of the school of digital clock, clear, open and stop function.Key words: programmable logic device FPGA Verilog Digital cloc EDA Technology目录前言 (1)第一章多功能数字钟概述 (2)1.1 数字钟的构成 (2)1.3 计时电路 (3)1.4 异步清零电路 (4)1.5 校时、校分功能电路 (4)第二章 FPGA简介 (5)2.1 现场可编程逻辑门阵列FPGA (5)2.2 FPGA简介 (6)2.3 Quartus II软件简介 (6)第三章设计方案 (7)第四章设计实现 (9)4.1 顶层模块 (9)4.2 新建工程项目 (9)4.3 选择芯片 (10)4.4 子模块 (12)4.4.1 分频器 (12)4.4.2 控制器和计数器 (13)4.4.3 显示器 (16)4.5 元件封装 (21)4.6 引脚的绑定和设置 (21)4.7 之后再进行一次编译运行。

fpga技术课程设计

fpga技术课程设计一、课程目标知识目标:1. 理解FPGA的基本概念、结构与工作原理,掌握FPGA在数字系统设计中的应用。

2. 学会使用硬件描述语言(如VHDL/Verilog)进行数字电路设计,并能将设计成功地在FPGA上实现。

3. 掌握FPGA设计流程,包括设计输入、综合、布局布线、仿真和下载等环节。

技能目标:1. 能够运用所学知识,设计简单的数字系统,具备基本的FPGA编程与调试能力。

2. 培养学生动手实践和问题解决能力,提高团队协作和沟通能力,形成良好的工程素养。

情感态度价值观目标:1. 培养学生对FPGA技术及数字系统设计的兴趣,激发学生的求知欲和创新精神。

2. 强化质量意识,培养学生严谨、细致的工作态度,形成良好的职业道德观念。

3. 增强学生的国家意识,认识到FPGA技术在我国电子产业发展中的重要性,激发学生的爱国情怀。

本课程针对高年级学生,结合学科特点,注重理论与实践相结合,以培养学生的实际操作能力和创新精神为核心。

课程目标具体、可衡量,旨在让学生在学习过程中明确学习成果,为后续教学设计和评估提供依据。

二、教学内容1. FPGA基本原理:包括FPGA的结构、工作原理、配置与编程方法等,对应教材第1章内容。

2. 硬件描述语言基础:以VHDL/Verilog为例,讲解基本语法、数据类型、运算符和基本电路描述方法,对应教材第2章内容。

3. 数字电路设计与实现:介绍组合逻辑电路和时序逻辑电路的设计方法,以及FPGA上的实现过程,对应教材第3章内容。

4. FPGA设计流程:讲解设计输入、综合、布局布线、仿真和下载等环节的操作方法和注意事项,对应教材第4章内容。

5. 实践项目:结合教材附录中的实例,进行FPGA编程与调试实践,提高学生的动手能力。

6. 课程拓展:介绍FPGA在人工智能、大数据等领域的应用,激发学生的创新意识。

教学内容安排和进度如下:1. 第1周:FPGA基本原理及配置方法学习。

大学生fpga课程设计

大学生fpga课程设计一、课程目标知识目标:1. 掌握FPGA的基本原理、结构及其在设计中的应用;2. 学习数字电路设计的基本流程,理解硬件描述语言(HDL)的编程规范;3. 熟悉FPGA开发环境及相关软件工具的使用;4. 了解FPGA在信号处理、通信等领域的应用案例。

技能目标:1. 能够运用HDL语言进行数字电路设计和仿真;2. 掌握FPGA硬件编程和配置方法,具备基本的FPGA调试能力;3. 能够根据实际需求,设计并实现简单的FPGA应用系统;4. 提高团队协作和项目实践能力,具备分析和解决实际问题的能力。

情感态度价值观目标:1. 培养学生对FPGA技术及其应用的兴趣,激发学生的学习热情和探索精神;2. 培养学生严谨的科学态度,养成良好的实验习惯和工程素养;3. 增强学生的创新意识,鼓励学生积极参与科技竞赛和实践活动;4. 培养学生的团队合作精神,提高沟通与交流能力。

本课程针对大学生FPGA课程设计,结合课程性质、学生特点和教学要求,明确了具体、可衡量的课程目标。

通过本课程的学习,使学生能够掌握FPGA技术的基本知识和技能,培养创新意识和实践能力,为今后从事相关领域的研究和工作打下坚实基础。

二、教学内容1. FPGA基本原理与结构:介绍FPGA的发展历程、基本组成、工作原理及其优势特点,结合教材第一章内容,使学生建立FPGA的基本概念。

2. 硬件描述语言(HDL):讲解VHDL和Verilog HDL的基本语法、编程规范以及设计流程,结合教材第二章内容,使学生掌握HDL语言的使用方法。

3. FPGA开发环境及工具:学习FPGA开发环境(如ISE、Quartus等)的安装与配置,介绍常用软件工具的功能和操作方法,结合教材第三章内容,使学生熟悉FPGA开发流程。

4. 数字电路设计实例:分析并实践简单的数字电路设计实例,如组合逻辑电路、时序逻辑电路等,结合教材第四章内容,提高学生的实际设计能力。

5. FPGA应用系统设计:学习FPGA在信号处理、通信等领域的应用案例,结合教材第五章内容,使学生了解FPGA在实际工程中的应用。

FPGA课程设计实验报告

FPGA课程设计实验报告1. 引言本报告是针对FPGA课程设计实验的实验结果进行总结和分析。

该实验旨在通过设计一个FPGA应用电路,加深对FPGA的理论知识的理解,并提高对FPGA设计流程的掌握能力。

本实验采用Verilog硬件描述语言进行FPGA设计。

2. 实验目的本实验的主要目的有以下几点: - 通过设计一个FPGA应用电路,提高对FPGA的理论知识的理解。

- 熟悉FPGA设计流程,掌握使用Verilog语言进行FPGA设计的方法。

- 掌握FPGA设计的仿真、综合和下载的流程。

- 提高对FPGA设计中时序约束的理解和处理能力。

3. 实验环境和工具本实验的实验环境和工具如下: - FPGA开发板:Xilinx Spartan-6 - FPGA设计工具:Xilinx ISE Design Suite - 仿真工具:Xilinx ISIM4. 实验设计本实验设计了一个简单的FPGA应用电路,实现了一个4位计数器。

该计数器能够从0递增到15,然后重新从0开始计数。

计数器的递增频率可通过外部开关调节,同时采用七段数码管显示当前计数器的值。

4.1 电路结构实验设计的电路结构如下所示:电路结构图电路结构图该电路包含以下模块: - 时钟模块:用于提供递增计数器的时钟信号。

- 计数器模块:实现了一个4位计数器,并能够从0递增到15。

- 控制模块:用于控制外部开关的输入,并将结果输出到七段数码管的控制端口。

- 七段数码管模块:用于将计数器的值以七段数码管的形式显示出来。

4.2 Verilog代码根据电路结构图,我们编写了如下的Verilog代码:module counter(input wire clk,input wire reset,output wire [6:0] seg,output wire seg_en);reg [3:0] count;always @(posedge clk or posedge reset)beginif (reset)count <= 4'b0000;else if (count == 4'b1111)count <= 4'b0000;elsecount <= count + 1;endassign seg = count;assign seg_en = 1'b1;endmodule5. 实验过程5.1 仿真在进行实际FPGA设计之前,我们首先对设计的Verilog代码进行仿真,以验证其功能的正确性。

FPGA课程设计报告

FPGA课程设计报告学部:信息科学与技术学部专业:通信工程班级:10级1班学号:姓名:万洁指导老师:祝宏合作伙伴:张紫君一.《任务书》:实验一 100进制的可逆计数器(11——12周)实验二交通灯控制系统(15周)实验三多功能数字钟系统(14-15周)二.实验书写格式:一:题目要求二:程序代码三:操作步骤及运行结果截图四:心得体会三.实验附录:一:老师提供的资源二:关于实验所用EP4CE115F29板的简介实验一 100进制的可逆计数器一、设计一个可控的100进制可逆计数器,要求用实验箱下载。

(1)计数器的时钟输入信号周期为200ns。

(2)以十进制形式显示。

(3)有一个复位端clr和两个控制端plus和minus,在这些控制信号的作用下,计数器具有复位、增或减计数、暂停功能。

二、程序如下:module keni100(CLR,CLK,PLUS,MINUS,OUT);——图在出现的输入界面内输入程序,点击file→save as,在出现的对话框中点击Yes,然后在出现的new project Wizard对话框中点击next,在Family&Device Settings 对话框中选择如下图所示的选项,在选择第三方软件的对话框中的选项选为none后点击next,在随后出现的对话框中,点击finish。

设置完成。

——图2、点击project→Set as Top-Level Entity,指向所输入的文件。

3、点击Processing→Start→Start Analysis & Synthesis。

——图4、点击File→New出现上面第一步时出现的对话框,如图,选择Vector Waveform File。

5、点击View→Utility Windows→Node Finder,在出现的对话框中点击List,如下图所示——图选择所需要的节点,将其拉到后面的Name栏中,并设置输入数据6、选择End Time:点击Edit→End Time,设置参数,如下图所示——图7、输入参数的数据设置完成后,保存,仿真图形如下图所示:——图8.点击Assigment→Settings,在出现的对话框(如图所示)中,选择Simulator Settings,在Simulation mode中选择Functional,进行功能编译。

数字电子技术FPGA设计及其报告

数字电子技术课程设计报告题目:基于FPGA的数字频率计设计学年:2010-2011学期:二专业:电气工程及其自动化班级:学号:姓名:指导教师:目录1 设计任务与要求 (1)2 系统设计总体方案 (1)3 各模块电路具体实现 (2)3.1 时钟分频模块 (2)3.2 时序控制模块 (3)3.3 计数模块 (3)3.4 锁存模块 (5)3.5 显示译码模块 (6)4 设计测试结果 (8)5 总结 (8)附录 (9)1 设计任务与要求本课题要完成的设计任务与要求如下:(1)、设计一个六位数的数字频率计.测量范围要求在0~999999Hz;(2)、需要设计五个模块电路,分别为:计数模块,译码显示模块,时序控制模块,分频模块,锁存模块;(3)、应用FPGA器件,通过QuartusⅡ软件(EP2C5T144C8)以原理图输入方式设计系统电路,根据设计要求选择可编程逻辑器件作为目标器件,应用QuarterⅡ软件进行系统开发设计.2 系统设计总体方案根据设计任务与要求,数字频率计系统主要有:计数模块、锁存模块、译码显示模块、时序控制模块、分频模块等电路模块组成,其系统组成框图如图2—1所示.图2—1 数字频率计系统设计组成框图各模块电路设计的主要思路和具体方案如下:(1)、计数模块:本模块主要实现六位数码管的十进制数的计数.可以通过常用的数字计数器来设计.如:74HC192、74161、74HC390等.本设计模块需要六个常用的计数器来实现个位到十万位的计数. ;(2)、锁存模块:本模块主要实现对计数值的锁存功能.可以选用常用的触发器.如D 触发器、RS触发器;或者,可以选用常用的锁存器来实现该功能;(3)、译码显示模块:本模块主要实现对计数模块的测量值以十进制数来显示,本系统选用共阴极数码管来作为显示器件,这里我们选用74HC138作为译码驱动器件;(4)、时序控制模块:本模块主要实现系统内部的各个模块协的调工作,主要产生三个控制信号:一秒钟的计数控制信号、锁存器的开启信号、计数器清零信号;(5)、分频模块:本模块主要实现将50MHz的时钟信号转换成1Hz的时钟信号.这里选用Verilog硬件描述语言来设计该模块电路.3 各模块电路具体实现3.1 时钟分频模块根据整个系统中各模块电路的需求,本模块主要实现将EDA实验板上50MHz晶振产生的时钟脉冲经过分频得到1Hz的时钟信号,考虑到应用触发器或计数器来设计,电路实现比较困难和繁琐,因此选择应用Verilog硬件描述语言来设计设计本模块电路,具体程序如下:module clk_div(CLK_in,CLK_out);input CLK_in;output CLK_out;reg CLK_out;reg[25:0] temp;always @(posedge CLK_in)beginif(temp>=25000000)begintemp=0;CLK_out= ~ CLK_out;endelsetemp=temp+1;endendmodule经过QuartusII软件综合后,电路的模块图如图3.1—1所示.图3.1—1 时钟分频模块电路图3.2 时序控制模块为了实现计数模块的计数和清零功能和锁存器的锁存开启功能可以在整个系统中协调工作,本模块电路采用QuartusII软件,以原理图的形式编辑,主要选用了T触发器将1Hz 脉冲信号转换成0.5Hz,T H为1秒的脉冲来作为计时器使能脉冲;经非门产生与计数使能脉冲相反的0.5Hz脉冲作为锁存器开启脉冲;将1Hz脉冲与0.5Hz脉冲经与门产生一个占空比为1/4,频率也为0.5Hz的脉冲信号作为计数器清零信号.具体电路原理图如图3.2—1所示.电路产生的时序波形图如图3.2—2所示.图3.2—1 时序控制模块电路原理图(1)En_jishu 引脚输出的是0.5Hz的时钟信号,也就是控制计数器的1秒钟时钟信号;(2)LOCK_EN 引脚输出的是0.5Hz的锁存器的开启信号;(3)qingling 引脚输出的是占空比为1:4且频率也为0.5Hz的时钟信号.图3.2—2 系统时序波形图3.3 计数模块根据设计要求要实现六位数的测量所以这里要求设计一个六位数的计数器,本模块电路选用74HC192来设计这个计数器在本设计中将计数模块设计成两成,第一层是将两个74HC192组合连接做成两位数的计数器;第二层将三个第一层的组合模块器件组合在一起这样就有六个74HC192就实现了六位十进制数的计数.第一层电路原理图如图3.3—1所示.;该层应用QuartusII软件创建的完整的模块图如图3.3—2所示.图3.3—1 计数第一层电路原理图图3.3—2第一层层电路模块图第二层原理图如图3.3—3所示;图3.3—3 计数器第二层原理图该层应用QuartusII软件创建的完整的模块图如图3.3—4所示.图3.3—4 计数器第二层模块图计数器模块仿真时序图如图3.3—5所示.图3.3—5 计数模块仿真时序图标注:由于仿真时间长,无法看到整个过程这里就截取数值为“099635“附近的仿真结果.3.4 锁存模块本模块主要完成对计数器的计数值的锁存功能,由于被测脉冲是不间断的,计数器会不断的计数循环没有一个固定的值,所以需要设计一个锁存模块来对计数器的计数值进行锁存,应用D触发器可以就可以实现数值的锁存功能,本模块采取将24个D触发器和在一起对计数器的产生的24位二进制数尽心锁存的理念设计了一个锁存模块,具体电路原理图如图3.4—1所示.应用QuartusII软件创建的完整的模块图如图3.4—1所示.图3.4—1 四位二进制数的锁存电路原理图应用QuartusII软件创建的完整的模块电路图如图3.4—2所示.图3.4—2 24位二进制数的锁存电路模块图3.5 显示译码模块根据EDA实验板上现有的数码管,只有7SLEDA、7SLEDB两个共阴数码管没有接译码驱动器件的,其余的四个数码管都已经现有接了CD4511.所以本设计中只需做两位数的译码驱动.本模块主要实现实两位数的译码显示,由于EDA实验板中是共阴的数码管,所以需要共阴译码驱动器件,这里应用74HC48来实现该设计中的译码显示,具体电路原理图如图3.5—1所示.图3.5—1 两位共阴数码管的译码驱动电路原理图应用QuartusII软件创建的完整的模块电路图如图3.5—2所示.图3.5—2 完整的译码模块器件译码模块时序仿真图如图3.5—3所示.图3.5—3 译码模块时序仿真图DD2对应输入端H、DD1对应输入端D.当H为1,D为1时;DD2为(011000)即为数码管显示“1”,DD1为(1111110)也就是数码管显示“0”.4 设计测试结果根据书本中芯CyclneⅡ系列的EP2C5T144C8芯片的引脚分配列表对所有引脚进行PIN 脚设置,50MHz信号就由EDA实验板上的50MHz晶振产生,引脚标号为“17“;被测信号由EDA实验板上的3.768KHz产生,经过4060分频产生4Hz、64Hz、128Hz、256Hz、512Hz、1024Hz、2048Hz、引脚编号为”88“,不同频率之间的转换用EDA实验板上的跳针来实现.最后下载到实验板上.本次下载用EDA实验板上的临时下载口下载,断电后就会被清除.测试结果当跳针在4Hz时数码管上显示”000004“左右、当跳针在512Hz时数码管显示”000512“左右数据有误差产生的原因可能有以下几点:(1) EDA实验板上的晶振产生的脉冲频率不稳定;(2) EDA实验板上脉冲经过4606分频后脉冲变得不稳定;(3)本设计中有很多的门电路,可能各个门电路上有延时.5 总结在为期四天的课程设计中我受益良多,首先,在一个月的寒假中我对QuartusⅡ已经遗忘了很多,在这次的课程设计中我有加深了对QuartusⅡ软件了解,更加熟悉了对Quartus Ⅱ软件的操作,在这次设计中又学会了一些新的操作方法,比如分层设计、分模块的设计方法、总线的连接方法等等.这让设计的条理变得更加清晰、方向更加明确、而且遇到错误查找起来更方便.不会像以前一样一旦有错误就要满设计的找,像个无头苍蝇一样.其次,在这次设计中我选用了74HC192来设计计数模块,这就让我更加清楚明白74HC192的功能,对其的引脚的功能更加清楚了.比如:CLR 清零、LD预置数、UP端加法计数脉冲接口、Down减法计数脉冲接口.CON 进位端,当74HC192计数到9时CON端就会产生一个低电平,BON端借位端,当74HC129减到0时BON端就会产生一个低电平等等.同时对该芯片的功能表也更加了解了,这次设计中也让我对D触发器和T触发器进行了一次复习.最后,这次设计不仅仅学会了对课程的设计,也同样知道了一些对今后学的设计,对生活的设计.在课程设计中,我们要先想好总的框架图,然后在细分到各个模块,再在各个模块中进行分设计,最后在综合在一起,这样就条理更清晰,不容易出差错.这和学习和生活的道理也是一样的,在学习上我们要先计划好学习的计划,然后再分步去做各个小的细节.这样就让学习更加的有效率.生活中也是要先规划好,小到一天或一个星期,大到一个月、一个季度或是一年.这样才更加的生活有节奏,不会浪费时间,碌碌无为,一学期下来什么都没有做.所以在今后的学习生活中我会尽力秉着这次课程设计时后的精神和方法去应对今后的学习和生活.附录系统设计总电路原理图如图5—1所示:图5—1 设计总图9 / 11。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2014年FPGA课程设计课程设计报告课程名称:FPGA课程设计实验名称:直接数字合成器设计姓名:李思彧学号: 20114690 班级:电子科11-1 班指导教师:倪伟合肥工业大学电子科学与应用物理学院制一、实验原理直接数字式频率合成器(DDS)是将先进的数字处理理论与方法引入频率合成的一项新技术,DDS把一系列数字量形式的信号通过数/模转换器转换成模拟量形式的信号。

DDS的具体工作过程是由N位相位累加器、N位加法器和N位累加寄存器组成。

每来一个时钟脉冲,N位加法器将频率控制字K与N 位累加寄存器输出的累加相位数据相加,并把相加后的结果送至累加寄存器的输入端。

累加寄存器一方面将上一时钟周期作用后所产生的新的相位数据反馈到加法器的输入端,使加法器在下一时钟的作用下继续与频率控制字K相加;另一方面将这个值作为取样地址送入幅度/相位转换电路,幅度/相位转换电路根据这个地址输出相应的波形数据。

最后经D/A转换器和LPF将波形数据转换成所需要的模拟波形。

图1.直接数字式频率合成的基本框图1 DDS的设计原理DDS的原理图如图1所示。

DDS实现频率合成主要是通过查表的方式进行的。

正弦查询表是一个只读存储器(ROM),以相位为地址,存有1个或多个按0°~360°相位划分幅值的正弦波幅度信息。

相位累加器对频率控制字进行累加运算,若需要还可以加入相位控制字,得到的结果作为正弦波查询表的地址。

正弦查询表的输出为数字化正弦幅度值,通过D/A转换器转化为近似正弦波的阶梯波,再通过低通滤波器滤除高频成分和噪声最终得到一个纯正度很高的正弦波。

1.1 建模正弦波y=sin(2πx),若以f量化的量化频率对其幅度值进行量化,一个周期可以得到M=f量化个幅度值。

将这些幅度值按顺序存入到ROM。

相位累加器在参考时钟的驱动下,每来1个脉冲,输出就会增加1个步长相位增量X,输出数据作为地址送入ROM中,读出对应的幅度值形成相应的波形。

1.2 参数设定DDS输出信号频率:其中,X为频率累加器设定值;N为相位累加器位数;fc为参考时钟频率。

例如,假定基准时钟为200 MHz,累加器的位数为32,频率控制字X 为:0x08000000H,即为227,则:再设定频率控制字X为0x80000000H,即为231,则:可见,理论上通过设定DDS相位累加器位数N、频率控制字X和基准fc的值,就可以得到任一频率的输出。

频率分辨率为:fres=fc/2N,由参考时钟和累加器的位数决定,当参考时钟的频率越高,相位累加器的位数越高,所得到的频率分辨率就越高。

1.3 方案的选择在利用FPGA制作DDS时,相位累加器是决定DDS性能的一个关键部分。

一方面可以利用进位链来实现快速、高效的电路结构,同时长的进位链会减少其他逻辑的布线资源,限制整个系统速度的提高;另一方面可以利用流水线技术提高工作频率,但系统频率转换速度会相对降低。

在选择累加器实现方案时需要综合考虑。

正弦波查询表ROM也是制作的重点。

在FPGA中ROM表的尺寸随着地址位数或数据位数的增加呈指数递增,如何在满足性能的前提下节省资源开销。

一方面通过相位累加器的输出截断方式,例如从32位的相位累加器结果中提取高16位作为ROM的查询地址,由此而产生的误差会对频谱纯度有影响,但是对波形的精度的影响是可以忽略的;另一方面可以根据信号周期对称性来压缩ROM的尺寸,这时系统硬件设计复杂度会有所增加。

因此,需要选取合适的参数和ROM 压缩技术,在满足系统性能的前提下使得系统尽量优化。

二、实验步骤2.Verilog HDL实现DDS模块2.1累加器模块累加器模块实现将相位控制字以及频率控制字累加,并生成地址输出,利用该地址可以对ROM寻址。

累加器模块的verilog程序如下:module acc(clk,clr,dataa,datab,addr);input[11:0] dataa,datab;input clk,clr;output[11:0] addr;wire[11:0] addr;//reg[15:0] daraa_reg,datab_reg;reg[11:0] A,addr_reg;always@(posedge clk or posedge clr)beginif(clr)beginaddr_reg=16'h0000;A=16'h0000;endelsebeginA=A+dataa;addr_reg=datab+A;endendassign addr=addr_reg;endmodule2.2ROM的生成制作DDS的过程中,我们需要正弦函数上各个点的具体数值,以便我们输出正弦波形,这些正弦波的数值需要存入一个只读寄存器(ROM)中。

在ise中可以通过添加ip核来生成ROM。

制作完成后可以在工程中看到生成的ROM如图2:图2.由于ROM数据较多我们需要利用matlab来完成COE文件的生成,生成COE的程序如下:t=0:2*pi/2^12:2*piy=0.5*sin(t)+0.5;r=ceil(y*(2^8-1)); %将小数转换为整数,ceil是向上取整。

fid = fopen('sin.coe','w'); %写到sin.coe文件,用来初始化sin_romfprintf(fid,'MEMORY_INITIALIZATION_RADIX=10;\n');fprintf(fid,'MEMORY_INITIALIZATION_VECTOR=\n');for i = 1:1:2^12fprintf(fid,'%d',r(i));if i==2^12fprintf(fid,';');elsefprintf(fid,',');endif i%15==0fprintf(fid,'\n');endendfclose(fid);2.3顶层模块设计:顶层模块完成累加器的调用,以及ROM的调用,输出我们所需要的数据顶层模块的程序如下:module topmodel(clk,clr,ena,dataa,datab,dds_data);input clk,clr,ena;input[11:0] dataa,datab;output[15:0] dds_data;//reg[15:0] result_reg;wire[11:0] result_wire;//reg[12:0] addr_reg;//wire[12:0] addr_wire;acc accu(.clk(clk),.clr(clr),.dataa(dataa),.datab(datab),.addr(result_wire));sinrom wave(.clka(clk), // input clka.ena(ena), // input ena.addra(result_wire), // input [12 : 0] addra.douta(dds_data) // output [15 : 0] douta);endmodule2.4测试文件的编写以及仿真在完成程序的编写之后,需要添加测试文件以及激励信号,实现在电脑上仿真。

测试程序如下:module testtop;// Inputsreg clk;reg clr;reg ena;reg [11:0] dataa;reg [11:0] datab;// Outputswire [15:0] dds_data;// Instantiate the Unit Under Test (UUT)topmodel uut (.clk(clk),.clr(clr),.ena(ena),.dataa(dataa),.datab(datab),.dds_data(dds_data));initial begin// Initialize Inputsclk = 0;clr = 1;ena = 0;dataa = 0;datab = 0;// Wait 100 ns for global reset to finish#6 clr=0;#5 dataa=12'h0003;#1 datab=12'h0003;#10 ena=1;//#2 ena=0;// Add stimulus hereendalways #5 clk=~clk;always@(posedge clk)begin$display("%d",dds_data);endendmodule2.5程序下载实现硬件仿真实现程序的下载首先需要先设置cdc图3.cdc设置图4.cdc关联引脚完成cdc设置之后需要进行ucf引脚约束文件的编写:ucf文件内容如下:NET "clk" LOC =AH15;NET "ena" LOC =AC24;NET "clr" LOC =AC25;NET "dataa[0]" LOC=AE26;NET "dataa[1]" LOC=AE27;NET "dataa[2]" LOC=AF26;NET "dataa[3]" LOC=AF25;NET "dataa[4]" LOC=AG27;NET "dataa[5]" LOC=U25;之后便可以下载仿真三、实验结果及分析3.1仿真波形在电脑上的仿真波形如图:图5.仿真波形将输出数据打印出来并用excel生成曲线图:图5.打印出的数据图6.EXCEL画出的正弦波通过EXCEL画出的曲线图我们可以清楚看到我们的输出数据完美的画出了正弦波,其中系列1为1.5625Mhz,系列2为12.5Mhz,这证明了我们输出是正确的,所以程序也是正确的。

3.2下载到实验板的仿真波形:通过CDC软件我们可以看到硬件仿真的结果,结果符合我们预期图7.cdc仿真结果四、体会在完成这次课程设计的过程中,我们不仅增长了自己的知识,同时也锻炼了自己的能力。

首先,这次课程设计让我们了解到了一种通过数字电路控制生成特定频率波形的方式,这是我们在日常的学习中没有接触过的。

DDS即直接数字合成器,我们向DDS中输入频率控制字,相位控制字,便可以在DDS的输出端得到一系列的数字,通过AD转换以及低通滤波便可以得到完美的正弦波信号。

另外,我们学习到了ise的使用,以及下载程序的方法。

其次,这次课程设计锻炼了我们解决问题的能力,我们拿到的题目只有要求而没有具体的实现方法,所以从方案的设计到程序的设计,直至最后结果的呈现完全依靠自己的摸索,在摸索中,我们初步了解了科研工作的基本工作步骤,例如如何查找文献,设计科研方案,解决在科研过程中出现的种种问题。