锁相环电路及工作原理(免费)

什么是锁相环电路?

什么是锁相环电路?一、锁相环电路的定义及原理锁相环电路是一种电子电路系统,通过不断调整输入信号与参考信号之间的差异,使得输出信号与参考信号同步的技术。

锁相环电路一般由相位检测器、低通滤波器、控制环节和输出环节组成。

其原理是利用反馈控制的方式,使得输出信号的相位与参考信号的相位保持一致。

锁相环电路在通信领域、测量仪器、音频处理等方面有着广泛的应用。

它能够消除信号传输过程中的相位误差,提高信号的稳定性和准确性。

二、锁相环电路的工作原理1. 相位检测器相位检测器是锁相环电路的核心部件之一,其作用是检测输入信号与参考信号之间的差异,并将差异信号转化为控制电压。

常见的相位检测器有边沿触发器、比较器和专用的数字相位检测器。

(1)边沿触发器:边沿触发器是一种简单实用的相位检测器,通过比较输入信号与参考信号的边沿差异来实现相位检测。

(2)比较器:比较器通过比较输入信号与参考信号的幅值大小来实现相位检测。

比较器常用于高频应用中。

(3)数字相位检测器:数字相位检测器通过将输入信号与参考信号转化为数字信号,并利用计算机算法来实现相位检测。

它具有高精度和稳定性的特点。

2. 低通滤波器低通滤波器用于消除相位检测器输出中的高频噪声,提取出有效的控制信号。

低通滤波器常用于锁相环电路的控制环节。

3. 控制环节控制环节通过获取低通滤波器输出的控制信号,并根据差异信号进行调节,使得输出信号的相位逐渐趋于参考信号的相位。

常用的控制方式有比例控制、积分控制和微分控制。

4. 输出环节输出环节将锁相环电路的输出信号转化为所需的形式,如模拟信号、脉冲信号或数字信号。

输出环节的设计对于锁相环电路的应用至关重要。

三、锁相环电路的应用1. 通信领域锁相环电路在通信领域中被广泛应用于时钟恢复、频率合成、时基稳定性控制以及数据调整等技术。

它可以提高通信系统的抗干扰能力和信号质量,保证数据的可靠传输。

2. 测量仪器锁相环电路在测量仪器中的应用主要体现在频率测量、相位测量和时间测量等方面。

锁相环的电路组成、器件参数及工作原理

摘要:简单介绍了锁相环电路的基本概念及原理,以通用型集成锁相环4046为例主要介绍了锁相环的电路组成、器件参数及工作原理,并对COMS集成锁相环CC4046的应用做了简单研究。

关键词:锁相环鉴相器压控振荡器1 引言锁相环作为一种重要的功能电路在通信、导航、控制、仪器仪表等领域得到了广泛的应用。

20世纪70年代以后随着集成电路技术的飞速发展,出现了多种型号的集成锁相环产品,其中模拟式集成锁相环以NE/SE 560系列最为常用,COMS集成锁相环CD/CC4046最具代表性。

两者基本原理相同,区别在于前者的鉴相器由模拟电路组成,而后者由逻辑电路组成。

2 锁相环的基本概念所谓锁相,就是相位同步的自动控制。

完成两个信号间相位同步的自动控制系统的环路叫做锁相环,也称PLL(Phase Locked Loop)。

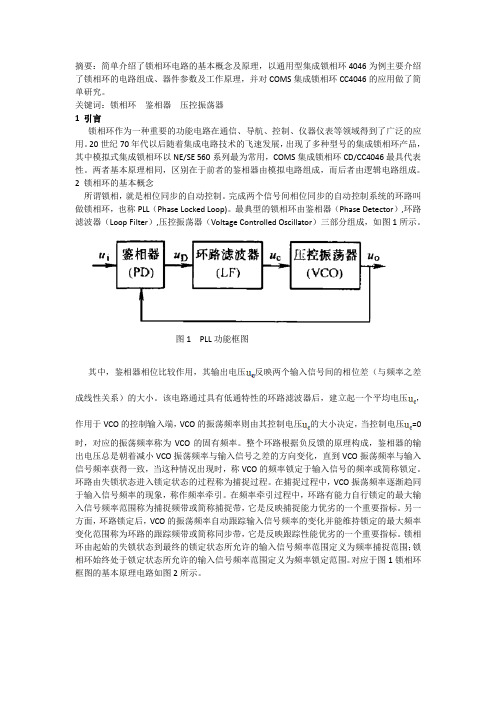

最典型的锁相环由鉴相器(Phase Detector),环路滤波器(Loop Filter),压控振荡器(Voltage Controlled Oscillator)三部分组成,如图1所示。

图1 PLL功能框图其中,鉴相器相位比较作用,其输出电压反映两个输入信号间的相位差(与频率之差成线性关系)的大小。

该电路通过具有低通特性的环路滤波器后,建立起一个平均电压,作用于VCO的控制输入端,VCO的振荡频率则由其控制电压的大小决定,当控制电压=0时,对应的振荡频率称为VCO的固有频率。

整个环路根据负反馈的原理构成,鉴相器的输出电压总是朝着减小VCO振荡频率与输入信号之差的方向变化,直到VCO振荡频率与输入信号频率获得一致,当这种情况出现时,称VCO的频率锁定于输入信号的频率或简称锁定。

环路由失锁状态进入锁定状态的过程称为捕捉过程。

在捕捉过程中,VCO振荡频率逐渐趋同于输入信号频率的现象,称作频率牵引。

在频率牵引过程中,环路有能力自行锁定的最大输入信号频率范围称为捕捉频带或简称捕捉带,它是反映捕捉能力优劣的一个重要指标。

锁相环路的工作原理

解决方案

减小环路带宽,降低VCO的调谐灵敏度,减小环路增益。

Part

05

锁相环路的优化设计

选择合适的鉴相器与压控振荡器

鉴相器选择

鉴相器是锁相环路中的核心元件,用于比较输入信号与压控振荡器输出信号的 相位差。根据应用需求,选择合适的鉴相器,如模拟鉴相器和数字鉴相器,确 保环路性能达到最佳。

高速锁定

锁相环路具有快速锁定能力,能够在短时间内实现相位同 步。

自动跟踪相位变化

锁相环路能够自动跟踪输入信号的相位变化,实现输出信 号与输入信号的相位同步。

高精度相位调整

锁相环路能够实现高精度相位调整,具有较低的相位噪声 。

工作原理概述

鉴相器

鉴相器用于比较输入信号 和输出信号的相位差,产 生一个误差信号。

雷达系统中的信号处理

雷达系统在探测、跟踪和识别目标时,需要处理大量的回波 信号。锁相环路在雷达信号处理中起到关键作用,用于实现 回波信号的频率跟踪和信号解调。

通过比较回波信号与本地振荡器信号的相位差,锁相环路能 够自动调整本地振荡器信号的频率,使其与回波信号的频率 一致,实现回波信号的准确解调。这有助于提高雷达系统的 目标检测和识别能力。

Part

06

锁相环路的实际应用案例

无线通信中的频率合成

频率合成器是无线通信系统中的关键组成部分,用于产生高精度、高稳定度的频率信号。 锁相环路被广泛应用于频率合成器中,通过比较输出信号与参考信号的相位差,自动调 整输出信号的频率,实现输出信号与参考信号的相位同步。

锁相环路在频率合成中的应用,能够提高频率信号的稳定性和精度,减小信号的相位噪 声,为无线通信系统的稳定运行提供保障。

(完整版)锁相环工作原理

基本组成和锁相环电路1、频率合成器电路频率合成器组成:频率合成器电路为本机收发电路的频率源,产生接收第一本机信号源和发射电路的发射信号源,发射信号源主要由锁相环和VCO电路直接产生。

如图3-4所示。

在现在的移动通信终端中,用于射频前端上下变频的本振源(LO),在射频电路中起着非常重要的作用。

本振源通常是由锁相环电路(Phase-Locked Loop)来实现。

2.锁相环:它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域3.锁相环基本原理:锁相环包含三个主要的部分:⑴鉴相器(或相位比较器,记为PD或PC):是完成相位比较的单元,用来比较输入信号和基准信号的之间的相位.它的输出电压正比于两个输入信号之相位差.⑵低通滤波器(LPF):是个线性电路,其作用是滤除鉴相器输出电压中的高频分量,起平滑滤波的作用.通常由电阻、电容或电感等组成,有时也包含运算放大器。

⑶压控振荡器(VCO):振荡频率受控制电压控制的振荡器,而振荡频率与控制电压之间成线性关系。

在PLL中,压控振荡器实际上是把控制电压转换为相位。

1、压控振荡器的输出经过采集并分频;2、和基准信号同时输入鉴相器;3、鉴相器通过比较上述两个信号的频率差,然后输出一个直流脉冲电压;4、控制VCO,使它的频率改变;5、这样经过一个很短的时间,VCO 的输出就会稳定于某一期望值。

锁相环电路是一种相位负反馈系统。

一个完整的锁相环电路是由晶振、鉴相器、R分频器、N分频器、压控振荡器(VCO)、低通滤波器(LFP)构成,并留有数据控制接口。

锁相环电路的工作原理是:在控制接口对R分频器和N分频器完成参数配置后。

晶振产生的参考频率(Fref)经R分频后输入到鉴相器,同时VCO的输出频率(Fout)也经N分频后输入到鉴相器,鉴相器对这两个信号进行相位比较,将比较的相位差以电压或电流的方式输出,并通过LFP滤波,加到VCO的调制端,从而控制VCO的输出频率,使鉴相器两输入端的输入频率相等。

锁相环电路概述

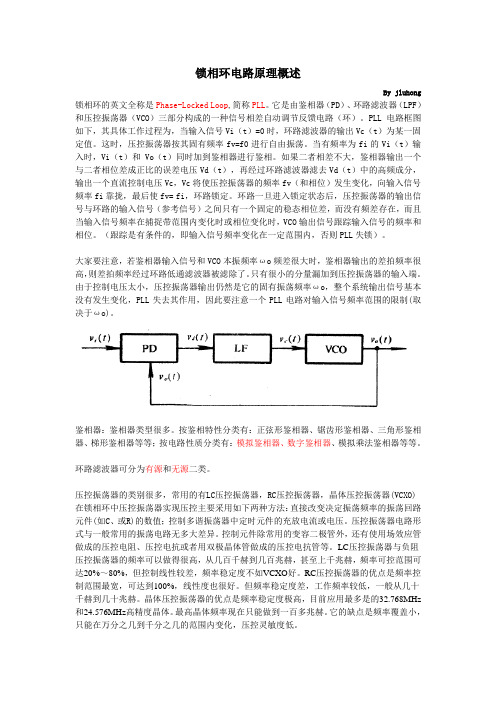

锁相环电路原理概述By jluhong 锁相环的英文全称是Phase-Locked Loop,简称PLL。

它是由鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)三部分构成的一种信号相差自动调节反馈电路(环)。

PLL电路框图如下,其具体工作过程为,当输入信号Vi(t)=0时,环路滤波器的输出Vc(t)为某一固定值。

这时,压控振荡器按其固有频率fv=f0进行自由振荡。

当有频率为fi的Vi(t)输入时,Vi(t)和Vo(t)同时加到鉴相器进行鉴相。

如果二者相差不大,鉴相器输出一个与二者相位差成正比的误差电压Vd(t),再经过环路滤波器滤去Vd(t)中的高频成分,输出一个直流控制电压Vc,Vc将使压控振荡器的频率fv(和相位)发生变化,向输入信号频率fi靠拢,最后使fv= fi,环路锁定。

环路一旦进入锁定状态后,压控振荡器的输出信号与环路的输入信号(参考信号)之间只有一个固定的稳态相位差,而没有频差存在,而且当输入信号频率在捕捉带范围内变化时或相位变化时,VCO输出信号跟踪输入信号的频率和相位。

(跟踪是有条件的,即输入信号频率变化在一定范围内,否则PLL失锁)。

大家要注意,若鉴相器输入信号和VCO本振频率ωo频差很大时,鉴相器输出的差拍频率很高,则差拍频率经过环路低通滤波器被滤除了。

只有很小的分量漏加到压控振荡器的输入端。

由于控制电压太小,压控振荡器输出仍然是它的固有振荡频率ωo,整个系统输出信号基本没有发生变化,PLL失去其作用,因此要注意一个PLL电路对输入信号频率范围的限制(取决于ωo)。

鉴相器:鉴相器类型很多。

按鉴相特性分类有:正弦形鉴相器、锯齿形鉴相器、三角形鉴相器、梯形鉴相器等等;按电路性质分类有:模拟鉴相器、数字鉴相器、模拟乘法鉴相器等等。

环路滤波器可分为有源和无源二类。

压控振荡器的类别很多,常用的有LC压控振荡器,RC压控振荡器,晶体压控振荡器(VCXO)在锁相环中压控振荡器实现压控主要采用如下两种方法:直接改变决定振荡频率的振荡回路元件(如C、或R)的数值;控制多谐振荡器中定时元件的充放电流或电压。

锁相环电路设计

锁相环电路设计锁相环电路是一种常见的电路设计,它可以用于频率合成、时钟恢复、数字信号处理等领域。

锁相环电路的基本原理是通过比较输入信号和参考信号的相位差,控制输出信号的频率和相位,使其与参考信号同步。

本文将介绍锁相环电路的基本原理、设计流程和应用。

一、锁相环电路的基本原理锁相环电路由相位检测器、环路滤波器、控制电压源和振荡器四部分组成。

其中,相位检测器用于检测输入信号和参考信号的相位差,环路滤波器用于滤波和放大控制电压,控制电压源用于产生控制电压,振荡器用于产生输出信号。

锁相环电路的工作原理如下:首先,输入信号和参考信号经过相位检测器比较,得到相位差。

然后,相位差经过环路滤波器滤波和放大,产生控制电压。

控制电压作用于振荡器,调整其频率和相位,使其与参考信号同步。

最后,输出信号经过除频器输出所需频率。

二、锁相环电路的设计流程锁相环电路的设计流程包括以下几个步骤:1. 确定输入信号和参考信号的频率范围和精度要求。

2. 选择合适的相位检测器和环路滤波器,根据输入信号和参考信号的特性确定其参数。

3. 选择合适的振荡器,根据输出信号的频率和精度要求确定其参数。

4. 设计控制电压源,根据环路滤波器的特性确定其参数。

5. 进行仿真和实验验证,调整参数,优化电路性能。

三、锁相环电路的应用锁相环电路广泛应用于频率合成、时钟恢复、数字信号处理等领域。

以下是几个典型的应用案例:1. 频率合成器:锁相环电路可以将参考信号的频率倍频或分频,产生所需的输出频率。

2. 时钟恢复器:锁相环电路可以从输入信号中恢复时钟信号,用于数字通信系统中的时钟同步。

3. 数字信号处理:锁相环电路可以用于数字信号的相位同步和频率同步,提高信号质量和可靠性。

四、总结锁相环电路是一种常见的电路设计,其基本原理是通过比较输入信号和参考信号的相位差,控制输出信号的频率和相位,使其与参考信号同步。

锁相环电路的设计流程包括确定输入信号和参考信号的特性、选择合适的电路元件、仿真和实验验证等步骤。

锁相环(pll)的工作原理

锁相环(pll)的工作原理英文回答:A phase-locked loop (PLL) is a control system that is widely used in electronic circuits to synchronize the phase and frequency of an output signal with that of a reference signal. It consists of three main components: a voltage-controlled oscillator (VCO), a phase detector, and a loop filter.The working principle of a PLL can be explained in the following steps:1. Phase Detection: The phase detector compares the phase of the reference signal with that of the output signal from the VCO. It generates an error signal that represents the phase difference between the two signals.2. Frequency Control: The error signal is filtered by the loop filter to remove any unwanted noise and to providea smooth control signal. This control signal is then applied to the VCO, which adjusts its frequency based on the control input.3. Phase Comparison: The output signal from the VCO is again compared with the reference signal, and the process of phase detection and frequency control is repeated. This feedback loop continues until the phase difference between the two signals is minimized.4. Locking: Once the phase difference is reduced to zero, the PLL is said to be locked. At this point, the output signal is in sync with the reference signal, and the VCO maintains a stable frequency and phase relationship with the input signal.The PLL can be used in various applications, such as clock synchronization, frequency synthesis, and demodulation. It provides a reliable and accurate methodfor maintaining phase and frequency coherence between different signals.中文回答:锁相环(PLL)是一种广泛应用于电子电路中的控制系统,用于将输出信号的相位和频率与参考信号同步。

PLL(锁相环)电路原理及设计 [收藏]

![PLL(锁相环)电路原理及设计 [收藏]](https://img.taocdn.com/s3/m/ca8d027601f69e3143329497.png)

PLL(锁相环)电路原理及设计[收藏]PLL(锁相环)电路原理及设计在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。

无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。

但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。

如果采用PLL(锁相环)(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。

此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。

一PLL(锁相环)电路的基本构成PLL(锁相环)电路的概要图1所示的为PLL(锁相环)电路的基本方块图。

此所使用的基准信号为稳定度很高的晶体振荡电路信号。

此一电路的中心为相位此较器。

相位比较器可以将基准信号与VCO (Voltage Controlled Oscillator……电压控制振荡器)的相位比较。

如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。

(将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。

)利用此一误差信号,可以控制VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率)成为一致。

PLL(锁相环)可以使高频率振荡器的频率与基准频率的整数倍的频率相一致。

由于,基准振荡器大多为使用晶体振荡器,因此,高频率振荡器的频率稳定度可以与晶体振荡器相比美。

只要是基准频率的整数倍,便可以得到各种频率的输出。

从图1的PLL(锁相环)基本构成中,可以知道其是由VCO,相位比较器,基准频率振荡器,回路滤波器所构成。

在此,假设基准振荡器的频率为fr,VCO的频率为fo。

在此一电路中,假设frgt;fo时,也即是VC0的振荡频率fo比fr低时。

此时的相位比较器的输出PD 会如图2所示,产生正脉波信号,使VCO的振荡器频率提高。

相反地,如果frlt;fo时,会产生负脉波信号。

(此为利用脉波的边缘做二个信号的比较。

锁相环的工作原理

锁相环工作原理锁相技术的理论早在1932年就提出了,但直到40年代在电视机中才得到广泛的应用。

锁相环的英文全称是Phase-Locked Loop,简称PLL,是实现相位自动控制的负反馈系统,它使振荡器的相位和频率与输入信号的相位和频率同步。

锁相环包含三个主要的部分:⑴鉴相环(或相位比较器,记为PD或PC):是完成相位比较的单元,用来比较输入信号和基准信号的之间的相位.它的输出电压正比于两个输入信号之相位差.⑵低通滤波器(LPF):是个线性电路,其作用是滤除鉴相器输出电压中的高频分量,起平滑滤波的作用.通常由电阻、电容或电感等组成,有时也包含运算放大器。

⑶压控振荡器(VCO):振荡频率受控制电压控制的振荡器,而振荡频率与控制电压之间成线性关系。

在PLL中,压控振荡器实际上是把控制电压转换为相位。

图1为上述三个部分组成PLL的方框图,它的工作过程如下:相位比较器把输入信号作为标准,将它的频率和相位与从VCO输出端送来的信号进行比较。

如果在它的工作范围内检测出任何相位(频率)差,就产生一个误差信号Ve(t),这个误差信号正比于输入信号和VCO输出信号之间的相位差,通常是以交流分量调制的直流电平。

由低通滤波器滤除误差信号中的交流分量,产生信号Vd(t)去控制VCO,强制VCO朝着减小相位/频率误差的方向改变其频率,使输入基准信号和VCO输出信号之间的任何频率或相位差逐渐减小直至为0,这时我们就称环路已被锁定。

如果VCO的输出频率低于输入基准信号的频率,相位比较器的输出振幅就为正,经滤波后去控制VCO,使其频率增加,直到两个信号的频率和相位精确同步。

相反,若VCO输出频率高于输入基准信号,相位比较器的输出会下降,使VCO锁定在输入基准信号的频率。

下面较详细地介绍它的捕捉过程和跟踪状态。

设VCO在没有输入控制信号时的固有振荡频率为Wo。

开机后,若相位比较器的输入信号频率Wi与Wo很接近,则相位比较器将输出这两个频率信号的差拍波,因其频率很低,它将顺利通过低通滤波器,然后加到VCO输入端去作控制电压,VCO受此差拍调频,其中心频率仍为Wo。

锁相环路(PLL)电路设计实例

软件实现PLL的代码示例

01

```systemverilog

02

// 定义PLL模块

03

module pll(input wire clk_in, output reg clk_out);

软件实现PLL的代码示例

01

parameter FREF = 100e3; // 参考频率

02

parameter N = 10; // 分频比

相位保持一致。

电荷泵型PLL的电路实现

电荷泵由两个开关和两个电容 组成,一个开关用于充电,另

一个用于放电。

当输入信号与VCO输出信号 的相位存在误差时,电荷泵 的开关会根据误差信号的极 性进行切换,从而在电容上

积累或释放电荷。

电容上的电荷量会转换为电压 信号,该电压信号通过低通滤 波器平滑后,用于调整VCO的

频率。

电荷泵型PLL的性能分析

01

电荷泵型PLL具有较高的带宽和较快的响应速度,因此适用于高 速数据传输和无线通信等应用。

02

由于电荷泵型PLL采用电荷传输方式,因此对电源噪声和电磁干

扰较为敏感,需要采取相应的措施进行抑制。

电荷泵型PLL的另一个优点是易于集成,因此适合于大规模生产

03

和应用。

04

软件实现PLL的代码示例

assign clk_out = div_by_n;

always @(posedge clk_in) begin phase_error <= #1 ($posedge clk_in ? 32'hFFFFFFFF : phase_error 1);

软件实现PLL的代码示例

PLL电路设计实例:模拟型 PLL

锁相环(PLL)的工作原理

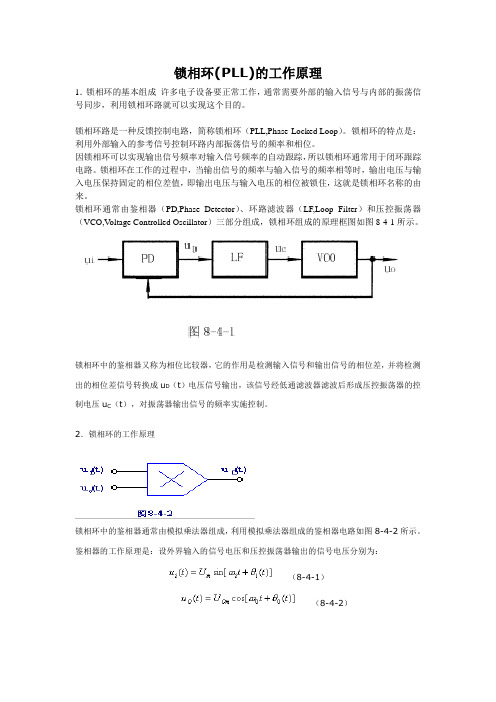

锁相环(PLL)的工作原理1.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u C(t),对振荡器输出信号的频率实施控制。

2.锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(8-4-1)(8-4-2)式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压u D为:用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压u C (t)。

即u C(t)为:(8-4-3)式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(8-4-4)则,瞬时相位差θd为:(8-4-5)对两边求微分,可得频差的关系式为(8-4-6)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,u c(t)为恒定值。

三相逆变器 锁相环pll 工作原理

三相逆变器锁相环pll 工作原理三相逆变器是一种将直流电能转换为交流电能的设备。

它通常由逆变电路和控制电路两部分组成。

锁相环(Phase-Locked Loop,PLL)是三相逆变器中的一个重要组成部分,用于实现电网电压和逆变器输出电压之间的同步控制。

锁相环(PLL)是一种用于提取频率和相位信息的控制系统。

在三相逆变器中,PLL的主要功能是将电网电压的频率和相位信息提取出来,并与逆变器的输出电压进行比较,以实现同步控制。

具体来说,锁相环通过不断调整逆变器的输出频率和相位,使其与电网电压保持同步,从而实现电能的高效转换。

锁相环的工作原理可以简单地分为三个步骤:相频检测、滤波和控制。

首先,相频检测器会对电网电压和逆变器输出电压进行相频检测,得到它们之间的相位差和频率差。

然后,滤波器会对相位差和频率差进行滤波处理,以减小干扰和噪声的影响。

最后,控制器根据滤波后的结果,调整逆变器的输出频率和相位,使其与电网电压保持同步。

在具体实现中,锁相环通常由相频检测器、环路滤波器和控制器三部分组成。

相频检测器可以通过比较电网电压和逆变器输出电压的相位差和频率差来提取同步信息。

环路滤波器则用于对相位差和频率差进行滤波处理,以消除噪声和干扰的影响。

控制器则根据滤波后的结果,调整逆变器的输出频率和相位,使其与电网电压保持同步。

在三相逆变器中,锁相环的工作原理非常重要。

通过锁相环的同步控制,可以有效地实现逆变器输出电压与电网电压的同步,从而提高逆变器的转换效率和功率质量。

同时,锁相环还具有快速响应、高精度和抗干扰等特点,能够在电网电压波动或扰动的情况下保持逆变器的稳定运行。

总结起来,三相逆变器中的锁相环是一种用于实现电网电压和逆变器输出电压同步控制的重要组成部分。

它通过相频检测、滤波和控制等步骤,不断调整逆变器的输出频率和相位,使其与电网电压保持同步。

锁相环的工作原理能够有效提高逆变器的转换效率和功率质量,并具有快速响应、高精度和抗干扰等特点,能够保持逆变器的稳定运行。

锁相环组成和工作原理

锁相环组成和工作原理

锁相环是一种用于控制信号的电子元件,它由一组环形的电

路组成,可以控制信号的频率和幅度。

它的工作原理是,当一个

信号通过环形电路时,它会受到一个反馈信号的影响,这个反馈

信号会改变原始信号的频率和幅度,从而控制信号的输出。

锁相环的组成主要有三部分:滤波器、放大器和比较器。

滤

波器的作用是过滤掉不需要的信号,从而使信号更加清晰;放大

器的作用是放大信号,使信号更加明显;比较器的作用是比较原

始信号和反馈信号,从而控制信号的输出。

锁相环的工作原理是,当一个信号通过滤波器时,它会被放大,然后通过比较器,比较器会比较原始信号和反馈信号,如果

发现两者不一致,就会调整原始信号的频率和幅度,从而控制信

号的输出。

锁相环的应用非常广泛,它可以用于控制信号的频率和幅度,也可以用于控制电机的转速,还可以用于控制电源的输出,从而

实现节能效果。

总之,锁相环是一种用于控制信号的电子元件,它由滤波器、放大器和比较器组成,它的工作原理是,当一个信号通过环形电

路时,它会受到一个反馈信号的影响,这个反馈信号会改变原始

信号的频率和幅度,从而控制信号的输出。

它的应用非常广泛,

可以用于控制信号的频率和幅度,也可以用于控制电机的转速,还可以用于控制电源的输出,从而实现节能效果。

《锁相环路》课件

环路滤波器

01

环路滤波器是锁相环路中的重要组成部分,用于滤除

鉴相器输出信号中的高频分量,以减小噪声和干扰。

02

它通常由RC电路或运算放大器构成,能够实现低通

滤波功能。

03

环路滤波器的参数设置对锁相环路的性能有很大影响

,需要根据实际情况进行调整。

压控振荡器

01

压控振荡器是锁相环路中的输出信号源,用于产生调频或调相 的输出信号。

05

锁相环路的设计与实现

设计原则与步骤

设计原则:稳定性、准确 性、可靠性、易实现性。

1. 确定系统参数和性能指 标。

3. 进行理论分析和仿真验 证。

设计步骤

2. 选择合适的元件和电路 结构。

4. 优化设计并进行实验测 试。

实现方法与技巧

实现方法:硬件实现、软件实现、软硬件结合 实现。

01

1. 选择合适的元件和电路,确保稳定性。

跟踪速的频率与相位精度

频率精度

锁相环路输出信号的频率与输入信号的频率之间的误差。

相位精度

锁相环路输出信号的相位与输入信号的相位之间的误差。

抗干扰性能与稳定性

抗干扰性能

锁相环路在存在噪声或干扰的情况下,保持锁定状态的能力。

稳定性

锁相环路在各种工作条件下,性能参数的变化情况,以及环路对参数变化的适应能力。

输出信号的调整与控制

调整环路参数

根据误差信号调整环路参数,如环路滤波器的增益、相位滞后等,以控制环路输 出信号的相位。

控制环路状态

通过调整环路参数,控制环路的锁定状态,使环路输出信号的相位与输入信号保 持一致。

04

锁相环路的性能指标

锁定时间与跟踪速度

锁定时间

锁相环工作原理

锁相环工作原理锁相环是一种常用于频率合成和时钟恢复的电路。

它通过对输入信号进行频率和相位的调整,使其与参考信号保持同步。

锁相环广泛应用于通信、雷达、测量仪器等领域。

一、基本原理锁相环由相位比较器、低通滤波器、电压控制振荡器(VCO)和分频器组成。

其工作原理如下:1. 参考信号输入:外部提供一个稳定的参考信号,作为锁相环的参考频率。

2. 相位比较:将输入信号与参考信号进行相位比较,得到相位误差信号。

3. 低通滤波:将相位误差信号经过低通滤波器滤波,得到平滑的控制电压。

4. 控制振荡器调频:将控制电压作为输入,控制电压控制振荡器的频率,实现频率的调整。

5. 分频:将控制振荡器的输出信号进行分频,得到反馈信号。

6. 反馈:将分频后的信号与输入信号进行相位比较,得到新的相位误差信号。

通过不断的相位比较、滤波和调频,锁相环可以实现输入信号与参考信号的同步。

二、工作过程锁相环的工作过程可以分为锁定和跟踪两个阶段。

1. 锁定阶段:在初始状态下,锁相环的输出与输入信号存在相位差。

相位比较器将输入信号与参考信号进行比较,得到相位误差信号。

经过低通滤波器滤波后,控制电压作用于VCO,调整其频率。

经过分频器分频后,反馈信号与输入信号再次进行相位比较,得到新的相位误差信号。

通过不断的反馈和调节,相位误差逐渐减小,最终锁定在一个稳定的值,输出信号与参考信号同步。

2. 跟踪阶段:当输入信号发生频率或相位变化时,锁相环需要跟踪这些变化。

相位比较器检测到相位误差信号增大,低通滤波器将其平滑后,调节VCO的频率。

通过分频器反馈信号与输入信号进行相位比较,得到新的相位误差信号。

锁相环通过不断的反馈和调节,使输出信号重新与输入信号同步。

三、应用领域锁相环在许多领域中都有广泛的应用,包括但不限于以下几个方面:1. 频率合成:锁相环可以将一个稳定的参考信号与一个可调频率的振荡器相结合,生成一个具有所需频率的输出信号。

这在通信系统、雷达系统等需要精确频率合成的应用中非常重要。

锁相环工作原理

锁相环工作原理引言概述:锁相环(Phase-Locked Loop,简称PLL)是一种常见的电子电路,用于同步信号的频率和相位。

它在通信系统、数字信号处理、时钟同步等领域被广泛应用。

本文将详细介绍锁相环的工作原理,包括基本原理、主要组成部分、工作过程以及应用场景。

一、基本原理:1.1 反馈环路:锁相环的核心是一个反馈环路,通过不断调整输入信号的频率和相位,使其与参考信号保持同步。

这个环路由比较器、低通滤波器和控制电路组成。

1.2 相位检测器:相位检测器用于比较输入信号和参考信号的相位差,产生一个误差信号。

根据误差信号的大小和方向,控制电路将调整输入信号的相位和频率。

1.3 数字控制:现代锁相环通常采用数字控制,通过数字控制器和数字控制电路,实现对反馈环路的精确控制。

数字控制还可以实现自适应调整,提高锁相环的性能。

二、主要组成部分:2.1 振荡器:振荡器是锁相环的基础,它产生一个参考信号,用于与输入信号进行比较。

常见的振荡器有晶体振荡器和压控振荡器,前者具有稳定的频率,适用于需要高精度的应用,而后者可以通过调节电压来改变频率,适用于需要频率可调的应用。

2.2 分频器:分频器用于将输入信号的频率降低到与参考信号相匹配的频率。

它可以将输入信号分成若干个相等的周期,用于和参考信号进行比较。

2.3 低通滤波器:低通滤波器用于滤除相位检测器输出中的高频噪声,保留误差信号中的低频成分。

它可以使锁相环的输出更加稳定。

三、工作过程:3.1 初始状态:锁相环初始状态下,输入信号和参考信号的频率和相位存在差异。

相位检测器会检测到相位差,并产生一个误差信号。

3.2 调整过程:控制电路根据误差信号的大小和方向,调整输入信号的相位和频率。

通过不断调整,误差信号逐渐减小,直到达到稳定状态。

3.3 稳定状态:当输入信号和参考信号的频率和相位完全一致时,锁相环进入稳定状态。

此时,输出信号与参考信号保持同步,相位差为零。

四、应用场景:4.1 通信系统:锁相环在通信系统中用于频率合成、时钟恢复和信号调制等方面。

锁相环(pll)的工作原理

锁相环(pll)的工作原理Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!锁相环(PLL)是一种控制系统,用于保持输入信号和参考信号之间的相位和频率同步。

PLL广泛应用于通信系统、数字信号处理、频率合成、时钟恢复等领域。

锁相环的工作原理可以简单地分为四个步骤:相位检测、数字控制、频率合成和反馈调节。

下面将详细解释每个步骤的工作原理。

首先是相位检测阶段。

在锁相环中,相位检测器用于比较输入信号和参考信号之间的相位差。

最常见的相位检测器是乘法器,它将输入信号和参考信号相乘产生一个误差信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

锁相环是一种控制晶振使其相对于参考信号保持恒定相位的电路,在数字通信系统中使用比较广泛。

目前微处理器或DSP集成的片上锁相环,主要作用则是通过软件实时地配置片上外设时钟,提高系统的灵活性和可靠性。

此外,由于采用软件可编程锁相环,所设计的系统处理器外部允许较低的工作频率,而片内经过锁相环微处理器提供较高的系统时钟。

这种设计可以有效地降低系统对外部时钟的依赖和电磁干扰,提高系统启动和运行的可靠性,降低系统对硬件的设计要求。

TMS320F28l2处理器的片上晶振和锁相环模块为内核及外设提供时钟信号,并且控制器件的低功耗工作模式。

片上晶振模块允许使用2种方式为器件提供时钟,即采用内部振荡器或外部时钟源。

如果使用内部振荡器,必须在XI/XCLKIN和X2这两个引脚之间连接一个石英晶体,一般选用30 MHz。

如果采用外部时钟,可以将输人的时钟信号直接接到XI/XCLKIN引脚上,而X2悬空,不使用内部振荡器。

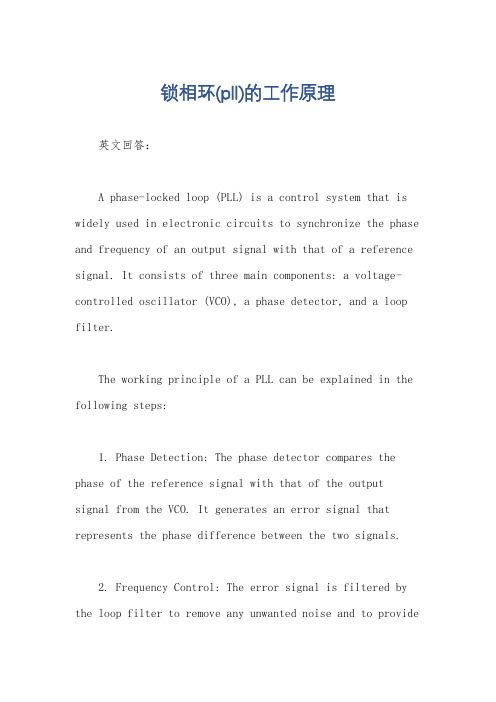

晶体振荡器及锁相环模块结构如图1 所示。

图1 晶体振荡器及锁相环模块

外部X PLL DIS引脚可以选择系统的时钟源。

当XPLLDIS为低电平时,系统直接采用外部时钟或外部晶振作为系统时钟;当XPLLDIS为高电平时,外部时钟经过PLL倍频后为系统提供时钟。

系统可以通过锁相环控制寄存器来选择锁相环的工作模式和倍频的系数。

表1列出了锁相环配置模式。

表1 锁相环配置模式

锁相环模块除了为C28x内核提供时钟外,还通过系统时钟输出提供快速和慢速2种外设时钟,如图2所示。

而系统时钟主要通过

外部引脚XPLLDIS及锁相环控制寄存器进行控制。

因此,在系统采用外部时钟并使能PLL(XPLLDIS=1)的情况下,可以通过软件设置C28x内核的时钟输人。

图2 处理器内部时钟电路

如果XPLLDIS为高电平,使能芯片内部锁相环电路,则可以通过控制寄存器PLLCR软件设置系统的工作频率。

但要注意,在通过软件改变系统的工作频率时,必须等待系统时钟稳定后才可以继续完成其他操作。

此外,还可以通过外设时钟控制寄存器使能外设时钟。

在具体的应用中,为降低系统功耗,不使用的外设最好将其时钟禁止。

外设时钟包括快速外设和慢速外设两种,分别通过HISPCP和LOSPCP寄存器进行设置。

下面给出改变锁相环倍频系数和外设时钟的具体应用程序。