Quartus常见错误分析 Error

学习verilog DHL问题笔记——Quartus常见错误

学习verilog DHL问题笔记——Quartus常见错误我初学verilog语言,很多细节都没注意,按着自己的思想就写了,编译的时候才发现各种问题。

这些都是我在学习中遇到的问题,还是很常见的。

1.Error (10028): Can't resolve multiple constant drivers for net ……解析:不能在两个以上always内对同一变量赋值,这个细节一般看书看资料会看到,但是编程时,就是没想到。

2.Error (10158): Verilog HDL Module Declaration error at clkseg.v(1): port "XXXX" is not declared as port解析:大意了,端口类型还没定义啊!3.Error (10110): variable "en" has mixed blocking and nonblocking Procedural Assignments -- must be all blocking or all nonblocking assignments解析:en在程序中有时用非阻塞赋值,有时用阻塞赋值,这是禁止的。

在初学的时候,可能分得不是很清楚,所以在检查时,一定要一步步观察慢慢来。

4.Error (10161): Verilog HDL error at clkseg.v(36): object "count" is not declared解析:这个错误应该很明显啦,只要能读得懂。

5.Error (10170): Verilog HDL syntax error at clkseg.v(37) near text "***"; expecting ";"解析:意思应该也很简单,就是检查的时候要细心点。

Quartus II 报错集锦

FPGA/CPLD在Quartus II中报错集锦1) QuartusII对代码进行时序仿真时出现Error: Can't continue timing simulation because delay annotation information for design is missing.原因:如果只需要进行功能仿真,不全编译也是可以进行下去的,但时序仿真就必须进行全编译(即工具栏上的紫色实心三角符号那项)。

全仿真包括四个模块:综合器(Synthesis)、电路装配器(Fitter)、组装器(Assember)和时序分析器(Timing Analyzer),任务窗格中会有成功标志(对号)。

2) 在下载运行的时候,出现下面的错误:Warning: The JTAG cable you are using is not supported for Nios II systems. You may experience intermittent JTAG communicationfailures with this cable. Please use a USB Blaster revision B.在运行之前已经将.sof文件下载到开发板上面了,但是依然出现上面的问题。

解决:在配置的时候,在run之后,进行配置,选择target connection,在最后一项:NIOS II Terminal Communication Device中,要选择none(不要是Jtag_uart)如果采用USB Blaster,可以选择Jtag_uart。

之后再run就ok了!3)Error: Can't compile duplicate declarations of entity "count3" into library "work"此错误一般是原理图文件的名字和图中一个器件的名字重复所致,所以更改原理图文件的名字保存即可。

Quartus常见问题

Quartus常见错误1.Error (10028): Can't resolve multiple constant drivers for net ……解析:不能在两个以上always内对同一变量赋值,这个细节一般看书看资料会看到,但是编程时,就是没想到。

2.Error (10158): Verilog HDL Module Declaration error at clkseg.v(1): port"XXXX" is not declared as port解析:大意了,端口类型还没定义啊!3.Error (10110): variable "en" has mixed blocking and nonblocking ProceduralAssignments -- must be all blocking or all nonblocking assignments解析:en在程序中有时用非阻塞赋值,有时用阻塞赋值,这是禁止的。

在初学的时候,可能分得不是很清楚,所以在检查时,一定要一步步观察慢慢来。

4.Error (10161): Verilog HDL error at clkseg.v(36): object "count" is notdeclared解析:这个错误应该很明显啦,只要能读得懂。

5.Error (10170): Verilog HDL syntax error at clkseg.v(37) near text "***";expecting ";"解析:意思应该也很简单,就是检查的时候要细心点。

6.Error (10171): Verilog HDL syntax error at ir_ctrl.v(149) near end of file ;expecting an identifier, or "endmodule", or a parallel statement解析:最后上了endmodule。

QUARTUSII常见错误解决方法

QUARTUSII常见错误解决方法QUARTUS II版本:9.0FPGA型号:EP2C8Q208配置芯片:EPCS4SDRAM型号: HY57V28820HCT-HFLASH型号 :TE28F320J3之前已经接触QUARTUS II比较长的时间了,也遇到过不少问题,有些比较简单解决后就忘了,现在把能记得起来列在前面几个。

后面的是自己后续遇到的问题的集锦...1.多模块或多进程驱动同一信号Error (10028): Can't resolve multiple constant drivers for net "FLASH_A[7]" at led.v(32)用Verilog描述电路时,一个信号只能在一个进程中驱动,如果在多个进程中对其驱动的话将产生如上错误。

解决方法为可以另加一个信号,通过在另一个进程中监视这个信号做出相应的动作。

2.多功能管脚的设置在用FLASH分配完管脚后编译出现如下错误:Error: Can't place multiple pins assigned to pin location Pin_108 (IOC_X34_Y2_N0)Info: Fitter preparation operations ending: elapsed time is 00:00:00Error: Can't fit design in deviceError: Quartus II Fitter was unsuccessful. 2 errors, 0 warnings Error: Quartus II Full Compilation was unsuccessful. 4 errors, 56 warnings原因是不能分配给多功能管脚PIN_108。

这是由于PIN_108是一个多功能管脚,还有一个功能是nCEO,也是默认的功能。

如果要用它当普通IO,需要提前设置一下:assignments>device>device and pin options>dual-purpose pins 里面把nCEO设置成use as regular i/o就可以了。

QuartusII常见问题

QuartusII常见问题1) QuartusII对代码进行时序仿真时出现Error: Can't continue timing simulation because delay annotation information for design is missing.原因:如果只需要进行功能仿真,不全编译也是可以进行下去的,但时序仿真就必须进行全编译(即工具栏上的紫色实心三角符号那项)。

全仿真包括四个模块:综合器(Synthesis)、电路装配器(Fitter)、组装器(Assember)和时序分析器(Timing Analyzer),任务窗格中会有成功标志(对号)。

2) 在下载运行的时候,出现下面的错误:Warning: The JTAG cable you are using is not supported for Nios II systems.You may experience intermittent JTAG communicationfailures with this cable. Please use a USB Blaster revision B.在运行之前已经将.sof文件下载到开发板上面了,但是依然出现上面的问题。

解决:在配置的时候,在run之后,进行配置,选择target connection,在最后一项:NIOS II Terminal Communication Device中,要选择none (不要是Jtag_uart)如果采用USB Blaster,可以选择Jtag_uart。

之后再run就ok了!3)Error: Can't compile duplicate declarations of entity "count3" into library "work"此错误一般是原理图文件的名字和图中一个器件的名字重复所致,所以更改原理图文件的名字保存即可。

quartus编译时常见错误和警告

quartus编译时常见错误和警告编译常见错误和警告1~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~2在QuartusII 下进行编译和仿真的时候,会出现一堆warning ,有的可以忽略,有的却需要注意。

虽然按F1可以了解关于该警告的帮助,但有时候帮助解释的仍然不清楚,大家群策群力,把自己知道和了解的一些关于警告的问题都说出来讨论一下,免得后来的人走弯路。

1.Found clock-sensitive change during active clock edge at time on register ""原因:vector source file 中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

措施:编辑vector source file2.Verilog HDL assignment warning at :truncated value with size to match size of target (原因:在HDL 设计中对目标的位数进行了设定,如:reg[4:0]a ,而默认为32位,将位数裁定到合适的大小。

措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数。

3.All reachable assignments to data_out(10)assign '0',register removed by optimization 原因:经过综合器优化后,输出端口已经不起作用了。

4.Following 9pins have nothing,GND,or VCC driving datain port --changes to thisconnectivity may change fitting results results..原因:第9脚,空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。

Quartus常见错误分析Error

Quartus常见错误分析ErrorQuartus常见错误分析ErrorWarning: VHDL Process Statement warning at random.vhd(18): signal reset is in statement, but is not in sensitivity list----没把singal放到process()中2 Warning: Found pins ing as undefined clocks and/or memory enablesInfo: Assuming node CLK is an undefined clock-=-----可能是说设计中产⽣的触发器没有使能端3 Error:VHDL Interface Declaration error in clk_gen.vhd(29): interface object "clk_scan" of mode out cannot be read. Change object mode to buffer or inout.------信号类型设置不对,out当作buffer来定义4 Error:Node instance "clk_gen1" instantiates undefined entity "clk_gen"-------引⽤的例化元件未定义实体--entity "clk_gen"5 Warning: Found 2 node(s) in clock paths which may be acting as ripple and/or gated cl ocks -- node(s) analyzed as buffer(s) resulting in clock skewInfo: Detected ripple clock "clk_gen:clk_gen1|clk_incr" as bufferInfo: Detected ripple clock "clk_gen:clk_gen1|clk_scan" as buffer6 Warning: VHDL Process Statement warning at ledmux.vhd(15): signal or variable "datao ut" may not be assigned a new in every possible path through the Process Statement. Signal or variable " dataout" holds its previous in every path with no new assignment, which may create a combinational loo p in the current design.7 Warning: VHDL Process Statement warning at divider_10.vhd(17): signal "cnt" is read i nside the Process Statement but isn't in the Process Statement's sensivitity list-----缺少敏感信号8 Warning: No clock transition on "counter_bcd7:counter_counter_clk|q_sig[3]" register9 Warning: Reduced register "counter_bcd7:counter_counter_clk|q_sig[3]" with stuck clock port to stuck GND10 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "class[1]" with clock skew larger than data delay. See Compilation Report for details.11 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "sign" with clock skew larger than data delay. See Compilation Report for details.12 Error:VHDL error at counter_clk.vhd(90): actual port "class" of mode "in" cannot be associated with formal port "class" of mode "out"------两者不能连接起来13 Warning: Ignored node in vector source file. Can't find corresponding node name "clas s_sig[2]" indesign.------没有编写testbench⽂件,或者没有编辑输⼊变量的值 testbench⾥是元件申明和映射14 Error:VHDL Binding Indication error at freqdetect_top.vhd(19): port "class"in design entity doesnot have std_logic_vector type that is specified for the same generic in the associated com ponent---在相关的元件⾥没有当前⽂件所定义的类型15 Error:VHDL error at tongbu.vhd(16): can't infer register for signal "gate" because sign al does nothold its outside clock edge16 Warning: Found clock high time violation at 1000.0 ns on register"|fcounter|lpm_counter:temp_rtl_0|dffs[4]"17 Warning: Compiler packed, optimized or synthesized away node "temp[19]". Ignored ve ctor source filenode.---"temp[19]"被优化掉了18 Warning: Reduced register "gate~reg0" with stuck data_in port to stuck GND19 Warning: Design contains 2 input pin(s) that do not drive logicWarning: No output dependent on input pin "clk"Warning: No output dependent on input pin "sign"------输出信号与输⼊信号⽆关,20 Warning: Found clock high time violation at 16625.0 ns on register "|impulcomp|gate1"21 Error:VHDL error at impulcomp.vhd(19): can't implement clock enable condition speci fied using binaryoperator "or"22 Error:VHDL Association List error at period_counter.vhd(38): actual parameter assigned to formalparameter "alarm", but formal parameter is not declared-------连接表错误,形参"alarm"赋值给实参,形参没定义,可能是形参与实参的位置颠倒了,规定形参在实参之前。

自己整理的:学习verilogDHL问题笔记——Quartus常见错误

⾃⼰整理的:学习verilogDHL问题笔记——Quartus常见错误我初学verilog语⾔,很多细节都没注意,按着⾃⼰的思想就写了,编译的时候才发现各种问题。

这些都是我在学习中遇到的问题,还是很常见的。

1.Error (10028): Can't resolve multiple constant drivers for net ……解析:不能在两个以上always内对同⼀变量赋值,这个细节⼀般看书看资料会看到,但是编程时,就是没想到。

2.Error (10158): Verilog HDL Module Declaration error at clkseg.v(1): port "XXXX" is not declared as port解析:⼤意了,端⼝类型还没定义啊!3.Error (10110): variable "en" has mixed blocking and nonblocking Procedural Assignments -- must be all blocking or all nonblocking assignments解析:en在程序中有时⽤⾮阻塞赋值,有时⽤阻塞赋值,这是禁⽌的。

在初学的时候,可能分得不是很清楚,所以在检查时,⼀定要⼀步步观察慢慢来。

4.Error (10161): Verilog HDL error at clkseg.v(36): object "count" is not declared解析:这个错误应该很明显啦,只要能读得懂。

5.Error (10170): Verilog HDL syntax error at clkseg.v(37) near text "***"; expecting ";"解析:意思应该也很简单,就是检查的时候要细⼼点。

Quartus常见警告分析

Quartus常见警告分析1.Found clock-sensitive change during active clock edge at time<time> on register "<name>"原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

措施:编辑vector source file2.Verilog HDL assignment warning at <location>: truncatedwith size <number> to match size of target (<number>原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0] a;而默认为32位,将位数裁定到合适的大小措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数3.All reachable assignments to data_out(10) assign '0', registerremoved by optimization原因:经过综合器优化后,输出端口已经不起作用了4.Following 9 pins have nothing, GND, or VCC driving datain port --changes to this connectivity may change fitting results原因:第9脚,空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。

如果你的设计中这些端口就是这样用的,那便可以不理会这些warning5.Found pins ing as undefined clocks and/or memory enables原因:是你作为时钟的PIN没有约束信息。

quartus_错误警告分析

Quartus常见警告分析1.Found clock-sensitive change during active clock edge at time<time>on register"<name>"原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

措施:编辑vector source file2.Verilog HDL assignment warning at<location>:truncatedwith size<number>to match size of target(<number>原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0]a;而默认为32位,将位数裁定到合适的大小措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数3.All reachable assignments to data_out(10)assign'0',registerremoved by optimization原因:经过综合器优化后,输出端口已经不起作用了4.Following9pins have nothing,GND,or VCC driving datain port--changes to this connectivity may change fitting results原因:第9脚,空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。

如果你的设计中这些端口就是这样用的,那便可以不理会这些warning5.Found pins ing as undefined clocks and/or memory enables原因:是你作为时钟的PIN没有约束信息。

Quartus常见警告和错误集锦

我们一起爱~主页博客相册个人档案好友查看文章FPGA错误集锦2009-05-07 10:151) QuartusII对代码进行时序仿真时出现Error: Can't continue timing simulation because delay annotation information for design is missing.原因:如果只需要进行功能仿真,不全编译也是可以进行下去的,但时序仿真就必须进行全编译(即工具栏上的紫色实心三角符号那项)。

全仿真包括四个模块:综合器(Synthesis)、电路装配器(Fitter)、组装器(Assember)和时序分析器(Timing Analyzer),任务窗格中会有成功标志(对号)。

2) 在下载运行的时候,出现下面的错误:Warning: The JTAG cable you are using is not supported for Nios II systems.You may experience intermittent JTAG communicationfailures with this cable. Please use a USB Blaster revision B.在运行之前已经将.sof文件下载到开发板上面了,但是依然出现上面的问题。

解决:在配置的时候,在run之后,进行配置,选择target connection,在最后一项:NIOS II Terminal Communication Device中,要选择none(不要是Jtag_uart)如果采用USB Blaster,可以选择Jtag_uart。

之后再run就ok了!3)Error: Can't compile duplicate declarations of entity "count3" into library "work"此错误一般是原理图文件的名字和图中一个器件的名字重复所致,所以更改原理图文件的名字保存即可。

Quartus常见警告和错误

Quartus常见警告和错误【转】2009-08-07 14:00Quartus常见警告和错误1 Warning: VHDL Process Statement warning at random.vhd(18): signal reset is in statement, but is not in sensitivity list----没把singal放到process()中2 Warning: Found pins ing as undefined clocks and/or memory enables Info: Assuming node CLK is an undefined clock-=-----可能是说设计中产生的触发器没有使能端3 Error: VHDL Interface Declaration error in clk_gen.vhd(29): interface object "clk_scan" of mode out cannot be read. Change object mode to buffer or inout.------信号类型设置不对,out当作buffer来定义4 Error: Node instance "clk_gen1" instantiates undefined entity "clk_gen" -------引用的例化元件未定义实体--entity "clk_gen"5 Warning: Found 2 node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s) analyzed as buffer(s) resulting in clock skewInfo: Detected ripple clock "clk_gen:clk_gen1|clk_incr" as buffer Info: Detected ripple clock "clk_gen:clk_gen1|clk_scan" as buffer6 Warning: VHDL Process Statement warning at ledmux.vhd(15): signal or variable "dataout" may not be assigned a new in every possible path through the Process Statement. Signal or variable "dataout" holds its previous in every path with no new assignment, which may create a combinational loop in the current design.7 Warning: VHDL Process Statement warning at divider_10.vhd(17): signal "cnt" is read inside the Process Statement but isn't in the Process Statement's sensivitity list-----缺少敏感信号8 Warning: No clock transition on"counter_bcd7:counter_counter_clk|q_sig[3]"register9 Warning: Reduced register "counter_bcd7:counter_counter_clk|q_sig[3]" with stuck clock port to stuck GND10 Warning: Circuit may not operate. Detected 1 non-operational path(s)clocked by clock "class[1]" with clock skew larger than data delay. See Compilation Report for details.11 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "sign" with clock skew larger than data delay. See Compilation Report for details.12 Error: VHDL error at counter_clk.vhd(90): actual port "class" of mode "in"cannot be associated with formal port "class" of mode "out"------两者不能连接起来13 Warning: Ignored node in vector source file. Can't find corresponding node name "class_sig[2]" in design.------没有编写testbench文件,或者没有编辑输入变量的值 testbench里是元件申明和映射14 Error: VHDL Binding Indication error at freqdetect_top.vhd(19): port "class"in design entity does not have std_logic_vector type that is specified for thesame generic in the associated component---在相关的元件里没有当前文件所定义的类型15 Error: VHDL error at tongbu.vhd(16): can't infer register for signal "gate"because signal does not hold its outside clock edge16 Warning: Found clock high time violation at 1000.0 ns on register "|fcounter|lpm_counter:temp_rtl_0|dffs[4]"17 Warning: Compiler packed, optimized or synthesized away node "temp[19]".Ignored vector source file node.---"temp[19]"被优化掉了18 Warning: Reduced register "gate~reg0" with stuck data_in port to stuck GND19 Warning: Design contains 2 input pin(s) that do not drive logic Warning: No output dependent on input pin "clk"Warning: No output dependent on input pin "sign"------输出信号与输入信号无关,20 Warning: Found clock high time violation at 16625.0 ns on register"|impulcomp|gate1"21 Error: VHDL error at impulcomp.vhd(19): can't implement clock enable condition specified using binary operator "or"22 Error: VHDL Association List error at period_counter.vhd(38): actual parameter assigned to formal parameter "alarm", but formal parameter is not declared-------连接表错误,形参"alarm"赋值给实参,形参没定义,可能是形参与实参的位置颠倒了,规定形参在实参之前。

QUARTUS 7常见错误剖析

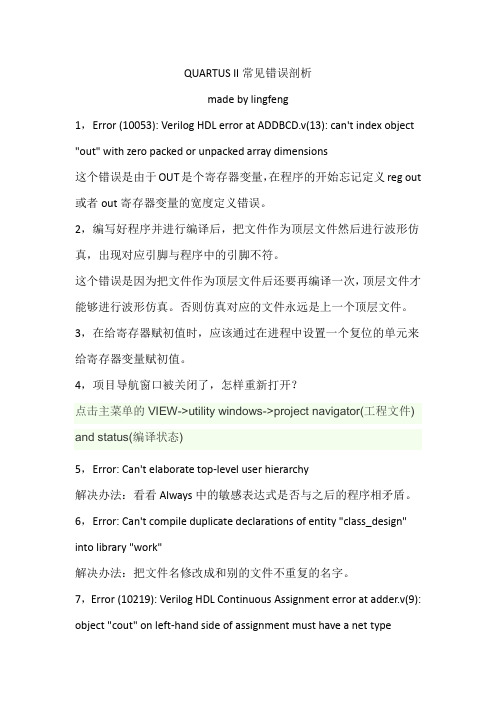

QUARTUS II常见错误剖析made by lingfeng1,Error (10053): Verilog HDL error at ADDBCD.v(13): can't index object "out" with zero packed or unpacked array dimensions这个错误是由于OUT是个寄存器变量,在程序的开始忘记定义reg out 或者out寄存器变量的宽度定义错误。

2,编写好程序并进行编译后,把文件作为顶层文件然后进行波形仿真,出现对应引脚与程序中的引脚不符。

这个错误是因为把文件作为顶层文件后还要再编译一次,顶层文件才能够进行波形仿真。

否则仿真对应的文件永远是上一个顶层文件。

3,在给寄存器赋初值时,应该通过在进程中设置一个复位的单元来给寄存器变量赋初值。

4,项目导航窗口被关闭了,怎样重新打开?点击主菜单的VIEW->utility windows->project navigator(工程文件) and status(编译状态)5,Error: Can't elaborate top-level user hierarchy解决办法:看看Always中的敏感表达式是否与之后的程序相矛盾。

6,Error: Can't compile duplicate declarations of entity "class_design" into library "work"解决办法:把文件名修改成和别的文件不重复的名字。

7,Error (10219): Verilog HDL Continuous Assignment error at adder.v(9): object "cout" on left-hand side of assignment must have a net type错误原因:变量的定义类型错误。

quartuserror (199014)

Quartus是一种用于FPGA设计的集成开发环境(IDE),由英特尔公司开发。

在使用Quartus进行FPGA设计的过程中,用户可能会遇到各种错误代码,其中最常见的就是xxx错误代码。

本文将对这一错误代码进行详细介绍,并提供解决办法。

1. 错误代码xxx的意义错误代码xxx通常表示在编译或者仿真过程中出现了一些问题。

这个问题可能涉及到用户的设计文件,也可能是与Quartus本身相关的。

2. 可能引发错误代码xxx的原因2.1 设计文件错误:设计文件中可能存在语法错误、逻辑错误或者其他与设计规范不符的情况,导致无法顺利编译或者仿真。

2.2 Quartus本身的问题:Quartus软件本身可能存在一些Bug或者不稳定的情况,导致出现xxx错误代码。

2.3 其他未知因素:在某些情况下,错误代码xxx的具体原因可能比较复杂,需要进一步的排查和分析。

3. 解决办法3.1 检查设计文件:用户需要仔细检查设计文件,确保其中没有语法错误、逻辑错误等问题。

可以尝试对设计文件进行逐步的简化,以确定具体是哪一部分代码引发了错误代码xxx。

3.2 更新Quartus版本:如果怀疑是Quartus本身的问题,用户可以尝试更新到最新版本的Quartus软件,看是否可以解决这个问题。

3.3 交流技术支持:如果以上方法都无法解决问题,用户可以选择向Quartus冠方或者相关的技术支持渠道寻求帮助。

他们可能会提供一些针对性的解决方案或者建议。

4. 避免错误代码xxx的方法4.1 编写规范的设计代码:在进行FPGA设计的过程中,用户可以遵循一些编码规范,编写清晰、规范的设计代码,以减少出现错误代码xxx 的可能性。

4.2 注意Quartus的稳定性:在使用Quartus软件的过程中,用户可以注意软件的稳定性表现,及时反馈一些异常情况给Quartus冠方,以帮助他们改进软件的质量。

总结:错误代码xxx是Quartus软件中常见的一个错误代码,通常表示在编译或者仿真过程中出现了一些问题。

QuartusII常见错误分析

bjxiong 发表于 - 2007-8-24 10:43:00

0

推荐1 Warning: VHDL Process Statement warning at random.vhd(18): signal reset is in statement, but is not in sensitivity list

12 Error: VHDL error at counter_clk.vhd(90): actual port "class" of mode "in" cannot be associated with formal port "class" of mode "out"

------两者不能连接起来

26 Error: Can't resolve multiple constant drivers for net "datain_reg[22]" at shift_reg.vhd(19)

27 can't infer register for signal "num[0]" because signal does not hold its outside clock edge

-------连接表错误,形参"alarm"赋值给实参,形参没定义,可能是形参与实参的位置颠倒了,规定形参在实参之前。

23 Error: Ignored construct behavier at period_counter.vhd(15) because of previous errors

Info: Detected ripple clock "clk_gen:clk_gen1|clk_incr" as buffer

quartus编译时常见错误和警告

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~1编译常见错误和警告~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~2在QuartusII 下进行编译和仿真的时候,会出现一堆warning ,有的可以忽略,有的却需要注意。

虽然按F1可以了解关于该警告的帮助,但有时候帮助解释的仍然不清楚,大家群策群力,把自己知道和了解的一些关于警告的问题都说出来讨论一下,免得后来的人走弯路。

1.Found clock-sensitive change during active clock edge at time <time>on register "<name>"原因:vector source file 中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

措施:编辑vector source file2.Verilog HDL assignment warning at <location>:truncated value with size <number>to match size of target (<number>原因:在HDL 设计中对目标的位数进行了设定,如:reg[4:0]a ,而默认为32位,将位数裁定到合适的大小。

措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数。

3.All reachable assignments to data_out(10)assign '0',register removed by optimization 原因:经过综合器优化后,输出端口已经不起作用了。

4.Following 9pins have nothing,GND,or VCC driving datain port --changes to thisconnectivity may change fitting results results..原因:第9脚,空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。

Quartus常见错误说明

quartus的功能仿真出错怎么办Error: Run Generate Functional Simulation Netlist (quartus_map and_gate --generate_functional_sim_netlist) to generate functional simulation netlist for top level entity "and_gate" before running the Simulator (quartus_sim)一般如果出现这些错误信息,可以作如下处理功能仿真出错你要运行下processing->Generate Functional Simulation Netlist 下再功能仿真就没有问题一、Quartus 中仿真时出现no simulation input file assignment specify 解决方法翻译成中文就是仿真文件没有被指定,要仿真的话先要建一个仿真文件: file -> new -> 选择Other file 选项卡-> Vector Waveform File 然后把输入输出端口加进去,再设置输入的信号,保存,就可以仿真了。

如果你之前已经建立过了,就打开assignments->settings->simulator settings 看里面的有个文本框simulation input 里面是否为空,为空的话就要找到你所建立的Vector Waveform File 文件,是以*.VWF 结尾的,如果没找到,你又以为你建立了Vector Waveform File ,很可能粗心的你还没保存Vector Waveform File ,保存了才会在project 里面找到。

找到之后进行仿真,如果是functional simulation,要做processing>generate functional simulation netlist..不然会出现:Error: Run Generate Functional Simulation Netlist (quartus_map bmg_control --generate_functional_sim_netlist) to generate functional simulation netlist for top level entity bmg_control before running the Simulator (quartus_sim)之类的错误。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

7 Warning: VHDL Process Statement warning at divider_10.vhd(17): signal "cnt" is read inside the Process

Statement but isn't in the Process Statement's sensivitity list

cannot be read. Change object mode to buffer or inout.

------信号类型设置不对,out当作buffer来定义

4 Error: Node instance "clk_gen1" instantiates undefined entity "clk_gen"

-------引用的例化元件未定义实体--entity "clk_gen"

5 Warning: Found 2 node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s)

analyzed as buffer(s) resulting in clock skew

-------同一进程中含有两个或多个if(edge)条件,(一个进程中之能有一个时钟沿)

26 Error: Can't resolve multiple constant drivers for net "datain_reg[22]" at shift_reg.vhd(19)

27 can't infer register for signal "num[0]" because signal does not hold its outside clock edge

28Error: Can't elaborate top-level user hierarchy

29 Error: Can't resolve multiple constant drivers for net "cs_in" at led_key.vhd(32)

----------有两个以上赋值语句,不能确定“cs_in”的值,

--------因为前一个错误而导致的错误

24 Error: VHDL error at period_counter.vhd(38): type of identifier "alarm" does not agree with its usage

as std_logic type

11 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "sign" with

clock skew larger than data delay. See Compilation Report for details.

Info: Detected ripple clock "clk_gen:clk_gen1|clk_incr" as buffer

Info: Detected ripple clock "clk_gen:clk_gen1|clk_scan" as buffer

6 Warning: VHDL Process Statement warning at ledmux.vhd(15): signal or variable "dataout" may not be

21 Error: VHDL error at impulcomp.vhd(19): can't implement clock enable condition specified using binary

operator "or"

22 Error: VHDL Association List error at period_counter.vhd(38): actual parameter assigned to formal

Warning: No output dependent on input pin "clk"

Warning: No output dependent on input pin "sign"

------输出信号与输入信号无关,

20 Warning: Found clock high time violation at 16625.0 ns on register "|impulcomp|gate1"

GND

10 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "class[1]" with

clock skew larger than data delay. See Compilation Report for details.

30 Warning: Ignored node in vector source file. Can't find corresponding node name "over" in design.

---------------在源文件中找不到对应的节点“over”。

31 Error: Can't access JTAG chain

14 Error: VHDL Binding Indication error at freqdetect_top.vhd(19): port "class" in design entity does

not have std_logic_vector type that is specified for the same generic in the associated component

-----缺少敏感信号

8 Warning: No clock transition on "counter_bcd7:counter_counter_clk|q_sig[3]" register

9 Warning: Reduced register "counter_bcd7:counter_counter_clk|q_sig[3]" with stuck clock port to stuck

Warning: VHDL Process Statement warning at random.vhd(18): signal reset is in statement, but is not in

sensitivity list

----没把singal放到process()中

3 Error: VHDL Interface Declaration error in clk_gen.vhd(29): interface object "clk_scan" of mode out

--------"alarm"的定义类型与使用的类型不一致

25 Error: VHDL error at shift_reg.vhd(24): can't synthesize logic for statement with conditions that

test for the edges of multiple clocks

1.

Warning: Found pins ing as undefined clocks and/or memory enables

Info: Assuming node CLK is an undefined clock

-=-----可能是说设计中产生的触发器没有使能端

2 ]"被优化掉了

18 Warning: Reduced register "gate~reg0" with stuck data_in port to stuck GND

19 Warning: Design contains 2 input pin(s) that do not drive logic

13 Warning: Ignored node in vector source file. Can't find corresponding node name "class_sig[2]" in

design.

------没有编写testbench文件,或者没有编辑输入变量的值 testbench里是元件申明和映射

16 Warning: Found clock high time violation at 1000.0 ns on register

"|fcounter|lpm_counter:temp_rtl_0|dffs[4]"

17 Warning: Compiler packed, optimized or synthesized away node "temp[19]". Ignored vector source file

12 Error: VHDL error at counter_clk.vhd(90): actual port "class" of mode "in" cannot be associated with