数字信号处理算法逻辑 第九章

数字信号处理第9章答案

滤波器? 为什么?

(该题21分, (1)15分, (2)6分) (自测时间2.5~3小时, 满分100分)

第 9 章

自

测

题

题9图

第 9 章

自

测

题

9.4 自 测 题 (四)

1. 设

0.19 X ( z) (1 0.9 z )(1 0.9 z 1 )

试求与X(z)对应的所有可能的序列x(n)。 (该题12分) 2. 假设x(n)=R8(n), h(n)=R4(n)。 (1)令y(n)=x(n)*h(n), 求y(n)。 要求写出y(n)的表达式, 并画出y(n)的波形。

ˆ (1) 写出 x (t ) 的表达式;

(2) 求出理想低通滤波器的输出信号y(t)。

(该题14分 , (1)6分, (2)8分) 4. 假设线性非时变系统的单位脉冲响应h(n)和输入信号

x(n)分别用下式表示:

h(n)=R8(n), x(n)=0.5nR8(n) (1) 计算并图示该系统的输出信号y(n);

y1(n)=IDFT[Y(k)]

(FFT计算作为一个框图), 并注明FFT的最小计算区间N

等于多少。 (该题22分, (1) 7分, (2) 7分, (3) 8分)

第 9 章

自

测

题

5. 二阶归一化低通巴特沃斯模拟滤波器的系统函数为

H a (s) 1 s 2 2s 1

采样间隔T=2 s, 为简单起见, 令3 dB截止频率Ωc=1 rad/s, 用 双线性变换法将该模拟滤波器转换成数字滤波器H(z), 要求: (1) 求出H(z); (2) 计算数字滤波器的3 dB截止频率; (3) 画出数字滤波器的直接型结构图。 (该题15分, (1) 5分, (2) 5分, (3) 5分)

数字信号处理 第九章多采样率数字信号处理

y(0) 1

2

Y (e jy

)dy

1

2

I

I

CX

(e

jIy

)d

y

C

2 I

X

(e jx

)dx

C I

x(0)

C I

*

时域关系

x(n)

v(m)

y(m) xa (mTy )

I

hI (m)

y(m) v(m) hI (m) hI (m k)v(k) k v(kI ) x(k), v(k) 0, k 0, I , 2I ,

I

y

2

*

如何实现 加滤波器

y(m) xa (mTy ) Ty Tx I

H

I

(e

j y

)

C

,

0,

y I I y

y x I

镜像滤波器

Y

(e

j y

)

CV 0,

(e

j y

) I

CX (e jIy

y

),

y I

C=?

x(n)

v(m)

y(m) xa (mTy )

I

hI (m)

*

*

x(n) X (e jw )

hD (n)

v(n)

H D (e j ) V (e jw )

D

y(n) Y (e jw )

H

D

(e

j

)

1,

0,

D D

V (z) Hd (z)X (z)

Y (e jy )

1

D1

j (y 2 k )

V (e D D )

D k0

1 D1

j (y 2 k )

数字信号处理9

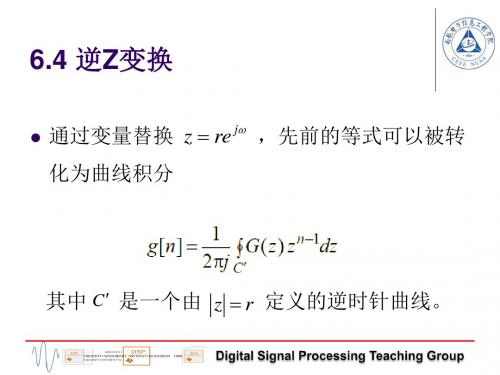

6.4 逆Z变换

现在

及

6.4 逆Z变换

得到

因此上式的逆变换为

6.4 逆Z变换

多重极点:若 G ( z ) 是有多重极点的真分式, 则部分分式展开的形式稍微有所不同。

例如,若在

z v

处有 L 重极点,而其他

1 N L N L 个极点是在 z 的单极点,

6.4 逆Z变换

例:考虑

用分子对分母进行长除,得到

从而有

6.4 逆Z变换

可以用函数impz来计算有理Z变换 G ( z ) 的逆。

函数计算 G ( z ) 的幂级数展开的系数。

系数的个数可以确定或自动获得。

6.5 Z变换定理

6.5 Z变换定理

例:考虑双边序列

记 和

及 分别是它们的Z变换。

g[n] [G( z) zn1在C内的极点的留数]

上面的公式需要在所有n值得范围内计算,在这里

我们没有对其进行展开计算。

6.4 逆Z变换

部分分式展开法

具有因果逆变换 g[n]的有理Z变换G ( z ) 的收 敛域是某个圆的外部。

此时,用部分分式展开形式表示G ( z ),然后

对展开式中每个简单项的逆变换求和来

用来实现逆 运算。

6.4 逆Z变换

对于因果序列,Z变换 G ( z ) 可以展开成 z 1 的幂级 数。

在该级数展开式中,乘以项 z

个样本 g[n] 。

n

的系数就是第 n

对于因果有理 G ( z ) ,将分子和分母表示为 幂级数将会很方便。

数字信号处理DSP9-2

p

E e n R e n 1

2 p 1 p p 1 2

E e n p

E e n 1 R e n

2 p 1 p p 1 2

优化条件

2 2 E e p n E e p n 0 R p

一维卡尔曼滤波

设含有噪声的信号测量值与信号估计值分 别采用以下模型表达:

xn c sn wn sn a sn 1 vn 1

a, c 为与时间无关的常数; w, v 为方差不随时间变化的白噪声。

一维卡尔曼滤波

建立一维卡尔曼方程如下:

sn an sn 1 bn xn

格型滤波

例:3阶系统

1 0.5 z 1 0.5 z 2 z 3 H z 1 1.8 z 1 1.4 z 2 0.4 z 3

c3 b3 3 1 c2 b3 2 c3a3 1 1.3 c1 b3 1 c2 a2 1 c3a3 2 1 c0 b3 0 c1a1 1 c2 a2 2 c3a3 3 0.8

k 1 p 1

格型滤波

P阶后向预测

P阶前向预测

格型滤波

误差递推关系与格型滤波结构

e n e 1 n R p e 1 n Fra bibliotek 1 p p p

e n e 1 n 1 R p e 1 n p p p

格型滤波

最小均方优化设计: 选择反射系数使前后向均方误差之和为最小 前向均方误差 后向均方误差

n p p 1 2 p 1 2 N 1

R p N 1

n p

e n e n 1

格型滤波

第9章维纳滤波PPT课件

t

R x s(t) h (t)R x x ()d, t

21.12.2023

.

23

做变量替换,t-=,t-=,得到:

R x s() 0 h ()R x x( )d ,0

或:

R x s() 0 h ()R x x( )d ,0

此时:

L M S R s s(0 ) 0h ()R x s()d

21.12.2023

.

31

H(ej)

0 1

Sss()

Sss()Snn()

Sss() 0,Snn() 0 Sss() 0,Snn() 0

Sss() 0,Snn() 0

21.12.2023

.

32

H(ej) 1

Sss(ej) Snn(ej)

0

非因果维纳滤波器的幅频特性

21.12.2023

.

33

例9.4 设信号的自相关函数是: R ss(m ) 0 .8 m m 0 , 1 , 2 , 噪声是白色的

E [d(t)d ˆ(t)]2m in

• 又限定估计 dˆ ( t ) 是由观察x(t)经线性滤波

器h(t)得出的:

d ˆ(t)x(t)*h(t)tf x()h(t)d t0

21.12.2023

.

11

最优线性均方估计的选取原则是使估计

误差 e(t)d(t)dˆ(t) 与所有的观察值

x(), ∊[t0,tf]正交,也就是说,如果 对每一个 ∊[t0,tf]都有:

21.12.2023

.

17

由于Rss‘(t)是奇函数,所以Rss‘(0)=0 把上式化简得到:

R ss (a ) a R ss (0 ) 0 R s's ( a ) b R s's'( 0 ) 0 故得到:

数字信号处理的基本原理及算法

数字信号处理的基本原理及算法数字信号处理(DSP)是指对模拟信号进行数字化、处理、压缩及重构等一系列的处理过程。

它以数字方式处理信号,并在数字计算机上实现各种算法和数学模型。

数字信号处理在现代通信、音频、视频、雷达、医疗成像、自动控制、电力电子、金融等领域都有着广泛的应用。

数字信号的获取数字信号获取是指将模拟信号进行采样,将连续的模拟信号转换成离散的数字信号。

采样的方法有脉冲采样和自适应采样两种。

脉冲采样是指将连续的模拟信号按照一定的时间间隔进行采样,将其转换成离散的数字信号。

采样的频率决定了采样过程中每个样点之间的时间间隔,也就是采样周期。

采样周期与采样频率成反比例关系,采样频率越高,则采样周期越短,采样到的波形越精细,但也会增加数字信号处理的运算量。

采样定理告诉我们,只要采样频率大于原始信号最高频率的两倍,则可以通过数字处理重建出原始信号。

自适应采样是一种比较高级的采样方法,它通过自适应地调整采样频率和采样周期来抓住波形的特征。

比如声音信号中,人的听力范围一般在20Hz-20kHz之间,对于这种频率范围内的声音,可以采用高速的采样周期得到精细的波形图,而对于较低或较高的频率信号,则可以采用较长的采样周期,用较少的采样点完成分析。

数字信号处理算法数字信号处理算法包括滤波、傅里叶变换、小波变换、自适应滤波、自适应调节、频谱分析、时域分析、波形分析等。

滤波是对数字信号进行处理的一个基本算法,它主要是去除数字信号中的噪声和干扰。

根据滤波器的特性,滤波器可以分为低通滤波器、高通滤波器、带通滤波器和带阻滤波器等。

低通滤波器主要是去掉高频成分,高通滤波器主要是去掉低频成分,带通滤波器可以去掉高频和低频部分,只保留某个频率范围的成分,而带阻滤波器则可以去掉某个频率范围的成分。

傅里叶变换是将一个时间域函数变换到其对应的频率域函数的一种方法。

对于一个周期信号,可以通过傅里叶级数展开成多个正弦波的叠加形式。

对于非周期信号,可以通过傅里叶积分转换到频率域。

数字信号处理:理论、算法与应用

数字信号处理:理论、算法与应用第一章:引言1.1 数字信号处理的背景和意义1.2 数字信号处理的基本概念和原理1.3 本书的结构和内容安排第二章:离散时间信号与系统2.1 离散时间信号的表示与描述2.2 离散时间系统的表示与描述2.3 离散时间系统的性质与分类2.4 离散时间系统的时域分析方法2.5 离散时间系统的频域分析方法2.6 离散时间系统的稳定性分析第三章:离散傅里叶变换与频谱分析3.1 离散傅里叶变换的定义与性质3.2 离散傅里叶变换的计算方法3.3 离散傅里叶变换的频谱分析应用3.4 快速傅里叶变换算法及其应用3.5 离散余弦变换及其应用第四章:数字滤波器设计与实现4.1 滤波器的基本概念和分类4.2 FIR滤波器的设计方法与实现4.3 IIR滤波器的设计方法与实现4.4 实时数字滤波器的实现技术4.5 系统识别与自适应滤波第五章:时频分析与时频变换5.1 时频分析的基本概念和方法5.2 短时傅里叶变换与连续小波变换5.3 离散小波变换与小波包变换5.4 小波分析与小波变换的应用5.5 时间频率分析与多尺度分析第六章:数字信号处理系统设计与实现6.1 数字信号处理系统的基本结构和功能6.2 数字信号处理器与运算器的选择与设计6.3 数字信号处理系统的接口与通信6.4 数字信号处理系统的实时性与稳定性6.5 数字信号处理系统的性能评估与优化第七章:语音信号处理与音频编解码7.1 语音信号的特点与分析方法7.2 语音信号的编码与解码算法7.3 音频信号的特点与处理方法7.4 音频编解码的原理与算法7.5 语音信号处理与音频编解码的应用第八章:图像与视频信号处理8.1 数字图像的表示与处理方法8.2 图像增强与滤波算法8.3 图像压缩与编码技术8.4 视频信号的表示与处理方法8.5 视频编码与解码的原理与算法第九章:数字信号处理在通信系统中的应用9.1 数字调制与解调技术9.2 信道均衡与信号检测算法9.3 多址信号处理与多用户检测9.4 自适应滤波与信道估计算法9.5 数字信号处理在通信系统中的应用案例第十章:数字信号处理在雷达与遥感中的应用10.1 雷达信号处理与目标检测算法10.2 雷达信号的距离测量与速度估计10.3 雷达信号的角度测量与波束形成10.4 遥感图像处理与目标识别算法10.5 遥感信号处理在地理信息系统中的应用第十一章:数字信号处理在生物医学工程中的应用11.1 生物医学信号的特点与分析方法11.2 心电信号处理与心律失常检测11.3 脑电信号处理与脑电图分析11.4 生物医学图像处理与医学图像分析11.5 生物医学信号处理在疾病诊断中的应用第十二章:数字信号处理的未来发展与趋势12.1 数字信号处理技术的发展历程与趋势12.2 人工智能与机器学习在数字信号处理中的应用12.3 量子计算与量子信号处理的前沿技术12.4 数字信号处理在物联网与智能系统中的应用12.5 数字信号处理技术的挑战与展望结语参考文献。

matlab在数字信号处理中的应用(第2版)课件第九章

1-5 小波分析在信号处理中的应用

9.2 小波变换

为了克服傅立叶变换没有任何局部化特性 和短时傅立叶变换固定分辨率的缺陷,希望 用于信号分解的基函数是持续时间很短的高 频函数和持续时间很长的低频函数。严格地 说,就是要求这些基函数具有足够的光滑性, 函数本身及其倒数在无穷远处速降,具有紧 支撑集和高阶消失矩,即小波基函数。

1-16 小波分析在信号处理中的应用

9.6 基于小波的信号消噪处理和压缩处理 信号的小波压缩处理和消噪处理在本质上是相同的,都是 在小波分解域上进行域值处理。其二者的区别主要在于阈值的 选择算法不同,既可以使用全局阈值,也可使用自适应阈值。 小波分析工具箱中用于信号压缩处理和消噪处理的函数如表96所示。

1-15 小波分析在信号处理中的应用

9.6 基于小波的信号消噪处理和压缩处理

用一维小波之所以能够对信号进行压缩,是因为 一个有规律的信号可以用一个数据量很小的低频系数 和几个高频系数来精确的逼近。用一维小波对信号进 行压缩的一般步骤为: (1) 进行信号的小波分解; (2) 将高频系数进行阈值量化处理; (3) 对量化后的系数进行小波重构; 对信号进行比较有效的压缩主要有两种方法。一 种方法是对信号进行小波尺度的扩展,采用全局阈值 进行压缩,相对简单;另一种方法是根据每一层分解 后的效果来确定每一层所采用的不同的阈值,此种方 法相对复杂一些,但是效果要相对好一些。

数字信号处理教案

数字信号处理教案第一章:数字信号处理概述1.1 数字信号处理的概念介绍数字信号处理的定义和特点解释信号的分类和数字信号的优势1.2 数字信号处理的发展历程回顾数字信号处理的发展历程和重要里程碑介绍数字信号处理的重要人物和贡献1.3 数字信号处理的应用领域概述数字信号处理在通信、音频、图像等领域的应用举例说明数字信号处理在实际应用中的重要性第二章:离散时间信号处理基础2.1 离散时间信号的概念介绍离散时间信号的定义和特点解释离散时间信号与连续时间信号的关系2.2 离散时间信号的运算介绍离散时间信号的基本运算包括翻转、平移、求和等给出离散时间信号运算的示例和应用2.3 离散时间系统的特性介绍离散时间系统的概念和特性解释离散时间系统的因果性和稳定性第三章:数字滤波器的基本概念3.1 数字滤波器的定义和作用介绍数字滤波器的定义和其在信号处理中的作用解释数字滤波器与模拟滤波器的区别3.2 数字滤波器的类型介绍不同类型的数字滤波器包括FIR、IIR、IIR 转换滤波器等分析各种类型数字滤波器的特点和应用场景3.3 数字滤波器的设计方法介绍数字滤波器的设计方法包括窗函数法、插值法等给出数字滤波器设计的示例和步骤第四章:离散傅里叶变换(DFT)4.1 离散傅里叶变换的定义和原理介绍离散傅里叶变换的定义和原理解释离散傅里叶变换与连续傅里叶变换的关系4.2 离散傅里叶变换的性质介绍离散傅里叶变换的性质包括周期性、对称性等给出离散傅里叶变换性质的证明和示例4.3 离散傅里叶变换的应用概述离散傅里叶变换在信号处理中的应用包括频谱分析、信号合成等举例说明离散傅里叶变换在实际应用中的重要性第五章:快速傅里叶变换(FFT)5.1 快速傅里叶变换的定义和原理介绍快速傅里叶变换的定义和原理解释快速傅里叶变换与离散傅里叶变换的关系5.2 快速傅里叶变换的算法介绍快速傅里叶变换的常用算法包括蝶形算法、Cooley-Tukey算法等给出快速傅里叶变换算法的示例和实现步骤5.3 快速傅里叶变换的应用概述快速傅里叶变换在信号处理中的应用包括频谱分析、信号合成等举例说明快速傅里叶变换在实际应用中的重要性第六章:数字信号处理中的采样与恢复6.1 采样定理介绍采样定理的定义和重要性解释采样定理在信号处理中的应用6.2 信号的采样与恢复介绍信号采样与恢复的基本概念解释理想采样器和实际采样器的工作原理6.3 信号的重建与插值介绍信号重建和插值的方法解释插值算法的原理和应用第七章:数字信号处理中的离散余弦变换(DCT)7.1 离散余弦变换的定义和原理介绍离散余弦变换的定义和原理解释离散余弦变换与离散傅里叶变换的关系7.2 离散余弦变换的应用概述离散余弦变换在信号处理中的应用包括图像压缩、信号分析等举例说明离散余弦变换在实际应用中的重要性7.3 离散余弦变换的快速算法介绍离散余弦变换的快速算法包括8x8 DCT算法等给出离散余弦变换快速算法的示例和实现步骤第八章:数字信号处理中的小波变换8.1 小波变换的定义和原理介绍小波变换的定义和原理解释小波变换与离散傅里叶变换的关系8.2 小波变换的应用概述小波变换在信号处理中的应用包括图像去噪、信号分析等举例说明小波变换在实际应用中的重要性8.3 小波变换的快速算法介绍小波变换的快速算法包括Mallat算法等给出小波变换快速算法的示例和实现步骤第九章:数字信号处理中的自适应滤波器9.1 自适应滤波器的定义和原理介绍自适应滤波器的定义和原理解释自适应滤波器在信号处理中的应用9.2 自适应滤波器的设计方法介绍自适应滤波器的设计方法包括最小均方误差法等给出自适应滤波器设计的示例和步骤9.3 自适应滤波器的应用概述自适应滤波器在信号处理中的应用包括噪声抑制、信号分离等举例说明自适应滤波器在实际应用中的重要性第十章:数字信号处理的综合应用10.1 数字信号处理在通信系统中的应用介绍数字信号处理在通信系统中的应用包括调制解调、信道编码等分析数字信号处理在通信系统中的重要性10.2 数字信号处理在音频处理中的应用介绍数字信号处理在音频处理中的应用包括声音合成、音频压缩等分析数字信号处理在音频处理中的重要性10.3 数字信号处理在图像处理中的应用介绍数字信号处理在图像处理中的应用包括图像滤波、图像增强等分析数字信号处理在图像处理中的重要性10.4 数字信号处理在其他领域的应用概述数字信号处理在其他领域的应用包括生物医学信号处理、地震信号处理等分析数字信号处理在其他领域中的重要性重点和难点解析重点环节1:数字信号处理的概念和特点数字信号处理是对模拟信号进行数字化的处理和分析数字信号处理具有可重复性、精确度高、易于存储和传输等特点需要关注数字信号处理与模拟信号处理的区别和优势重点环节2:数字信号处理的发展历程和应用领域数字信号处理经历了从早期研究到现代应用的发展过程数字信号处理在通信、音频、图像等领域有广泛的应用需要关注数字信号处理的重要人物和里程碑事件重点环节3:离散时间信号处理基础离散时间信号是数字信号处理的基础需要关注离散时间信号的定义、特点和运算方法理解离散时间信号与连续时间信号的关系重点环节4:数字滤波器的基本概念和类型数字滤波器是数字信号处理的核心组件需要关注数字滤波器的定义、类型和设计方法理解不同类型数字滤波器的特点和应用场景重点环节5:离散傅里叶变换(DFT)离散傅里叶变换是数字信号处理中的重要工具需要关注离散傅里叶变换的定义、性质和应用理解离散傅里叶变换与连续傅里叶变换的关系重点环节6:快速傅里叶变换(FFT)快速傅里叶变换是离散傅里叶变换的优化算法需要关注快速傅里叶变换的定义、算法和应用理解快速傅里叶变换与离散傅里叶变换的关系重点环节7:数字信号处理中的采样与恢复采样与恢复是数字信号处理的关键环节需要关注采样定理的重要性、信号的采样与恢复方法理解插值算法的原理和应用重点环节8:数字信号处理中的离散余弦变换(DCT)离散余弦变换是数字信号处理中的另一种重要变换需要关注离散余弦变换的定义、应用和快速算法理解离散余弦变换与离散傅里叶变换的关系重点环节9:数字信号处理中的小波变换小波变换是数字信号处理的另一种重要变换需要关注小波变换的定义、应用和快速算法理解小波变换与离散傅里叶变换的关系重点环节10:数字信号处理中的自适应滤波器自适应滤波器是数字信号处理中的高级应用需要关注自适应滤波器的定义、设计方法和应用领域理解自适应滤波器在信号处理中的重要性本教案涵盖了数字信号处理的基本概念、发展历程、离散时间信号处理、数字滤波器、离散傅里叶变换、快速傅里叶变换、采样与恢复、离散余弦变换、小波变换、自适应滤波器等多个重点环节。

数字信号处理 第九章 图像分析与识别基础

9.1.2 特征分析模式

特征分析模式是根据景物特征实现视觉再现 的理论,其过程为提取特征、特征分类、 分析与识别几个步骤。 需要较大的特征运算。难度在于:1)如何对 于不同的对象选择适合的特征;2)如何确 定各特征之间的关系。

9.1.3 结构描述模式

结构描述模式通常用“图”表示,“图”的 节点代表对象景物的某一部分或某一特性; 节点之间的有向边说明各部分或个特性之 间的关系。

l(x,y)

l(x,y)

9.2.2 边缘检测法

5 Kirsch边缘检测算子

g ( x , y ) max

5 3 3

3 3 5

f ( x , y ) g i ( x , y ), i

5 0 3 3 0 5 5 5 3 3 3 3 3 3 3 5 5 5 3 0 3 3 0 3 5 5 5 3 3 3

9.1 视觉再认模式

本节主要从心理学的角度分析视觉对景物的 再认模式,以便从更深的层次理解图像分 析与识别方法的原理。视觉再认模式主要 有以下四种: 9.1.1 模板匹配模式 9.1.2 特征分析模式 9.1.3 结构描述模式 9.1.4 傅立叶模式

9.1.1 模板匹配模式

随着经验和阅历的增长,人的记忆中存在着代 表各种景物形态的“模版”,当人注视某景 物时,大脑神经中枢就会搜索存储在大脑中 的各个模版,并与看到的景物进行匹配,一 旦匹配一致或相关性最大,则认为再认成功。 模版匹配模式可以看作是一个决策过程。

第9章

图像分析与识别基础

概述

图像分析(image analysis)也叫景物分析(scenery analysis)或图像理解(image understand),其目 的是从图像中提取有用测度(useful estimate)、 数据或信息,生成非图的描述或表示,如数值、 符号等等,不局限于对给定景物的区域在一定数 目的已知类别里进行分类,更重要是要对千变万 化和难以预测的复杂景物加以描述,从中找出潜 藏在景物图像中的深层次信息,涉及到物体的前 景与背景、物体之间的关系以及人工智能技术等 问题。其研究的内容包括特征提取、符号描述、 景物匹配和识别等等。

数字信号处理教程—MATLAB释义与实现第09章

1 p(q) , q 2 2

语音量化噪声的改善

用分贝来度量的噪声均方值为: 2 2 N 10 log E 10 log 6 N 10.8 dB(9.2.4) 12 可以看出,上述的量化器每增加一位,量化噪声 减小6dB,高质量语音要求每个样本至少量化 为12位,因此传送速率至少为96000位/秒。 最大幅度为±V伏的N位(不含符号位)二进制 A/D变换器的数学模型建立如下。它把电压V分 解为2N-1份,故量化步长为V/(2N-1),得出二 进制量化子程序bqtize。

14

信号处理工具(sptool)介绍

在本例中滤波器输出sig8基本上是一个较 纯的10Hz正弦波,这是不难想象的。经 过仔细观测和分析,如不满意,可以修 改滤波器后重新实验。 用这个工具,不难在很短的时间内完成多 个滤波器的设计,并分别观测它们的输 出。所有的结果都存储在案,可用于试 验报告。所以这是一个提高效率的有效 工具。

24

语音量化压缩器的特性

图 9.2.2

μ -律与 A-律非线性压缩器的比较

25

语音量化噪声的改善

例9.2.2 设某A/D变换器把最大输入为5伏的 信号量化为四位二进制(不含符号位),要求 用图形描写其输入输出关系,并画出其绝对误 差和相对误差的曲线。 又若信号像图9.2.1那样经过压缩扩张器,则输 入输出关系有何变化? 解: A/D变换器的数学模型为绝对量化函数 bqtize,已经在前面得出。利用这个函数,加 上求绝对误差和相对误差的语句,可以方便地 列出以下的MATLAB程序hc922。

要想求得该信号的频谱,也先选定sig7,然后在 频谱栏下点击【creat】,此时出现频谱观测器 的界面,见图9.1.4。先要在左栏上部选定求 频谱的方法,目前我们只学了一种,即选FFT. 在下面的框中填入点数,例如1024,然后点击 【Apply】,就出现了频谱的曲线。

9第九章数字信号处理中的有限字长效应

两极点对a2变化的灵敏度为

z1 1 1 3.3333e j90 a2 z1 z2 j0.3 z2 1 1 3.3333e j90 a2 z2 z1 j0.3

可以看出a2对两极点的大小影响是相同的。只考虑大 小时用绝对值表示,有

z2

z2 a2

a2

因此

a2

z2 z2 / a2

极点从原来的单位圆内迁移到单位圆上,从而产生 等幅序列形式的极限环震荡。

总结

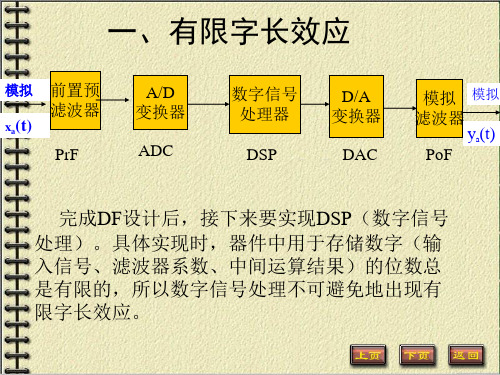

由于存储数字的位数总是有限的,所以数字信 号处理不可避免地出现有限字长效应。

有限字长效应引入的误差:

1. 输入信号的量化误差 2. 系数的量化误差 3. 运算过程中的运算误差。

请通过实验深入领会有限字长效应引入的误差。

0.0373 z1 0.745

z

2

1

0.0373 a1z 1 a2

z

2

利用a2变化造成的极点灵敏度,为保持极点在其正常 值的0.5%内变化,试确定所需要的最小字长。

解: 令H(z)的分母为零,11.7z1 0.745z2 0

求得极点为 z1 0.85 j0.15, z2 0.85 j0.15

IIR DF 的极限环振荡

由于字长有限,IIR DF零输入下也有固定不变 的输出,或输出在一定范围内出现震荡现象。

产生极限环震荡的原因 量化使下式成立

y[k] y[k 1] x[k]

Q[ y[k 1]] y[k 1] ( 0取, 0取)

即系统的差分方程变为

y[k] x[k] y[k 1]

2.有限字长效应

在量化和运算过程中,由于有限字长必然产 生误差。

这些误差给数字信号处理的实现精度 和滤波器稳定性带来不良影响,称为有限字

数字信号处理 第九章

数的正负,数的本身只有小数部分,它称为“尾数”。

定点制的特点:

① 大数的表示

比例因子归一化

② 加法运算会产生溢出: 0.1001+0.1101=1.0110,溢出 ③ 乘法运算字长会加倍; ④ 尾数处理:舍入法和截尾法; 舍入法:将尾数第 b+1位,逢1进位,逢0舍去 如: x(nT)=0.110101101,留取5位(b=5)得:Q[x(n)]=0.11011 截尾法:将尾数的第 b+1位起全部舍去 如: x(nT)=0.110101101,留取5位(b=5)得:Q[x(n)]=0.11010 使用不同的尾数处理方法,量化误差是不同的。

影响极点偏移的因素: (1) 极点偏移与系数量化误差的大小有关:

增加寄存器长度 (b) 减小极点偏移 (2) 极点偏移与系统极点的密集程度有关: 特别是窄带滤波器一般极点会靠的很近,引起较大的极点偏移。 (3) 极点偏移与滤波器的阶数 N 有关:

阶数越高,系数的量化效应影响越大,极点偏移就越大。

所以二阶以上的滤波器最好不要用直接型结构, 而用一阶或二阶的基本网络进行级联或并联实现。

通用硬件实现:

通常人们希望数字信号处理器的通用性更强些,对各 种不同的信号处理任务,只要配备相应的软件和外围设备 都可实现。 数字信号处理器(DSP)就是满足这种要求的通用单 片微处理器,它集数字计算机的通用性和专用数字信号处 理器件的高速度于一身,大大缩短了信号处理系统硬件的

研制周期,降低了成本,提高了速度。

两个二阶网络的级联结构

2、考虑网络结构的软件实现 例2:如考虑网络结构,将信号流图的节点进行排序,把延时

支路输出节点以及网络输入节点排序k=0,网络中其它可以由

k=0节点变量计算出的节点排序k=1,然后由k=0、 k=1可以计

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CONVST 控制,数据的存取由选片信号 C S 和读信号 RD 输入信号控制(低电平有效)。下

面的 Verilog 源代码描述了该 A/D 的转换启动和数据读出功能,(假设 C S 和 RD 都为低电

平)根据手册的说明,输入和输出波形如下图所示:

在实际电路中,A/D 包括模拟部分,和许多必要的控制和参考电平输入,而在这里为了简单 和说明问题起见,只介绍 A/D 模块有关数字接口的一部分功能,把这部分功能编写成虚拟 模块。其中只包括了 A/D 控制信号的输入、数据总线和“忙”信号的输出。为了进一步简化

还假设选片信号 C S 和读信号 RD 总是为低电平(有效)。因此,该模型实质上是为教学目

output nbusy;

// A/D 工作标志,即上图中

output

data;

// 数据总线,从 AD.DATA 文件中读取数据后经端口输出

reg[7:0] databuf,i; // 内部寄存器

reg

nbusy;

wire[7:0] data;

reg[7:0] data_mem[0:255];

reg

9.1 虚拟器件和虚拟接口模块的供应商

在这一节中我们列出一些虚拟器件和接口的供应商的 E-mail 地址及它们提供的产品和服务 供读者参考:

深圳市 21EDA 电子 夏宇闻著作

公司名

虚拟器件类型

所用语言 加密否 语言级别

American Microsystem 电子信箱: tdrake@

//+++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

`timescale 1ns/100ps

module adc (nconvst, nbusy, data);

input nconvst;

// A/D 启动脉冲 ST,即上图中

link_bus;

integer tconv,

t5,

t8,

t9,

t12;

integer wideth1,

wideth2,

wideth;

//时间参数定义(依据 AD7886 手册):

always @(negedge nconvst)

begin

tconv =9500+{$random}%500; //(type 950, max 1000)Conversion Time

[例 1]. 模数转换器 AD7886 仿真模型(虚拟模块)的设计:

下面介绍的名为 ADC 的 Verilog 模块在设计中可以用来模拟实际的模数转换器(下面简称 A/D)AD7886。因此,该仿真模型的输入与出各输出信号间的逻辑关系,必须严格按照数据 手册描述的波形编写,信号间的时间关系也必须完全符合手册要求,这样才能起到虚拟模块 的作用。只有这样在设计电路的测试中才能用它来代替实际器件。同时,虚拟模块还应具备 实际电路所没有的功能: 如对于不符合要求的输入信号还能产生错误提示。 在实际的电路 中,我们很难控制 A/D 的输出数据,然而在该设计中,我们可以编写数据文件,得到我们想 要的各种类型的数据, 来测试后续电路的功能,并可以随时根据测试要求更改数据,非常 方便。虚拟模块的编写是 Verilog 语言应用的重要方面。它为 ASIC 设计投片一次成功提供 了可能。

深圳市 21EDA 电子 夏宇闻著作

t5 ={$random}%1000; //(max 100) CONVST to BUSY Propagation Dlay // CL = 10pf

t8 = 200; //(min 20) CL=20pf Data Setup Time Prior to BUSY //(min 10) CL=100pf

深圳市 21EDA 电子 夏宇闻著作

第九章 虚拟器件和虚拟接口模型

以及它们在大型数字系统设计中的作用

前言

宏单元(Macrocells 或 Megacells)或核(Cores)是预先设计好的,其功能经过验证的、由总 数超过 5000 个门构成的一体化的电路模块,这个模块可以是以软件为基础的,也可以是以 硬件为基础的。这就是我们在第一章的 1.5.3 和 1.5.4 节中讨论过的软核和硬核。所谓虚拟 器件(Virtual Chips)也就是用软核构成的器件,即用 Verilog HDL 或 VHDL 语言描述的常用 大规模集成电路模型。 在新电路研制过程中,借助 EDA 综合工具,软核和虚拟器件可以很 容易地与其它外部逻辑结合为一体,从而大大扩展了设计者可选用的资源。掌握软核和虚拟 器件(也称接口模型)的重用技术可大大缩短设计周期,加快高技术新芯片的投产和上市 。 而所谓虚拟接口模型则是用系统级 Verilog HDL 或 VHDL 语言描述的常用大规模集成电路(如 ROM 和 RAM)或总线接口的行为模型等,往往是不可综合的,也没有必要综合成具体电路, 但其所有对外的性能与真实的器件或接口完全一致,在仿真时可用来代替真实的部件,用以 验证所设计的电路(必须综合的部分)是否正确。

begin @(posedge nconvst) begin #(tconv-t8) databuf=data_mem[i];

深圳市 21EDA 电子 夏宇闻著作

end

if(wideth <10000 && wideth>500) begin if(i==255) i=0; else i=i+1; end

ARM Semiconductor 电子信箱: armsemi@

Scenix Semiconductor 电子信箱: sales@

Sierra Research and Technology 电子信箱: core@

算术运算函数 异步同步 FIFO DSP 微处理器 UART 和 USARTs RAM 和 ROM 微处理器: 8031,8032,8051 通信器件: 8530 总线控制器: 82365(PCMCIA Host i/f) 控制器: NS COP8 PCI arbiter,master & target 8237 DMA ATM SAR 622 Mbits Ethernet 控 制 器 100/10-Mbits CPU R3000 核

nconvst 信号的上升沿到来后,经过(tconv - t8)时间,输出一个字节(8 位数据)到 databuf, 该数据来自于 data_mem。而 data_mem 中的数据是初始化时从数据文件 AD.DATA 中读取的。 此时应启动总线的三态输出。 ---------------------------------------------------------------------------*/ always @(negedge nconvst)

t9 = 100+{$random}%900; //(min 10, max 100) Bus Relinquish Time After //CONVST

t12 = 2500; //(type) BUSY High to CONVST Low, SHA Acquisition Time end

initial begin $readmemh("adc.data",data_mem); i = 0; nbusy = 1; link_bus = 0; end

的而编写的简化虚拟模块, 在仿真时仅能代替真实 A/D 的一部分功能。它类似一个数据发生 器,根据输入控制信号和 A/D 自身的特性输出一个字节(8 位)数据和“忙”信号。同时根 据手册规定,不断检测输入信号是否符合要求。虚拟模型的精确与否,直接影响到设计是否 能够一次投片成功。因此在 ASIC 系统芯片的设计中应予以充分的重视。

Micro VGA

DSP PCI Master PCI target

Verilog

Verilog VHDL

不

门级

RTL 级

不

门级

RTL 级

和

系统级

(只可用

Hale Waihona Puke 于仿真)三种都可提供

深圳市 21EDA 电子 夏宇闻著作

9.2 虚拟模块的设计

我国大陆地区由于复杂芯片的设计工作开展较晚,经费也比较少,目前许多单位有还不能及 时得到商业化的虚拟模块和接口,因此就有必要自己来设计虚拟接口模型。下面的例子说明 了怎样根据数据手册和波形图来编写虚拟的接口模型。

Verilog VHDL

Verilog

Verilog Verilog

不

门级

RTL 级

可选

系统级 (只可用 于仿真)

不

门级

RTL 级

不

门级

RTL 级

Silicon Engineering 电子信箱: info@ Lucent Technology 电子信箱: attfpga@

//从数据文件 adc.data 中读取数据

assign data = link_bus? databuf:8'bzz; //三态总线