CL1112中文规格书

罗特洛尼克CL11桌面数据记录仪说明书

Fig.5

Fig.6

Fig.7

Fig.8

ALபைடு நூலகம்RM

The meter features acoustic & light alarm to give warnings when CO2 concentration exceeds the limit. (See “Meter Setup” section for setting alarm threshold). It emits beeps (~80dB) & red LED light when CO2 level goes over the set value and stops only when the readings fall below the set value or manually turn beeper off. It beeps again when value goes over the limit. Please note, if the beeper is selected as OFF, device emit light warning only, no beeper.

CL11 InDesignCS5_A3.indd 1

Operation

POWER ON/OFF

FPGA可编程逻辑器件芯片XCZU15EG-L11FFVB1156中文规格书

CoolRunner-II Smart Card ReaderXAPP372(v1.0)September 19,2003SRAM InterfaceSRAM Interface logic interfaces to the external SRAM.This logic block controls the SRAM read/write addressing.Smart card data is saved in SRAM and later fetched and decoded for the LCD display.LCD ControlLCD control logic interfaces to the LCD Display.This logic block accepts the decoded data and writes to the LCD Display.Refer to XAPP431,CoolRunner-II Character LCD Display Controller ,for detailed information.ExternalDevices Level ShifterThe On semiconductor NCN6011is a level shifter (analog device)to translate the voltages between a smart card and CoolRunner-II CPLD.This device handles all the 5V signals needed for the smart card and 1.8V signals for the CoolRunner-II CPLD.It is transparent to the smart card control logic in the CPLD.LCD DisplayThe OKAYA RC1602ARS is a 16-character x 2-line,dot matrix,liquid crystal display module.It has an on-board controller and LSI drivers,which display alpha numerics,Japanese KATA KANA characters and a wide variety of other symbols in 5x 7dot matrix.SRAMA low power,32k x 8ISSI IS61LV256SRAM is used in the module memory.The functionality of the SRAM does not require additional explanation.For more in-depth SRAM information refer to the ISSI SRAM data sheet.Smart Card AcceptorThe Amphenol C70210M0082834is a low cost smart card acceptor.It provides a direct sliding contact between the acceptor and the smart card.This acceptor has a “NC closed card present switch”which opens when the card is fully inserted.The switch activates the smart card reader operation.Smart Card Standard ISO7816Smart Card is defined by the international standard ISO 7816.The first two parts cover smart card’s physical dimensions and locations of the chip contacts.A smart card image and its contacts are shown in Figure 3.Figure 3:Smart Card Image and ContactsCoolRunner-II Smart Card ReaderFigure12:Main Control Logic Flow ChartThe next data record is decoded gender information.The data value is one for male,two for female.After gender comes status information,also decoded as one and two(one for single, two for married).The age information is saved as binary value in the smart card.It has to be converted to ASCII digits before getting sent to the LCD controller.A binary-to-digital module is separated from the top module,which is for the ASCII coding function.SRAM InterfaceThe SRAM interface is controlled by the main control logic.The signal sram_w is always kept high as write enable during smart card reading.The address counter will be reset when the main control state machine enters the standby state for writing data to the LCD display.The data is then retrieved in the order it was saved.XAPP372(v1.0)September19,2003。

FPGA可编程逻辑器件芯片XC5VLX50-1FFG1153I中文规格书

4.08

XC5VLX85

3.52

3.78

4.20

XC5VLX85T

3.52

3.78

4.20

XC5VLX110

3.57

3.84

4.27

XC5VLX110T

3.57

3.84

4.27

XC5VLX155

3.83

4.10

4.53

XC5VLX155T

3.83

4.10

4.53

XC5VLX220

N/A

4.33

4.76

6. TRCKO_FLAGS includes the following parameters: TRCKO_AEMPTY, TRCKO_AFULL, TRCKO_EMPTY, TRCKO_FULL, TRCKO_RDERR, TRCKO_WRERR. 7. TRCKO_POINTERS includes both TRCKO_RDCOUNT and TRCKO_WRCOUNT. 8. The ADDR setup and hold must be met when EN is asserted even though WE is deasserted. Otherwise, block RAM data corruption is possible.

Table 94: Global Clock Setup and Hold With PLL in System-Synchronous Mode

Symbol

Description

Device

Speed Grade

-3

-2

-1

Input Setup and Hold Time Relative to Global Clock Input Signal for LVCMOS25 Standard.(1)

诺基亚互联网适配棒 CS-11 2.0 版中文版说明书

诺基亚互联网适配棒 CS-11第2.0版声明我们诺基亚公司郑重声明产品 RD-15 符合指令1999/5/EC 中的基本要求及其他相关条款。

此声明的全文可在 http:// /phones/ declaration_of_conformity/© 2010-2011 诺基亚。

保留所有权利。

诺基亚、Nokia、Nokia Connecting People 和诺基亚原厂配件标志是诺基亚公司的商标或注册商标。

本文档中提及的其他产品或公司的名称可能是其各自所有者的商标或商名。

在未经诺基亚事先书面许可的情况下,严禁以任何形式复制、传递、分发和存储本文档中的任何内容。

诺基亚遵循持续发展的策略。

因此,诺基亚保留在不预先通知的情况下,对本文档中描述的任何产品进行修改和改进的权利。

在适用法律允许的最大限度内,在任何情况下,诺基亚或其任何被许可方均不对任何数据或收入方面的损失,或任何特殊、偶然、附带或间接损失承担责任,无论该损失由何种原因引起。

本文档的内容按“现状”提供。

除非适用的法律另有规定,否则不对本文档的准确性、可靠性和内容做出任何类型的、明确或默许的保证,其中包括但不限于对适销性和对具体用途的适用性的保证。

诺基亚保留在不预先通知的情况下随时修订或收回本文档的权利。

有关最新的产品更新文档,请参见。

产品的供货情况,以及适用于这些产品的应用程序和服务可能因地区而异。

有关详情以及提供的语言选项,请向您的诺基亚指定经销商咨询。

本设备可能包含受美国和其他国家或地区的出口法律和法规控制的商品、技术或软件。

严禁任何违反法律的转移行为。

安全事项请阅读以下简明的规则。

不遵守这些规则可能会导致危险或触犯法律。

本用户手册中提供了有关安全事项的更详细信息。

安全开机当禁止使用无线设备或设备的使用会引起干扰或危险时,请不要开机。

干扰所有的无线设备都可能受到干扰,从而影响性能。

在受限制区域应关机请遵守任何相关的限制规定。

在飞机上,或在医疗设备、燃料、化学制品或爆破地点附近应关机。

MEMORY存储芯片MT58L512Y36PF-6中文规格书

12.Only applicable for DRAM component-level test/characterization purposes. Not applica-ble for normal mode of operation. V REF valid qualifies the step times, which will be char-acterized at the component level.V REFDQ RangesMR6[6] selects range 1 (60% to 92.5% of V DDQ ) or range 2 (45% to 77.5% of V DDQ ), and MR6[5:0] sets the V REFDQ level, as listed in the following table. The values in MR6[6:0]will update the V DDQ range and level independent of MR6[7] setting. It is recommended MR6[7] be enabled when changing the settings in MR6[6:0], and it is highly recommen-ded MR6[7] be enabled when changing the settings in MR6[6:0] multiple times during a calibration routine.Table 83: V REFDQ Range and Levels8Gb: x4, x8, x16 DDR4 SDRAM Electrical Characteristics – AC and DC Operating ConditionsCommands that require locked DLL in the normal operating range:•t XSDLL – RD, RDS4, RDS8, RDA, RDAS4, and RDAS8 (unlike DDR3, WR, WRS4, WRS8,WRA, WRAS4, and WRAS8 because synchronous ODT is required).Depending on the system environment and the amount of time spent in self refresh, ZQ CALIBRATION commands may be required to compensate for the voltage and tempera-ture drift described in the ZQ CALIBRATION Commands section. To issue ZQ CALIBRA-TION commands, applicable timing requirements must be satisfied (see the ZQ Calibra-tion Timing figure).CKE must remain HIGH for the entire self refresh exit period t XSDLL for proper opera-tion except for self refresh re-entry. Upon exit from self refresh, the device can be put back into self refresh mode or power-down mode after waiting at least t XS period and issuing one REFRESH command (refresh period of t RFC). The DESELECT command must be registered on each positive clock edge during the self refresh exit interval t XS.ODT must be turned off during t XSDLL.The use of self refresh mode introduces the possibility that an internally timed refresh event can be missed when CKE is raised for exit from self refresh mode. Upon exit from self refresh, the device requires a minimum of one extra REFRESH command before it is put back into self refresh mode.Figure 90: Self Refresh Entry/Exit TimingCK_tCK_cCommandADDRCKEODTNotes: 1.Only MRS (limited to those described in the SELF REFRESH Operation section), ZQCS, orZQCL commands are allowed.2.Valid commands not requiring a locked DLL.3.Valid commands requiring a locked DLL.8Gb: x4, x8, x16 DDR4 SDRAM SELF REFRESH OperationTable 144: I DD4Wc Measurement – Loop Pattern 1Notes: 1.Pattern provided for reference only.2.DQS_t, DQS_c are V DDQ when not toggling.3.BG1 is a "Don't Care" for x16 devices.4.Burst sequence driven on each DQ signal by WRITE command. Outside burst operation,DQ signals are V DDQ .5.For x4 and x8 only.8Gb: x4, x8, x16 DDR4 SDRAM Current Specifications – Patterns and Test Conditions。

FPGA可编程逻辑器件芯片EP4CE115F29C8LN中文规格书

PIPELINED VISION PROCESSOR (PVP) PVP FUNCTIONAL DESCRIPTION

• If PVP_IIMn_SCALE.HSCL =7, the IIMn outputs only every 8th column.

• Supports independent scaling in both directions

The output frame size is selectable in steps of 16. The values supported are: 16 × n × 16 × m where n,m=1,2,...,8. The output size is programmed in the PVP_UDS_OHCNT and PVP_UDS_OVCNT registers.

M L

,QS, - 6$7, - 6$7, - 6$7, -

As with integral row mode, the initial values of the integral are assumed to be zero—SAT-1,J = 0 and SATI,1 = 0. In the SAT output map, each value contains the accumulated input values from the frame's origin to the actual position, as shown in the Illustration of SAT Mode figure.

Camera pipes and memory pipes can operate concurrently. The pipes have separate control mechanisms, have separate data paths, and operate with independent timing. The camera and memory pipes do share

FPGA可编程逻辑器件芯片EP4CE22F17C8L中文规格书

Chapter 1:Overview for the Arria II Device FamilyArria II Device Architecture Arria II Device Handbook Volume 1: Device Interfaces and Integration1PCIe Gen2 protocol is only available in Arria II GZ devices.The following sections provide an overview of the various features of the Arria IIFPGA.PCIe Hard IP BlockEvery Arria II device includes an integrated hard IP block which implements PCIe PHY/MAC, data link, and transaction layers. This PCIe hard IP block is highlyconfigurable to meet the requirements of the majority of PCIe applications. PCIehard IP makes implementing PCIe Gen1 and PCIe Gen2 solution in your Arria IIdesign simple and easy.You can instantiate PCIe hard IP block using the PCI Compiler MegaWizard TMPlug-In Manager, similar to soft IP functions, but does not consume core FPGAresources or require placement, routing, and timing analysis to ensure correctoperation of the core. Table 1–6 lists the PCIe hard IP block support for Arria II GX and GZ devices.Logic Array Block and Adaptive Logic Modules■Logic array blocks (LABs) consists of 10 ALMs, carry chains, shared arithmeticchains, LAB control signals, local interconnect, and register chain connection lines■ALMs expand the traditional four-input LUT architecture to eight-inputs,increasing performance by reducing logic elements (LEs), logic levels, andassociated routing■LABs have a derivative called MLAB, which adds SRAM-memory capability tothe LAB■MLAB and LAB blocks always coexist as pairs, allowing up to 50% of the logic(LABs) to be traded for memory (MLABs)Embedded Memory Blocks■MLABs, M9K, and M144K embedded memory blocks provide up to 20,836Kbitsof on-chip memory capable of up to 540-MHz performance. The embeddedmemory structure consists of columns of embedded memory blocks that you canconfigure as RAM, FIFO buffers, and ROM.■Optimized for applications such as high-throughput packet processing,high-definition (HD) line buffers for video processing functions, and embeddedprocessor program and data storage.Table 1–6.PCIe Hard IP Block Support SupportArria II GX Devices Arria II GZ Devices PCIe Gen1x1, x4, x8x1, x4, x8PCIe Gen2—x1, x4Root Port and endpoint configurationsYes Yes Payloads 128-byte to 256-byte 128-byte to 2K-byteChapter 2:Logic Array Blocks and Adaptive Logic Modules in Arria II DevicesAdaptive Logic ModulesFor the packing of two 5-input functions into one ALM, the functions must have atleast two common inputs. The common inputs are dataa and datab. The combinationof a 4-input function with a 5-input function requires one common input (either dataaor datab).In the case of implementing two 6-input functions in one ALM, four inputs must beshared and the combinational function must be the same. In a sparsely used device,functions that could be placed in one ALM may be implemented in separate ALMs bythe Quartus II software to achieve the best possible performance. As a device beginsto fill up, the Quartus II software automatically utilizes the full potential of theArria II ALM. The Quartus II Compiler automatically searches for functions usingcommon inputs or completely independent functions to be placed in one ALM tomake efficient use of device resources. In addition, you can manually control resourceusage by setting location assignments.Any 6-input function can be implemented using inputs dataa, datab, datac, datad,and either datae0 and dataf0 or datae1 and dataf1. If datae0 and dataf0 are utilized,the output is driven to register0, and/or register0 is bypassed and the data drivesout to the interconnect using the top set of output drivers (refer to Figure2–8). Ifdatae1 and dataf1 are used, the output either drives to register1 or bypassesregister1 and drives to the interconnect using the bottom set of output drivers. TheQuartus II Compiler automatically selects the inputs to the LUT. ALMs in normalmode support register packing.Figure2–8.Input Function in Normal Mode (Note1)Notes to Figure2–8:(1)If datae1 and dataf1 are used as inputs to a 6-input function, datae0 and dataf0 are available for register packing.(2)The dataf1 input is available for register packing only if the 6-input function is unregistered.Arria II Device Handbook Volume 1: Device Interfaces and IntegrationChapter 3:Memory Blocks in Arria II DevicesMemory FeaturesFigure3–5 shows the address clock enable waveform during write cycle for M9K andM144K blocks.Figure3–5.Address Clock Enable During Write Cycle Waveform for M9K and M144K BlocksFigure3–6 shows the address clock enable waveform during the write cycle forMLABs.Figure3–6.Address Clock Enable During Write Cycle Waveform for MLABsArria II Device Handbook Volume 1: Device Interfaces and Integration。

FPGA可编程逻辑器件芯片XC7VX690T-2FF1158C中文规格书

7Series FPGAs Data Sheet: OverviewDS180 (v2.6.1) September 8, 2020Product SpecificationStacked Silicon Interconnect (SSI) TechnologyThere are many challenges associated with creating high capacity FPGAs that Xilinx addresses with the SSI technology. SSI technology enables multiple super logic regions (SLRs) to be combined on a passive interposer layer, using proven manufacturing and assembly techniques from industry leaders, to create a single FPGA with more than ten thousand inter-SLR connections, providing ultra-high bandwidth connectivity with low latency and low power consumption. There are two types of SLRs used in Virtex-7 FPGAs: a logic intensive SLR used in the Virtex-7 T devices and a DSP/blockRAM/transceiver-rich SLR used in the Virtex-7 XT and HT devices. SSI technology enables the production of highercapability FPGAs than traditional manufacturing methods, enabling the highest capacity and highest performance FPGAs ever created to reach production more quickly and with less risk than would otherwise be possible. Thousands of super long line (SLL) routing resources and ultra-high performance clock lines that cross between the SLRs ensure that designs span seamlessly across these high-density programmable logic devices.CLBs, Slices, and LUTsSome key features of the CLB architecture include:•Real 6-input look-up tables (LUTs)•Memory capability within the LUT •Register and shift register functionalityThe LUTs in 7 series FPGAs can be configured as either one 6-input LUT (64-bit ROMs) with one output, or as two 5-input LUTs (32-bit ROMs) with separate outputs but common addresses or logic inputs. Each LUT output can optionally be registered in a flip-flop. Four such LUTs and their eight flip-flops as well as multiplexers and arithmetic carry logic form a slice, and two slices form a configurable logic block (CLB). Four of the eight flip-flops per slice (one per LUT) can optionally be configured as latches.Between 25–50% of all slices can also use their LUTs as distributed 64-bit RAM or as 32-bit shift registers (SRL32) or as two SRL16s. Modern synthesis tools take advantage of these highly efficient logic, arithmetic, and memory features.Clock ManagementSome of the key highlights of the clock management architecture include:•High-speed buffers and routing for low-skew clock distribution •Frequency synthesis and phase shifting •Low-jitter clock generation and jitter filteringEach 7series FPGA has up to 24 clock management tiles (CMTs), each consisting of one mixed-mode clock manager (MMCM)and one phase-locked loop (PLL).Table 11:Virtex-7 HT FPGA Device-Package Combinations and Maximum I/Os Package (1)FLG1155FLG1931FLG1932Size (mm)35 x 3545 x 4545 x 45Ball Pitch1.0 1.0 1.0DeviceGTH GTZ I/O GTH GTZ I/O GTH GTZ I/O HP (2)HP (2)HP (2)XC7VH580T248400488600XC7VH870T 7216300Notes:1.All packages listed are Pb-free with exemption 15. Some packages are available in Pb option.2.HP = High-performance I/O with support for I/O voltage from 1.2V to 1.8V.7Series FPGAs Data Sheet: OverviewMixed-Mode Clock Manager and Phase-Locked LoopThe MMCM and PLL share many characteristics. Both can serve as a frequency synthesizer for a wide range of frequencies and as a jitter filter for incoming clocks. At the center of both components is a voltage-controlled oscillator (VCO), which speeds up and slows down depending on the input voltage it receives from the phase frequency detector (PFD).There are three sets of programmable frequency dividers: D, M, and O. The pre-divider D (programmable by configuration and afterwards via DRP) reduces the input frequency and feeds one input of the traditional PLL phase/frequency comparator. The feedback divider M (programmable by configuration and afterwards via DRP) acts as a multiplier because it divides the VCO output frequency before feeding the other input of the phase comparator. D and M must be chosen appropriately to keep the VCO within its specified frequency range. The VCO has eight equally-spaced output phases (0°, 45°, 90°, 135°, 180°, 225°, 270°, and 315°). Each can be selected to drive one of the output dividers (six for the PLL, O0 to O5, and seven for the MMCM, O0 to O6), each programmable by configuration to divide by any integer from 1 to 128. The MMCM and PLL have three input-jitter filter options: low bandwidth, high bandwidth, or optimized mode. Low-bandwidth mode has the best jitter attenuation but not the smallest phase offset. High-bandwidth mode has the best phase offset, but not the best jitter attenuation. Optimized mode allows the tools to find the best setting.MMCM Additional Programmable FeaturesThe MMCM can have a fractional counter in either the feedback path (acting as a multiplier) or in one output path. Fractional counters allow non-integer increments of 1/8 and can thus increase frequency synthesis capabilities by a factor of 8.The MMCM can also provide fixed or dynamic phase shift in small increments that depend on the VCO frequency. At 1600MHz, the phase-shift timing increment is 11.2ps.Clock DistributionEach 7series FPGA provides six different types of clock lines (BUFG, BUFR, BUFIO, BUFH, BUFMR, and the high-performance clock) to address the different clocking requirements of high fanout, short propagation delay, and extremely low skew.Global Clock LinesIn each 7series FPGA (except XC7S6 and XC7S15), 32 global clock lines have the highest fanout and can reach every flip-flop clock, clock enable, and set/reset, as well as many logic inputs. There are 12 global clock lines within any clock region driven by the horizontal clock buffers (BUFH). Each BUFH can be independently enabled/disabled, allowing for clocks to be turned off within a region, thereby offering fine-grain control over which clock regions consume power. Global clock lines can be driven by global clock buffers, which can also perform glitchless clock multiplexing and clock enable functions. Global clocks are often driven from the CMT, which can completely eliminate the basic clock distribution delay.Regional ClocksRegional clocks can drive all clock destinations in their region. A region is defined as an area that is 50 I/O and 50 CLB high and half the chip wide. 7series FPGAs have between two and twenty-four regions. There are four regional clock tracks in every region. Each regional clock buffer can be driven from any of four clock-capable input pins, and its frequency can optionally be divided by any integer from 1 to 8.I/O ClocksI/O clocks are especially fast and serve only I/O logic and serializer/deserializer (SerDes) circuits, as described in theI/O Logic section. The 7series devices have a direct connection from the MMCM to the I/O for low-jitter, high-performance interfaces.DS180 (v2.6.1) September 8, 2020Product Specification。

CL1118 隔离三绕组8-12W工程规格书

方案规格承认书 APPROVAL SHEET

客户名称 CUSTOMERS: 芯联芯片型号 Chiplink PART/NO. 芯联 DEMO 板型号 Chiplink DEMO PART/NO. 客户产品规格 CUSTOMEE: Report NO: ---

0805 DIP-8 DO-15

SMA 卧式

客户承认反确 CUSTOMER APPROVED:

芯联审核 CHECKED BY:

芯联制表 PREPARED BY:

-3-

SEMICONDUCTOR

PCB Layout

客户承认反确 CUSTOMER APPROVED:

芯联审核 CHECKED BY:

芯联制表 PREPARED BY:

D1,D2,D3,D4,D5 T1

Description(规格) 贴片电阻 47K +1% 贴片电阻 5.1K +1% 贴片电阻 22R +1% 贴片电阻 1.5M +5% 贴片电阻 200K +5% 贴片电阻 100R +1% 贴片电阻 36K +5% 贴片电阻 5R1 +1% 贴片电阻 1R5 +1%

1 :此承认书适用范围:贵司要求我司工程部依据贵司产品的外形规格,电气特 性,认证要求之类来为贵司开发定制方案,方案性能及成本经贵司确认后,贵司 会直接依据我司提供定制方案打样,试产,量产。

2:我司方案样机调试完毕,贵司对方案确认无误后,必须经过打样确认,试产确 认,才可以量产。

3:方案确认无误后,贵司未与我司协商确认,随意变更 BOM,变压器,PCB 导 致的量产问题,我司对量产产品不承担任何责任。

铝电解电容 10uF/400V 贴片电容 106k/25v 贴片电容 104K/25V 贴片电容 102K/1KV

MEMORY存储芯片MT41K512M16TSR-125IT E中文规格书

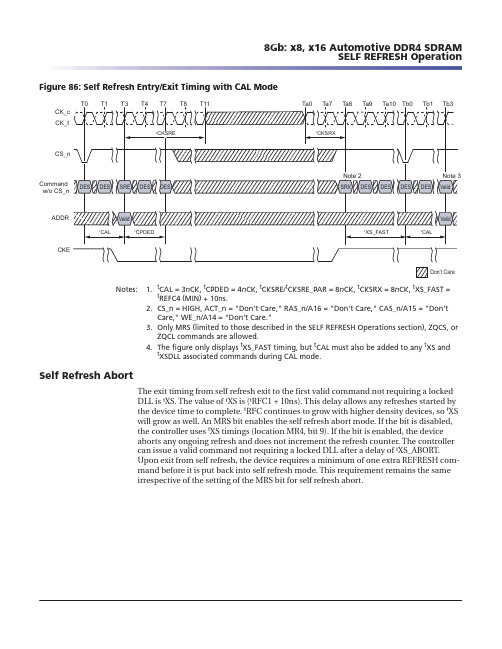

Figure 86: Self Refresh Entry/Exit Timing with CAL Mode&.BW&.BF&RPPDQG $''5Z R &6BQ &6BQ&.('RQ¶W &DUHNotes: 1.t CAL = 3n CK, t CPDED = 4n CK, t CKSRE/t CKSRE_PAR = 8n CK, t CKSRX = 8n CK, t XS_FAST =t REFC4 (MIN) + 10ns.2.CS_n = HIGH, ACT_n = "Don't Care," RAS_n/A16 = "Don't Care," CAS_n/A15 = "Don't Care," WE_n/A14 = "Don't Care."3.Only MRS (limited to those described in the SELF REFRESH Operations section), ZQCS, or ZQCL commands are allowed.4.The figure only displays t XS_FAST timing, but t CAL must also be added to any t XS and t XSDLL associated commands during CAL mode.Self Refresh AbortThe exit timing from self refresh exit to the first valid command not requiring a locked DLL is t XS. The value of t XS is (t RFC1 + 10ns). This delay allows any refreshes started by the device time to complete. t RFC continues to grow with higher density devices, so t XS will grow as well. An MRS bit enables the self refresh abort mode. If the bit is disabled,the controller uses t XS timings (location MR4, bit 9). If the bit is enabled, the device aborts any ongoing refresh and does not increment the refresh counter. The controller can issue a valid command not requiring a locked DLL after a delay of t XS_ABORT.Upon exit from self refresh, the device requires a minimum of one extra REFRESH com-mand before it is put back into self refresh mode. This requirement remains the same irrespective of the setting of the MRS bit for self refresh abort.8Gb: x8, x16 Automotive DDR4 SDRAM SELF REFRESH OperationTable 132: DRAM Package Electrical Specifications for x16 Devices (Continued)Notes: 1.This parameter is not subject to a production test; it is verified by design and characteri-zation and are provided for reference; system signal simulations should not use these values but use the Micron package model. The package parasitic (L and C) are validated using package only samples. The capacitance is measured with V DD , V DDQ , V SS , and V SSQ shorted with all other signal pins floating. The inductance is measured with V DD , V DDQ ,V SS , and V SSQ shorted and all other signal pins shorted at the die, not pin, side.2.Package-only impedance (Zpkg) is calculated based on the Lpkg and Cpkg total for a given pin where: Zpkg (total per pin) = SQRT (Lpkg/Cpkg).3.Package-only delay (Tpkg) is calculated based on Lpkg and Cpkg total for a given pin where: Tdpkg (total per pin) = SQRT (Lpkg × Cpkg).4.Z IO and Td IO apply to DQ, DM, TDQS_t and TDQS_c.5.Absolute value of ZCK_t, ZCK_c for impedance (Z) or absolute value of TdCK_t, TdCK_c for delay (Td).6.Absolute value of ZIO (DQS_t), ZIO (DQS_c) for impedance (Z) or absolute value of TdIO (DQS_t), TdIO (DQS_c) for delay (Td).7.Z I ADD CMD and Td I ADD CMD apply to A[17:0], BA[1:0], BG[1:0], RAS_n CAS_n, WE_n,ACT_n, and PAR.8.Z I CTRL and Td I CTRL apply to ODT, CS_n, and CKE.9.Package implementations will meet specification if the Zpkg and package delay fall within the ranges shown, and the maximum Lpkg and Cpkg do not exceed the maxi-mum values shown.10.It is assumed that Lpkg can be approximated as Lpkg = Z O × Td.11.It is assumed that Cpkg can be approximated as Cpkg = Td/Z O .8Gb: x8, x16 Automotive DDR4 SDRAM DRAM Package Electrical Specifications。

FPGA可编程逻辑器件芯片EP4CE115F29C8L中文规格书

Mode 0 (continuous frame mode) is popular for camera pipe operation. Often, the camera pipe is enabled statically, and updates to the coefficients are only required from time to time. On demand software may enable the configuration DMA in stop mode to trigger the fetch of one single BCL. In this mode, the PVP_IPFn_TAG register is useful to match status results with a respective configuration. The new BCL only updates coefficients of processing blocks. The BCL does not alter the pipe configuration.Mode 1 (back-to-back mode) is useful in camera pipe mode when coefficients have to change every N th frame. This mode supports on-the-fly reprogramming of coefficients, but it does not support on-the-fly reprogramming of pipe configurations. The following settings must not change unless the DRAIN bit is set:•Pipe structure (PVP_xxx_CFG registers)•Fundamental operating modes (such as 1st-derivative to 2nd-derivative mode of PEC)•Input format and OPORT configuration (PVP_IPFn_CTL registers)•Horizontal size of input frame (HCNT)If any of the above settings change on-the-fly, the PVP_IPFn_PIPECTL.DRAIN bit must be set for proper operation to use Mode 2. In memory pipe mode, the PVP_IPFn_PIPECTL.DRAIN bit causes of few clock cycles of overhead depending to pipeline depth. In camera pipe mode, the PVP_IPFn_PIPECTL.DRAIN bit causes the loss of an entire frame. Operation stops after the pipe has been drained and resumes with the next incoming VSYNC signal.Whenever the next PVP job stalls until the completion event of the data output DMA is flagged either as an interrupt or as a system trigger, setting the PVP_IPFn_PIPECTL.DRAIN bit is a requirement at the appli-cation level. The data output DMA work unit does not complete as long as related data sticks in the pipe. The data in the pipe does not progress until the configuration DMA and data source grant. Such deadlock situations can be avoided by using Mode 2. Once a deadlock occurs, it can be resolved by Mode 3 opera-tion.Mode 3 (drain now instruction) is more similar to a one-time instruction than an operating mode. This mode is used whenever software needs to respond to unpredictable events. For example, while the camera >01Mode 2: Auto-Completion ModeFCNT frames are requested by the IPFn, and these feed the pipe. The last datawords are automatically pushed out, and the operation automatically completes.If a new configuration is granted by DMA or by MMR writes, the configuration isapplied for the next FCNT set of frames.All processing blocks auto-disable. A new configuration must set all wanted STARTbits again.01Mode 3: Drain Now InstructionThis combination instructs the IPFn to flush all content out of the pipe.All processing blocks auto-disable. A new configuration must set all wanted STARTbits again.Table 30-47:Operating Modes by FCNT and DRAIN Selections (Continued)FCNT DRAINModeConfiguring with Daisy Chain MethodConfiguration and coefficient memory mapped registers (MMRs) of all processing blocks are double buff-ered. Whenever PVP_IPFn_FCNT is zero and the PVP_IPF0_CFG.START and PVP_IPF1_CFG.START bits =1, the values are copied from MMR registers into application buffers at the frame boundary. Due to the pipe-lined nature of the PVP, not all values are copied at the same time. Rather, the timing of value copying is closely related to how the VSYNC of the next frame progresses through the pipe. New settings apply to the first pixel of the new frame immediately after the last pixel of the old frame has been processed. The update command is daisy chained through the pipe, starting from the IPFn blocks through to the OPFn blocks. While sequencing through the daisy chain operation, hardware clears the PVP_xxx_CFG.START bits of all involved processing blocks in MMR space. Write conflicts can occur if software attempts to write the PVP_xxx_CFG registers during the daisy chain operation.The PVP_STAT register provides two status bits that report whether a daisy chain operation is ongoing in the camera pipes (PVP_STAT.CPDC ) or in the memory pipe (PVP_STAT.MPDC ). These bits are set along with the PVP_IPF0_CFG.START or PVP_IPF1_CFG.START bit and are cleared if the output formatters have been updated.In camera pipe mode, the PVP_STAT.CPDC bit is cleared only after the daisy chain progresses through the furthest of the enabled OPFn blocks. During this time, software should not write the PVP registers. If soft-ware mistakenly does write to these registers, the event is reported by the PVP_STAT.CPWRERR and PVP_STAT.MPWRERR flags. While all status bits in the PVP_STAT register are self clearing, the PVP_ILAT register latches the events until cleared by a software handshake.A PVP block which is enabled in either the camera pipe or memory pipe can be moved to the other pipe only after the drain done command is received for the former pipe. This restriction ensures that the PVP completely processes all the pixels in one pipe and disables the PVP block, before the PVP is enables the PVP block for pixel processing in the next pipe.NOTE :Camera pipes and memory pipes can be configured by MMR writes or BCL fetches. These are sepa-rate control mechanisms and are not intended to be mixed for a given pipe during ongoing opera-tion. Before switching from one method to the other, inspect the daisy chain and drain status bits in the PVP_STAT register to ensure no operation from the other method is pending.PMA5ACU7PEC2x HCNT + 11 if 2nd derivative mode with ZCRSS=0, otherwise 1xHCNT + 6IIMn6UDS varies with settingsTable 30-48:Block Latencies (Continued)PVP Block Latency [Data Clocks]P IPELINED V ISION P ROCESSOR (PVP)P ROGRAMMING M ODELto handle the three data flows, BCS, data IN, data OUT, and optionally status data OUT. If the descrip-tors are all completed by the core, multiple PVP memory pipe jobs can be chained without any further core intervention as the DMA operations run through the chained lists and handle the multiple dataflows autonomously. The following description assumes the memory pipe is inactive, (a non initialized state PVP_CTL.MPEN =0).To run a PVP memory pipe job from the PVP memory pipe job list, the PVP first loads the memorypipe configuration into the respective shadow registers of the respective PCP elements to build the PVP memory pipe. The configuration within the shadow register is activated (transferred from shadowregister to active register) using hardware triggers (staggered transfer). This configuration stream into the shadow registers is handled by DMA 45 which is controlled by a linked descriptor list. The last valid descriptor must contain a DMA_CFG.FLOW field =0 (STOP Mode) to gracefully stop the DMA 45 aftercompleting the PVP memory pipe job list and avoid loading non valid data into PVP memory pipeconfiguration register. All DMA_CFG descriptor fields within the linked list have DMA_CFG.FLOW =6 or =7 (descriptor list mode) or alternatively DMA_CFG.FLOW =4 (descriptor array mode).A 1-dimensional DMA operation is shown in the following figure. Note however, a 2-dimensionalDMA operation can also be used.Figure 30-55:Static Linked Descriptor List for Configuration Data (BCL Data)•Job List Global TriggerAfter the first initialization of the linked descriptor list the parameter registers of DMA 45 have to beinitialized, particularly the DMA_DSCPTR_NXT and DMA_CFG register. The DMA 45 is started but thenstalls until the PVP memory pipe is enabled and the PVP_IPFn_FCNT =0.To generate a unique synchronization signal that synchronizes the Data Out (DMA 42) and Data In(DMA 43) stream, all DMA_CFG descriptor fields of DMA 45 should have the bit field DMA_CFG.TRIG =1.This generates a trigger signal after a new configuration is loaded into the shadow registers.•Job List StartAfter setting up the three DMA linked lists, the memory pipe has to be activated (PVP_CTL.MPEN =1).。

FPGA可编程逻辑器件芯片EP1C12Q240I8N中文规格书

SPORT Controllers •Performs A-law and -law hardware companding on transmitted and received words. (See “Companding” on page24-31 for moreinformation.)•Internally generates serial clock and frame sync signals in a wide range of frequencies or accepts clock and frame sync input from anexternal source•Operates with or without frame synchronization signals for each data word, with internally generated or externally generated framesignals, with active high or active low frame signals, and with eitherof two configurable pulse widths and frame signal timing •Performs interrupt-driven, single word transfers to and from on-chip memory under processor control•Provides direct memory access transfer to and from memory under DMA master control. DMA can be autobuffer-based (a repeated,identical range of transfers) or descriptor-based (individual orrepeated ranges of transfers with differing DMA parameters).•Has a multichannel mode for TDM interfaces. Each SPORT can receive and transmit data selectively from a time-division-multi-plexed serial bit stream on 128 contiguous channels from a streamof up to 1024 total channels. This mode can be useful as a networkcommunication scheme for multiple processors. The 128 channelsavailable to the processor can be selected to start at any channellocation from 0 to 895 = (1023 – 128). Note the multichannelselect registers and the WSIZE register control which subset of the128 channels within the active region can be accessed.ADSP-BF54x Blackfin Processor Hardware ReferenceProgramming ExamplesTWI0_SLAVE_INIT:/***********************************************************Enable the TWI0 controller and set the Prescale valuePrescale = 10 (0xA) for an SCLK = 100 MHz (CLKIN = 50MHz)Prescale = SCLK / 10 MHzP1 points to the base of the system MMRsP0 points to the base of the core MMRs***********************************************************/R1 = TWI0_ENA | 0xA (z);W[P1 + LO(TWI0_CONTROL)] = R1;/***********************************************************Slave addressprogram the address to which this slave responds to.this is an arbitrary 7-bit value***********************************************************/R1 = 0x5F;W[P1 + LO(TWI0_SLAVE_ADDR)] = R1;/***********************************************************Pre-load the TX FIFO with the first two bytes to betransmitted in the event the slave is addressed and a transmit is required***********************************************************/R3=0xB537(Z);W[P1 + LO(TWI0_XMT_DATA16)] = R3;/***********************************************************FIFO Control determines whether an interrupt is generatedfor every byte transferred or for every two bytes.A value of zero which is the default, allows for single byteevents to generate interrupts***********************************************************/ADSP-BF54x Blackfin Processor Hardware Reference。

CL1120规格书

CL1120CL1120_CN Rev. 1.4 1 CL1120CL1120_CN Rev. 1.4 2 管脚描述管脚号 管脚名 1 GND接地端2 GD外置功率3 CS 变压器原边电流采样端4 FB5 COMP6 VDDCL1120CL1120_CN Rev. 1.4 3 CL112020W 原边控制高精度恒压/恒流PWM 控制器CL1120_CN Rev. 1.4 4 最大额定值 (注)参数范围电源电压-0.3 V to VDD CLAMP齐纳电压钳位连续电流 10 mA COMP 脚电压 -0.3 V to 7 V CS 脚电压 -0.3 V to 7 V FB 脚电压-0.3 V to 7 V 最小/最大工作结温T J -40 ℃ to 125 ℃ 最小/最大存储温度T stg -55 ℃ to 150 ℃焊接温度(焊锡,10秒 )260 ℃封装耗散等级封装R θJA (/W)℃ SOT-23-6L 208.2注:超出“最大额定值”可能损毁器件。

推荐工作范围内器件可以工作,但不保证其特性。

长时间运行在最大额定条件下可能会影响器件的可靠性。

CL112020W 原边控制高精度恒压/恒流PWM 控制器CL1120_CN Rev. 1.4 5 电气特性(如果没有特殊说明,环境温度= 25, ℃输入电压=16V)符号 参数 测试条件 最小值典型值. 最大值单位 电源电压(VDD 电压) I ST 待机电流 VDD =13V 5 20 uAI OP 工作电流 FB=2V, CS=0V,VDD=18V 2 3mAV UVLO(ON) 进入欠压锁定电压 VDD 电压下降 8.2 9.0 10.5 V V UVLO(OFF) 退出欠压锁定电压 VDD 电压上升 13.5 14.8 16.0 V VDD CLAMP 电源最大工作电压 IDD =10mA 27 28.5 30 V V OVP 过电压保护电压 使VDD 上升至栅极关断26 27.5 29 V电流检测输入 t LEB前沿消隐时间625 nsV th_OC 过电流阈值 880 910 940 mVt D_OC 过流动作延迟 110 ns Z SENSE_IN 输入阻抗 50 k Ω t SS 软启动时间 17 ms频率f MAX Note 1 IC 最高频率 70 75 80 kHz f NOM 系统最大开关频率 55 kHzf SARTUP FB =0V, COMP =5V 14 kHzf/f △OP Note 2频率抖动范围 ±6 %误差放大器V REF_EA EA 参考电压 1.97 2 2.03 VGAIN EA 直流增益 60 dBI COMP_MAX 当前最大输出线压降补偿FB=2V, COMP=0V 35 50 65 uA栅极驱动器输出 VOL 输出低电平 Io=20mA 1 V VOH 输出高电平 Io=20mA 8 V V OUT_CLAMP 输出钳位电压 16 V t OR 输出上升时间 C LOAD =0.5nF 650 ns t OF 输出下降时间 C LOAD =0.5nF 40 nsNote 1:f MAX 所示为集成电路内部最大时钟频率。

FPGA可编程逻辑器件芯片EP4CE115F29C7中文规格书

When the bits settings are EPPI_CTL.SPLTEO =1, EPPI_CTL.SUBSPLTODD =1 and EPPI_CTL.DMACFG =0, note that although the second Chroma component (U0U1U2U3 in the tables above) sent over the DMA bus is completely packed before the Luma component (Y4Y5Y6Y7 in the tables above), it is intentionally held until that previous word is moved out. This allows the separation of Luma and Chroma values into individual buffers when using 2D-DMA.Table 31-27:8-bit Split Receive Mode with SKIPEN = 0 and SWAPEN = 1 Pin Data (8 bits)SPLTEO=1SUBSPLTODD=0SW APEN=1SKIPEN=0SKIPEO=XSPLTEO=1SUBSPLTODD=1SW APEN=1SKIPEN=0SKIPEO=X DMACFG=1DMACFG=0DMACFG=1DMACFG=0PRIMARY DMA CHANNEL SECONDARY DMA CHANNELPRIMARYDMACHANNEL PRIMARY DMA CHANNEL SECONDARY DMA CHANNEL PRIMARY DMA CHANNEL V 0Y 0U 0Y 1V 1Y 2U 1V 0U 0V 1U 1 V 0U 0V 1U 1 Y 3Y 0Y 1Y 2Y 3Y 0Y 1Y 2Y 3 Y 0Y 1Y 2Y 3Y 0Y 1Y 2Y 3V 2Y 4U 2Y 5V 3V 0V 1V 2V 3 V 0V 1V 2V 3 Y 6U 3V 2U 2V 3U 3 V 2U 2V 3U 3U 0U 1U 2U 3 Y 7Y 4Y 5Y 6Y 7Y 4Y 5Y 6Y 7 Y 4Y 5Y 6Y 7Y 4Y 5Y 6Y 7 V 4 U 0U 1U 2U 3Configuring 16-Bit Split Receive Mode with SPLTWRD=1For 16-bit split receive mode, the EPPI_CTL.PACKEN bit is not valid. The EPPI always packs two 16-bit words into one 32-bit word. The EPPI_CTL.SPLTWRD bit is only valid when the EPPI_CTL.DLEN bit=16 bits.Y 0U 0V 0U 0V 0U 0 Y 1Y 0Y 1Y 0Y 1Y 0Y 1Y 0Y 1 V 1V 0V 1V 0V 1 Y 2U 1V 1U 1V 1U 1U 0U 1 Y 3Y 2Y 3Y 2Y 3Y 2Y 3Y 2Y 3 V 2 U 0U 1 Table 31-30:16-bit Split Receive Mode with SPLTWRD = 1, SKIPEN = 0 and SWAPEN = 0Pin Data(16 bits)SPLTEO=1SUBSPLTODD=0SW APEN=0SKIPEN=0SKIPEO=XSPLT_EVEN_ODD=1SUBSPLTODD=1SW APEN=0SKIPEN=0SKIPEO=X DMACFG=1DMACFG=0DMACFG=1DMACFG=0Primary DMA Channel Secondary DMA Channel Primary DMA Channel Primary DMA Channel Secondary DMA Channel Primary DMA Channel V 0Y 0U 0Y 1V 1Y 2U 1Y 3 Y 3Y 2Y 1Y 0 U 1V 1U 0V 0 Y 3Y 2Y 1Y 0 Y 3Y 2Y 1Y 0Y 3Y 2Y 1Y 0Table 31-29:16-bit Split Receive Mode with SPLTWRD = 0, SKIPEN = 0 and SWAPEN = 1 (Continued)Pin Data (16 bits)SPLTEO=1SUBSPLTODD=0SW APEN=1SKIPEN=0SKIPEO=XSPLTEO=1SUBSPLTODD=1SW APEN=1SKIPEN=0SKIPEO=X DMACFG=1DMACFG=0DMACFG=1DMACFG=0PRIMARY DMA CHANNEL SECONDARY DMA CHANNELPRIMARYDMACHANNEL PRIMARY DMA CHANNEL SECONDARY DMA CHANNEL PRIMARY DMA CHANNELE NHANCED P ARALLEL P ERIPHERAL I NTERFACE (EPPI)EPPI P ROGRAMMING M ODELConfiguring 10/12/14-Bit Transmit ModesFor 10, 12, or 14-bit non-split transmit modes, if the EPPI_CTL.PACKEN bit=1, the DMA is a 32-bit DMA and the EPPI unpacks the 32-bit word from memory into two 16-bit data words, then transmits therequired LSBs from each. The EPPI transmits either the most significant word or the least significant word as the first data, depending on the EPPI_CTL.SWAPEN bit setting. If EPPI_CTL.PACKEN =0, the DMA is a 16-bit DMA and the EPPI transmits the required LSBs. The EPPI_CTL.SWAPEN bit has no effect when the EPPI_CTL.PACKEN bit=0.Configuring 16-Bit Transmit ModeFor 16-bit non-split transmit mode, if the EPPI_CTL.PACKEN bit=1, the DMA is a 32-bit DMA and the EPPI unpacks the 32-bit word from memory into two 16-bit data words to transmit. The EPPI transmits either the MSBs or the LSBs as the first data, depending on the EPPI_CTL.SWAPEN bit setting. If the EPPI_CTL.PACKEN bit=0, the DMA is a 16-bit DMA and the EPPI transmits the data as is. The EPPI_CTL.SWAPEN has no effect when EPPI_CTL.PACKEN bit=0.Table 31-32:Data Sent in 8-bit Transmit Mode with Packing Disabled DMA Data (16 bits)Pin Data SW APEN=X 0x12340x340x23450x450x34560x56Table 31-33:10-bit Transmit Mode with Packing EnabledDMA Data (32 bits)Pin Data when SW APEN=0Pin Data when SW APEN=10x1111 22220x2220x1110x3333 44440x1110x2220x0440x3330x3330x044Table 31-34:10-bit Transmit Mode with Packing DisabledDMA Data (16 bits)Pin Data SW APEN=X 0x12340x2340x23450x3450x34560x0560x45670x167。

FPGA可编程逻辑器件芯片10AX115R3F40I2LGAA中文规格书

Symbol

Performance (for All Speed Grades)

tDQS_PSERR

5

Unit ps

Memory Output Clock Jitter Specifications

(71) –E1S and –E2S speed grades are applicable to both VCC = 0.9 V and 0.95 V. –E3S speed grade is only applicable to VCC = 0.9 V. (72) Clock Boost Factor (W) is the ratio between the input data rate and the input clock rate. (73) This is achieved by using the PHY clock network.

Symbol

Condition

–E1S(71), –E1H, –I1S(71), –I1H

–E2L, –E2S(71), –I2L, – I2S(71)

Min

Typ

Max

Min

Typ

Max

fHSCLK_in (input clock frequency) True

Clock boost factor

Protocol

Parameter

Symbol

Non-SmartVID

SmartVID (–3V Speed Grade)

Unit

Data Rate (Mbps)

FPGA可编程逻辑器件芯片XCKU115-2FFLVA1517I中文规格书

Chapter2 Board Setup and ConfigurationBoard Component LocationFigure2-1 shows the KCU1500 board component locations. Each numbered componentshown in the figure is keyed to Table2-1. Table2-1 identifies the components, references the respective schematic page numbers, and links to a detailed functional description of the components and board features in Chapter3.Electrostatic Discharge Cautionreplacing components.To prevent ESD damage:•Use an ESD wrist or ankle strap and ensure that it makes skin contact. Connect the equipment end of the strap to an unpainted metal surface on the chassis.•Avoid touching the adapter against your clothing. The wrist strap protects components from ESD on the body only.•Handle the adapter by its bracket or edges only. Avoid touching the printed circuit board or the connectors.•Put the adapter down only on an antistatic surface such as the bag supplied in your kit.•If you are returning the adapter to Xilinx Product Support, place it back in its antistatic bag immediately.Chapter 3:Board Component DescriptionsStep 5: Verify Successful Board InstallationDuring execution of xbinst, a simple, prebuilt executable and the associated xclbin is included in the <xbinst-area>/test directory. This executable checks that the drivers and the DSA are correctly installed and that the setup is operating as expected. These steps are required to perform the installation validation:1.Source the setup.sh (Bash) or setup.csh (csh/tcsh):$ source <xbinst-area>/setup.[sh|csh]2.Change to the test directory and run the validation executable.If the test directory is not write-enabled, it might be necessary to run the executable from a different directory with an absolute path to the verify.exe.3.Execute the following:$ cd /tmp/$ <xbinst-area>/test/verify.exe <xbinst-area>/test/verify.xclbinThe system is correctly functioning if the output looks similar to the following:CL_PLATFORM_VENDOR XilinxCL_PLATFORM_NAME XilinxGet 1 devicesUsing 1th deviceloading <..path to..>/verify.xclbinRESULT:Hello WorldDebugging the InstallationThis section covers debugging and troubleshooting. For software support and related software debug techniques, see the SDx Command and Utility Reference Guide (UG1279) [Ref6]. For more information, see Answer Record 43745.This section lists the commands used to query and investigate different scenarios such as: • A sanity check needs to be performed on a new board.•The host application is abruptly interrupted and the board or the driver is in a stale or unknown mode.•The deployment machine needs to be rebooted to set everything back to a working state.The commands in this section are used for debugging. The first two commands are SDAccel board utility tools that are further detailed in the SDx Command and Utility Reference Guide (UG1279) [Ref6]. The other commands are Linux command line tools: lspci and dmesg.。

FPGA可编程逻辑器件芯片EP3SL110F1152C2中文规格书

after the lane's RSFEC_ERR_INJ_TX.rate or RSFEC_ERR_INJ_TX.pat has been cleared.

One entry per physical lane, regardless of RSFEC_CORE_CFG.frac.

0x00

9.5.24. rsfec_corr_cw_cnt (Low)

Bits 4-7 covers the data buffers for the RS decoding. When RSFEC_CORE_CFG.frac = frac4, these are used 1:1 for the physical lanes 0-3.

SW Access Reset HW Access Protection

W1C WO1S -

0x00

W1C WO1S -

0x00

9.5.22. rsfec_err_inj_tx

Register Name rsfec_err_inj_tx_0 rsfec_err_inj_tx_1 rsfec_err_inj_tx_2 rsfec_err_inj_tx_3

Description RS-FEC error injection mode

Bit Name

Description

6:0 skew

Lane skew value (unit is 80 bits). Only valid when the RX lanes are aligned. Only applicable when RSFEC_CORE_CFG.frac = none (100GE/128GFC).

9.5.21. rsfec_core_ecc_hold

11F1E2 产品手册说明书

11F1E2产品手册产品手册更新历史文档版本更新日期更新内容适用硬件版本V1.02023-4-12创建文档V1.0V1.12023-6-29修改售后维修地址;V1.0V1.22023-7-17增加串口和I/O的功能描述;V1.0电子元件和电路对静电放电很敏感,虽然本公司在设计电路板卡产品时会对板卡上的主要接口做防静电保护设计,但很难对所有元件及电路做到防静电安全防护。

因此在处理任何电路板组件时,建议遵守防静电安全保护措施。

防静电安全保护措施包括但不限于以下几点:运输、存储过程中应将板卡放在防静电袋中,直至安装部署时再拿出板卡。

在身体接触板卡之前应将身体内寄存的静电释放掉:佩戴放电接地腕带。

仅在静电放电安全区域内操作电路板卡。

避免在铺有地毯的区域搬移电路板。

通过板边接触来避免直接接触板卡上的电子元件。

注意事项及售后维修注意事项◆使用产品之前,请仔细阅读本手册,并妥善保管,以备将来参考;◆请注意和遵循标注在产品上的所有警示和指引信息;◆请使用配套电源适配器,以保证电流、电压的稳定;◆请在凉爽、干燥、清洁的地方使用本产品;◆请勿在冷热交替的环境中使用本产品,避免结露损坏内部元器件;◆请勿将任何液体泼溅在本产品上,禁止使用有机溶剂或腐蚀性液体清洗本产品;◆请勿在多尘、脏乱的环境中使用本产品,如果长期不使用,请包装好本产品;◆请勿在振动过大的环境中使用,任何跌落、敲打都可能损坏线路及元器件;◆请勿在通电情况下,插拔核心板及外围模块;◆请勿自行维修、拆解本产品,如产品出现故障应及时联系本公司进行维修;◆请勿自行修改或使用未经授权的配件,由此造成的损坏将不予保修;售后维修1保修期限◆底板、核心板:3年(非人为损坏)2联系方式◆地址:北京市海淀区上地三街9号金隅嘉华大厦C座10层C1106/C1108◆收件人:RMA◆电话:************◆邮寄须知:提前与本公司销售联系,会尽快安排技术人员核实排除由误操作引起的错误,核实后请将设备邮寄到本公司,邮寄时请附物品清单及故障原因,方便核实,以免快递过程中的丢失、损耗。

FPGA可编程逻辑器件芯片XCKU115-2FLVA1517E中文规格书

SummaryThe diagrams in this chapter show a top-view perspective of the package pinout of each UltraScale and UltraScale+ device/package combination. Table 3-1 through Table 3-4contain cross references to the device diagrams. The I/O-bank diagram shows the location of each user I/O and GTH/GTY transceiver and the respective bank or GT quad. Theconfiguration-power diagram shows the location of every power pin and dedicated as well as multi-function configuration pin in the package. See Package SpecificationsDesignations in Chapter 2 for definitions of Evaluation Only , Engineering Sample , and Productiondevice diagrams.Table 3-1:Cross-Reference to Kintex UltraScale and XQ Kintex UltraScale Device Diagrams byPackage PackageFootprint Compatible DevicesPackage StatusFBVA676XCKU035page 186XCKU040page 186Production RBA676XQKU040page 186Production SFVA784XCKU035page 188XCKU040page 188Production FBVA900XCKU035page 190XCKU040page 190Production FFVA1156XCKU025page 192XCKU035page 194XCKU040page 196XCKU060page 198XCKU095page 200Production RFA1156XQKU040page 196XQKU060page 198XQKU095page 200Production FFVA1517XCKU060page 202Production找FPGA 和CPLD 可编程逻辑器件,上深圳宇航军工半导体有限公司ASCII Pinout FilesLinks to the ASCII pinout information by device/package are listed in Table2-1. The pinouts of XQ devices are identical to the pinouts of their equivalent XC devices in footprint compatible package. Links in this table to XQ devices open the XC version of the pinout file. For example, the link to RBA676-XQKU040 opens the FBVA676-XCKU040 pinout file. Download all available Kintex UltraScale, Kintex UltraScale+, Virtex UltraScale, and Virtex UltraScale+ FPGA package/device/pinout files at:Note:All package files are ASCII files in TXT and CSV file format. Only the available files listed in Table2-1are linked and consolidated in this ZIP file.FFVE900XCKU9PProductionXCKU13PProductionFFVA1156XCKU025ProductionXCKU035ProductionXCKU040ProductionXCKU060ProductionXCKU095ProductionXCKU11PProductionXCKU15PProductionFFRA1156XQKU15P ProductionRFA1156XQKU040ProductionXQKU060ProductionXQKU095ProductionFFVA1517XCKU060 ProductionFLVA1517XCKU085 ProductionXCKU115ProductionFFVC1517XCKU095ProductionXCVU065ProductionXCVU080ProductionXCVU095ProductionXCVU3PProductionFFRC1517XQVU3P ProductionFFVD1517XCVU080 ProductionXCVU095ProductionFLVD1517XCKU115 ProductionXCVU125ProductionFFVE1517XCKU11P ProductionXCKU15PProductionFFRE1517XQKU15P ProductionRLD1517XQKU115 ProductionFFVA1760XCKU15P ProductionFFVB1760XCKU095ProductionXCVU080ProductionXCVU095ProductionFLVB1760XCKU085ProductionXCKU115ProductionXCVU125ProductionFFVE1760XCKU15P ProductionFLVD1924XCKU115 ProductionTable 2-1:Package/Device Pinout Files (Cont’d)Package Device。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4 5/6 7/8

管脚名 VDD COMP

FB

CS DRAIN GND

I/O

描述

P 电源

I 环路补偿提高恒压稳定性

辅助绕组进行电压反馈。连接电阻分压器和辅助绕组反映输出电

I

压。PWM占空比周期由EA输出和引脚4的电流检测信号决定

I 电流检测输入

O 高压MOSFET的漏极引脚,该引脚连接到变压器原边

CL1112

SEMICONDUCTOR

使用说明

CL1112是一款高集成度的原边反馈PWM控制芯片,其可有效提高低功率反激变换器的性能。 原边反馈拓扑结构可简化控制器电路设计,特别在电池充电器应用中。由于CL1112采用原边采样 和校准,因此不需要TL431和光耦合器。在无二次反馈电路下,准确地实现恒压和恒流控制。 CL1112具有频率抖动功能,其可提高系统的EMI性能。结果,相比与常规充电器设计或线性变压 器,采用CL1112的充电器具有更轻的质量、更小的体积和更低的成本。

CL1112

SEMICONDUCTOR

●电流检测和前沿消隐

CL1112提供了逐周期电流限制,CS引脚的采样电阻对开关电流进行侦测。在功率开关导通时, 采样电阻上会出现开启尖峰。为避免由开启尖峰所引起的误操作,采用在功率开关导通后屏蔽CS 引脚采样信号625ns来实现。在屏蔽期间电流采样比较器输出被置位,芯片驱动端不会关闭。

打标 CL1112S CL1112D

最大额定值 (注释1)

参数

漏极电压(关闭状态) 电源电压 齐纳电压钳位连续电流 补偿电压 CS 输入电压 FB 输入电压 最小/最大工作结温Tj 最小/最大存储温度Tstg 焊接温度(焊锡, 10secs )

范围

-0.3V to Bvdss -0.3 to 电压钳位

2 第 1/1 9页

脚位由打标 文字方向确定

版本:CL1112_CN_SZ_31 支持:+86 13823600403 版次更新:2013/05/02

SEMICONDUCTOR

封装耗散等级

封装 SOP8 DIP8

RθJA (℃/W) 90 40

CL1112

10 mA -0.3 to 7V -0.3 to 7V -0.3 to 7V -20 to 150 ℃ -55 to 150 ℃

260 ℃

注释 1: 超出“绝对最大额定值”可能损毁器件。推荐工作范围内器件可以工作,但不保证其特

性。.运行在绝对最大额定条件下长时间可能会影响器件的可靠性。

管脚描述

管脚号 1 2

SEMICONDUCTOR

电气特性

(TA = 25℃, VDD=16V, 如果没有特殊说明)

CL1112

符号

参数

电源电压(VDD电压)

IDD_ST

待机电流

IDD_op

工作电流

UVLO(ON) UVLO(OFF) VDD_clamp

OVP

VDD欠压锁定时电压 VDD锁定退出时电压 电源最大工作电压

过电压保护开始

●输出电压设置

通过电阻对Ra和Rb的分压,CL1112的FB脚位可检测辅助绕组反激信号。FB电压与参考电 压间的差值通过误差放大器放大来控制开关信号的占空比。

输出电压可由下式得出。为了提高输出电压的精确度,变压器的漏感应尽可能的降低。

VOUT

=

2.0V × (1+

Ra Rb

)× (

Ns Na

)

其中:Ra和Rb为顶端和低端反馈电阻值。

●控制保护

良好的电源供应系统的可靠性是由其丰富的保护功能实现的。包括逐周期电流限制(OCP), VDD电压钳位功能,软启动电源和欠压保护等特性。电源输入由变压器辅助绕组提供,当电源电 压低于UVLO(ON)时CL1112的输出自动关闭,而电源转换器输入,电源启动。

2 第 6/6 9页

●软启动

CL1112采用了内部软启动以尽量减少在电源启动时的部分电气过应力。软启动的时长设定 为17ms。当VDD电压达到UVLO欠压保护时,控制算法将使峰值电压阈值逐渐从几乎为零的值上 升到正常设置的0.90V。而且每次重新启动都有一个软启动过程。

●恒压/恒流工作

CL1112设计可以对恒流/恒压进行更好的控制,控制特性如图1所示,电池充电器应用中通常 具有两种运作模式,恒压充电和恒流充电。当电池电压过低时,充电器是恒流充电,这是对电池 充电的最主要的方式,大部分的能量进入电池。当电池电压达到电池饱和电压时,充电电流逐渐 变小,充电器进入恒压模式。最后,充电电流继续减小直到达到0。

电流检测输入

TLEB Vth_oc Td_oc ZSENSE_IN T_ss 频率 Freq_MaxNote 1

Freq_Nom

LEB时间 过电流阈值 OCP传播延迟 输入阻抗 软启动时间

IC最高频率 系统额定开关频率

测试条件

最小值 典型值. 最大值. 单位

VDD=13V 操作电源电流FB=2V,

CS=0V, VDD =20V VDD 电压下降 VDD电压上升

P 接地

2 第 2/2 9页

版本:CL1112_CN_SZ_31 支持:+86 13823600403 版次更新:2013/05/02

SEMICONDUCTOR

结构框图

CL1112

2 第 3/3 9页

版本:CL1112_CN_SZ_31 支持:+86 13823600403 版次更新:2013/05/02

2 第 9/9 9页

版本:CL1112_CN_SZ_31 支持:+86 13823600403 版次更新:2013/05/02

Ns和Na为变压器次端和辅助端线圈的匝数比。

原边反馈控制器的负载调整率和线性调整度对于变压器的结构较为敏感。为了得到较好的调

整度和效率,建议变压器采用三明治结构。

●电感校正电路

在初级励磁电感过高或过低时,CL1112将通过调节振荡器频率自动对此进行补偿。由于这 个控制器用于在非连续导通模式下工作,因此输出功率与设定初级电感直接成正比,并可通过调 节开关频率对其容差进行完全补偿。

CL1112

SEMICONDUCTOR

12W原边控制高精度恒压/恒流PWM控制器

概述

CL1112是一款性能优异的原边反馈控制器,它集成了多种保护功能。CL1112最大限度地 减少了系统元件数目并采用 SOP-8/DIP-8封装,这些使得CL1112较好地应用于低成本的设计中。 CL1112具有低电流启动功能、电流采样LEB和内部斜率补偿。同时,CL1112具有过压保护功能, 以防止电路在异常情况下被损坏。

版本:CL1112_CN_SZ_31 支持:+86 13823600403 版次更新:2013/05/02

SEMICONDUCTOR

封装说明:SOP-8

CL1112

2 第 7/7 9页

版本:CL1112_CN_SZ_31 支持:+86 13823600403 版次更新:2013/05/02

特性

◆ ±5%以内的恒压精度, ±5%以内的恒流精度 ◆ 原边反馈省去TL431和光耦以降低成本 ◆ 低启动电流:5μA(典型值) ◆ 低工作电流:2mA(典型值) ◆ 可调输出恒定电压、恒定电流及功率 ◆ 峰值电流模控制 ◆ 补偿变压器电感容差 ◆ 补偿电缆压降 ◆ 内置频率抖动技术改善EMI ◆ 内置软启动功能 ◆ 内置前沿消隐电路(LEB) ◆ 逐周期电流限制 ◆ 欠压保护(UVLO) ◆ VDD OVP保护功能 ◆ VDD电压钳位功能 ◆ 内置MOSFET功率管

应用范围

12W低功率的AC-DC离线开关电源应用 于: ◆ 手机/无绳电话充电器 ◆ 数码相机充电器 ◆ 小功率电源适配器 ◆ 电脑/电视辅助电源 ◆ 替代线性电源

CL1112采用SOP-8和DIP-8封装

典型应用

典型 CC/CV 曲线

管脚分布图

SOP8/DIP8

图中管脚为示意作用非实物脚位

图1 典型CC/CV曲线

SEMICONDUCTOR

封装说明:DIP-8

CL1112

2 第 8/8 9页

版本:CL1112_CN_SZ_31 支持:+86 13823600403 版次更新:2013/05/02

SEMICONDUCTOR

CL1112

z 此处描述的信息有可能有所修改,恕不另行通知。 z 芯联半导体不对由电路或图表描述引起的与的工业标准,专利或第三方权利相关

●欠压保护

CL1112 采 用 一 个 欠 压 保 护 比 较 器 实 现 检 测 VDD 脚 位 的 电 压 。 以 保 证 供 应 电 源 足 够 运 行 CL1112 PWM控制器和驱动功率MOSFET。欠压保护为了在启动时电源电压出现骤降的情况下保 护芯片,开启和关闭阈值分别为14.8V和9V。

●输出线压降补偿

常规芯片在恒压模式下,通过改变MOSFET管导通时间来调节在片反馈电压,其不包括在电 线上的压降。这样导致了由于采用不同规格不同长度的电线,会产生不同的输出电压。CL1112 具有线损补偿功能,可补偿输出电压在电线上的压降。通过内置电流流入电阻分压器在FB脚位产 生补偿电压。随着转换器负载从空载增大至峰值功率点(恒压与恒流之间的切换点),将通过增 大反馈引脚参考电压对输出电缆上的压降进行补偿。控制器根据状态调节器的输出来决定输出负 载以及相应补偿的程度。

FB=0V, Comp=5V

14

KHz

f/Freq

频率抖动范围

±4

%

误差放大器

Vref_EA

EA参考电压

1.97

2

2.03

V

Gain

EA直流增益

60

dB