基于ARM微处理器的硬件系统设计模板

2020年chap10基于ARM微处理器的硬件系统设计参考模板

• AT91SAM9263具备两组独立的外部存储器总线EBI0 和D控制器,可支持2D图形加速、双通道 DMA和图像传感器接口

• 集成了多种标准外设接口,例如USART,SPI,TWI, 定时计数器,PWM,多媒体卡接口和CAN控制器等

10

意法半导体公司的ARM微处微理处理器器系统芯结构与片嵌入式系统设计

• 意法半导体有限公司(STMicroelectronics)是全球最大的半导 体公司之一。其采用ARM内核的微处理器主要包括三个系列: 采用Cortex-M3内核的STM32系列、采用ARM7TDMI内核的 STR7系列和采用ARM966E-S内核的STR9系列。

• 三星公司采用ARM内核的微处理器主要按照应用来划分,如 通用型32位MCU主要采用ARM7TDMI内核,面向CAN/LIN

5 总线、以太网、发动机控制和RFID等应用场合。

微处理器系统结构与嵌入式系统设计

三星公司的S3C2440A

• 采用ARM920T内核,实 现了MMU,AMBA总线 和哈佛架构的高速缓冲体 系结构。

微处理器系统结构与嵌入式系统设计

第十章 基于ARM微处理器的硬 件系统设计

5学时

1

微处理器系统结构与嵌入式系统设计

第十章 基于ARM微处理器的硬件系统设计

10.1 基于ARM微处理器的系统设计概述(理解) 10.2 S3C2440A微处理器(了解)

✓ S3C2440A微处理器简介 ✓ S3C2440A内部结构及主要特性 ✓ S3C2440A外部引脚

6

微处理器系统结构与嵌入式系统设计

基于ARM的嵌入式系统硬件结构设计PPT课件

第22页/共141页

初始值 0

0 0 0

0 0 0

5.1.1 存储器控制器

WS5 DW5 ST4

WS4 DW4 ST3

WS3 DW3

[22] [21:20] [19]

起始 _ffff

_ffff

_ffff

_ffff

_ffff

7号地址

地址 0x3020 起始 _0000

0x3040 _0000

0x3080 _0000

0x3100 _0000

0x3200 _0000

结束 0x303f 0x307f 0x30ff 0x31ff 0x33ff

地址 _ffff

_ffff

_ffff

第1页/共141页

Samsung S3C44B0X

• Samsung S3C44B0X微处理器是三星公司专为手持 设备和一般应用提供的高性价比和高性能的微控制 器解决方案,它使用ARM7TDMI核,工作在66MHZ。

• 芯片还集成了8KB Cache、外部存储器控制器、 LCD控制器、4个DMA通道、2通道UART、1个多主 I2C总线控制器、1个IIS总线控制器,5通道PWM定 时器及一个内部定时器、71个通用I/O口、8个外部 中断源、实时时钟、8通道10位ADC等。

第8页/共141页

AMBA(Advanced Microcontroller Bus Architecture) 可将 RISC处理器集成在其它 IP芯核和外设中,

2.0版AMBA标准定义了 三组总线:AHB(高性能 总线)、ASB(系统总线)、 和APB(AMBA外设总线)。

七基于ARM的嵌入式系统硬件结构设计.ppt

自动引导模式流程

自动引导模式流程: 复位; 如果自动引导模式使能,Nand Flash中的前4KB代码拷贝到内部

的小石头区域; 小石头映射到nGCS0; CPU开始执行小石头区域中的代码。 Nand Flash模式: 通过NFCONF寄存器设置Nand Flash配置; 把Nand Flash命令写入NFCMD寄存器; 把Nand Flash地址写入NFADDR寄存器; 读/写数据同时通过NFSTAT寄存器检测Nand Flash状态。读操作

5

S3C2410X及片内外围简介

6

S3C2410X支持大、小端模式,将存储空间分成8组( Bank),每组大小是128MB,共计1GB。

7

特殊功能寄存器

1、内存控制器(Memory Controller):内存控制器为访问外部存 储空间提供存储器控制信号,共有13个寄存器。

8

特殊功能寄存器

2.Nand Flash 控制器 S3C2410X支持Nand Flash启动,启动代码存储在Nand Flash上 。启动时,Nand Flash的前4KB将被装载到内部的固定地址的 SRAM中,利用硬件纠错码ECC对数据的正确性检验,然后开始 执行其中的启动代码。一般情况下,该启动代码会把Nand Flash 中的内容拷贝到SDRAM中去,拷贝完后,主程序将在SDRAM中 执行。操作流程如图4.13所示。

12

时钟和电源管理

(1)锁相环PLL。 锁相环最基本的结构由3个基本的部件组成:鉴相器(PFD)、环 路滤波器(Loop Filter)和压控振荡器(VCO),如图4.14所示 。鉴相器是个相位比较装置,它把输入信号Fref与压控振荡器输 出分频后的信号Fvco的相位进行比较,产生对应于两个信号相位 差的误差电压,该误差电压控制调整压控振荡器的频率,以达到 与输入信号同频。

基于ARM的硬件系统设计

由于NOR技术Flash Memory的擦除和编程速度较慢,而块尺 寸又较大,因此擦除和编程操作所花费的时间很长,在纯 数据存储和文件存储的应用中,NOR技术显得力不从心。

11

NAND技术

NAND技术 Flash Memory具有以下特点: 以页为单位进行读和编程操作,1页为256或512字节;以 块为单位进行擦除操作,1块为4K、8K或16K字节。具 有快编程和快擦除的功能,其块擦除时间是2ms;而 NOR技术的块擦除时间达到几百ms。 数据、地址采用同一总线,实现串行读取。随机读取速 度慢且不能按字节随机编程。 芯片尺寸小,引脚少,是位成本(bit cost)最低的固态存 储器,突破了每兆字节1元的价格限制。 芯片包含有失效块,其数目最大可达到3~35块(取决于 存储器密度)。失效块不会影响有效块的性能,但设计 者需要将失效块在地址映射表中屏蔽起来。

I/O子系统的目标是对RTOS和应用程序员隐藏设备特定的信 息,并且对系统的外围I/O设备提供一个统一的访问方法。

应用程序 RTOS

I/O子系统 设备驱动程序

中断处理程序 I/O设备硬件

31

从不同角度看I/O系统

从系统软件开发者角度看,I/O操作意味着与设备的 通信、对设备编程初始化和请示执行设备与系统之间 的实际数据传输以及操作完成后通知请求者。系统软 件工程师必须理解设备的物理特性,如寄存器的定义 和设备的访问方法。

Memory Stick

Sony

15

2410的存储器系统

— 可通过软件选择大小端 — 地址空间:每个Bank 128Mbytes (总共 1GB) —除 bank0 (16/32-bit) 外,所有的Bank都可以通过编程选

五、基于ARM的嵌入式系统硬件结构设计

DMA传输速度取决于I/O设备的传输速度、内存设备的速度和DMA控 制器的速度。

通过指定源地址、目的内存地址和传输到DMA控制器长度,处理器 建立传输操作。

CPU

DMA 控制器

主存储器

I/O设备

33

字符模式设备与块模式设备

根据设备如何处理与系统之间的数据传输方法可将设 备分为字符模式设备和块模式设备 字符模式设备:允许非结构的数据传输。数据传输典 型地采用串行的形式,每次一个字节;字符设备通常 是简单的设备,如串口、键盘等;当系统到设备的传 输速率高于设备的处理速率时,设备驱动程序开设缓 冲区,缓存这些数据;

块模式设备:每次传输一个数据块。采用硬件方式控 制数据块的大小,有时需要采用固定的传输协议,如 USB、以太网等设备

34

建立通用的I/O接口函数

应用

I/O操作

Create() Open() Read() Write() Close() Loctl() Destroy()

设备驱动程序

Driver_Create() Driver_Open() Driver_Read() Driver_Write() Driver_Close() Driver_Loctl() Driver_Destroy()

存储器地址引脚

A0 A1 A2 …

对应 S3C44B0/ S3C2410 地址引脚连接

8bit 数据总线

16bit 数据总线 32bit 数据总线

A0

A1

A2

A1

A2

A3

A2

A3

A4

…

…

…

22

NAND和NOR——性能比较

NOR和NAND是现在市场上两种主要的非易失闪存技术

基于ARM的硬件系统设计

基于ARM的硬件系统设计引言:随着电子技术的飞速发展,计算机硬件系统设计逐渐成为现代科技领域的热门研究方向。

其中,基于ARM架构的硬件系统设计备受关注,因为ARM处理器具有低功耗、高性能和良好的可扩展性等特点,适用于各种应用场合。

本文将介绍基于ARM的硬件系统设计的一般流程和一些重要的设计考虑。

一、硬件系统设计流程:1.确定系统需求:首先,需要明确设计系统的需求,包括系统功能、性能、功耗和成本等方面的要求。

这些需求将在整个设计过程中起到指导作用。

2.选择合适的ARM处理器:根据系统需求,选择适合的ARM处理器,如Cortex-M系列、Cortex-A系列或Cortex-R系列等。

不同系列的处理器有不同的性能和功耗特点,需要根据实际情况做出合理的选择。

3.进行系统架构设计:根据系统需求和选定的ARM处理器,进行系统架构设计。

这包括模块划分、接口定义和性能估算等。

系统架构设计的目标是确保系统具有良好的可扩展性和可维护性。

4.选择外围设备:根据系统需求,选择适合的外围设备,如存储器、显示器、通信接口等。

这些外围设备的选择应与ARM处理器和系统架构相匹配,以实现系统功能的完整性。

5.进行电路设计:根据系统架构和选定的外围设备,进行电路设计。

这包括逻辑设计、时序设计和功耗优化等。

电路设计需要考虑系统性能、功耗和可靠性等因素。

6.进行PCB设计:根据电路设计,进行PCB布局和布线。

PCB设计应考虑信号完整性、电磁兼容性和热管理等因素。

合理的PCB设计可以提高系统性能和可靠性。

7.进行硬件调试和验证:制造出硬件原型后,进行硬件调试和验证。

这包括功能测试、性能测试和可靠性测试等。

通过调试和验证,可以确保硬件系统满足设计需求。

8.进行系统集成和软件开发:将硬件系统与软件系统进行集成,然后进行软件开发。

系统集成和软件开发是硬件系统设计中的最后一步,它们需要密切合作,以实现系统的功能和性能。

除了以上步骤,硬件系统设计还需要考虑一些重要的设计考虑。

基于ARM的硬件系统设计.

S3C2410X处理器详解

8通道的10位ADC,最高速率可达500kB/s, 10位分辨率; 触摸屏接口; IIS总线接口; 2个USB主机接口,1个USB设备接口; 2个SPI接口; SD卡接口和MMC卡接口; 16位看门狗定时器; 117位通用I/O口和24位外部中断源; 电源管理。

19

本节提要

1 基于ARM的硬件系统体系结构 2 存储器接口设计 3 4 5 6 I/O接口设计

人机交互接口设计

网络接口设计

其它通讯接口设计

20

嵌入式开发板与PC机的串行通讯

嵌入式开发板和PC机的通讯电缆可以按照如 图所示的方式连接。

RS-232 串行接口 2 3 PC 5 RS-232 串行接口 2 3 5 嵌入式 开发板

23

字符串行输出格式

发送前:线路处于空闲状态,连续发送 “1” 开始发送:首先,发送一位起始位 “0” 然后,发送连续的二进制位,数据位可以为5、6、7、8 随后,紧跟一位奇偶校验位(可选择奇/偶/无校验) 最后,发送停止位 “1”,可以有1位、1.5位或2位停止位

24

串行通讯硬件规范及连接方法

如果采用外部带时钟的UART,则UART可以实现更 高速度的传输; 每个UART包括2个16Byte的接收/发送FIFO。

22

UART控制框图

并行总线 数据接收器

发送FIFO(16 Byte)

发送移相器

TXDn

控制单元

波特率发生器

时钟源

接收移相器

RXDn

接收FIFO(16 Byte)

数据接收器

16

接口差别

NOR flash带有SRAM接口,线性寻址,可以 很容易地存取其内部的每一个字节 NAND flash使用复用接口和控制IO多次寻 址存取数据 NAND读和写操作采用512字节的块,这一点 有点像硬盘管理,此类操作易于取代硬盘 等类似的块设备

基于ARM的硬件系统设计(2)

+3.3V

LPC2214最小系统

JTAG接口 LPC2214 + 电源电路 + 晶振电路 + 复位电路 + JTAG接口 电路可构成真正意义上的最小系统 程序可运行于LPC2214内部的16KB SRAM中,也可以下载到 程序可运行于LPC2214内部的16KB SRAM中 LPC2214内部的 片内256KB Flash中 256KB的 片内256KB的Flash中。

(a)内部振荡方式

(b)外部输入方式

4

晶振电路设计

根据LPC2214的最高工作频率以及PLL电路的工作方式, 根据LPC2214的最高工作频率以及PLL电路的工作方式,选 LPC2214的最高工作频率以及PLL电路的工作方式 12MHz的无源晶振 12MHz的晶振频率经过LPC2214片内的 的无源晶振, 的晶振频率经过LPC2214片内的PLL 择12MHz的无源晶振,12MHz的晶振频率经过LPC2214片内的PLL 电路倍频后,最高可以达到60MHz 60MHz。 电路倍频后,最高可以达到60MHz。 片内的PLL电路兼有倍频和信号提纯的功能,因此, 片内的PLL电路兼有倍频和信号提纯的功能,因此,系统可 PLL电路兼有倍频和信号提纯的功能 以以较低的外部时钟信号获得较高的工作频率, 以以较低的外部时钟信号获得较高的工作频率,以降低因高速 开关时钟所造成的高频噪声。 开关时钟所造成的高频噪声。

13

4、软件编程涉及模块

系统控制模块: PLL获得更高的系统时钟cclk。 获得更高的系统时钟cclk 系统控制模块:设置 PLL获得更高的系统时钟cclk。 引脚连接模块:设置P0口的P0.17~P0.25为通用I/O口 引脚连接模块:设置P0口的P0.17~P0.25为通用I/O口。 P0口的P0.17~P0.25为通用I/O GPIO模块:设置P0口 为输入引脚, GPIO模块:设置P0口P0.17~P0.22为输入引脚, 模块 P0 为输入引脚 P0.23~P0.25也为输出引脚,并控制相应引脚的高低电平。 也为输出引脚,并控制相应引脚的高低电平。 也为输出引脚

基于ARM的嵌入式系统硬件设计

基于ARM的嵌入式系统硬件设计基于ARM的嵌入式系统硬件设计近年来,随着科技和信息技术的发展,嵌入式系统在各个领域中得到了广泛应用,包括智能家居、智能交通、医疗设备等。

而ARM架构作为嵌入式系统中最为常见和流行的处理器架构之一,其广泛应用程度不言而喻。

本文将详细介绍基于ARM 的嵌入式系统硬件设计的相关内容,包括硬件平台的选择、系统设计过程以及一些设计上的考虑等。

首先,嵌入式系统的硬件设计需要选择合适的硬件平台。

ARM架构提供了多种处理器选择,如Cortex-A、Cortex-R和Cortex-M系列等。

Cortex-A系列处理器适用于高性能应用,如智能手机和平板电脑。

Cortex-R系列处理器则专注于实时计算,适用于要求高实时性的应用,比如汽车电子系统。

Cortex-M系列处理器则专注于低功耗和低成本,适用于传感器、智能家居等领域。

接下来,基于ARM的嵌入式系统硬件设计需要考虑系统的整体架构。

首先,需要确定系统的功能需求和性能指标,以确定所需的外围设备和接口。

其次,需要进行电源供应设计,确保系统能够正常工作并具备稳定的电源供应。

此外,还需要进行时钟系统设计,确定系统需要使用的时钟频率和时钟源,保证系统各个模块的同步运行。

在硬件设计的过程中,需要考虑的一个重要因素是系统的可扩展性和可重用性。

通过模块化的设计思想,可以将系统划分为各个模块,每个模块负责不同的功能。

这样设计的好处是在后期系统升级和扩展时,只需要对相应的模块进行修改和升级,而不需要对整个系统进行改动。

此外,还可以通过接口的标准化设计,使得各个模块之间能够方便地进行连接和交互。

此外,硬件设计还需要考虑系统的可靠性和稳定性。

为了提高系统的可靠性,可以采用冗余设计和错误检测与纠正技术。

冗余设计指的是在系统中增加备用模块,一旦某个模块出现故障,备用模块可以自动接管。

错误检测与纠正技术可以通过添加冗余的错误检测电路或算法,及时发现和纠正硬件故障,保证系统的正常运行。

微机原理@10 基于ARM微处理器的硬件系统设计

•

•

ARM微处理器最小硬件系统的设计

最小硬件系统通常是指以 嵌入式处理器为核心,包含电 源、时钟和复位等保障处理器 正常工作的基本硬件电路 。

ARM微处理器; 电源模块,包括CPU内核和 I/O接口电源电源; 时钟模块,包括系统主时钟 和实时时钟; 复位模块,包括系统上电复 位、手动复位和内部复位; 存储器模块,包括程序保存 存储器(FLASH)和程序运 行存储器(SDRAM);

–在设计PCB时需要对模拟电源和数字电源进 行物理上的隔离

S3C2440A最小硬件系统:时钟模块

时钟模块为系统提供同步工作信号,其稳定性 直接关系到系统的工作稳定性。 在ARM嵌入式系统中通常包括频率较高的系统 主时钟和频率较低的实时时钟。

时钟经内部锁相环后得到四组时钟信号: FCLK:ARM920T内核 HCLK : AHB 总线、存储器控制器、中断控制器、 LCD控制器、DMA控制器和USB主机模块 PCLK :访问 APB 总线的外设,如 WDT , I2S , I2C , PWM 定时器, MMC 接口, ADC , UART , GPIO , RTC和SPI等模块 UCLK:USB模块需要的48 MHz时钟

GPIO

在S3C2440A中共有130个多功能I/O引脚 ,这些引脚除了可以作为某个特殊功能使用外, 均可以配置成GPIO模式,并分为以下9组:

• • • • • • • • • Port Port Port Port Port Port Port Port Port A(GPA):25个输出端口 B(GPB):11个输入/输出端口 C(GPC):16个输入/输出端口 D(GPD):16个输入/输出端口 E(GPE):16个输入/输出端口 F(GPF):8个输入/输出端口 G(GPG):16个输入/输出端口 H(GPH):9个输入/输出端口 J(GPJ):13个输入/输出端口

ARM嵌入式系统硬件设计及应用实例

ARM嵌入式系统硬件设计及应用实例ARM嵌入式系统是指使用ARM架构的处理器作为核心的嵌入式系统,它在嵌入式领域应用非常广泛,因为ARM处理器具有低功耗、高性能、低成本等优势。

ARM嵌入式系统的硬件设计主要包括处理器选择、电源管理、外设接口、外设选型等方面,下面将以一个智能家居控制系统为例,介绍ARM嵌入式系统硬件设计及应用实例。

一、处理器选择在设计ARM嵌入式系统时,首先需要选择合适的ARM处理器,常见的ARM处理器系列包括Cortex-M系列、Cortex-A系列和Cortex-R系列。

对于智能家居控制系统这种低功耗、实时性要求不高的应用场景,可以选择Cortex-M系列处理器,如STM32系列。

STM32系列处理器具有低功耗、高性能、丰富的外设接口等特点,非常适合嵌入式系统应用。

二、电源管理在设计ARM嵌入式系统时,电源管理是非常重要的一环。

智能家居控制系统通常需要接入多个传感器、执行器等设备,这些设备工作时会消耗大量电能。

因此,需要合理设计电源管理模块,包括电源管理芯片、电源转换器、稳压器等组件,以确保系统稳定可靠地工作。

三、外设接口智能家居控制系统通常需要接入多种外设设备,如传感器、执行器、显示屏、通信模块等。

因此,在ARM嵌入式系统的硬件设计中,需要设计适配这些外设设备的接口,如GPIO、SPI、I2C、UART等接口。

同时,还需要考虑外设设备与ARM处理器之间的数据传输速度、稳定性等因素。

四、外设选型在设计ARM嵌入式系统时,选择合适的外设设备也非常重要。

对于智能家居控制系统来说,传感器是必不可少的外设设备之一、传感器的选择应考虑其精度、灵敏度、稳定性等因素。

此外,还需要考虑执行器、显示屏、通信模块等外设设备的选型,以确保系统正常工作。

以上是一个智能家居控制系统的ARM嵌入式系统硬件设计及应用实例。

通过合理选择处理器、设计电源管理模块、设计外设接口、选择外设设备等步骤,可以设计出稳定可靠的ARM嵌入式系统,满足不同应用场景的需求。

ARM系统硬件设计

•

时钟电路

1、根据S3C2410X的最高工作频率以及PLL电路 的工作方式,选择12MHz的无源晶振。12MHz 的晶振频率经过S3C2410X片内的PLL电路倍频 后,可达到202.8MHz的频率。 2、片内的PLL电路兼有频率放大和信号提纯 的功能,因此,系统可以以较低的外部时钟信 号获得较高的工作频率,以降低因高速开关时 钟所造成的高频噪声。

• •

ARM系统硬件设计

最小系统框图

时钟电路 调试测试接口

可选,方便调试 和测试,一般都 加上。

嵌入式控制器 电源电路 复位电路

存储器电路

可选,当嵌入式处理 器中无存储器时,或 需扩充存储器时,需 加上。

ARM系统硬件设计

电源电路-概述

•

电源系统为整个系统提供能量,是整个系统 工作的基础,具有极其重要的地位。电源系 统处理的好坏,将直接影响到整个系统的稳 定性、可靠性等。多电源系统的设计、电源 的分配、印制板设计中电源的设计等,都是 必须考虑的。

ARM系统硬件设计

电源

ARM系统硬件设计

•

4.2 最小系统的设计

1、一个嵌入式处理器是不能独立工作的,必须给它供 电、加上时钟信号、提供复位信号,如果芯片没有片 内程序存储器,则还要加上存储器系统,然后嵌入式 处理器才可能工作。 2、这些提供嵌入式处理器运行所必须的条件的电路与 嵌入式处理器共同构成了这个嵌入式处理器的最小系 统。 3、大多数基于ARM9处理器核的微控制器都有调试接 口,这部分在芯片实际工作时不是必需的,但因为这 部分在开发时很重要,所以把这部分也归入到最小系 统中。

ARM系统硬件设计

FLASH接口电路设计- TE28F128J3A引脚分布

ARM系统硬件设计

基于ARM的嵌入式系统硬件结构设计

”

I/O接口

接口的概念

CPU与外部设备的接口(I/O适配器)

接口的功能

控制

缓冲

状态

转换

整理

程序中断

通用设计原则(I/O设备)

I/O接口 3种寄存器 数据寄存器、控制寄存器和状态寄存器

数据寄存器

状态寄存器

控制寄存器

I/O接口芯片

去I/O设备

去CPU

通用设计原则(I/O设备)

1

I/O子系统的目标是对RTOS和应用程序员隐藏设备特定的信息,并且对系统的外围I/O设备提供一个统一的访问方法。

2

从不同角度看I/O系统

从系统软件开发者角度看,I/O操作意味着与设备的通信、对设备编程初始化和请示执行设备与系统之间的实际数据传输以及操作完成后通知请求者。系统软件工程师必须理解设备的物理特性,如寄存器的定义和设备的访问方法。

I/O设备寻址 I/O寻址 定位I/O设备内部的寄存器(或一小块存储器) 与存储器共享总线 存储器映像法 混合编址

CPU

存储器

地址总线

数据总线

读信号

写总线

译码

I/O接口

译码

通用设计原则(I/O设备)

I/O设备寻址 I/O隔离法 独立编址 信号线MERQ/IORQ 地址空间

CPU

存储器

地址总线

数据总线

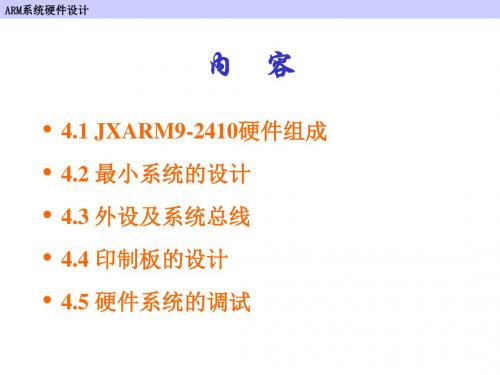

嵌入式系统设计与实例开发

——基于32位微处理器与实时操作系统

第七讲 基于ARM的硬件系统结构设计

本节提要

CONTENTS

基于ARM的硬件系统体系结构

存储器接口设计

I/O接口设计

01

人机交互接口设计

网络接口设计

第十章 基于ARM内核微处理器硬件设计

nOE

nWAIT

读允许 O

等待请求 I

nBE[3:0]

数据高/低字节允许 O

nWBE[3:0] 写字节允许 O

nXBREQ

nXBACK

总线保持请求 I

SCLK[1:0]

SDRAM时钟 O

SDRAM时钟允许 O

总线保持应答 O SCKE

nBE[3:0]=nWBE[3:0] & nOE

0x3FFF_FFFF 0x3800_0000

0x50000000 ~ 0x50000028

0x50004000 ~ 0x50004028 0x50008000 ~ 0x50008028 0x51000000 ~ 0x51000040 0x52000140 ~ 0x5200026c 0x53000000 ~ 0x53000008

IIC

IIS AC97

10.1 S3C2440微处理器简介

外部存储器控制单元(控制SDRAM和片选) LCD专用控制器和专用DMA通道 外部4路独立DMA控制器 3路串口,读写64k缓存 2路spi口 I2C总线接口 I2S音频总线接口 AC'97解码总线接口 SD host interface version 1.0 and MMc 2.11 2路USB host 控制器 和 单路设备USB控制器 1.1 4路定时器,1路内部计数器和看门狗 8通道10bitADC和触摸屏接口 RTC时间日志功能 摄像头接口(Max 4096x4096 and 2048x2048 support for scaling) 130路独立通用GPIO/ 24通道中断资源

G端口GPGDAT寄存器存放IO的数据

D7

D6

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2018-10-26

意法半导体公司的STR91x

•

•

•

•

• •

采用96 MHz ARM966E-S内核, 带有单周期的DSP指令和与介质 无关的联网功能; 大容量存储器可满足复杂的应用、 实时操作系统(RTOS)、通信协 议栈和数据存储的需求;双体闪 存是实现在线编程(IAP)和 E2PROM仿真的理想结构。 具有优化DMA数据流的10/100 M以太网接口; 支持USB,CAN,SPI,I2C, UART/IrDA和多个计时器,最多 80个5 V兼容的GPIO; 带有10位ADC并具有全方位的 CPU监控功能; 灵活的功耗和时钟管理功能,具 有多种低功耗模式和带闹钟功能 的低功耗实时时钟。

AHB总线采用了6×3多 层交叉开关(MAX), 支持多个并行事项,改善 总线的有效吞吐量。 其外部存储器接口可以支 持16/32位SDRAM或DDR 存储器、8/16位NAND flash存储器和PSRAM。

2018-10-26

6/74

Atmel公司的ARM微处理器芯片

• 美国Atmel公司继成功推出AT89系列(兼容MCS-51)和AT90系列(RISC)单 片机后,采用业界流行的ARM内核推出了更强的32位AT91系列微控制器。 该系列主要包含以下子系列: –AT91M42800A,AT91M55800A –AT91RM9200,AT91SAM7A –AT91SAM7L(低功耗),AT91SAM7S –AT91SAM7SE,AT91SAM7X –AT91SAM9,AT91SAM9XE和AT91X40 • AT91系列微控制器使用高密度CMOS技术,集成了ARM内核和大量的Flash 存储器、片内RAM和各种外围功能模块,为许多需要加强运算的嵌入式应 用提供了高度灵活且性价比高的解决方案。

• 除i.MX系列微处理器以外,飞思卡尔公司还有少数其他产品 也采用了ARM内核,例如适用于便携式多媒体播放器和导航 设备的STMP37XX系列产品。

2018-10-26 5/74

飞思卡尔公司的i.MX27

采用ARM926EJ-S内核, 一级指令缓存和数据缓存 各有16KB

集成了16通道DMA和 ETM实时调试接口

2018-10-26

11/74

恩智浦半导体的LPC2000

ARM7TDMI-S内核

– 三级流水线 – 冯·诺依曼架构 – T: Thumb指令集 – D: Debug扩展 – M: 增强的乘法指令(32B x 8B -> 64B) – I: 内核带有EmbeddedICE逻辑功能扩展 – S: 软核

2018-10-26

4/74

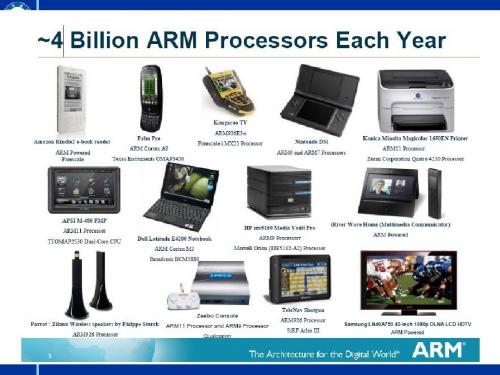

飞思卡尔公司的ARM微处理器芯片

• 美国飞思卡尔公司采用ARM内核的微处理器命名为i.MX系列, 该系列主要包含以下子系列:

• i.MXS,i.MXL,i.MX1,i.MX21,i.MX27,i.MX31,i.MX35, i.MX37、i.MX51等

• 该系列微处理器主要应用于智能手机、便携式多媒体播放器、 便携式导航设备、视频监控、销售终端机系统和条码扫描仪 等消费类、工业、健康等领域的产品。

2018-10-26

8/74

意法半导体公司的ARM微处理器芯片

•

•

•

•

意法半导体有限公司(STMicroelectronics)是全球最大的半导体公司之一。 其采用ARM内核的微处理器主要包括三个系列:采用Cortex-M3内核的 STM32系列、采用ARM7TDMI内核的STR7系列和采用ARM966E-S内核 的STR9系列。 STM32系列产品得益于Cortex-M3在架构上进行的多项改进,包括性能 和代码密度同时得以提升的Thumb-2指令集,大幅度提高的中断响应, 而且所有新功能都同时具有业界最优的功耗水平。 STR7系列产品融合了16位和32位产品的优势,适合嵌入式控制应用, 如工业控制、工厂自动化、销售终端设备、医疗和测试设备以及电信和 消费电子应用等。 STR9系列结合了ARM9E处理器内核和通用闪存,并加入了联网功能, 使实现各种要求苛刻的应用变得更加简单和廉价。

10/74

2018-10-26

恩智浦半导体的ARM微处理器芯片

恩智浦半导体由飞利浦在 50 多年前创立。恩智浦提供半导体、系统 解决方案和软件,为电视、机顶盒、智能识别应用、手机、汽车以及 其他形形色色的电子设备提供更好的感知体验。

恩智浦半导体基于ARM7的LPC2000 为32 位微控制器设定了新的性 价比,包括LPC213x,LPC214x、LPC2101/2/3等系列, 采用了0.160.18 μm工艺 更高性能产品系列(LPC2300,LPC2400,LPC2800)采用了0.14um工艺

2018-10-26 3/74

三星公司的S3C2440A

• 采用ARM920T内核,实 现了MMU,AMBA总线 和哈佛架构的高速缓冲体 系结构。 • 在高速缓存方面采用了独 立的16 KB的I-cache和16 KB的D-cache。 • 采用0.13 m CMOS工艺 标准宏单元和存储器单元, 其低功耗、简洁的结构和 全静态电路设计特别适合 对成本和功耗敏感的应用。 • 为了降低整机系统的成本, 提供了各类丰富的功能模 块,在系统设计中无需配 置额外的外部组件。

13/74

•

•

2018-10-26

ARM微处理器最小硬件系统的设计

最小硬件系统通常是指以 嵌入式处理器为核心,包含电 源、时钟和复位等保障处理器 正常工作的基本硬件电路 。

ARM微处理器; 电源模块,包括CPU内核和 I/O接口电源电源; 时钟模块,包括系统主时钟 和实时时钟; 复位模块,包括系统上电复 位、手动复位和内部复位; 存储器模块,包括程序保存 存储器(FLASH)和程序运 行存储器(SDRAM);

高速嵌入式Flash 丰富的外设资源

– UART, SPI, I2C, CAN, USB, ethernet等

工业级芯片

– 工作温度范围: –40°C~+85°C / +105°C

丰富开发工具支持

– 高性能, 低价格

2018-10-26 12/74

ARM芯片的选型

• 性能参数的考虑 – ARM核版本 – 工作频率 – 内部存储器容量 – 电源控制 – DSP协处理器 – 功耗 外设接口的考虑 – USB接口 – RTC – GPIO数量 – 其他因素 芯片封装的选择 – 芯片的封装有很多种类型,如:DIP、QFP、PGA、BGA等 – 在散热性能、信号完整性特性、体积大小等方面的要求

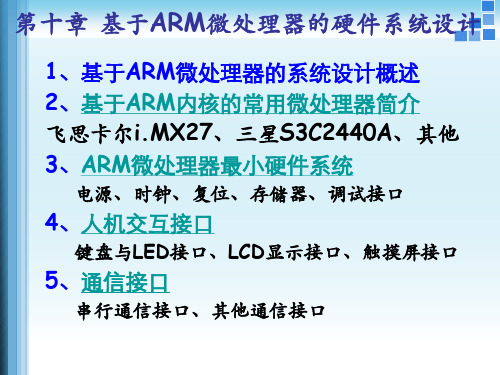

第十章 基于ARM微处理器的硬件系统设计

1、基于ARM微处理器的系统设计概述 2、基于ARM内核的常用微处理器简介 飞思卡尔i.MX27、三星S3C2440A、其他 3、ARM微处理器最小硬件系统

电源、时钟、复位、存储器、调试接口

4、人机交互接口

键盘与LED接口、LCD显示接口、触摸屏接口

5、通信接口

2018-10-26 20/74

S3C2440A最小硬件系统:存储器模块

存储器模块为系统程序的保存和运行提供空间, 在系统设计中主要根据处理器的存储器接口选择 合适的存储器芯片(存储类型、容量、速度和接 口类型 )

ARM 最小系统中的存储器通常包括存放程序的 NAND Flash和用于程序运行的SDRAM。 存储器模块通常挂接在 ARM 芯片的局部总线上 (外部三总线)。

–电源纹波和电路干扰的处理

–在设计PCB时需要对模拟电源和数字电源进 行物理上的隔离

2018-10-26 15/74

2018-10-26

16/74

S3C2440A最小硬件系统:时钟模块

时钟模块为系统提供同步工作信号,其稳定性直接关 系到系统的工作稳定性。 在 ARM 嵌入式系统中通常包括频率较高的系统主时钟 和频率较低的实时时钟。

2018-10-26

19/74

S3C2440A最小硬件系统:JTAG调试接口

ARM微处理器一般都采用 JTAG作为调试接口,通过 并口连接到调试主机(如果 没有并口,可以通过JLink 实现USB接口转JTAG

TCK :测试时钟输入; TDI :测试数据输入,数据通过TDI输入JTAG口; TDO:测试数据输出,数据通过TDO从JTAG口输出; TMS:测试模式选择,TMS用来设置JTAG口处于某种特定的测 试模式。 nTRST(可选引脚):测试复位,输入引脚,低电平有效。

2018-10-26 17/74

2018-10-26

18/74

S3C2440A最小硬件系统:复位模块

一般来说系统对外部复位信号波形有一定的要求,若不能满 足要求(例如持续时间过短),则系统将不能正常工作。

复位类型:系统上电复位、手动复位和内部复位 1. 系统上电复位、手动复位 : 外部电路复位 2. 内部复位:系统内部事务处理(看门狗复位) (看门狗本质实际上是一个计数器,当计数到初始设置值, 就向CPU的nReset引脚输出低电平;因此当程序运行时 需要定时喂狗(看门狗检测到喂狗信号时计数值清0)) ( 复位异常处理情况详见:P235最前面第二段, P314最后 两段)

– 意法半导体:STR91x …

– 恩智浦半导体:LPC2000 系列…

2018-10-26

2/74

三星公司的ARM微处理器芯片

• 三星公司推出的基于ARM内核的微处理器主要面向消费类便携式设备, 为手持设备和一般应用提供了高性价比和高性能的微控制器解决方案。 包括: –采用ARM7TDMI内核的S3C44B0和S3C3410 –采用ARM926EJ-S内核的S3C2412,S3C2413,S3C2416,S3C2450 和S3C24A0 –采用ARM920T内核的S3C2410,S3C2440,S3C2442和S3C2443 –采用ARM1176JZF内核的S3C6400等 • 三星公司采用ARM内核的微处理器主要按照应用来划分,如通用型32 位MCU主要采用ARM7TDMI内核,面向CAN/LIN总线、以太网、发动 机控制和RFID等应用场合。