2位10进制加法计数器课程设计

数显两位十进制计数器电路设计报告

东北大学秦皇岛分校计算机与通信工程学院电子线路课程设计压力测量数显电路专业名称班级学号学生姓名指导教师设计时间课程设计任务书专业学号学生姓名(签名):设计题目:压力测量数显电路一、设计实验条件Multisim实验室二、设计任务及要求1.熟悉译码器、555定时器、计数器和七位数码管的功能,并熟练应用;2.掌握555定时器产生脉冲的原理和方法;3.选择合适的器件来构成脉冲信号发生器;4.学会利用计数器构成不同进制的计数器;5.设计压力测量数显电路。

三、设计报告的内容1.设计题目与设计任务(设计任务书)2.前言(绪论)(设计的目的、意义等)3.设计主体(各部分设计内容、分析、结论等)4.结束语(设计的收获、体会等)5.参考资料四、设计时间与安排1、设计时间:2周2、设计时间安排:熟悉实验设备、收集资料:2 天设计图纸、实验、计算、程序编写调试: 5天编写课程设计报告:2 天答辩:1 天1、绪论随着计算机科学与技术迅猛地发展,用数字电路进行信号处理的优势也更加的突出。

数字电路具有精度高、稳定性好、抗干扰能力强、程序软件控制等一系列优点。

为了充分发挥数字电路在信号处理上的强大功能,我们可以先将拟信号按比例转换成数字信号,然后送到数字电路进行处理,最后将处理结果根据需要转换成相应的模拟信号输出。

自20世纪七十年代开始,这种用数字电路处理模拟信号的所谓“数字化”浪潮已经席卷了电子技术几乎左右的领域。

现在,学校给我提供了这次机会,我将利用所学的数电知识,仿真一个压力测试数电电路,以求更好掌握数电知识。

此次课程设计的目的是学会利用555定时器产生脉冲信号,熟练应用计数器、译码器和数码器构成压力测试数显电路。

通过此次的课程设计掌握数字信号的基本元件和知识,以实践的方式加深知识的掌握程度,扩展我们的思维。

2、系统设计(一)设计结构1、由555脉冲信号发生器产生脉冲信号;2、100进制计数器有两个74LS160计数器串联构成;3、显示器是由两个译码器和两个数码管构成。

2位十进制四则运算器电路

《电子设计自动化》课程设计题目: 2位十进制四则运算器电路摘要本次设计的目的是通过QuartusII软件实现输入两个2位十进制数(0~99),输出它们的四则运算(加减乘除)结果(发光二极管显示运算模式;调用LPM_MULT、LPM_CONSTANT及LPM_DIVIDE模块)。

实现的方法是利用四则运算的规律进行初步设计,然后进行调整和修改。

最终结果要求:随机的输入两个数,经过加法、减法、乘法和除法的运算,可以得到正确的运算结果。

主要分为4大部分:一、2位十进制数模块;二、加减乘除四则运算四个小模块;三、加减乘除四则运算的选择模块;四、处理输出结果的模块。

目录1 系统设计 (4)2 单元电路设计 (5)3 软件设计 (5)4 系统测试 (14)5 结论 (14)6 参考文献 (14)1、系统设计一、设计要求:输入两个2位十进制数(0~99),输出它们的四则运算(加减乘除)结果;发光二极管显示运算模式;可调用LPM_MULT及LPM_DIVIDE模块。

二、系统设计方案:(1)系统设计思路要完成2位十进制四则运算器电路,首先,需要生成2个两位的十进制数,其次,需要加减乘除四个运算,然后,四种运算的选择,最后,对输出结果的处理。

2个2位十进制模块:法一,用两个100进制计数器构成;法二,用4个10进制计数器构成。

因为add1模块(后面详细介绍)只有两个输入口,所以选择法一比较方便。

加减乘除四则运算:①加法:写一个加法程序,制成模块,再分别取出它的各位、十位、百位。

②减法:写一个减法程序,用调用LPM的方法制成一个模块,在分别取出它的各位、十位和符号位。

③乘法:直接调用内部LPM,制成乘法模块。

④除法:直接调用内部LPM,制成除法模块。

加减乘除运算的选择:写一个4路选择器,分别选择加减乘除。

对输出结果的处理:写一个程序,对应不同选择下的不同输出,注意位数(加法:输出在0~198之间,需3个LED灯来显示;减法:输出在0~99之间,需3个LED灯(其中一个符号位);乘法:输出在0~9801之间,需4个LED灯;除法:输出在0~99之间,需2个LED灯。

10进制计数器课程设计

10进制计数器课程设计一、课程目标知识目标:1. 学生能理解10进制计数器的基本概念,掌握10进制数的组成和计数规律。

2. 学生能运用10进制计数器进行数值的加减运算,并正确表达计算过程和结果。

3. 学生了解10进制计数器在日常生活和科学技术中的应用。

技能目标:1. 学生能够独立操作10进制计数器,进行简单的数值计算。

2. 学生通过实际操作,培养观察、分析、解决问题的能力。

3. 学生通过小组合作,提高沟通、协作和团队意识。

情感态度价值观目标:1. 学生对10进制计数器产生兴趣,激发学习数学的积极性。

2. 学生在探索过程中,培养耐心、细致、勇于尝试的精神。

3. 学生认识到数学知识在实际生活中的重要性,增强学以致用的意识。

课程性质:本课程属于数学学科,旨在帮助学生掌握10进制计数器的运用,提高数学运算能力和实际应用能力。

学生特点:四年级学生具有一定的数学基础,好奇心强,喜欢动手操作,但注意力集中时间较短。

教学要求:注重理论与实践相结合,以学生为主体,激发学生兴趣,培养动手操作能力和团队协作精神。

通过分解课程目标为具体的学习成果,使学生在愉快的氛围中掌握知识,提高能力。

二、教学内容1. 引入10进制计数器概念,介绍其在数学运算中的应用。

- 教材章节:第三章《数的认识》- 内容:10进制计数器的定义、计数规律、数位顺序表。

2. 学习10进制计数器的操作方法,进行数值的加减运算。

- 教材章节:第四章《简单的数学计算》- 内容:10进制计数器操作方法、数值加减运算、进位与退位。

3. 实践与应用,运用10进制计数器解决实际问题。

- 教材章节:第五章《生活中的数学》- 内容:运用10进制计数器进行购物找零、时间计算等实际问题的解决。

4. 小组合作,探讨10进制计数器在科学技术领域的应用。

- 教材章节:第六章《数学与科技》- 内容:10进制计数器在计算机、电子设备等领域的应用案例。

教学进度安排:第一课时:引入10进制计数器概念,学习计数规律和数位顺序表。

课程设计-十进制加法计算器设计

课程设计(论文)任务书电气学院电力系统专业12(1 )班一、课程设计(论文)题目:十进制加法计算器设计二、课程设计(论文)工作自2015年1 月12 日起至2015 年1月16 日止。

三、课程设计(论文) 地点: 电气学院机房10-303四、课程设计(论文)容要求:1.课程设计的目的(1)综合运用单片机原理及应用相关课程的理论知识和实际应用知识,进行单片机应用系统电路及程序设计,从而使这些知识得到进一步的巩固,加深和发展;(2)熟悉和掌握单片机控制系统的设计方法,汇编语言程序设计及proteus 软件的使用;(3)通过查阅图书资料、以及书写课程设计报告可提高综合应用设计能力,培养独立分析问题和解决问题的能力。

2.课程设计的容及任务课程设计容:利用单片机及一些外围电路设计一个简易的十进制加法计算器,硬件电路设计大概主要包括:键盘电路,显示电路以及复位电路和晶振电路。

软件方面的设计主要包括:LED显示程序设计、数值送显示缓存程序设计、读键子程序设计、运算程序的设计。

课程设计任务:设计一个键盘显示装置,键盘上除了定义0~9共10个数字键外,还要相应的功能健,其它键不定义无响应。

利用此系统可分别输入十进制被加数和加数,实现两个数相加并将结果以十进制形式显示出来。

3.课程设计说明书编写要求(1)设计说明书用A4纸统一规格,论述清晰,字迹端正,应用资料应说明出处。

(2)说明书容应包括(装订次序):题目、目录、正文、设计总结、参考文献等。

应阐述整个设计容,要重点突出,图文并茂,文字通畅。

(3)报告容应包括方案分析;方案对比;整体设计论述;硬件设计(电路接线,元器件说明,硬件资源分配);软件设计(软件流程,编程思想,程序注释,)调试结果;收获与体会;附录(设计代码放在附录部分,必须加上合理的注释)(4)学生签名:2015年1月16 日课程设计(论文)评审意见(1)总体方案的选择是否正确;正确()、较正确()、基本正确()(2)程序仿真能满足基本要求;满足()、较满足()、基本满足()(3)设计功能是否完善;完善()、较完善()、基本完善()(4)元器件选择是否合理;合理()、较合理()、基本合理()(5)动手实践能力;强()、较强()、一般()(6)学习态度;好()、良好()、一般()(7)基础知识掌握程度;好()、良好()、一般()(8)回答问题是否正确;正确()、较正确()、基本正确()、不正确()(9)程序代码是否具有创新性;全部()、部分()、无()(10)书写整洁、条理清楚、格式规;规()、较规()、一般()总评成绩优()、良()、中()、及格()、不及格()评阅人:年月日摘要随着社会科技的发展和进步,计算器因其功能强大而早已成为人们日常生活中必不可少的工具,最简单的计算器就能实现简单的加减乘除运算,这让人们免去了复杂的计算过程,大大提高了工作效率。

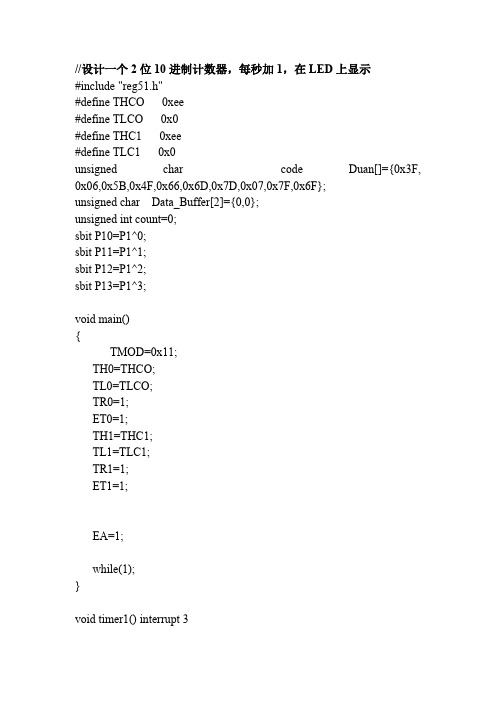

2位10进制计数器

//设计一个2位10进制计数器,每秒加1,在LED上显示#include "reg51.h"#define THCO 0xee#define TLCO 0x0#define THC1 0xee#define TLC1 0x0unsigned char code Duan[]={0x3F, 0x06,0x5B,0x4F,0x66,0x6D,0x7D,0x07,0x7F,0x6F};unsigned char Data_Buffer[2]={0,0};unsigned int count=0;sbit P10=P1^0;sbit P11=P1^1;sbit P12=P1^2;sbit P13=P1^3;void main(){TMOD=0x11;TH0=THCO;TL0=TLCO;TR0=1;ET0=1;TH1=THC1;TL1=TLC1;TR1=1;ET1=1;EA=1;while(1);}void timer1() interrupt 3{static unsigned char Bit1;TH1=THC1;TL1=TLC1;count++;if(count>200){count=0;Bit1++;if(Bit1>99)Bit1 = 0;Data_Buffer[0]=Bit1/10;Data_Buffer[1]=Bit1%10; }}void timer0() interrupt 1{static unsigned char Bit=0;TH0=THCO;TL0=TLCO;Bit++;if(Bit>=2)Bit=0;P1|=0x0f;P0=Duan[Data_Buffer[Bit]]; switch(Bit){case 0: P10=0;break;case 1: P11=0;break;}}实验5思考题#include "reg51.h"#define THCO 0xee#define TLCO 0x00#define THC1 0xee#define TLC1 0x00unsigned char code Duan[]={0x3F, 0x06,0x5B,0x4F,0x66,0x6D,0x7D,0x07,0x7F,0x6F};unsigned char Data_number[4]={1,2,3,4};unsigned char Data_time[2]={0,0};sbit P10=P1^0;sbit P11=P1^1;sbit P12=P1^2;sbit P13=P1^3;sbit key=P3^2;int mode=0,Bit1=0,Bit=0;void main(){TMOD=0x11;TH0=THCO;TL0=TLCO;TR0=1;ET0=1;EX0=1;IT0=1;TH1=THC1;TL1=TLC1;TR1=0;ET1=1;EA=1;while(1);}void tans_mode() interrupt 0{int t;if(key==0){for(t=0;t<1000;t++);if(key==0){while(!key);mode++;if(mode==3)mode=0;Bit=0;if(mode==2){TR1=1;Bit1=0;}else{TR1=0;}}}}void timer1() interrupt 3{static unsigned int count=0;TH1=THC1;TL1=TLC1;count++;if(count>200){count=0;Bit1++;if(Bit1>99)Bit1=0;Data_time[0]=Bit1/10;Data_time[1]=Bit1%10; }}void timer0() interrupt 1{TH0=THCO;TL0=TLCO;P1=0x0f;if(mode==0){P0=Duan[0];}if(mode==1){Bit++;if(Bit>=4)Bit=0;P0=Duan[Data_number[Bit]]; }if(mode==2){Bit++;if(Bit>=2)Bit=0;P0=Duan[Data_time[Bit]];}switch(Bit){case 0: P10=0;break; case 1: P11=0;break; case 2: P12=0;break; case 3: P13=0;break; }}。

十进制加减法数字电路课程设计报告

设计名称:设计一个一位十进制加减法器 设计内容:1、0-9十个字符和“+”“-”分别对应一个按键,用于数据输入。

2、用一个开关控制加减法器的开关状态。

3、要求在数码显示管上显示结果。

设计目的与要求:1、学习数字逻辑等电路设计方法,熟知加减法器、编码器、译码显示的工作原理及特点;2、培养勤奋认真、分析故障和解决问题的能力。

设计环境或器材、原理与说明:环境:利用多功能虚拟软件Multism8进行电路的制作、调试,并生成文件。

器材:74LS283或者4008, 4个异或门(一片74LS86)(减法);74LS08,3输入或门(加法)设计原理:图1分析:如图1所示,第一步置入两个四位二进制数(要求置入的数小于1010),如(1001)2和(0111)2,同时在两个七段译码显示器上显示出对应的十进制数9和7;第二步通过开关选择运算方式加或者减;第三步,若选择加运算方式,所置数送入加法运算电路进行运算,同理若选择减运算方式,则所置数送入减法运算电路运算;第四步,前面所得结果通过另外两个七段译码器显示。

设计过程(步骤)或程序代码: 实验电路:1:减法电路的实现:(1):原理:如图1所示(如下),该电路功能为计算A-B 。

若n 位二进制原码为N 原,则与它相对应的补码为N 补=2n -N 原,补码与反码的关系式为N 补=N 反+1,A-B=A+B补-2n=A+B反+1-2n(2):因为B○+1= B非,B○+0=B,所以通过异或门74LS86对输入的数B求其反码,并将进位输入端接逻辑1以实现加1,由此求得B的补码。

加法器相加的结果为:A+B反+1,(3):由于2n=24=(10000)2,相加结果与相2n减只能由加法器进位输出信号完成。

当进位输出信号为1时,它与2n的差为0;当进位输出信号为0时,它与2n差值为1,同时还要发出借位信号。

因为设计要求被减数大于或等于减数,所以所得的差值就是A-B差的原码,借位信号为0。

微机实验:两个多位十进制数相加的实验

实验一、两个多位十进制数相加的实验1、实验目的(1).学习数据传送和算术运算指令的用法。

(2).熟悉在PC机上建立、汇编、链接、调试和运行8088汇编语言程序的过程。

2、实验内容将两个多位十进制数相加。

要求被加数均以ASCII码形式各自顺序存放在以DATAl和DATA2为首的5个内存单元中(低位在前),结果送回DATAl处。

3、程序框图4、参考程序:DATAS SEGMENTDAT1 DB 5 DUP (0)DAT2 DB 5 DUP (0)DAT3 DB 6 DUP(0)JH DB'+','$'HX DB'_______','$';此处输入数据段代码DATAS ENDSSTACKS SEGMENT;此处输入堆栈段代码STACKS ENDSCODES SEGMENTASSUME CS:CODES,DS:DATAS,SS:STACKS START:MOV AX,DATASMOV DS,AXMOV DL,20H; 输入空格用以竖式对齐MOV AH,02HINT 21HLEA BX,DAT1MOV CX,5INADD1: MOV AH,01HINT 21HMOV [BX],ALINC BXLOOP INADD1MOV DL,0AH; 换行MOV AH,02HINT 21HMOV DL,0DHMOV AH,02HINT 21HLEA DX,JH; 输出加号MOV AH,09HINT 21HLEA SI,DAT2MOV CX,5INADD2: MOV AH,01HINT 21HMOV [SI],ALINC SILOOP INADD2MOV DL,0AH;换行MOV AH,02HINT 21HMOV DL,0DHMOV AH,02HINT 21HLEA DX,HX; 输出横线MOV AH,09HINT 21HMOV DL,0AH;换行MOV AH,02HINT 21HMOV DL,0DHMOV AH,02HINT 21H;以下计算结果LEA BX,DAT1+4LEA SI,DAT2+4LEA DI,DAT3+5MOV CX,5CLC ;清除CF标志位L1: MOV AL,[BX]ADC AL,[SI]AAAPUSHFOR AL,30H; 将AL转换为ASCII码POPFMOV [DI],ALDEC DIDEC BXDEC SILOOP L1MOV CL,6;6位循环6次JNC OUT1;没有进位直接输出MOV byte ptr [DI],31H;有进位给最高位赋1 ;以下输出显示OUT1:MOV DL,[DI]INC DIMOV AH,02HINT 21HLOOP OUT1MOV AH,4CHINT 21HCODES ENDSEND START。

(小学四年级数学教案)数学教案-十进制计数法-教学教案

数学教案-十进制计数法-教学教案教学目标1.使同学知道数的产生.2.生疏亿级的数,把握计数单位“亿〞、“十亿〞、“百亿〞、“千亿〞及“千亿〞内的数位挨次表和十进制计数法,会依据数级正确地读千亿以内的数.教学重点把握数位挨次表及多位数的读法和应用.教学难点读法应用及数中零的读法.教学步骤一、铺垫孕伏.谈话导入:同学们,我们已经学习了三年多数学,每天都要和数打交道,那么你们知道数是怎样产生的吗〔老师板书:数的产生〕二、探究新知.〔一〕教学数的产生.1.同学自学课本内容.同学答复:人们在劳动生产中有了计数的需要,比方数人数、物体个数等,这样就产生了数.老师明确:远古时代人们虽然有计数的需要,但开头不会用一、二、三、四.……这些数词数物体的个数,只是知道“同样多〞.“多〞、“少〞,因此那时人们只能借助一些其他物品来计数.2.同学观看教材插图内容.〔1〕放牧时摆小石子,每放出一只羊,就摆一个小石子,放出多少只羊就摆多少个小石子.放牧回来,再把这些小石子和羊—一对应起来,假设二者同样多,说明放牧时羊没有丢.〔2〕人手中的木棒,木棒上有好多道,这就是记录.人们出去打猎时,拿走的武器,每拿一件武器就在上面刻一道,等到人们打猎回来时,再看二者是否同样多,以此来推断武器的丢失.〔3〕结绳计数的道理也是这样.过去人们无论实行的哪种计数方式,都是要把数的实物和用来计数的实物一个一个地对应起来.〔4〕随着语言的开展,便渐渐消灭了数词,随着文字的开展人们制造了记数的符号,也就是最初的数字.不同的国家和地区符号也不同.老师提问:你知道哪些国家的数字各是怎样的〔巴比伦数字、中国数字、罗马数字、阿拉伯数字〕〔5〕人类对数的生疏渐渐增加,数认得越来越大,这样就产生了进位制,因进位制有很多种,十进制计数比拟便利,所以后来渐渐统一接受十进制.有了数的概念、数字和计数方法,又渐渐开展成较完整的计数方法,这就是我们今日要讲的“十进制计数法〞.〔板书课题:十进制计数法〕〔二〕教学十进制计数法.1.说出亿以内的数的计数单位.亿以内的数字有哪些计数单位2.提问:10个一是多少10个十是多少……10个一千万是多少3.亿以内每相邻两个单位的关系怎样4.举例说明,日常生活中比亿大的数.我国人口十二亿就比亿大.从一亿开头,还可以连续数下去,请同学们拿出算盘.让同学在算盘上先拨上一亿,然后一亿一亿地数,数到九亿,再拨上一亿老师提问:A、九亿再加一亿是多少亿位满十要怎样十亿应写在什么位置百亿、千亿呢〔老师同步板书〕B、十亿、百亿、千亿也叫计数单位.我们共学了哪些计数单位C、从刚刚一边拨珠,一边数数的过程中,谁发觉了每相邻两个计数单位之间有什么关系老师明确:A、比千亿大的计数单位,因不常用,临时不学,所以在千亿的左面用……表示〔板书:……〕B、“每相邻的两个计数单位之间的进率都是十〞的计数方法,叫做“十进制计数法〞.〔三〕生疏数位和数位挨次表.1.我们知道了什么叫十进制计数法,要把一个数写出来,就要用到数字,老师提问:我们学过哪些数字〔1、2.3、4、5、6、7、8、9.0〕老师说明:这些数字叫阿拉伯数字.老师强调:写数的时候,把计数单位按肯定的挨次排列起来,它们所占的位置叫做数位.一个数字所在的数位不同,表示的大小也不同.2.观看数位挨次表.老师提问:亿以内的数位挨次是怎样的〔强化右起第五位是万位,第九位是亿位.〕千万位百万位十万位万位千位百位十位个位3.数位分级〔同学自学〕自学题目:从右边起几个数位为一级,各是什么数级个级、万级、亿级有什么异同点〔四〕教学亿级的读法.1.下面的数该怎样读呢〔回忆读亿以内数的方法.〕老师板书:50000106000400305002.在上面三个数后各加4个0,变成例1.〔1〕同学试读、相互读、小组争辩读.〔2〕引导同学总结多位数的读法法那么.同学争辩:含有亿级、万级和个级的数,按什么挨次来读怎样读亿级、万级的数什么位置的“0〞不读什么位置的读,读几个同学总结法那么:〔1〕从高位起,一级一级地往下读;〔2〕读亿级或万级的数时,要依据个级的数的读法来读,再在后面加上“亿〞字或“万〞字;〔3〕每级末尾的0都不读,其他数位有一个0或连续有几个0都只读一个“零〞.三、稳固练习.1.填空.〔1〕从右起第9位是〔〕位.〔2〕十个一亿是〔〕亿.〔3〕10个一百亿是〔〕亿.〔4〕、、、是亿级,万级有、、、.2.推断.〔1〕两个计数单位间的进率是10.〔〕〔2〕308040000000读作三千八十亿四千万.〔〕3.读出下面每组数.〔1〕65 650000 65 0000 0000〔2〕4070 4070 0000 4070 0000 0000四、课堂小结.引导同学总结十进制计数法,正确读多位数的法那么.五、布置作业.读出下面横线上的数.1.到2000年第五次全国人口普查为止,我国总人口到达1295330000人2.1999年全国有学校生135479600人3.地球和太阳的平均距离是149500000千米六、板书设计.十进制计数法1、数的产生2、十进制计数法相邻两个计数单位间的进率都是10.数学教案-十进制计数法一文。

微机原理实验之两位十进制数相加

计算机硬件实验室实验报告课程名称:微机原理及应用

三.实现方法(含实现思路、程序流程图、实验电路图和源程序列表等)

源代码:

Mov AH,1

Int 21H

Mov BH, AL

Mov AH,1

AND Bh, 0fH

Int 21h

Mov BL,AL

AND Bl, 0fH

Mov DL, '+'

Mov AH, 2

Int 21h

MOV AH, 1

INT 21H

Mov CH,AL

AND CH, 0fH

Mov AH, 1

INT 21H

Mov CL,AL

AND CL, 0fH

ADD BL, CL

Mov Al,BL

Mov AH,00H 四.实验结果分析(含执行结果验证、输出显示信息、图形、调试过程中所遇的问题及处理方法等)

结论如上图

五.结论

本次实验完成了简单的两个两位十进制数相加。

完成了表达式的输出,将实验跟理论相结合,加深了对知识的理解。

AAA Mov Bl,Al ADC BH,CH Mov AL,BH Mov AH,00H AAA Mov CH,AH Mov CL,Al ADD BL, 30H ADD CX, 3030H Mov DL, '=' Mov AH, 2 Int 21H Mov DL,CH Mov AH, 2 Int 21H Mov DL, CL Mov AH, 2 Int 21H Mov DL,BL Mov AH, 2 INT 21H。

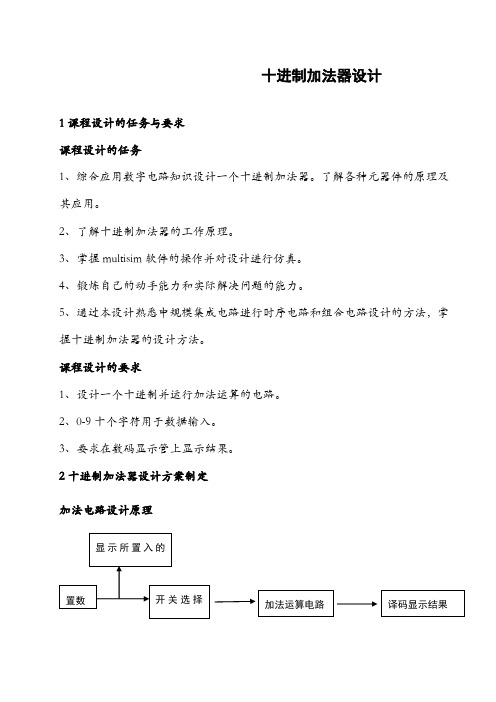

十进制加法计数器

十进制加法器设计1课程设计的任务与要求 课程设计的任务1、综合应用数字电路知识设计一个十进制加法器。

了解各种元器件的原理及其应用。

2、了解十进制加法器的工作原理。

3、掌握multisim 软件的操作并对设计进行仿真。

4、锻炼自己的动手能力和实际解决问题的能力。

5、通过本设计熟悉中规模集成电路进行时序电路和组合电路设计的方法,掌握十进制加法器的设计方法。

课程设计的要求1、设计一个十进制并运行加法运算的电路。

2、0-9十个字符用于数据输入。

3、要求在数码显示管上显示结果。

2十进制加法器设计方案制定 加法电路设计原理图1加法运算原理框图如图1所示第一步置入两个四位二进制数。

例如(1001)2,(0011)2和(0101)2,(1000),同时在两个七段译码显示器上显示出对应的十进制数9,3和5,8。

2第二步将置入的数运用加法电路进行加法运算。

第三步前面所得结果通过另外两个七段译码器显示。

即:加法运算方式,则(1000)2+(0110)2=(1110)2 十进制8+6=14 并在七段译码显示出14。

运算方案通过开关S1——S8接不同的高低电平来控制输入端所置的两个一位十进制数,译码显示器U8和U9分别显示所置入的两个数。

数A直接置入四位超前进位加法器74LS283的A4——A1端,74LS283的B4——B1端接四个2输入异或门。

四个2输入异或门的一输入端同时接到开关S1上,另一输入端分别接开关S5——S8,通过开关S5——S8控制数B的输入,通过加法器74LS283完成两个数A和B的相加。

由于译码显示器只能显示0——9,所以当A+B>9时不能显示,我们在此用另一片芯片74LS283完成二进制码与8421BCD码的转换,即S>9(1001)2时加上3(0011)2,产生的进位信号送入译码器U10来显示结果的十位,U11显示结果的个位。

3十进制加法器电路设计加法电路的实现用两片4位全加器74LS283和门电路设计一位8421BCD码加法器。

EDA课程设计--2位十进制四则运算器电路

《电子设计自动化》课程设计题目:2位十进制四则运算器电路院(系)专业届别班级学号姓名任课老师摘要本次设计的目的是通过QuartusII软件实现输入两个2位十进制数(0~99),输出它们的四则运算(加减乘除)结果(发光二极管显示运算模式;调用LPM_MULT、LPM_CONSTANT及LPM_DIVIDE模块)。

实现的方法是利用四则运算的规律进行初步设计,然后进行调整和修改。

最终结果要求:随机的输入两个数,经过加法、减法、乘法和除法的运算,可以得到正确的运算结果。

主要分为4大部分:一、2位十进制数模块;二、加减乘除四则运算四个小模块;三、加减乘除四则运算的选择模块;四、处理输出结果的模块。

目录1 系统设计 (4)2 单元电路设计 (5)3 软件设计 (5)4 系统测试 (14)5 结论 (14)6 参考文献 (14)1、系统设计一、设计要求:输入两个2位十进制数(0~99),输出它们的四则运算(加减乘除)结果;发光二极管显示运算模式;可调用LPM_MULT及LPM_DIVIDE模块。

二、系统设计方案:(1)系统设计思路要完成2位十进制四则运算器电路,首先,需要生成2个两位的十进制数,其次,需要加减乘除四个运算,然后,四种运算的选择,最后,对输出结果的处理。

2个2位十进制模块:法一,用两个100进制计数器构成;法二,用4个10进制计数器构成。

因为add1模块(后面详细介绍)只有两个输入口,所以选择法一比较方便。

加减乘除四则运算:①加法:写一个加法程序,制成模块,再分别取出它的各位、十位、百位。

②减法:写一个减法程序,用调用LPM的方法制成一个模块,在分别取出它的各位、十位和符号位。

③乘法:直接调用内部LPM,制成乘法模块。

④除法:直接调用内部LPM,制成除法模块。

加减乘除运算的选择:写一个4路选择器,分别选择加减乘除。

对输出结果的处理:写一个程序,对应不同选择下的不同输出,注意位数(加法:输出在0~198之间,需3个LED灯来显示;减法:输出在0~99之间,需3个LED灯(其中一个符号位);乘法:输出在0~9801之间,需4个LED灯;除法:输出在0~99之间,需2个LED灯。

EDA课程设计方案之2位十进制四则运算器电路四则运算器

《电子设计自动化》课程设计题目: 2位十进制四则运算器电路院(系)信息科学与工程学院专业通信工程届别 2011级班级学号姓名任课老师彭盛亮摘要本设计是利用EDA技术实现的2位十进制四则运算器,是基于QuartusII7.2软件,利用其强大、直观、便捷和操作灵活的原理图输入设计的功能来完成本次设计的。

此设计利用QuartusII7.2中的EP2C5T144C8芯片来控制整个程序的运行,用七段数码管显示各个输入和输出,用LED灯的亮灭来显示运算模式,而软件部分则是由VHDL 语言来编写的,是通过精心的设计和合理的规划而完成的设计。

设计完成后的运算器不仅能实现数据的加减乘除运算,而且还能使数据及其计算结果在数码管上显示出来,能够实现0-99的十进制数字四则运算。

目录第一章系统设计 (1)1.1设计要求 (1)1.2系统设计方案 (1)1.2.2总体方案的论证 (2)1.2.4各功能块的划分和组成 (3)第二章单元电路设计 (4)2.1 输入模块 (4)2.2加法模块 (5)2.3减法模块 (5)2.4乘法模块 (6)2.5 除法模块 (7)2.6 模式选择模块 (8)2.7输出模块 (8)第三章软件设计 (9)3.1 软件设计平台、开发工具和实现方法 (9)3.2程序的流程方框图 (9)3.3实现的功能及程序清单 (10)3.3.1百进制计数器 (10)3.3.2四选一数据选择器 (11)3.3.3加法模块: (12)3.3.4减法模块 (12)3.3.5乘法模块 (13)3.3.6除法模块 (13)3.3.7输出模块 (13)第四章系统测试 (15)4.1 功能的测试方法、步骤 (15)4.2 仪器设备 (16)第五章结论 (16)参考文献 (16)附录A 电路图图纸 (17)附录B 软件程序 (20)第一章系统设计1.1设计要求输入两个2位十进制数(0~99),输出它们的四则运算(加减乘除)结果;发光二极管显示运算模式;可调用LPM_MULT及LPM_DIVIDE模块。

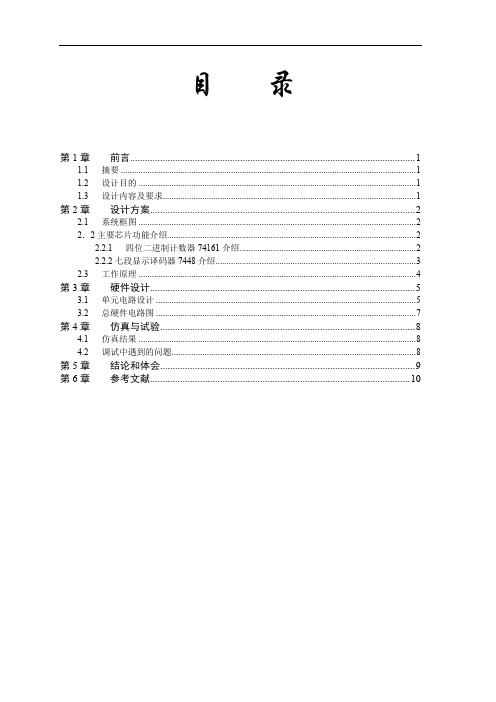

2位10进制加法计数器课程设计

目录第1章前言 (1)1.1 摘要 (1)1.2 设计目的 (1)1.3 设计内容及要求 (1)第2章设计方案 (2)2.1 系统框图 (2)2.2主要芯片功能介绍 (2)2.2.1 四位二进制计数器74161介绍 (2)2.2.2七段显示译码器7448介绍 (3)2.3 工作原理 (4)第3章硬件设计 (5)3.1 单元电路设计 (5)3.2 总硬件电路图 (7)第4章仿真与试验 (8)4.1 仿真结果 (8)4.2 调试中遇到的问题 (8)第5章结论和体会 (9)第6章参考文献 (10)第1章前言1.1 摘要在数字电路技术的课程中,计数器的功能是记忆脉冲的个数,它是数字系统中应用最广泛的基本时序逻辑构件。

计数器在微型计算机系统中的主要作用就是为CPU和I/O设备提供实时时钟,以实现定时中断、定时检测、定时扫描、定时显示等定时控制,或者对外部事件进行计数。

一般的微机系统和微机应用系统中均配置了定时器/计数器电路,它既可当作计数器作用,又可当作定时器使用,其基本的工作原理就是"减1"计数。

计数器:CLK输入脉冲是一个非周期事件计数脉冲,当计算单元为零时,OUT输出一个脉冲信号,以示计数完毕。

本十进制加法计数器是基于74161芯片而设计的,依靠传感器感应外界信号,传感器在感应范围内有物体时输出低电位,反之则是高电位。

当传感器的感应范围内有物体移过时,传感器电位由高到低再到高,出现上跳沿。

计数器会自动加一,并将在数码管上显示。

本十进制加法计数器有两位七段数码管。

可计数0~99个物体,并易于扩展。

该十进制加法计数器设计理念是用于工厂流水线上产品计数,自动计数,方便简单。

1.2 设计目的1、综合运用相关课程中所学到的理论知识去独立完成某一设计课题;2、学习用集成触发器构成计数器的方法;3、进一步熟悉常用芯片和电子器件的类型及特性,并掌握合理选用器件的原则;5、初步了解电路设计、仿真的过程和方法;4、锻炼分析问题解决问题的能力;1.3 设计内容及要求1、具有2位10进制计数功能;2、利用传感器,不接触计数;3、每一个物体经过,计数器自动加1;4、具有显示功能;5、并用相关仿真软件对电路进行仿真。

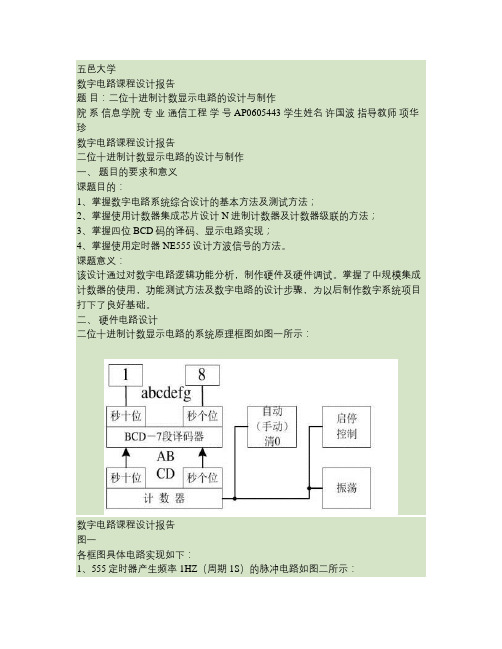

二位十进制计数显示电路的设计与制作

五邑大学数字电路课程设计报告题目:二位十进制计数显示电路的设计与制作院系信息学院专业通信工程学号 AP0605443 学生姓名许国波指导教师项华珍数字电路课程设计报告二位十进制计数显示电路的设计与制作一、题目的要求和意义课题目的:1、掌握数字电路系统综合设计的基本方法及测试方法;2、掌握使用计数器集成芯片设计N进制计数器及计数器级联的方法;3、掌握四位BCD码的译码、显示电路实现;4、掌握使用定时器NE555设计方波信号的方法。

课题意义:该设计通过对数字电路逻辑功能分析,制作硬件及硬件调试。

掌握了中规模集成计数器的使用,功能测试方法及数字电路的设计步骤,为以后制作数字系统项目打下了良好基础。

二、硬件电路设计二位十进制计数显示电路的系统原理框图如图一所示:数字电路课程设计报告图一各框图具体电路实现如下:1、555定时器产生频率1HZ(周期1S)的脉冲电路如图二所示:图二图二电路的振荡周期为:T=0.7(R1+2R2)C2=1S2、两片同步十进制计数器74160接成百进制读数器如图三所示:(1)74LS160的功能:74LS160为四位十进制计数器,它的主要功能有:异步清零:当CLR为低电平时,Q0~Q3均为低电平,而与CP无关。

同步置数功能:当LD为低电平时,计数功能被禁止,在CP上升沿作用下D0~D3的数据被置入计数器,并呈现在Q0~Q3输出端。

同步计数:当EP和ET均为高电平时,在CLK上升沿作用下,Q0~Q3同时变化。

当计数字电路课程设计报告数到最大时,C输出一个高电平脉冲。

锁存:当EP和ET中任意一个为低电平,则计数器禁止计数,为锁存状态。

(2)两片同步十进制计数器74160接成百进制计数器。

图三电路是并行进位方式的接法,以第一片的进位输出TC作为第二片的EP和ET输入,每当第一片计成9(1001)时TC变为1,下个CLK信号到达时第二片为计数工作状态,计入1,而第二片计成0(0000),它的TC端加到低电平。

实验三 双十进制计数器

• 另一种级间采用并行进位方式,即同步方式,这种 方式一般是把各计数器的CP端连在一起接统一的时 钟脉冲,而低位计数器的进位输出送高位计数器的 计数控制端。

仿真后根据波形图可以进一步分析电路的工作原 理:当clk输入时钟信号时,clr信号具有清0功能,当 enb为高电平时允许计数,低电平时禁止计数;当低4 位计数器计到9的向高4位计数器进位,当计数计满99 之后cout进位信号值变为1。

注意:引脚锁定时clk信号与clr信号均采用芯片 中的全局时钟与全局清零信号,即clk信号锁定83引脚, clr锁定数器中触发器翻转是否同步分:异步计数 器、同步计数器。

(2)按计数进制分:二进制计数器、十进制计数器 、N进制计数器。

(3)按计数增减分:加法计数器、减法计数器、加/ 减法计数器。

• 同步计数器有进位或借位输出端,可以选择合适 的进位或借位输出信号来驱动下一级计数器计数。

任务三 图形法---双十进制计数器

1

任务分析:计数器原理

2

知识准备:电路工作原理

3

任务实施:总线的使用

1

一、任务分析:计数器工作原理

在数字电路中,能够记忆输入脉冲CP个 数的电路称为计数器。计数器累计输入脉冲 的最大数目称为计数器的“模”,用M表示。 计数器的“模”实际上为电路的有效状态。 计数器的应用:计数、定时、分频及进行数 字运算等。

第2个计数器的4位计数输出是q[7]-q[4],总线输出

信号是q[7..4]。这两个计数器的总的进位信号,即可用

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录

第1章前言 (1)

1.1 摘要 (1)

1.2 设计目的 (1)

1.3 设计内容及要求 (1)

第2章设计方案 (2)

2.1 系统框图 (2)

2.2主要芯片功能介绍 (2)

2.2.1 四位二进制计数器74161介绍 (2)

2.2.2七段显示译码器7448介绍 (3)

2.3 工作原理 (4)

第3章硬件设计 (5)

3.1 单元电路设计 (5)

3.2 总硬件电路图 (7)

第4章仿真与试验 (8)

4.1 仿真结果 (8)

4.2 调试中遇到的问题 (8)

第5章结论和体会 (9)

第6章参考文献 (10)

第1章前言

1.1 摘要

在数字电路技术的课程中,计数器的功能是记忆脉冲的个数,它是数字系统中应用最广泛的基本时序逻辑构件。

计数器在微型计算机系统中的主要作用就是为CPU和I/O设备提供实时时钟,以实现定时中断、定时检测、定时扫描、定时显示等定时控制,或者对外部事件进行计数。

一般的微机系统和微机应用系统中均配置了定时器/计数器电路,它既可当作计数器作用,又可当作定时器使用,其基本的工作原理就是"减1"计数。

计数器:CLK输入脉冲是一个非周期事件计数脉冲,当计算单元为零时,OUT输出一个脉冲信号,以示计数完毕。

本十进制加法计数器是基于74161芯片而设计的,依靠传感器感应外界信号,传感器在感应范围内有物体时输出低电位,反之则是高电位。

当传感器的感应范围内有物体移过时,传感器电位由高到低再到高,出现上跳沿。

计数器会自动加一,并将在数码管上显示。

本十进制加法计数器有两位七段数码管。

可计数0~99个物体,并易于扩展。

该十进制加法计数器设计理念是用于工厂流水线上产品计数,自动计数,方便简单。

1.2 设计目的

1、综合运用相关课程中所学到的理论知识去独立完成某一设计课题;

2、学习用集成触发器构成计数器的方法;

3、进一步熟悉常用芯片和电子器件的类型及特性,并掌握合理选用器件的原则;

5、初步了解电路设计、仿真的过程和方法;

4、锻炼分析问题解决问题的能力;

1.3 设计内容及要求

1、具有2位10进制计数功能;

2、利用传感器,不接触计数;

3、每一个物体经过,计数器自动加1;

4、具有显示功能;

5、并用相关仿真软件对电路进行仿真。

第2章设计方案

2.1 系统框图

图表 2.1 计数器的整体框图

2.2主要芯片功能介绍

2.2.1 四位二进制计数器74161介绍

图2.2.是74161芯片的逻辑电路图,其也对应了74161芯片的引脚。

图2.3是74161芯片的功能表

图表 2.2 74ls161逻辑电路图

图表 2.3 74161的功能表

异步清零:当CR=0 时,不论始终脉冲是否有上升沿用,立即,Q0 = 0 ;Q1 = 0 ;Q2 = 0 ;Q3 = 0

同步预置:当LD=0时,在时钟脉冲上升沿的作用下,Q0 = d1 ;Q1 = d2 ;Q2 = d3 ;Q3 = d4

当使能端LD=0 :S=0时,计数器计数。

锁存:当使能端ENP=0或ENT=0时,计数器禁止计数,为锁存状态。

2.2.2七段显示译码器7448介绍

图2.4是7448芯片的引脚。

2.5是7448芯片的功能表,当接好数码管时显示的结果。

图表 1.4 7448引脚

图表 2.5 七段译码器逻辑功能表

正常译码显示:LT=1,BI/RBO=1时,对输入的十进制1到15进行译码,产生七段相对应的七段显示码。

灭灯:当RBI=0,而输入端为0时,是译码器全灭。

当RBI=1时才产生7显示码。

试灯:LT=0无论输入怎么样,则七段数码管全亮,所以LT用来检测数码管的好坏。

2.3 工作原理

利用四位2制计数器74161设计成两位十进制。

个位、十位74161计数器的S、M脚接低电平,个位74161计数器CP脚接传感器的输出端口。

需要注明的是,本计数器采用异步清零法实现十进制。

个位、十位74161计数器的Q3、Q1相与非,与非门输出端接到74161清零端。

十位74161计数器CP脚接个位与非门的输出端。

,这样个位,十位都处于计数工作状态。

个位计数器由Q3Q2Q1Q0(0000)2增加到(1010)2时产生进位信号,进位信号接传给个位计数器和十位计数器,分别实现了个位清零十位加一的功能。

第3章硬件设计

3.1 单元电路设计

3.1 两位十进制计数器电路图

功能:U2的D0 D1 D2 D3输出的个位,U1的D0 D1 D2 D3输出的十位。

当传感器的感应范围内有物体移过时,传感器电位由高到低再到高,出现上跳沿。

计数器会自动加一。

个位计数器加满9后,下次输出端出现1010,此时通过与非门,实现个位清零,同时,十位加一。

3.2 解码显示电路

功能: D C B A接口接输入信号,U 3的 D C B A接来个位74191芯片的的输出端,U4接十位74191的输出端,这样来自于计数器的个位、十位数据就能在数码管上显示。

3.2 总硬件电路图

图表 3.3 总硬件电路图元器件清单:

1 、7400 一片

2 、7448 两片

3 、74161 两片

4 、共阴数码管两个

5 、传感器一个

第4章仿真与试验

4.1 仿真结果

图4.1是仿真结果图。

本仿真是在Multisim10的仿真环境下进行的。

从图中可以清楚的看见整个电路工作原理和工作过程。

4.1电路仿真结果

4.2 调试中遇到的问题

设计本电路的难点是怎么实现74161的十六制转化为十进制?十六进制的1001到1010的进位就等于9到10的进位,所以要实现十进制的关键是当1001变到1010时能产生一个脉冲信号,该脉冲信号传到下一级的输入端和本级的清零端。

初步设计就采集Q3Q1的信号再相“与非”,当1001变到1010时输出“1”;

第5章结论和体会

回顾起此课程设计,至今我仍感慨颇多,从理论到实践,在这段日子里,可以说得是苦多于甜,但是可以学到很多很多的东西,同时不仅可以巩固了以前所学过的知识,而且学到了很多在书本上所没有学到过的知识。

此次课程设计,真可谓一波多折,期间真的是让人伤透了脑筋,也经历了许多的挫折和磨难,几度想退缩放弃,但硬是熬到了最后,并仿真成功。

这次设计不仅让我又一次全面的复习了模拟、数字电子技术的一部分知识,同时也让自己体会到从设计到画图、再仿真、再调试的酸甜苦辣,但可喜的是最终都得到了解决。

在课程设计后我有以下心得体会:

1 本次课程设计提高了自己的设计能力,对知识的应用能力,及查找知识的能力。

在设计和仿真过程中往往不是一蹴而就,一帆风顺。

元器件型号的正确选择,在仿真过程中产生的问题都是需要解决的。

在仿真过程中意料之外的情况就会接踵而至,更有甚者原理没问题,但是就是仿真不出来结果,有的可能是逻辑表达式存在竞争冒险,有的可能是元器件选择不对。

有时因为知识有限,所以需要查阅相关资料,思路即出路,有什么不懂不明白的地方要及时请教或上网查询。

2 帮助我更加熟练仿真软件protues和multisim的运用,这对我以后的课程设计会有很大的帮助。

由于设计的电路中可能存在错误,或者在搭接电路时出错,可能损坏元器件,或者在调试中损坏仪器,从而造成经济损失。

而电路仿真中也会损坏元器件或仪器,但不会造成经济损失。

但是我们不能一味依赖仿真,仿真软件虽然方便可也能增加惰性,不能真正起到提高我们动手能力的目的。

3 熟练了对word文档的格式编排,尝试使用新的画框图软件visio。

Word软件应用极为广泛,熟练对文档的排版是大学生的基本技能要求。

通过对该报告的排版,我在这方面的能力得到了很大的提高。

4 热爱生活,体验生活,完善生活。

设计开始时毫无头绪,不知道该设计什么,能设计什么。

灵感总是青睐于热爱生活的人,设计该题目的灵感就来自于体育场,我就想到了设计一个万用型的计分器。

所以最终决定设计一个十进制加一计数器。

5本次课程设计让我对学以致用有了深刻的体会。

宋代朱熹有诗“纸上得来终觉浅,绝知此事要躬行”。

课堂上学得仅仅是理论,理论可以指导实践,但在实际做的过程中往往不是那么得心应手,或许是困难重重,荆棘满地,这就需要我们用所学的知识去分析解决问题,这过过程我感觉可以称之为“反哺”,它有利于我们对知识的理解,加深我们对知识的掌握,促进我们对知识的应用。

6通过这此电子设计提高了我对数电,模电学习的兴趣,在生活中有很多电子商品,可我们感觉离我们可能太远,于是望而却步,徘徊不前。

如果有这样的心理,那永远不可能进步,永远不可能接触到电子设计。

所以我们需要勇气去尝试,积累设计的宝贵经验,不积跬步无以至千里,最终我们定当越做越好。

二位十进制计数器

第6章参考文献

[1] 艾永乐,付子义. 数字电子技术基础. 北京:中国电力出版社,2008.

[1] 康华光. 电子技术基础. 第五版. 北京:高等教育出版社,2008

[2] 艾永乐,付子义. 模拟电子技术基础. 北京:中国电力出版社,2008.

[2] 周瑞景,张丽,娜丁莉. 基于protues的电路及单片机设计仿真,第二版. 北京:北京航空航天大学出版社,2010.

10。