【资料】集成电路制造工艺流程(漫画)汇编

集成电路制造工艺流程图

2020/8/12

韩良

3

集成电路设计原理

国际微电子中心

引言

3. PDK文件

➢ 首先,代工单位将经过前期开发确定的一套工艺 设计文件PDK(Pocess Design Kits)通过因特网传 送给设计单位。

PDK文件包括:工艺电路模拟用的器件的SPICE

宏力 8英寸晶圆0.25/0.18 mCMOS工艺 华虹 NEC 8英寸晶圆0.25mCMOS工艺 台积电(TSMC) 在松江筹建 8英寸晶圆0.18

mCMOS工艺 联华(UMC) 在苏州筹建 8英寸晶圆0.18

mCMOS工艺等等。

2020/8/12

韩良

8

集成电路设计原理

7.境外代工厂家一览表

➢ 在一张张掩模的参与下,工艺工程师完成芯片的 流水式加工,将版图数据定义的图形最终有序的 固化到芯片上。这一过程通常简称为“流片”。

2020/8/12

韩良

6

集成电路设计原理

国际微电子中心

引言

6. 代工工艺

代工(Foundry)厂家很多,如:

无锡上华(0.6/0.5 mCOS和4 mBiCMOS 工艺)

国际微电子中心

思考题

1.需要几块光刻掩膜版(mask)? 2.每块掩膜版的作用是什么? 3.器件之间是如何隔离的? 4.器件的电极是如何引出的? 5.埋层的作用?

2020/8/12

韩良

16

集成电路设计原理

国际微电子中心

双极集成电路的基本制造工艺,可以粗

略的分为两类:一类为在元器件间要做隔离 区。隔离的方法有多种,如PN结隔离,全介 质隔离及PN结-介质混合隔离等。另一类为 器件间的自然隔离。

微电子技术应用基础第二章集成电路的制造工艺

③ 离子注入掺杂的均匀性好,可以在较大面积上形成既薄又均匀的 掺杂层,而且横向扩散比热扩散小得多。

④ 离子注入技术对于注入离子的能量和剂量可以分别独立地控制, 因而可以精确控制掺杂的浓度和掺杂深度。

第七节

1

在二氧化硅薄膜上开窗口的光刻工艺步骤 图

3 二氧化硅膜的制备方法 图

此外还有氢氧合成氧化及高压氧化等制备二氧化硅膜的方法。

第五节 化学汽相淀积(CVD)方法

化学汽相淀积指的是通过气态物质的化学反应在衬底上淀积一层薄膜 材料的过程。

化学汽相淀积技术特点是:淀积温度低,淀积薄膜的成分和厚度容易 控制,均匀性和重复性好,适用范围宽,设备简单等诸多优点。

1

(1) PN

图

PN结隔离工艺的优点是方法简单、易于制造、无需特殊技术和设备。

① 由于PN结漏电流的存在,隔离性能欠理想。

② 由于隔离扩散时的横向扩散,因此要占用较多芯片面积,这对提高 集成度不利。

③ 隔离结面积大,由于PN结的电容效应,会影响高频放大器的频率响 应和高速数字电路的速度。

④ PN结隔离的抗辐照能力差,受温度影响大。这是因为PN结的电特性 对温度和辐射影响灵敏的缘故。

做专业的企业,做专业的事情,让自 己专业 起来。 2020年 12月 下午10 时13分 20.12. 722:1 3Dec ember 7, 2020

时间是人类发展的空间。2020年12 月7日星 期一1 0时13 分17秒 22:13 :177 December 2020

科学,你是国力的灵魂;同时又是社 会发展 的标志 。下午 10时13 分17 秒下午1 0时13 分22: 13:17 20.12. 7

集成电路的制造工艺流程.

外延层淀积

1。VPE(Vaporous phase epitaxy)

硅

SiCl4+H2→Si+HCl 2。氧化

气相外延生长

Tepi>Xjc+Xmc+TBL-up+tepi-ox SiO2

N-epi

N+-BL

N+-BL

P-SUB

第二次光刻—P+隔离扩散孔

• 在衬底上形成孤立的外延层岛,实现元件的隔离.

IC常用术语

圆片:硅片 芯片(Chip, Die): 6、8 :硅(园)片直径:1 =25.4mm 6150mm; 8200mm; 12300mm; 亚微米<1m的设计规范 深亚微米<=0.5 m的设计规范 0.5 m 、 0.35 m -设计规范(最小特征尺

寸) 布线层数:金属(掺杂多晶硅)连线的层数。

集成度:每个芯片上集成的晶体管数

IC工艺常用术语

净化级别:Class 1, Class 10, Class 10,000 每立方米空气中含灰尘的个数 去离子水 氧化 扩散 注入 光刻 …………….

生产工厂简介 PSI

一级净化厂房

Fab Two was completed January 2,

1996 and is a "State of the Art"

第五次光刻—引线接触孔

•

SiO2

P P+

N+-BL

P N-epi P+ N-epi

N+ P+

N+-BL

P-SUB

去SiO2—氧化--涂胶—烘烤---掩膜(曝光)---显影---坚膜 —蚀刻—清洗—去膜—清洗

集成电路制造工艺流程.ppt

? mCMOS工艺 ? 联华(UMC) 在苏州筹建 8英寸晶圆0.18

? mCMOS工艺等等。

2013-4-18

韩良

8

集成电路设计原理

通过因特网传送到代工单位。

2013-4-18

韩良

5

集成电路设计原理

国际微电子中心

引言

5. 掩模与流片

? 代工单位根据设计单位提供的 GDS-Ⅱ格式的版图 数据,首先制作掩模( Mask),将版图数据定义 的图形固化到铬板等材料的一套掩模上。

? 一张掩模一方面对应于版图设计中的一层的图形, 另一方面对应于芯片制作中的一道或多道工艺。

8. 芯片工程与多项目晶圆计划

2013-4-18

韩良

11

集成电路设计原理

国际微电子中心

引言

8. 芯片工程与多项目晶圆计划

? 多项目晶圆 MPW(multi-project wafer) 技术服 务是一种国际科研和大学计划的流行方式。

? MPW技术把几到几十种工艺上兼容的芯片拼装 到一个宏芯片(Macro-Chip )上然后以步进的 方式排列到一到多个晶圆上,制版和硅片加工 费用由几十种芯片分担,极大地降低芯片研制 成本,在一个晶圆上可以通过变换版图数据交 替布置多种宏芯片。

(Simulation Program with IC Emphasis)参

数,版图设计用的 层次定义,设计规则 ,晶体管 、电阻、电容等元件和通孔( VIA)、焊盘等基 本结构的版图 ,与设计工具关联的 设计规则检查 (DRC)、参数提取( EXT)和版图电路对照( LVS)用的文件。

集成电路制造工艺流程图

在集成电路制造过程中,该公司面临生产效率低下、产品质 量不稳定等问题,需要进行工艺流程优化。

优化动机

为了提高生产效率、降低成本、提升产品质量,该公司决定 开展集成电路制造工艺流程优化实践。

工艺流程优化措施与实践

措施一

引入自动化设备与智能检测系统

具体实践

引入先进的自动化生产线和智能检测设备,实现生产过程的自动化和智能化。

集成电路制造的定义

集成电路制造是指将多个电子元件集 成在一块衬底上,通过微细加工技术 实现电路功能的过程。

集成电路制造涉及多个工艺步骤,包 括光刻、刻蚀、掺杂、薄膜淀积等, 以实现电路的设计要求。

集成电路制造的重要性

集成电路制造是现代电子工业的基础 ,广泛应用于通信、计算机、消费电 子等领域。

集成电路制造技术的发展对于提高电 子产品的性能、降低成本、促进产业 升级具有重要意义。

Hale Waihona Puke 详细描述新型封装技术如倒装焊、晶圆级封装等不断 涌现,能够实现更小体积、更高集成度的封 装形式。同时,测试技术也在向自动化、高 精度方向发展,以提高测试效率和准确性。 这些技术的发展为集成电路的性能提升和应 用拓展提供了有力支持。

04

集成电路制造的设备与材料

集成电路制造的设备

晶圆制备设备

用于制造集成电路的晶 圆制备设备,包括切割 机、研磨机、清洗机等

。

光刻设备

用于将电路图形转移到 晶圆表面的光刻设备, 包括曝光机和掩膜对准

器等。

刻蚀设备

用于在晶圆表面刻蚀出 电路图形的刻蚀设备, 包括等离子刻蚀机和湿

法刻蚀机等。

集成电路制造的材料

半导体材料

用于制造集成电路的半导体材料,如硅和锗等 。

集成电路制造流程共64页文档

集成电路制造流程

56、极端的法规,就是极端的不公。 ——西 塞罗 57、法律一旦成为人们的需要,人们 就不再 配享受 自由了 。—— 毕达哥 拉斯 58、法律规定的惩罚不是为了私人的 利益, 而是为 了公共 的利益 ;一部 分靠有 害的强 制,一 部分靠 榜样的 效力。 ——格 老秀斯 59、假如没有法律他们会更快乐的话 ,那么 法律作 为一件 无用之 物自己 就会消 灭。— —洛克

60、人民的幸福是至高无个的法。— —西塞 罗

6、最大的骄傲于最大的自卑都表示心灵的最软弱无力。——斯宾诺莎 7、自知之明是最难得的知识。——西班牙 8、勇气通往天堂,怯懦通往地狱。——塞内加 9、有时候读书是一种巧妙地避开思考的方法。——赫尔普斯 10、阅读一切好书如同和过去最杰出的人谈话。——笛卡儿

集成电路制造流程图

2012-04-23

中国科学技术大学 快电子实验室 刘树彬 赵雷

27

版图设计

2012-04-23

中国科学技术大学 快电子实验室 刘树彬 赵雷

28

版图设计

2012-04-23

中国科学技术大学 快电子实验室 刘树彬 赵雷

29

集成电路设计制造过程

2012-04-23

中国科学技术大学 快电子实验室 刘树彬 赵雷

期使用一层金属,慢慢扩展到双层金属,0.35um工艺可 以提供3~4层金属,现代工艺足以提供6层以上的金属。 镍铬合金薄膜电阻(金属膜电阻,高方块电阻阻) BiCMOS工艺 BCD工艺 HVCMOS工艺

2012-04-23

中国科学技术大学 快电子实验室 刘树彬 赵雷

26

版图(Layout)设计

2012-04-23

中国科学技术大学 快电子实验室 刘树彬 赵雷

18

栅氧和阈值电压调整

未经调整的PMOS管的阈值电压在-1.5 V到-1.9 V之间,NMOS 可能在-0.2 V到0.2 V之间。所以在栅氧(厚度在0.01 um~0.03 um)生长后,一般在栅氧区注入硼来进行阈值电压调整。

工艺线上一般同时对NMOS和PMOS进行阈值电压调整,将 NMOS阈值电压调整到0.7~0.8 V,PMOS调整到0.8~0.9 V阱区 掺杂浓度过高会导致阱区结电容和衬偏效应更加明显,阈值电 压调整可以降低阱的掺杂浓度。

2012-04-23

中国科学技术大学 快电子实验室 刘树彬 赵雷

10

掺杂 -- 扩散

硅中固态杂质的扩散需要3个步骤:预淀积、推进(推阱 )、和退火(激活杂质)。

预淀积过程中,硅片被送入到高温扩散炉中,杂质从源转 移到扩散炉中,温度800到1100℃持续10~30分钟,杂质 仅进入了硅片很薄的一层。

集成电路设计与制造的主要流程图

单元库

综合

向Foundry提供 逻辑网表

布局布线

网表

逻辑模拟

逻辑图

掩膜版图 生成延迟

版图检查/网表和参数 文件

后仿真

提取/网表一致性检查

产生测试向量

制版/流片 /测试/封装

门阵列设计过程

43

门阵列方法的设计特点:设计周期短,设计成本 低,适合设计适当规模、中等性能、要求设计时 间短、数量相对较少的电路

19

实际设计流程

2、逻辑和电路设计

概念:确定满足一定逻辑或电路功能的由逻辑或电路单元组 成的逻辑或电路结构

过程: A.数字电路:RTL级描述

逻辑综合(Synopsys,Ambit)

逻辑网表

逻辑模拟与验证,时序分析和优化 难以综合的:人工设计后进行原理图输入,再进行

逻辑模拟

20

电路实现(包括满足电路性能要求的电路结构 和元件参数):调用单元库完成;

件来完成设计 各级设计需要验证

15

典型的实际设计流程

1、系统功能设计

目标:实现系统功能,满足基本性能要求 过程:功能块划分,RTL级描述,行为仿真

功能块划分

RTL级描述(RTL级VHDL、Verilog)

RTL级行为仿真:总体功能和时序是否正确

16

功能块划分原则: 既要使功能块之间的连线尽可能地少,接口清 晰,又要求功能块规模合理,便于各个功能块 各自独立设计。同时在功能块最大规模的选择 时要考虑设计软件可处理的设计级别

图

版图设计

功能描述与逻辑描述

功能图 逻辑图 电路图 符号式版图, 版图

举例:x=a’b+ab’;CMOS与非门;CMOS反相器版图

12

集成电路制造工艺流程介绍

集成电路制造工艺流程介绍集成电路已经在各行各业中发挥着非常重要的作用,是现代信息社会的基石。

集成电路设计:一般英文称为IC,integrated circuit,涉及对电子器件 例如晶体管、电阻器、电容器等)、器件间互连线模型的建立。

所有的器件和互连线都需安置在一块半导体衬底材料之上,这些组件通过半导体器件制造工艺 例如光刻等)安置在单一的硅衬底上,从而形成电路。

集成电路的制作,是将设计好的电路图通过众多复杂的工艺构建在事先准备好的硅片上,最后进行封测的过程。

这一过程需要半导体材料、设备、洁净工程等上游产业链作为支撑。

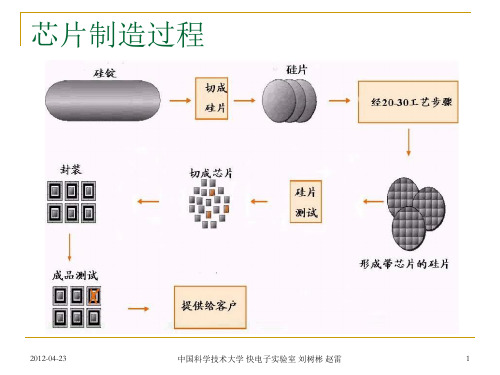

成电路设计与制造的主要流程一颗芯片的诞生,可分为芯片设计、芯片制造和封装三个环节。

一、芯片设计客户提出设计要求,IC设计工程师完成逻辑电路的设计,将设计图转化成电路图,进行软件测试验证,看是否符合客户需求,最后将电路图以光罩的形式制作出来,用于下一步制造使用。

二、芯片制造IC制造分为两大环节:晶圆制造和晶圆加工。

晶圆(wafer),是制造各式电脑芯片的基础。

我们可以将芯片制造想象成用乐高积木盖房子,即由一层又一层的堆叠,完成自己期望的造型(也就是各式芯片)。

为了做出一座完美、稳固的房子,我们需要有一个良好的地基,也就是一个平稳的基板。

对芯片制造来说,这个基板就是“晶圆”。

晶圆制造就是利用二氧化硅作为原材料制作单晶硅硅片的过程。

单晶硅片的生产流程是:拉晶--滚磨--线切割--倒角--研磨--腐蚀--热处理--边缘抛光--正面抛光--清洗--检测--外延等步骤,其中拉晶、研磨和抛光是保证半导体硅片质量的关键。

晶圆加工:指在晶圆上制作逻辑电路的过程,在硅片上进行扩散、沉积、光刻、刻蚀、离子注入、抛光、金属化等操作,这些都是在晶圆洁净厂房进行的。

三、IC封测对晶圆进行减薄、切割、贴片、引线键合、封装、测试的过程。

半导体制造最后一个制程为测试,测试制程可分成初步测试与最终测试,其主要目的除了为保证顾客所要的货无缺点外,也将依规格划分IC的等级。

集成电路设计与制造的主要流程课件

•65

•集成电路设计与制造的主要流程

•66

•集成电路设计与制造的主要流程

•67

•集成电路设计与制造的主要流程

•பைடு நூலகம்8

•集成电路设计与制造的主要流程

•69

•集成电路设计与制造的主要流程

•70

•集成电路设计与制造的主要流程

•71

•集成电路设计与制造的主要流程

•72

•集成电路设计与制造的主要流程

•25

•集成电路设计与制造的主要流程

•26

•集成电路设计与制造的主要流程

•27

•集成电路设计与制造的主要流程

•28

•集成电路设计与制造的主要流程

•29

•集成电路设计与制造的主要流程

•30

•集成电路设计与制造的主要流程

•31

•集成电路设计与制造的主要流程

•32

•集成电路设计与制造的主要流程

•57

•集成电路设计与制造的主要流程

•58

•集成电路设计与制造的主要流程

•59

•集成电路设计与制造的主要流程

•60

•集成电路设计与制造的主要流程

•61

•集成电路设计与制造的主要流程

•62

•集成电路设计与制造的主要流程

•63

•集成电路设计与制造的主要流程

•64

•集成电路设计与制造的主要流程

•41

•集成电路设计与制造的主要流程

•42

•集成电路设计与制造的主要流程

•43

•集成电路设计与制造的主要流程

•44

•集成电路设计与制造的主要流程

•45

•集成电路设计与制造的主要流程

•46

•集成电路设计与制造的主要流程

集成电路的制造工艺流程

目录

• 集成电路制造概述 • 集成电路设计 • 集成电路制造工艺 • 集成电路制造设备与材料 • 集成电路制造的环境影响与可持

续性 • 集成电路制造的案例研究

01

集成电路制造概述

集成电路的定义与重要性

集成电路是将多个电子元件集成在一块衬底上,实现一定的电路或系统功能的微 型电子部件。由于其体积小、性能高、可靠性强的特点,集成电路在通信、计算 机、消费电子、汽车电子、工业控制等领域得到广泛应用。

智能化与自动化

随着智能化和自动化技术的发展, 制造设备和材料需要更加智能化和 自动化,以提高生产效率和产品质 量。

05

集成电路制造的环境影响与 可持续性

制造过程中的环境影响

1 2

能源消耗

集成电路制造过程中需要大量的能源,包括电力、 蒸汽和冷却水等,能源消耗巨大。

废弃物产生

制造过程中会产生各种废弃物,如废水、废气和 固体废弃物等,对环境造成一定压力。

3. 刻蚀和切割

通过刻蚀技术将电路结构转移 到衬底上,并使用切割技术将 单个器件分离出来。

总结词

MEMS器件是一种微小型化的 机械和电子系统,具有高精度、 高可靠性和低成本等特点。

2. 制膜和光刻

在衬底上制备所需的薄膜材料, 并使用光刻技术将电路图形转 移到薄膜上。

4. 测试和封装

对制造完成的MEMS器件进行 性能测试,合格的产品进行封 装和可靠性试验。

绿色采购

优先选择环保合规的供应 商和原材料,从源头减少 对环境的负面影响。

环境友好型制造技术的未来发展

新材料和新工艺

研发和推广环境友好型新材料和 新工艺,替代传统的高污染材料 和工艺,降低能耗和减少废弃物 排放。

【良心出品】集成电路制造工艺流程

集成电路制造工艺流程1.晶圆制造( 晶体生长-切片-边缘研磨-抛光-包裹-运输 )晶体生长(Crystal Growth)晶体生长需要高精度的自动化拉晶系统。

将石英矿石经由电弧炉提炼,盐酸氯化,并经蒸馏后,制成了高纯度的多晶硅,其纯度高达0.99999999999。

采用精炼石英矿而获得的多晶硅,加入少量的电活性“掺杂剂”,如砷、硼、磷或锑,一同放入位于高温炉中融解。

多晶硅块及掺杂剂融化以后,用一根长晶线缆作为籽晶,插入到融化的多晶硅中直至底部。

然后,旋转线缆并慢慢拉出,最后,再将其冷却结晶,就形成圆柱状的单晶硅晶棒,即硅棒。

此过程称为“长晶”。

硅棒一般长3英尺,直径有6英寸、8英寸、12英寸等不同尺寸。

硅晶棒再经过研磨、抛光和切片后,即成为制造集成电路的基本原料——晶圆。

切片(Slicing) /边缘研磨(Edge Grinding)/抛光(Surface Polishing)切片是利用特殊的内圆刀片,将硅棒切成具有精确几何尺寸的薄晶圆。

然后,对晶圆表面和边缘进行抛光、研磨并清洗,将刚切割的晶圆的锐利边缘整成圆弧形,去除粗糙的划痕和杂质,就获得近乎完美的硅晶圆。

包裹(Wrapping)/运输(Shipping)晶圆制造完成以后,还需要专业的设备对这些近乎完美的硅晶圆进行包裹和运输。

晶圆输送载体可为半导体制造商提供快速一致和可靠的晶圆取放,并提高生产力。

2.沉积外延沉积 Epitaxial Deposition在晶圆使用过程中,外延层是在半导体晶圆上沉积的第一层。

现代大多数外延生长沉积是在硅底层上利用低压化学气相沉积(LPCVD)方法生长硅薄膜。

外延层由超纯硅形成,是作为缓冲层阻止有害杂质进入硅衬底的。

过去一般是双极工艺需要使用外延层,CMOS技术不使用。

由于外延层可能会使有少量缺陷的晶圆能够被使用,所以今后可能会在300mm晶圆上更多采用。

9.晶圆检查Wafer Inspection (Particles)在晶圆制造过程中很多步骤需要进行晶圆的污染微粒检查。