第6章 输入输出及中断技术PPT课件

合集下载

专题六输入输出和中断系统 PPT资料共73页

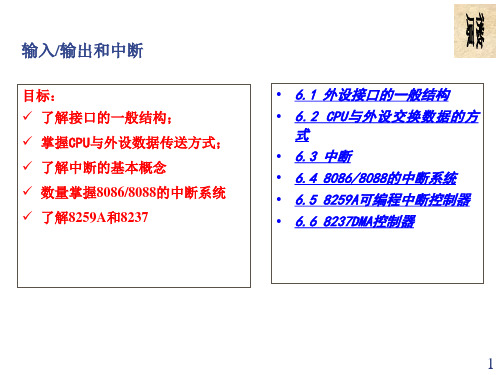

5.3 中断技术

5.3.1 中断的定义及必要性 5.3.2 中断源 5.3.3 中断的分类 5.3.4 中断系统的功能 5.3.5 中断处理过程

5.4 MCS-51的中断系统

5.4.1 MCS-51的中断源和中断标志 5.4.2 MCS-51对中断请求的控制 5.4.3 MCS-51对中断的响应和撤除 5.4.4 MCS-51中断系统的初始化及应用

DMA过程: 优点:速度快 缺点:硬件复杂,成本增加

外设向DMAC发DMA申请 DMAC向CPU发BUSRQ CPU发BUSAK响应 DMAC发存储器地址和读写信号 DMA控制结束,恢复CPU对总线控制

接口

BUS

① DMAC

②

CPU ③

DMA过程

存储器

外设

存储器

CPU

口地址

外设准备好,置入状态信号 Q=1

CPU读数据口时清掉状态信号

5.2.2 查询式传送方式

(又称条件传送——异步传送)

CPU查询外设状态信息(Ready,Busy),条件 满足时,进行数据传送

程序简单 高速CPU查询低速外设 浪费CPU时间,效率低 输入接口原理图 输出接口原理图 程序流程图

条件传送方式程序举例

Test:mov DPTR,#PORTS

movx A,DPTR Ready=1

anl A,#80H

Busy=0

jz Test ;(jnz Test)

输入接口状态

mov DPTR,#PORTD movx A,DPTR ;输入 (movx DPTR,A;输出)

D7 (A) 0/1

准备好? NO

MCS-51就是具有可屏蔽中断功能的一类CPU。

第六章_基本输入输出接口技术

20

6.3 CPU与外设之间的数据传送方式

[例] 设状态端口地址为086H,数据端口地址为084H,外 设忙碌D7=1,请用查询方式写出CPU从存储器缓冲区 Buffer送出1KB的数据给外设的程序段。 LEA SI , Buffer ;取Buffer的有效地址送SI MOV CX , 1000 ;循环次数 W1: MOV DX, 086H ;状态端口地址送DX W2: IN AL , DX ;从状态端口读入状态信息 AND AL,80H ; BUSY=0? JNZ W2 ; BUSY=1,返回继续查询 MOV AL,[SI] ; BUSY=0,取数据 MOV DX, 084H ;数据端口地址送DX OUT DX,AL ;数据输出到数据端口 INC SI ;SI指向下一个字节数据 LOOP W1 ;CX-1送CX≠0,循环 HLT ;CX=0,传送结束

FFFFF

内存 空间 I/O 空间

10

§6-2 I/O端口的编址与访问

二、 I/O端口地址的译码方法:

I/O端口地址译码的一般原则是:把CPU用于I/O端口寻址 的地址线分为高位地址线和低位地址线两部分:

将低位地址线直接连到I/O接口芯片的相应地址引脚, 实现片内寻址,即选中片内的端口。 将高位地址线与CPU的控制信号组合,经地址译码电 路产生I/O接口芯片的片选信号。 常见的译码器: 2/4线译码器74LS139 3/8线译码器74LS138

返回断点

6.3 CPU与外设之间的数据传送方式

关于中断的几点说明:

采用中断的数据传送方式时,外设处于主动申请地 位,CPU配合进行数据传送;CPU不必反复去查询 外设的状态,而是可以与外设“并行工作”,因此 提高了CPU的工作效率,并且更具有实时性。

第6章输入输出技术ppt课件

据

出 端

线

口

地址译码

(WR,IO/M ) IOW

2021/4/22

21

6.3 I/O的基本方式

( Direct Memory Access )

2021/4/22

22

▪ 无条件传送(CPU与外设同步工作):外部控制 过程各种动作时间是固定的,而且是已知的。

无条件传送:输出

输 出 设 备

锁存器

DQ G

2021/4/22

锁 存 DB(D7~D0) 器

AB 地址译码器 IOW(WR,IO/M)

28

例:如图示,外设为8个发光二极管,与其相连的 I/O端口地址80H,欲使发光二极管全亮,执行指令:

MOV AL, 0

OUT 80H, AL

CPU

DB AB CB

4

6.1 概述

输入输出(I/O)设备是计算机系统的重要组 成部分,计算机通过它们与外界进行数据交换。 因I/O设备种类繁多,CPU并不与I/O设备直接 进行信息交流,而是通过I/O接口进行。I/O接 口是连接CPU和I/O设备之间的桥梁。

输入设备和输出设备统称为外设。 I/O接口电路:即I/O适配器。

2021/4/22

5

2、接口传递的信息

接口传递的基本信息是数据信息,除此之外,还 传递状态信息和控制信息。不同的信息用不同的I/O 端口区分。 数据信息:CPU与I/O设备传递的基本信息,包括数 字量、模拟量、开关量和脉冲量。

状态信息:反映I/O设备当前工作状态的信息,如输 出设备是否空闲,输入设备是否数据准备好等。

2021/4/22

24

输入接口设计

完成如下任务: 当开关接通时,CPU 执行程序段ON; 当开关断开时,CPU 执行程序段OFF;

输入输出与中断精品PPT课件

5.1 I/O概述

数据总线

处 理 控制总线 器

地址总线

数据寄存器 状态寄存器 控制寄存器

外设数据 输 入 输

状态信号 出 设

控制信号 备

图5-1 I/ O接口示意图

5.1 I/O概述

5.1.2 I/O端口

• I/O端口是CPU与输入输出设备的交换数据 的场所。

• 端口在I/O空间中均被指定一固定地址,这 种寻址方式就被称为端口寻址。在80x86微 机中,I/O端口与存储器地址完全分开,编 址在一个独立的地址空间中,端口地址为 0000H~FFFFH ,目前大多数微机所用的 端口地址都在0~3FFH范围之内。

I/O地址 00H~0FH 20H~3FH 40H~5FH 60H~7FH 80H~9FH A0H~BFH

170H~1F7H 200H~20FH 278H~27AH

5.1 I/O概述

表5-1 I/O端口地址分配

功能 DMA控制器8237 A 中断控制器8259A 定时/计数器8253A 并行接口芯片8255A DMA页面寄存器 不屏蔽中断寄存

(2)输出指令 • 格式:OUT PortNo/DX, AL/AX • 作用:把寄存器AL或AX的内容输出到指定

端口。如果某输出设备的端口地址在0~255 范围之内,那么,可在指令OUT中直接给 出,否则,要把该端口地址先存入寄存器 DX中,然后在指令中由DX来给出其端口地 址。

5.1 I/O概述

电子CLoO工mpGa业nOy 出版社

输入输出与中断

第五章 输入输出与中断

1

5.1 I/O概述

2

5.2 简单I/O程序举例

3

5.3 中断系统

4

5.4 中断服务程序设计

40第6章输入输出和中断精品PPT课件

9

查询传送方式——又称异步传送方式

START:MOV DL,0F8H

LEA DI,DSTOR

; 存A/D结果的数据区指针

AGAIN:MOV AL,DL

AND AL,0EFH OUT 4,AL

; 使D4=0 ; 停止A/D

CALL DELAY

; 等待停止A/D动作的完成

MOV AL,DL OUT 4,AL POLL: IN AL,2

11Leabharlann 6.2.4 DMA传输4

数据

REA启DY动 D4 D2 D1 D0

U1 A/D转换器

IN0

…

1个模拟量

U5

IN7

电路的功能:完成8个模拟输入信号的采集。 工作过程: ①向口地址4写入一个字节,其D2—D0加到U5上,将IN0—IN7之一送到A/D转 换器的入口。同时由D4位启动A/D转换器工作。 ②A/D是否已转换完成,可通过口地址2读入判断。 ③READY=1则可从端口3读入A/D转换结果,存入指定区域。

传送数据前先检查外设状态,在状态满足条件时才可传 送数据,否则等待。 缺点:CPU花大量的时间进行状态查询,CPU效率较低

从状态端口读入状态信 息

外设准备好? N Y

从数据端口传送一个数据

8

6.2.2 查询传送方式举例

例:以查询方式工作的数据采集系统(P181图6—3)

DB

U3

D0

U4

CPU

3

2 U2

; 用意是DH=01,DL=00 ;BX指向数据区开始(用于存放A/D结果) ; AL=0,CF=0

OUT 20H,AL

; P0—P7全断电

CALL NEAR DELAY1 ;调延时子程序,等待继电器触点动作

查询传送方式——又称异步传送方式

START:MOV DL,0F8H

LEA DI,DSTOR

; 存A/D结果的数据区指针

AGAIN:MOV AL,DL

AND AL,0EFH OUT 4,AL

; 使D4=0 ; 停止A/D

CALL DELAY

; 等待停止A/D动作的完成

MOV AL,DL OUT 4,AL POLL: IN AL,2

11Leabharlann 6.2.4 DMA传输4

数据

REA启DY动 D4 D2 D1 D0

U1 A/D转换器

IN0

…

1个模拟量

U5

IN7

电路的功能:完成8个模拟输入信号的采集。 工作过程: ①向口地址4写入一个字节,其D2—D0加到U5上,将IN0—IN7之一送到A/D转 换器的入口。同时由D4位启动A/D转换器工作。 ②A/D是否已转换完成,可通过口地址2读入判断。 ③READY=1则可从端口3读入A/D转换结果,存入指定区域。

传送数据前先检查外设状态,在状态满足条件时才可传 送数据,否则等待。 缺点:CPU花大量的时间进行状态查询,CPU效率较低

从状态端口读入状态信 息

外设准备好? N Y

从数据端口传送一个数据

8

6.2.2 查询传送方式举例

例:以查询方式工作的数据采集系统(P181图6—3)

DB

U3

D0

U4

CPU

3

2 U2

; 用意是DH=01,DL=00 ;BX指向数据区开始(用于存放A/D结果) ; AL=0,CF=0

OUT 20H,AL

; P0—P7全断电

CALL NEAR DELAY1 ;调延时子程序,等待继电器触点动作

输入输出和中断技术优秀课件

接口的功能

设置I/O接口的必要性——I/O设备的多样性使 CPU与I/O设备交换信息比CPU与存储器交换信息 更为复杂,表现在:

1)I/O设备工作速度不同; 2)数据字长多样; 3)处理的信号不同 (模拟或数字信号、并行或串

行) ; 4)所需的控制信号不同。 I/O接口在它连接的CPU与I/O设备之间起转换作 用。

I/O单独编址

属性 统一编址

单独编址

应用 特点

motorola的M6800系列, 80X86 ,MCS96系列,

iMCS51系列

Z80系列

1.I/O端口相当于内存的一部分, 1.端口与存储器分别独立编

使内存容量减小

址,端口不占用内存空间

2.对I/O端口的读/写与对存储器 2.设有专门的 I/O指令对端 的读/写相同,所有可对内存操 口进行读写,内存操作的指 作的指令对I/O端口均可使用 令不能用于I/O端口 3.指令系统中不专设I/O指令

在PC/XT中采用的系统总线标准:PC总线。其中:AEN 引脚信号表示:当为高电平时,CPU让出总线控制权,给 DMA控制器掌管系统总线。

简单I/O接口

三态缓冲器 输入设备通过数据总线向CPU传送数据,首先需通过缓冲 器进行缓冲隔离,当CPU选通缓冲器时,才将数据送到数 据总线上,而其他的输入设备此时与总线隔离。

2、I/O传送方式

不同的传送方式适用不同的I/O设备、不同的工作 环境 :

程序控制的输入与输出 中断控制的输入与输出 直接存储器访问方式(DMA)

程序控制的输入与输出

程序传送方式以CPU为中心,数据传送的控制来 自CPU,通过执行预先编制的输入/输出程序实现 数据传输。程序传送方式可分为无条件传送和查 询传送方式。

第06章-IO系统设计ppt课件(全)

◦ 数据传输率等于所连接外设中速度最高的外设速率

A1 A2 …

B1 B2 …

通道 A1 A2 … B1 B2 … C1 C2 …

C1 C2 …

图6.16 选择通道传送方式示意图

(3)数组多路通道

◦ 综合前两种通道的优点,可连接多台高速设备,允许几 台设备并行工作,以成组交叉方式传送。每个外设都有 数据缓冲区。

硬件中断(硬中断):是一个异步信号,表明需要注意、 或需要改变执行一个同步事件。

软件中断(软中断):是利用硬件中断的概念,用软件方 式进行模拟,实现宏观上的异步执行效果。

外部中断:一般是指由计算机外设发出的中断请求,如: 键盘中断、打印机中断、定时器中断等。外部中断是可以 屏蔽的中断。

内部中断:是指因硬件出错(如突然掉电、奇偶校验错等) 或运算出错(除数为零、运算溢出、单步中断等)所引起 的中断。内部中断是不可屏蔽的中断。

主存

…

12H JMP 200 向量地址 13H JMP 300

14H JMP 400

入口地址 200 打印机服务程序

入口地址 300 显示器服务程序

… ……

图6.10 通过向量地址寻找入口地址

图6.12 链式排队线路和设备编码器

直接存储器访问方式(Direct Memory Access,DMA), 是一种直接依靠硬件在主存与I/O设备间进行数据传送,且 在 数 据 传 送 过 程 中 不 需 CPU 干 预 的 I/O 数 据 传 送 控 制 方 式 。 CPU与接口的数据传送的具体过程由硬件(DMA Controller, DMAC,DMA控制器)完成,传送速度比通过CPU快。 (1)CPU暂停方式 (2)周期挪用方式(周期窃取方式) (3)交替访问内存方式

A1 A2 …

B1 B2 …

通道 A1 A2 … B1 B2 … C1 C2 …

C1 C2 …

图6.16 选择通道传送方式示意图

(3)数组多路通道

◦ 综合前两种通道的优点,可连接多台高速设备,允许几 台设备并行工作,以成组交叉方式传送。每个外设都有 数据缓冲区。

硬件中断(硬中断):是一个异步信号,表明需要注意、 或需要改变执行一个同步事件。

软件中断(软中断):是利用硬件中断的概念,用软件方 式进行模拟,实现宏观上的异步执行效果。

外部中断:一般是指由计算机外设发出的中断请求,如: 键盘中断、打印机中断、定时器中断等。外部中断是可以 屏蔽的中断。

内部中断:是指因硬件出错(如突然掉电、奇偶校验错等) 或运算出错(除数为零、运算溢出、单步中断等)所引起 的中断。内部中断是不可屏蔽的中断。

主存

…

12H JMP 200 向量地址 13H JMP 300

14H JMP 400

入口地址 200 打印机服务程序

入口地址 300 显示器服务程序

… ……

图6.10 通过向量地址寻找入口地址

图6.12 链式排队线路和设备编码器

直接存储器访问方式(Direct Memory Access,DMA), 是一种直接依靠硬件在主存与I/O设备间进行数据传送,且 在 数 据 传 送 过 程 中 不 需 CPU 干 预 的 I/O 数 据 传 送 控 制 方 式 。 CPU与接口的数据传送的具体过程由硬件(DMA Controller, DMAC,DMA控制器)完成,传送速度比通过CPU快。 (1)CPU暂停方式 (2)周期挪用方式(周期窃取方式) (3)交替访问内存方式

输入输出与中断课件

详细描述

输入输出接口是计算机与外部设备之间的连接器,它负责将外部设备的信号转换为计算机可以识别的格式,或将 计算机的信号传输给外部设备。常见的输入输出接口包括USB、HDMI、VGA等,它们支持多种设备的连接和数 据传输。

02

中断基础

中断定 义

中断:指在计算机执行程序的过程中,出现某些突发事件或 者异常情况,打断了原有的程序执行流程,转而去执行相应 的中断处理程序。

输入输出与中断的应用场景

在实时系统中,输入输出与中断 技术被广泛应用于数据采集、控

制和通信等方面。

在多媒体处理领域,输入输出与 中断技术用于音频、视频数据的

实时传输和处理。

在网络通信中,输入输出与中断 技术用于数据的发送和接收,保 证数据传输的实时性和可靠性。

输入输出与中断的发展趋势

随着云计算、物联网等技术的发展, 输入输出与中断技术将更加注重分布 式、异构环境下系统的实时性和可靠 性。

随着虚拟现实、增强现实等技术的发展,输入输 出与中断技术也将会在这些领域得到更广泛的应 用,为人们提供更加沉浸式的体验。

未来输入输出与中断技术的发展将呈现出多元化、 智能化、人性化、虚拟化等趋势,为计算机技术 的发展注入新的活力。

THANKS

感谢观看

中断处理程序是一种特殊的程序,它可以在任何时候被操作系统调用,以处理各种中断事件。

在中断编程中,我们需要了解中断的基本概念、中断处理程序的编写方法以及如何使用编程 语言提供的中断处理函数或库进行编程。

输入输出与中断的编程实例

• 下面是一个简单的C语言程序,它演示了如何使用 输入输出函数和中断处理函数来实现一个简单的 计算器程序

3

scanf("%d %c %d", &num1, &op, &num2);

输入输出接口是计算机与外部设备之间的连接器,它负责将外部设备的信号转换为计算机可以识别的格式,或将 计算机的信号传输给外部设备。常见的输入输出接口包括USB、HDMI、VGA等,它们支持多种设备的连接和数 据传输。

02

中断基础

中断定 义

中断:指在计算机执行程序的过程中,出现某些突发事件或 者异常情况,打断了原有的程序执行流程,转而去执行相应 的中断处理程序。

输入输出与中断的应用场景

在实时系统中,输入输出与中断 技术被广泛应用于数据采集、控

制和通信等方面。

在多媒体处理领域,输入输出与 中断技术用于音频、视频数据的

实时传输和处理。

在网络通信中,输入输出与中断 技术用于数据的发送和接收,保 证数据传输的实时性和可靠性。

输入输出与中断的发展趋势

随着云计算、物联网等技术的发展, 输入输出与中断技术将更加注重分布 式、异构环境下系统的实时性和可靠 性。

随着虚拟现实、增强现实等技术的发展,输入输 出与中断技术也将会在这些领域得到更广泛的应 用,为人们提供更加沉浸式的体验。

未来输入输出与中断技术的发展将呈现出多元化、 智能化、人性化、虚拟化等趋势,为计算机技术 的发展注入新的活力。

THANKS

感谢观看

中断处理程序是一种特殊的程序,它可以在任何时候被操作系统调用,以处理各种中断事件。

在中断编程中,我们需要了解中断的基本概念、中断处理程序的编写方法以及如何使用编程 语言提供的中断处理函数或库进行编程。

输入输出与中断的编程实例

• 下面是一个简单的C语言程序,它演示了如何使用 输入输出函数和中断处理函数来实现一个简单的 计算器程序

3

scanf("%d %c %d", &num1, &op, &num2);

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

D0~D7

译码器

IOW

≥1

A6~A4

A7

A3 A2 A1 A0

74LS138

&

G

Y0

1

G2A

G2B

C B

Y1

A

IOR

≥1

74LS273

7406 Rx8

D0 Q0

a

| Q1

反相器

b

D7 Q2

c

பைடு நூலகம்

Q3

d

Q4

e

CP Q5

f

Q6

g

Q7

DP

74LS244

D0 O1 I1 D1 O2 I2 D2 O3 I3 D3 O4 I4

6

二、I/O端口

数据端口 端口 状态端口

控制端口

7

I/O端口

I/O接口 DB

数据

CPU

状态

控制

外设

8

接口和端口

接口1

端口1 端口2

┅ 端口m

接口2

端口1 端口2

┅ 端口m

接口N

端口1

┅

端口2

┅

端口m

端口地址=芯片地址(高位地址)+片内地址

端口编 址

9

三、I/O端口的编址方式

8086/8088的寻址能力:

16

I/O地址译码例

某外设接口有4个端口,地址为2F0H—— 2F3H,由A15~A2译码得到,而A1、A0用 来区分接口中的4个端口。试画该接口与系 统的连接图。

17

I/O地址译码例

地址范围:

A11

××××001011110000 ××××001011110011

任意状态 图中不接入

片内地址

状态寄存器 (or 三态门)

命令寄存器

数据线 状态线 控制线

22

接口的基本构成

数据输入/输出寄存器

暂存输入/输出的数据

命令寄存器

存放控制命令

设定接口功能、工作参数和工作方式。

状态寄存器

保存外设当前状态,以供CPU读取。

23

二、接口的类型及特点

按传输信息的方向分类:

输入接口 输出接口

14

四、I/O地址的译码

目的: 确定端口的地址 参加译码的信号: IOR,IOW,高位地址信号 OUT指令将使总线的IOW信号有效 IN指令将使总线的IOR信号有效

15

I/O译码的地址信号

当接口只有一个端口时,16位地址线一般应 全部参与译码,译码输出直接选择该端口;

当接口具有多个端口时,则16位地址线的高 位参与译码(决定接口的基地址),而低位 则用于确定要访问哪一个端口。

较少

00000H

FFFFFH 0000H

FFFFH

内存 地址

I/O 地址

12

端口的寻址

8088/8086寻址端口数:

64K个

寻址端口的信号:

IOR、IOW A15 ~ A0

13

8088/8086的I/O端口编址

采用I/O独立编址方式(但地址线与存储器共用) 地址线上的地址信号用IO/M来区分 I/O操作只使用20根地址线中的16根:A15~A0 可寻址的I/O端口数为64K(65536)个 I/O地址范围为0~FFFFH IBM PC只使用了1024个I/O地址(0~3FFH)

E1

+5V K0~K3

符号 ’0’ ’1’ ’2’ ’3’ ’4’ ’5’ ’6’ ’7’

形状

7段码 .gfedcba

符号 ’8’ ’9’ ’A’

’B’ ’C’ ’D’ ’E’ ’F’

形状

7段码 .gfedcba

I/O接口综合应用例 —— 程序段

…… Seg7 DB 3FH,06H, 5BH,4FH,66H,6DH, 7DH,07H,7FH,67H,77H, 7CH,39H,5EH,79H,71H

第6章

输入输出及中断技术

1

主要内容

基本概念

输入输出系统 I/O接口和端口 端口的编址方式

简单接口芯片及其应用 基本输入输出方法 中断的基本概念及工作过程

2

§6.1 输入输出系统

3

了解和掌握:

接口的基本功能 端口的概念 端口的编址方式 I/O地址译码

4

一、I/O接口

接口要解决的问题

18

I/O地址译码例

译码电路图:

IOR &

IOW

A11

A10

A18

≥1

A3

A2

A9

A7 ┇

A4

A1 A0

&

接口芯片

CE

19

§6.2 简单接口电路

20

掌握:

接口电路的分类及特点; 两类简单接口芯片的应用

21

一、接口的基本构成

译码

AB

电路

DB

CB

控制 逻辑

数据输入寄存器 (or 三态门)

数据输出寄存器 (锁存器)

内存:

1MB

端口:

64K个

编址方式:

与内存统一编址 独立编址

10

端口与内存的统一编址

特点:

指令及控制信号统一; 内存地址资源减少

00000H

F0000H FFFFFH

内存 地址 960KB

I/O地址 64KB

11

端口的独立编址

特点:

内存地址资源充分利用 能够应用于端口的指令

速度匹配(Buffer) 信号的驱动能力(电平转换器、驱动器) 信号形式和电平的匹配(A/D、D/A) 信息格式(字节流、块、数据包、帧) 时序匹配(定时关系) 总线隔离(三态门)

5

接口的功能

数据的缓冲与暂存 信号电平与类型的转换 增加信号的驱动能力 对外设进行监测、控制与管理,中断处理

教材p238

P238

图

27

四、锁存器接口

通常由D触发器构成; 特点:

具有对数据的锁存能力; 不具备对数据的控制能力

28

常用锁存器芯片

74LS273

8D触发器,不具备数据的控制能力

P240图

74LS373

含三态的8D触发器,具有对数据的控制能力。 既可以做输入接口,也可以做输出接口。

29

I/O接口综合应用例

根据开关状态在7段数码管上显示数字或符号 设输出接口的地址为F0H 设输入接口地址为F1H 当开关的状态分别为0000~1111时,在7段

数码管上对应显示’0’~’F’

7段数码管图见教材p242

30

F0H = 1111 0000 A0 F1H = 1111 0001

按传输信息的类型分类:

数字接口 模拟接口

按传输信息的方式分类:

并行接口 串行接口

24

接口特点

输入接口:

要求对数据具有控制能力 常用三态门实现

输出接口:

要求对数据具有锁存能力 常用锁存器实现

25

三、三态门接口

高电平、低电平、高阻态

26

74LS244

含8个三态门的集成电路芯片 在外设具有数据保持能力时用来输入接口 74LS244应用例

……

GO: IN AND MOV MOV OUT JMP

AL, 0F1H

AL, 0FH SI, AX AL, [BX+SI] 0F0H, AL GO

LEA BX, Seg7

MOV AH, 0

33

§6.3 基本输入/输出方法

34

基本输入/输出方法