低温共烧多层陶瓷(LTCC)技术特点与应用上课讲义

低温共烧陶瓷(LTCC)配套浆料和相关材料开发与应用方案(二)

低温共烧陶瓷(LTCC)配套浆料和相关材料开发与应用方案一、实施背景随着科技的飞速发展,电子行业对高性能、高可靠性、小型化和低成本的要求越来越高。

低温共烧陶瓷(LTCC)技术作为一种先进的陶瓷基板制备技术,具有高性能、高可靠性、小型化等优点,已成为电子行业的重要发展方向。

然而,LTCC技术在实际应用中仍存在一些问题,如材料性能不稳定、制造成本高等,这限制了其广泛应用。

因此,开发与LTCC 技术配套的浆料和相关材料,对于提高LTCC产品的性能、降低制造成本、推动电子行业的发展具有重要意义。

二、工作原理低温共烧陶瓷(LTCC)技术是一种将陶瓷粉体、有机载体、添加剂等原料混合制备成LTCC浆料,然后通过印刷、叠层、烧结等工艺制备成高性能、高可靠性的陶瓷基板的技术。

其中,LTCC浆料的性能直接决定了最终产品的性能。

因此,开发与LTCC技术配套的浆料和相关材料是关键。

三、实施计划步骤1.调研市场:了解当前LTCC技术的市场需求和应用情况,收集相关企业和研究机构的资料,分析现有产品的优缺点。

2.确定研究方向:根据市场调研结果,确定LTCC配套浆料和相关材料的研究方向,包括材料成分、制备工艺、性能指标等方面。

3.制备样品:根据确定的研究方向,制备LTCC配套浆料和相关材料样品。

4.性能测试:对制备的样品进行性能测试,包括物理性能、化学性能、电学性能等,以验证其是否满足市场需求。

5.优化配方:根据性能测试结果,对LTCC配套浆料和相关材料的配方进行优化,以提高产品性能。

6.中试生产:在完成配方优化后,进行中试生产,以验证生产工艺的可行性和产品的稳定性。

7.推广应用:将中试生产的产品推广到市场中,与相关企业和研究机构合作,以推动LTCC技术的广泛应用。

四、适用范围本方案适用于电子行业中的陶瓷基板制备领域,特别是那些需要高性能、高可靠性、小型化且对成本敏感的应用领域,如通信、汽车电子、航空航天等。

五、创新要点1.材料创新:通过开发新型的陶瓷粉体、有机载体和添加剂等原料,优化LTCC浆料的配方,提高产品的性能。

低温共烧结陶瓷_LTCC_特点_应用及问题_钟慧

孔径 μm 200 200 200 200 200 200 200 200 200

孔间距 mm

4 LTCC 技术的局限性

与其他封装技术比较尽管 LTCC 技术有不可 取代的优越性,是 MCM 封装技术的理想基础,但 LTCC 技术仍然存在收缩率控制和基板散热问题, 有待进一步改善。

(1)收缩率控制问题

磁性材料及器件 2003 年 8 月

LTCC 基板应用于高性能系统时,金属布线间 距小,烧结的微小形变都会严重影响系统的性能, 而且基板的收缩对信号孔和散热孔的对准也将产

(2)基板散热问题 虽然 LTCC 基板比传统的 PCB 板在散热方面 已经有了很大的改进,但由于集成度高、层数多、

器件工作功率密度高,LTCC 基板的散热仍是一个 关键问题,成为影响系统工作稳定性的决定因素之 一。目前解决散热的方法主要是采用热通孔。在 LTCC 基板上打孔,向孔中加入 Ag、Cu、Au 等高 导热的金属材料,这样可有效改善基板在叠层方向 的散热性,但层面散热仍未解决。为了使层面层的 散热也得到改善,最常用的方法是在基板的背面镀

Science and Technology, Chengdu 610054, China

Abstract:The low temperature co-fired ceramics (LTCC) technology has advantage over other traditional

packing technologies for its excellent high frequency characteristics, fine line and spaces, low resistance metallization. Integrations of four passive devices (such as L, R, T, C) and active devices (such as transistor, IC module and power MOS) to the hybrid IC can be achieved by LTCC technology. Here we introduced the history, present condition and foreground, especially its classification, market and limitations.

LTCC技术 I课件

1.2.1 LTCC 技术特点

LTCC 技术属于多芯片组件(MCM)技术中的一个分支, 最早由美国休斯公司于 1982 年开发。它兼具高温共烧陶 瓷(HTCC)技术和厚膜技术的许多优点,拥有极其广阔的 应用前景。表列出了三者之间的性能比较。

1.2.1 LTCC 技术特点

除以上表格中列举的优点外,LTCC 技术还具有温 度系数好,热膨胀系数可与硅半导体匹配的独特优点。 LTCC 相对传统的微波混合集成电路(HMIC)而言, 其特点和优势可从以下几个方面来说明: 1、内层基板中可以埋入无源电路元件,这使基板的表 面将有更多的区域可以用来安装有源器件和铺设大面积 地。这有两方面好处,一可以使组装密度获得提高,生 产效率得到改善,系统可靠性得到增强;二可以通过大 面积地的设计来实现微波的良好接地,进一步获得优良 的高频特性。 2、不同材料配方制作的 LTCC 基板的介电常数不同, 可以设计在一个较大范围内,这可以提高设计电路时的 灵活性。

陶瓷多层布线基板中,顶层需要焊接IC和元件的焊 盘采用Cu/Ni/Au金属结构。陶瓷多层布线基板的局部结 构如图所示。

内埋臵无源元件及多层布线结构基板局部图

1.1 MCM技术简介[1]

从基板材料、生产工艺的角度,MCM主要可以分为: MCM-L、MCM-C、MCM-D三类。 MCM-L采用多层印制电路板,生产工艺成熟,成本 低廉,但其电性能较差,可靠性不高,在频段较低的民用 产品中应用广泛。

1.1 MCM技术简介[1]

多芯片组件(Multi-Chip Module,简称为MCM)技术 是继表面安装技术(SMT)之后,日益兴起的一种高密度封 装技术。 其核心是将多个裸芯片在水平方向上通过较短的布线 连接,在垂直方向上使用金属化通孔连接,从而实现组件 的高密度组装。其基本结构如图1-1所示。 MCM最突出的特点就是高密度集成,并以实现高速 度、高可靠性、低成本和多功能为目标。

《LTCC元器件基础》课件

它是一种高性能、高可靠性的电 子元器件,广泛应用于航空航天 、军事、通信、汽车电子等领域 。

LTCC特点

01

02

03

04

高频性能优异

LTCC材料具有较低的介电常 数和介质损耗,适用于高频电

路。

集成度高

可以实现多层电路集成,减小 了元器件体积,提高了电路密

度。

可靠性高

LTCC材料具有较高的热导率 和机械强度,能够承受恶劣环

振荡器

总结词

高频率稳定性、低相位噪声、小型化

详细描述

LTCC振荡器利用低温共烧陶瓷的优良电气性能和多层布线技术,具有高频率稳定性和低相位噪声。此 外,LTCC振荡器可以实现小型化,广泛应用于各种通信系统和频率计量等领域。

04

LTCC元器件应用案例

手机中的LTCC元器件应用

总结词:小型电常数、低损耗、高稳定性

详细描述

LTCC电容器利用低温共烧陶瓷的优良介电性能,具有高介电常数和低损耗的特点 。这使得LTCC电容器具有高稳定性,能够满足各种高频、高稳定性的应用需求。

滤波器

总结词

高频率选择性、低插入损耗、小型化

详细描述

LTCC滤波器采用多层布线技术和低温 共烧陶瓷的高Q值特性,具有高频率 选择性和低插入损耗。此外,LTCC滤 波器可以实现小型化,方便集成到无 线通信等系统中。

航天器中的LTCC元器件应用

总结词:高精度、高稳定性、轻量化

航天器中使用的LTCC元器件需要具备高精度和高稳定性的特性,以确保航天器的安全和可靠性。LTCC技术在航天器中应用广 泛,如微波组件、天线、滤波器等。

05

LTCC元器件发展趋势与挑战

LTCC元器件发展趋势

01

低温共烧多层陶瓷技术特点与应用

低温共烧多层陶瓷技术特点与应用低温共烧多层陶瓷(Low Temperature Co-fired Ceramic,LTCC)是一种先进的电子封装技术,其特点是可以在低温下完成陶瓷的共烧,以实现多层陶瓷的制作。

LTCC技术具有许多优点,使得它在电子封装领域得到广泛应用。

首先,LTCC技术具有良好的耐高温性能。

LTCC陶瓷可以在高温环境下长时间稳定工作,通常可以耐受高达600℃的温度。

这使得LTCC在一些需要高温运行的应用中非常有用,比如汽车电子、航空航天等领域。

其次,LTCC技术具有优异的机械性能。

LTCC陶瓷具有高硬度、高强度和低热膨胀系数等特点,可以有效抵抗机械应力和热应力,从而保证器件长时间的可靠工作。

另外,LTCC技术还具有优异的电学性能。

LTCC陶瓷具有低介电常数和低损耗因子等特点,可以有效降低信号衰减和串扰,提高信号传输的品质。

在应用方面,LTCC技术已经被广泛应用于电子封装领域,特别是微波器件、射频器件和传感器等高频应用。

在微波器件方面,LTCC技术可以实现高可靠性的微波滤波器、耦合器、功分器等器件的制造。

利用LTCC的低介电常数和低损耗因子,可以实现微波信号的高效传输和处理,提高系统的性能。

在射频器件方面,LTCC技术可以制造高性能的射频滤波器、功放、天线等器件。

利用LTCC的优异机械性能和电学性能,可以实现射频信号的高稳定性和高可靠性传输,从而提高通信系统的性能。

在传感器方面,LTCC技术可以制造高灵敏度、高稳定性的物理传感器、化学传感器和生物传感器等器件。

利用LTCC的优异的电学性能和化学稳定性,可以实现对物理量、化学量和生物分子等的高效检测和分析。

此外,LTCC技术还可以应用于医疗器械、能源管理、光电子器件等领域。

在医疗器械方面,LTCC技术可以制造高灵敏度、高稳定性的生物传感器和医用射频器件等;在能源管理方面,LTCC技术可以制造高效的功率传输器件和能源存储器件;在光电子器件方面,LTCC技术可以制造高性能的光电子器件和光通信器件。

LTCC技术技术及其应用

三、 LTCC中的工艺流程

流延 裁片 冲孔 填孔 印刷 叠片 静压 切割 烧结 调阻 测试

目的:将坯料切割成一定尺寸的陶瓷薄片,每一片将成为多层 陶瓷基板的一层。过程中,对流延不良的薄片进行剔除。

切刀

生陶瓷

三、 LTCC中的工艺流程

流延 裁片 冲孔 填孔 印刷 叠片 静压 切割 烧结 调阻 测试

刮刀 浆料 印刷网版

多孔台板 特制纸

真空吸引

三、LTCC中的工艺流程

流延 裁片 冲孔 填孔 印刷 叠片 静压 切割 烧结 调阻 测试

目的:使用丝网印刷方法,将导电浆料或介质材料印刷在陶瓷片上,用 以制作电气互联的导线及印制元器件(电阻、电容、压敏电阻等)。

三、LTCC中的工艺流程

流延 裁片 冲孔 填孔 印刷 叠片 静压 切割 烧结 调阻 测试

LTCC布线材料

对金属材料有如下要求 金属粉的物理性质适于丝网漏印细线和填满通孔; 浆料与基板生片粘合剂的有机体系兼容; 金 属粉末的烧结行为与基板生料的烧结行为匹配, 控制收缩达到好的面间整体性,烧结时的收缩差 异不能造成基板变形; 烧结后的导带有高的电导率 。

LTCC布线材料

方法:激光脉冲加热

三、LTCC中的工艺流程

流延 裁片 冲孔 填孔 印刷 叠片 静压 切割 烧结 调阻 测试

目的:产品加工过程中,对质量进行监察,避免不良品流入下道工序。 主要包括外观检查、电气特性测量、内部结构检查。

方法:光学检测 探针测试 X光检测 自动光学检测系统可检缺陷包 括: 过焊、缺焊、污迹、线宽过窄、 鼠啮、通孔、污染物、印制漂 移、基板收缩、丝网老化等, 同时系统还可分辨随机缺陷和 系统缺陷。

方法1:光学检测

三、LTCC中的工艺流程

LTCC的概念低温共烧陶瓷

LTCC的概念低温共烧陶瓷LTCC(Low Temperature Co-fired Ceramic)是一种低温共烧陶瓷技术,用于制造多层陶瓷板(MLCC)和射频模块(RF Module)等微电子器件。

LTCC技术以其优异的电性能、热性能和机械性能,成为了电子器件封装技术领域中的重要技术之一LTCC技术的核心在于材料的成分和共烧工艺的控制。

LTCC材料主要由陶瓷粉体、玻璃粉体和有机添加剂等组成。

这些粉体经过共烧过程,形成致密的陶瓷结构,其中陶瓷相和玻璃相具有不同的性质,以满足不同的应用需求。

共烧工艺包括成形、裁切、粘贴、层压和共烧等步骤,要求温度控制和气氛控制等因素,以确保陶瓷板具有良好的性能和可靠性。

LTCC技术具有许多优势。

首先,LTCC材料具有优异的介电性能,能在高频率下传输信号,且具有较低的介电损耗。

而且LTCC材料还具有良好的热导率和热稳定性,能够在高温环境下工作。

其次,LTCC制造工艺相对简单,可以实现高度集成和微型化。

它可以在一块陶瓷板上制造出多个电路和部件,减少了连接线的长度和功耗,提高了可靠性和效率。

此外,LTCC材料可与金、银等导电材料粘接,在电路板上制造导线和元件,从而实现高度集成。

LTCC技术已广泛应用于电子通信、汽车、医疗、物联网和航天等领域。

在电子通信领域,LTCC技术可以制造高速率的射频滤波器和耦合器,用于无线通信和卫星通信等应用。

在汽车领域,LTCC技术可以制造汽车电子模块,如发动机控制单元(ECU)、车载导航系统和胎压监测系统等。

在医疗领域,LTCC技术可以制造医疗传感器、无线医疗设备和植入式医疗器械等。

在物联网领域,LTCC技术可以制造智能家居设备、智能穿戴设备和智能监控设备等。

在航天领域,LTCC技术可以制造高温和高频率下工作的射频模块和元件。

虽然LTCC技术具有众多的优点,但也存在一些挑战和局限。

首先,LTCC材料的陶瓷粉体和玻璃粉体的选择和制备对材料的性能有重要影响。

低温共烧多层陶瓷技术特点与应用

低温共烧多层陶瓷技术特点与应用

1.技术特点:

(1)低温共烧:LTCC技术能够在较低的温度下进行烧结,通常在

850°C-900°C之间,相对于传统的高温烧结工艺,降低了能源消耗。

(2)多层结构:LTCC技术可以制作多层结构的封装材料,每一层都可

以设计电路线路和电器元件的连接点。

(3)绝缘性能:LTCC材料具有良好的绝缘性能,可以避免电路线路之

间的干扰,提高电路的可靠性。

(4)低介电损耗:LTCC材料的介电损耗较低,可以在高频电路中保持

较高的信号传输质量。

(5)高温稳定性:LTCC材料在高温条件下具有良好的稳定性,可以应

用于高温环境下的电子封装。

2.应用:

(1)射频模块:由于LTCC材料具有较好的高频性能,能够在高频范围

内传输信号,因此应用于射频模块的制作中,如天线模块、射频滤波器等。

(2)传感器:LTCC材料具有高温稳定性和良好的绝缘性能,适用于制

作各种传感器,如温度传感器、湿度传感器等。

(3)多层电路板:由于LTCC技术可以制作多层结构,可以用来制作多

层电路板,实现高密度的线路连接。

(4)微波封装:由于LTCC材料在高温下具有良好的稳定性和低介电损

耗的特点,可以应用于微波封装中,如滤波器、功率放大器等。

(5)模组封装:LTCC技术可以制作复杂的三维结构,可以用于模组封装,如无线通信模块、传感器模块等。

总之,低温共烧多层陶瓷(LTCC)技术以其低温烧结、多层结构、良好

的绝缘性能和高温稳定性等特点,被广泛应用于电子封装领域,为高性能、高密度的电子器件提供了一种可靠的封装材料。

19低温共烧陶瓷(LTCC)技术

低温共烧陶瓷(LTCC)技术郁建元李悦(唐山学院,河北唐山063000)摘要主要概述了低温共烧陶瓷(Low Temperature Co-fired Ceramics,简称LTCC)材料的应用和研究现状。

作为一种新兴的集成封装技术,低温共烧陶瓷(LTCC)技术以其优良的高频和高速传输特性、小型化、高可靠而备受关注。

关键词LTCC技术材料特性发展趋势Low Temperature Co-fired Ceramic (LTCC) TechnologyYU Jianyuan Li Yue(Tangshan College, the Department of Environmental and Chemical Engineering,Tangshan, 063000)Abstract: This paper reviews the application and research progress of low temperature co-fired ceramics (LTCC) materials.As a new integrating and packing technology, the low temperature co-firedceramic (LTCC) technology attracts close attention for its excellent high frequency and high speedtransfer characteristics, miniaturization, high reliability.Key words: LTCC technology, material characteristics, development低温共烧陶瓷是与高温共烧陶瓷(High Temperature Co-fired Ceramics, 简称HTCC)相对而言的。

LTCC(低温共烧陶瓷)

发 展 的 需

要 。 虽 然 钽

原料稀缺 , 电容价 格较 昂贵 , 由于大量采 用高 比容钽粉 钽 但

(0 u .— O u . /) 并对 电容器制造工 艺进行 了改进和 3 K FgI K F Vg , O 完 善, 电解 电容器 得到迅速发展 , 钽 使用范 围 日益 广泛 。

目前 生产 的钽 电解 电容 器主 要有 烧 结型 固体 、 箔形

在生 瓷带上 利用激光打孔 、 孔注 浆、 微 精密导体浆料 印刷 等 用金属 薄膜 电容 ;Y 电容是 分别跨接在 电力线两线和 地之 工艺制 出所 需要的 电路 图形 , 并将 多个无源元件 ( 如低 容值 间 (— N— )的电容 , LE' E 一般是 成对 出现 。基 于漏 电流 的 限 Y电容值 不能太大 , 一般 X电容是 u F级, Y电容是 n F 电容 、 电阻 、 滤波器 、 阻抗转换器 、 耦合器等 ) 埋入 多层 陶瓷 制 , 基板 中, 然后叠压在一起 。 内外 电极可分别使用银 、 金等 级 。X电容 抑制差模干扰 , 铜、 Y电容抑制共模干 扰 。 圃

E ii EW I (

邈子西科

金 属 ,在 9 0C下烧 结 ,制 成三维 空间互 不干 扰 的高密度 0 ̄ 电路 ,也可 制成 内置 无源元件 的三维 电路基板 ,在 其表面

可 以贴装 l C和有源 器件 , 制成无源/ 有源集成 的功能模 块 ,

可进一步将 电路小型化 与高密度化 ,特别适 合于高频通 讯

需要的信 号能量,可 以使用 片式 磁珠扮演 高频 电阻 的角色

应 了 目前 电 子技 术 自动

化 和 小 型 化

( 衰减器 ) 器件将 允许 直流信号通过 , , 而滤 除交流信号 。铁 氧 体磁珠 (ereB a )q 目前应用发展 很快 的一种抗干 F rt e d ̄ 是 i 扰 组件 , 廉价 易用 , 除高频噪声效果显著 。 滤

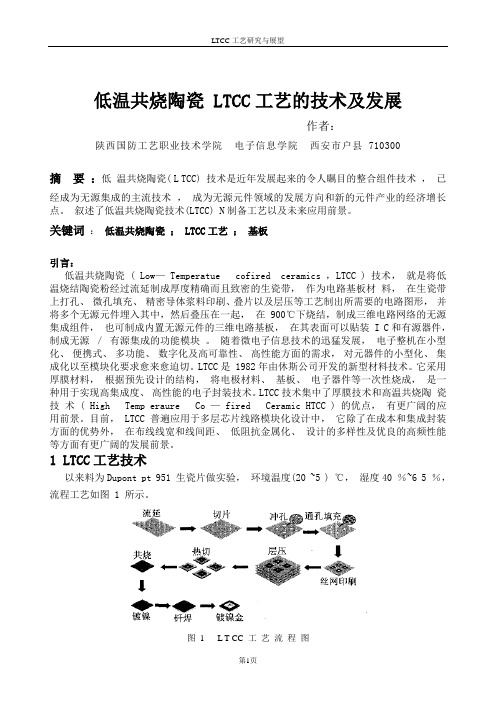

低温共烧陶瓷 LTCC工艺的技术及发展

低温共烧陶瓷 LTCC工艺的技术及发展作者:陕西国防工艺职业技术学院电子信息学院西安市户县 710300摘要:低温共烧陶瓷( L TCC) 技术是近年发展起来的令人瞩目的整合组件技术,已经成为无源集成的主流技术,成为无源元件领域的发展方向和新的元件产业的经济增长点。

叙述了低温共烧陶瓷技术(LTCC) N制备工艺以及未来应用前景。

关键词:低温共烧陶瓷; LTCC工艺;基板引言:低温共烧陶瓷 ( Low— Temperatue cofired ceramics ,LTCC ) 技术,就是将低温烧结陶瓷粉经过流延制成厚度精确而且致密的生瓷带,作为电路基板材料,在生瓷带上打孔、微孔填充、精密导体浆料印刷、叠片以及层压等工艺制出所需要的电路图形,并将多个无源元件埋入其中,然后叠压在一起,在900℃下烧结,制成三维电路网络的无源集成组件,也可制成内置无源元件的三维电路基板,在其表面可以贴装 I C和有源器件,制成无源/有源集成的功能模块。

随着微电子信息技术的迅猛发展,电子整机在小型化、便携式、多功能、数字化及高可靠性、高性能方面的需求,对元器件的小型化、集成化以至模块化要求愈来愈迫切。

LTCC是 1982年由休斯公司开发的新型材料技术。

它采用厚膜材料,根据预先设计的结构,将电极材料、基板、电子器件等一次性烧成,是一种用于实现高集成度、高性能的电子封装技术。

LTCC技术集中了厚膜技术和高温共烧陶瓷技术 ( High Temp eraure Co — fired Ceramic HTCC ) 的优点,有更广阔的应用前景。

目前, LTCC 普遍应用于多层芯片线路模块化设计中,它除了在成本和集成封装方面的优势外,在布线线宽和线间距、低阻抗金属化、设计的多样性及优良的高频性能等方面有更广阔的发展前景。

1 LTCC工艺技术以来料为Dupont pt 951 生瓷片做实验,环境温度(20 ~5 ) ℃,湿度40 %~6 5 %,流程工艺如图 1 所示。

低温共烧陶瓷(LTCC)封装

摘要:低温共烧陶瓷(Low Temperature Co-Fired Ceramics, LTCC )封装能将不同种类的芯片等元器件组装集成于同一封装体内以实现系统的某些功能,是实现系统小型化、集成化、多功能化和高可靠性的重要手段。

总结了LTCC 基板所采用的封装方式,阐述了LTCC 基板的金属外壳封装、针栅阵列( Pin Grid Array, PGA)封装、焊球阵列(Ball Grid Array,BGA )封装、穿墙无引脚封装、四面引脚扁平(Quad Flat Package, QFP )封装、无引脚片式载体(Leadless Chip Carrier, LCC )封装和三维多芯片模块(Three-Dimensional MulTIchip Module, 3D-MCM )封装技术的特点及研究现状。

分析了LTCC 基板不同类型封装中影响封装气密性和可靠性的一些关键技术因素,并对LTCC 封装技术的发展趋势进行了展望。

1 引言便携式通讯系统对电子产品的需求和对电子整机高性能的要求极大地推动着电子产品向小型化、集成化、多功能、高频化和高可靠性等方向发展,同时也带动了与之密切相关的电子封装技术的发展。

电子封装技术直接影响着电子器件和集成电路的高速传输、功耗、复杂性、可靠性和成本等,因此成为电子领域的关键技术。

在摩尔定律继续发展面临来自物理极限、经济限制等多重压力的现实下,以超越摩尔定律为目标的功能多样化成为集成电路技术发展的主要方向之一,迫使人们将整机产品性能的提高更多地转向在封装内实现多种功能集成的系统产品和封装中功能密度的提高。

电子封装按照所使用的封装材料来划分,分为金属封装、陶瓷封装和塑料封装。

金属封装气密性好,不受外界环境因素的影响,但价格昂贵,外型灵活性小,不能满足半导体器件快速发展的需要;塑料封装以环氧树脂热固性塑料应用最为广泛,具有绝缘性能好、价格低、质量轻等优点,性价比最高,但是气密性差,对湿度敏感,容易膨胀爆裂;陶瓷封装可与金属封装一样实现气密性封装,具有气密性好、绝缘性能好、热膨胀系数小、耐湿性好和热导率较高等特点,但也有烧结精度波动、工艺相对复杂、价格贵等不足。

LTCC技术综述11LTCC概述111LTCC性能特点低温共烧

第一部分LTCC技术综述1.1 LTCC概述1.1.1 LTCC性能特点低温共烧陶瓷(Low Temperature Co-fired Ceramics,LTCC)是1982年由美国休斯公司开发的新型材料技术。

它采用低温烧结陶瓷粉料(800℃~900℃),根据预先设计的结构,通过流延工艺将陶瓷浆料制成厚度精确且致密的生瓷带,在生瓷带上利用激光打孔、微孔注浆、精密导体浆料印刷等工艺形成金属化布线和通孔金属化制成所需要的电路图形,然后将电极材料(Au、Ag、Ag/Pd和Cu)、基板、电子器件(如低容值电容、电阻、滤波器、阻抗转换器、耦合器等)等叠片后,在1000℃以下一次性烧成多层互连三维电路基板,在其表面可以贴装IC 和有源器件,制成无源/有源集成的功能模块。

是一种用于实现高集成度、高性能的电子封装技术[1-4]。

传统基板材料如Al2O3、SiC等和高温烧结陶瓷HTCC烧结技术,不仅烧结温度高(>1500℃,只能与高熔点、高电阻的金属Mo、W等共烧),而且不利于降低生产成本。

而低温共烧陶瓷LTCC技术,其低烧结温度可使金属良导体Cu、Ag等同生坯片共烧,提高厚膜电路的导电性能[5]。

因LTCC多层基板技术,能将部分无源元件集成到基板中,有利于系统的小型化,提高了电路的组装密度和系统的可靠性。

与其它集成技术相比,LTCC具有以下几个特点:(1)多层互连,提高了模块可靠性,减少了体积;内埋无源元件,提高电路的组装密度;一次烧结成型,印制精度高,多层基板生瓷带可进行逐步检查,有利于生产效率提高,降低成本,适应批量生产。

(2)LTCC基板材料,介电常数较小(一般ε≤10),有非常优良的高频特性。

(3)适应大电流及耐高温要求,比普通PCB电路基板具有优良的热传导性。

(4)具有较好的温度特性,如较小的热膨胀系数(CTE),较小的共振频率温度系数(η),是多芯片组装MCM首选多层基板,可以制做多达几十层电路基板。

低温共烧陶瓷(LTCC)配套浆料和相关材料开发与应用方案(一)

低温共烧陶瓷(LTCC)配套浆料和相关材料开发与应用方案一、实施背景随着电子产业的快速发展,低温共烧陶瓷(LTCC)技术以其高密度、高可靠性和低成本等优势,广泛应用于电子封装、基板制造等领域。

然而,当前LTCC 材料体系不够完善,配套浆料及相关材料存在较大的提升空间,制约了LTCC 技术的进一步发展。

因此,开展LTCC 配套浆料和相关材料的开发与应用研究,对于推动电子产业升级具有重要意义。

二、工作原理LTCC 配套浆料和相关材料开发与应用方案的工作原理主要包括两个方面:一是通过优化材料配方,提高LTCC 材料的性能;二是通过改进生产工艺,实现LTCC 材料的规模化生产。

首先,针对LTCC 材料的性能提升,我们将采用特种陶瓷粉体、有机载体、添加剂等原料,通过精细研磨、调配、改性等工艺手段,制备出高性能的LTCC 浆料。

该浆料具有高粘度、高稳定性、高浸润性等优点,能够满足不同应用场景的需求。

其次,针对LTCC 材料的规模化生产,我们将引进先进的流延机、烧结炉等设备,建立自动化生产线。

通过优化工艺参数,实现LTCC 材料的快速制备和高效烧结。

此外,我们还将建立完善的质量控制体系,确保产品的稳定性和一致性。

三、实施计划步骤1.材料配方研究:开展特种陶瓷粉体、有机载体、添加剂等原料的研究,优化材料配方,制备出高性能的LTCC 浆料。

2.生产工艺研究:引进先进的流延机、烧结炉等设备,建立自动化生产线,优化工艺参数,实现LTCC 材料的快速制备和高效烧结。

3.产品应用研究:与电子封装、基板制造等领域的企业合作,开展LTCC 材料的实际应用研究,探索其在实际生产中的应用潜力。

4.成果转化推广:将研究成果转化为实际生产力,推广至电子产业领域,促进电子产业的升级发展。

四、适用范围本方案适用于电子封装、基板制造等领域的企业,旨在提供高性能、低成本的LTCC 材料解决方案。

通过本方案的实施,企业可以提高产品性能、降低生产成本、缩短研发周期,提升市场竞争力。

低温共烧多层陶瓷(LTCC)技术特点与应用

低温共烧多层陶瓷(LTCC)技术特点与应用什么是低温共烧多层陶瓷(LTCC)技术低温共烧多层陶瓷(Low Temperature Co-fired Ceramics,简称LTCC)是一种多层陶瓷电子制造技术,利用多种陶瓷材料加上陶瓷压块工艺及精密印刷工艺,制造出三维结构的电子器件。

通常情况下,制造出的器件包括滤波器、天线、功分器等。

LTCC技术特点1. 低温加工LTCC技术最显著的特点就是低温加工。

相对于传统的陶瓷加工工艺,LTCC技术在加热工艺上,降低了材料烧结温度。

一方面可以避免因高温引起的压块变形,另一方面可以增加烧结的材料种类,使制造出来的多层陶瓷具有更细致的复杂结构。

2. 极好的高频特性LTCC技术的另一个特点就是其极好的高频特性。

由于使用多种陶瓷材料,并在制造的时候使用了精密印刷技术,所以制造出来的器件具有微小、高精度的电线结构,从而保证器件的散热性能。

因此,LTCC器件在高频电路中的应用越来越普遍。

3. 可实现三维结构LTCC技术制造出来的器件不仅可以使用二维板材制造,还可以实现三维结构,提高了器件性能,扩大了器件应用范围。

4. 耐高温性除了具有很好的高频特性,由于使用了多种陶瓷材料,所以LTCC器件具有更高的耐高温性能。

LTCC技术的应用1. 无线通讯领域LTCC技术可以制造出一些在无线通讯领域中必不可少的器件,比如天线和滤波器等,这些器件在高温环境下仍能保持稳定的性能。

2. 汽车电子领域LTCC技术常被应用于汽车电子领域的压力、流量、温度传感器、发动机管理、驾驶辅助系统等方面。

其中, LTCC技术制造的传感器具有优异的高温性能,稳定性和可靠性。

3. 医疗器械领域LTCC技术可以制造出高精度的医疗器械,如血糖测量器、医用颗粒计量等等,这些器械具有微小、精密、高精度、高可靠性等特点,可以帮助医疗领域更好地实现无损诊断和治疗。

结论总体来说,低温共烧多层陶瓷(LTCC)技术具有低温加工、极好的高频特性、实现三维结构和耐高温等特点。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

单芯片模块技术尚未实用化之前,被动元件在成本及特性的因素下,无法完全整合于IC内,必须利用外接的方式来达到功能模块,但是因为在功能模块上所使用的被动元件数目相当多,容易造成可靠度低、高生产成本及基板面积不易缩小等缺点,所以利用低温共烧多层陶瓷(Low-Temperature Co-fired Ceramics;LTCC)技术来克服上述的缺点。

低温共烧陶瓷以其优异的电子、机械、热力特性,已成为未来电子元件积集化、模块化的首选方式,在全球发展迅速,目前已初步形成产业雏形。

低温共烧陶瓷技术成被动元件显学低温共烧多层陶瓷技术提供了高度的主动元件或模块及被动元件的整合能力,并能到模块缩小化及低成本的要求,可以堆叠数个厚度只有几微米的陶瓷基板,并且嵌入被动元件以及其它IC,所以近年来LTCC是被动元件产业极力开发的技术。

低温共烧多层陶瓷技术是利用陶瓷材料作为基板,将低容值电容、电阻、耦合等被动元件埋入多层陶瓷基板中,并采用金、银、铜等贵金属等低阻抗金属共烧作为电极,再使用平行印刷来涂布电路,最后在摄氏850-900度中烧结而形成整合式陶瓷元件。

除了芯片、石英震荡器、快闪存储器以及大电容和大电阻之外,大多数的被动元件及天线都能采用低温共烧多层陶瓷(LTCC)技术来将元件埋入基板,容易的地将被动元件与电路配线集中于基板内层,而达到节省空间、降低成本的SoP(System on Package)目标,开发出轻、薄、短、小及低成本的模块。

图2:利用多层多成分陶瓷的共烧而实现被动元件集成电子元件的模块化已成为产品必然的趋势,尤其以LTCC技术生产更是目前各业者积极开发的方向。

目前可供选择的模块基板包括了LTCC、HTCC(高温共烧陶瓷)、传统的PCB 如FR4和PTFE(高性能聚四氟已烯)等。

不过由于HTCC的烧结温度需在1500℃以上,而所采用的高熔金属如钨、钼、锰等导电性能较差,所以烧结收缩并不如LTCC易于控制,但是,HTCC也不是全无优点,表1、表2为高温共烧陶瓷多层基板的一些优点。

HTCC是一种成熟技术,产业界已对材料和技术已有相当的了解。

并且,氧化铝的机械强度比LTCC介质材料的机械强度高得多,可使封装较牢固和更持久。

此外,氧化铝的热导率比LTCC介质材料的热导率几乎要高20倍。

在介电损耗方面,RF4要比LTCC来的高,而虽然PTFE的损耗较低,但绝缘性却不如LTCC。

所以LTCC比大多数有机基板材料提供了更好地控制能力,在高频性能、尺寸和成本方面,比较之下LTCC比其它基板更为出色。

利用LTCC技术开发的被动元件和模块具有许多优点,包括了,陶瓷材料具有高频、高Q特性;LTCC技术使用电导率高的金属材料作为导体材料,有利于提高电路系统的质量;可适应大电流及耐高温特性要求,并具备比普通PCB电路基板优良的热传导性;可将被动元件嵌入多层电路基板中,有利于提高电路的组装密度;具有较好的温度特性,如较小的热膨胀系数、较小的介电常数温度系数,可以制作层数极高的电路基板,可以制作线宽小于50μm 的细线结构。

LTCC封装业者对于线宽的发展也相当的积极,例如,日本KOA利用喷墨技术将含有银的材料将图案印刷到绿色薄片上,然后进行烧结来以达到20μm的线和线距。

所以包括日本、美国等大厂,例如Kyocera、Soshin、TDK、Dupont、CTS、NS等业者对于LTCC(多层低温共烧陶瓷)的开发都相当积极,另外也有部份业者建构LTCC的绕线布局设计软件及资料库,相信未来低温共烧多层陶瓷(LTCC)技术将会是甚被期待的被动元件技术之一。

材料的选用关系著LTCC的优劣高频化是数码3C产品发展的必然趋势。

就像目前第三代移动通信系统的频率高达2GHz 左右。

这对于对陶瓷材料来说,如何适应高工作频率是一个严苛的挑战。

因此,陶瓷材料必须提供良好高频特性以及工作频率的功能,所以微波介质陶瓷材料及新型微波元件是积极被开发的课题。

例如开发适合应用于微波应用的低损耗、温度稳定的电介质陶瓷材料,可以被应用在微波谐振器、滤波器、微波电容器以及微波基板等等。

所以求高介电常数、高质量、低频率温度系数是目前微波介质陶瓷材料研究的重点。

介电常数是LTCC材料最关键的性能。

目前,LTCC技术最常被应用于手机的射频系统上,而谐振器的长度与材料的介电常数的平方根是成反比,所以当元件的工作频率较低时,如果使用低介电常数的材料,那么谐振器的长度就长得无法接受。

介电损耗也是射频元件设计时一个重要参数,直接与元件的损耗相关,所以当然期望材料介电损耗能越小越好。

日本积极发展不同介电常数材料堆叠在生产的技术上,目前,大部分在基板上都是堆叠相同介电常数的基板。

但是已经开始有业者尝试著将不同的材料或者将磁性材料堆叠在一起,也就是意味著,将不同介电常数的基板堆叠在一起。

例如,在DC-DC Converter的模块中,堆叠了磁性材料后就可以形成一个1.5μH电感,然后再加上一个MOSFET后就可以完成一个单芯片的DC-DC Converter,并且降低Converter的体积。

就像Panasonic试著在LTCC层之间注入磁性剂,借以形成电感,而日立金属也正发展这方面的技术。

而共烧不同特定介电常数的材料这一方面,期望在单一模块中封装两个不同特性的元件,例如Soshin Electric堆叠介电常数为25和81的材料,来将滤波器和平衡/Balum封装在同一个模块之内。

但是堆叠不同介电常数或磁性材料还有一些技术上的问题需要克服。

例如陶瓷在烧结期间的缩小变化。

一般来说,利用LTCC技术的陶瓷材料缩小率大概在1520%左右,但是,如果在堆叠不同材料之后,在烧结的过程中,这些不同介电常数材料会出现不同的缩小率,使得烧结后模块会产生变形的现象。

除了缩小率之外,膨胀系数也是一个问题,系数不同材料,在烧结过程中当然会出现不同的膨胀现象,同样的,也会使得烧结后模块会产生变形甚至于失败的现象。

图3:陶瓷介质、铁氧体共烧系统的烧结收缩速率曲线和收缩曲线。

(资料来源:北京清华大学材料科学与工程系实验室)另外,开发出高介电常数的材料也是业界努力的另一个方向。

由于采用高介电常数的材料可以提高电容量,以目前来说,使用介电常数100左右的材料,所内建的只有电容量大概几百个pF,但是如果使用介电常数1000的材料,可以将电容量提高到0.01μF以上。

LTCC的TCE值较接近矽和砷化镓射频元件电性能的温度稳定性是取决于材料的温度系数,为了保证利用LTCC技术生产元件的可靠性,所以在进行材料选择时,必须考虑到耐热性能力,其中最关键的是热膨胀系数,需要尽可能与基板相匹配。

此外,考虑到加工及以后的应用,LTCC材料还要满足多项机械性能的要求,例如弯曲强度、硬度、表面平整度、弹性模量及断裂韧性等等。

图4是IC封装的各种材料的热膨胀系数,可以发现LTCC、氧化铝和其它陶瓷封装的TCE 接近Si、砷化镓以及磷化铟的TCE值,而有机印制电板路材料的TCE值都比Si、砷化镓高出很多。

图4:用于IC制造、封装和连接材料的TCE与矽和砷化镓的TCE值相接近的材料,可以减小机械应力、而可以应用在尺寸较大的芯片,不必使用有机叠层。

减小热不匹配性还可以增强机械的整体性,降低温度特性的变化,以及增加类比、数码和光学、电子技术的集成能力。

图5则是比较了陶瓷和有机印制电路板材料的热导率。

可以发现,陶瓷材料的热导率都很高,其中氧化铝基板的热导率是PCB有机材料的100倍,LTCC材料的热导率是有机叠层的20倍。

热导率越高,可以简化散热设计,进而提高电路的寿命和可靠性。

目前有许多光学元件要求气密性封装且热性能好,但传统的气密性封装技术成本相当高,而要结合陶瓷材料的低温共烧技术,具有成本低廉的优势,可以取代传统的气密性封装,并达到高可靠性。

图5:陶瓷和有机PCB材料的导热率LTCC需面对的问题制作生产过程中,还必须注意的要点包括了,必须在900℃以下的温度下烧结成致密、无气孔的结构;致密化温度不能太低,以免阻止银浆材料和有机物的排出;加入适当有机材料后可流延成均匀、光滑、有一定强度表面。

但是就基板材料而言,LTCC技术并非是业者唯一的选择,由于LTCC是利用烧结陶瓷材料制作,所以耐冲击的能力上也就出现了一些问题,例如基板太薄时容易破裂等,但是为了提高抗冲击而将基板面积做得较小时,那么被设计在其中的元件数量也就随之减少。

例如,当客户要求元件不得超过1.2平方毫米时,封装生产业者或许就会选择高介电常数或Q值的塑料材料。

另外对于产品而言,是否需要如此小的模块面积,也是产品客户的考量,就像在目前面积约为3.2平方毫米的GSM手机天线开关模块中,就包括了34个RF滤波器、阻抗匹配电路及其它功能的几十个零组件。

但是,产品客户未必会花费更多的成本来采用LTCC封装技术,让模块的尺寸再缩小到2平方毫米以内,因为,这与客户所考量的价值性息息相关,与其花费较多的成本只缩小了接近一半模块的面积,倒不如利用这些成本来提高手机的功能性。

LTCC已被积极的应用在各领域由于LTCC是以陶瓷为介电材料,具有高Q值与高频的特性,因而非常适用于高频通讯模块中,LTCC主要用于手机通讯、蓝芽(Bluetooth)、无线网络(WLAN)与全球卫星定位系统(GPS)的产品中。

目前通讯产品中运用LTCC技术制作的整合型元件有功率放大器、天线、滤波器等。

以手机为例,目前每个手机中约有200个以上的被动元件,因此被动元件的小型化决定了手机的轻薄,这样的需求推动了被动电子陶瓷元件的小型化、积集化。

因此使用多元复合、集成化被动元件,使缩小手机体积尺寸,并提高元件密度的最佳解决方案。

因此,多层陶瓷元件正由单一元件朝向复合多元、高集成化趋势发展。

过去,LTCC较常被应用在手机中射频的基板上,利用LTCC技术可以将包括AP、滤波器、微带滤波器、多层天线等等10多个元件整合在几公厘平方的封装之中。

以滤波器为例,由LTCC 制成的滤波器,频率可以从数十MHz直到5.8GHz,再加上LTCC滤波器在体积、价格和温度稳定性等方面有其优势性,所以已经被广泛的使用。

另外一些包括收发前端模块、功率模块和蓝芽模块等,也已成功开发利用LTCC技术将芯片与被动元件积集于同一基板上。

但是,随著加入者数量陆续增加,让市场产生了激烈竞争的现象,使得业者陆续开发更多的应用领域。

目前LTCC技术已经迈入更新的应用阶段,包括了无线区域网络、地面数码广播、全球定位系统接收器模块、数码信号处理器和存储器等等以及其它电源供应模块、甚至是数码电路模块基板。

例如有村田、三菱电工、京瓷、TDK、Epcos、日立、Avx等十多家开发的手机天线开关模块,NEC、村田和易利信等开发的蓝芽模块,都是由LTCC技术制成的。