单片机结构和时序

单片机P0~P3口结构与时序

单片机IO口结构及上拉电阻MCS-51有4组8位I/O口:P0、P1、P2和P3口,P1、P2和P3为准双向口,P0口则为双向三态输入输出口,下面我们分别介绍这几个口线。

一、P0口和P2口图1和图2为P0口和P2口其中一位的电路图。

由图可见,电路中包含一个数据输出锁存器(D触发器)和两个三态数据输入缓冲器,另外还有一个数据输出的驱动(T1和T2)和控制电路。

这两组口线用来作为CPU与外部数据存储器、外部程序存储器和I/O扩展口,而不能象P1、P3直接用作输出口。

它们一起可以作为外部地址总线,P0口身兼两职,既可作为地址总线,也可作为数据总线。

图1 单片机P0口内部一位结构图图2 单片机P2口内部一位结构图P2口作为外部数据存储器或程序存储器的地址总线的高8位输出口AB8-AB15,P0口由ALE选通作为地址总线的低8位输出口AB0-AB7。

外部的程序存储器由PSEN信号选通,数据存储器则由WR和RD读写信号选通,因为2^16=64k,所以MCS-51最大可外接64kB的程序存储器和数据存储器。

二、P1口图3为P1口其中一位的电路图,P1口为8位准双向口,每一位均可单独定义为输入或输出口,当作为输入口时,1写入锁存器,Q(非)=0,T2截止,内上拉电阻将电位拉至"1",此时该口输出为1,当0写入锁存器,Q(非)=1,T2导通,输出则为0。

图3 单片机P2口内部一位结构图作为输入口时,锁存器置1,Q(非)=0,T2截止,此时该位既可以把外部电路拉成低电平,也可由内部上拉电阻拉成高电平,正因为这个原因,所以P1口常称为准双向口。

需要说明的是,作为输入口使用时,有两种情况:1.首先是读锁存器的内容,进行处理后再写到锁存器中,这种操作即读—修改—写操作,象JBC(逻辑判断)、CPL(取反)、INC(递增)、DEC(递减)、ANL(与逻辑)和ORL(逻辑或)指令均属于这类操作。

2.读P1口线状态时,打开三态门G2,将外部状态读入CPU。

8051单片机的内部结构

8051单片机的内部结构8051单片机是一种经典的8位微控制器,因其性能稳定、易于使用和广泛应用于各种嵌入式系统中而备受推崇。

8051单片机采用哈佛架构,具有强大的功能和丰富的内部资源。

本文将详细介绍8051单片机的内部结构。

1.CPU核心:8051单片机核心包括中央处理器(CPU)和一些相关模块,主要包括ALU(算术逻辑单元)和控制单元。

ALU负责执行算术和逻辑运算,而控制单元负责指令译码和控制指令执行。

2.存储器:8051单片机具有多种类型的存储器,包括ROM、RAM和特殊功能寄存器。

- ROM(Read Only Memory):8051单片机的ROM存储器用于存储程序指令,其容量通常为4KB至64KB,并且不可编程。

程序储存在ROM中,在运行时从中读取指令并执行。

- RAM(Random Access Memory):8051单片机的RAM存储器用于存储变量和临时数据。

其容量通常从XDATA的8051型号开始,为128B至256B。

与ROM不同,RAM可读可写,并且容易被程序修改。

-特殊功能寄存器(SFR):8051单片机的特殊功能寄存器是一种特殊的存储器类型,用于存储特定功能的控制和状态信息。

例如,P0(口0)用于控制和监测微控制器的输入/输出。

3.端口:8051单片机包含4个8位双向并行端口(P0-P3),用于与外部设备进行通信。

每个端口都可以配置为输入或输出,并且具有输入缓冲器和输出驱动器。

4. 定时器/计数器:8051单片机具有两个16位定时器/计数器(Timer/Counter 0和Timer/Counter 1)。

它们可用于测量时间间隔、生成定时中断和计数外部事件。

5.串行通信接口:8051单片机具有一个串行通信接口(UART),用于与外部设备进行串行数据传输。

UART可以通过异步串行通信或同步串行通信来传输数据。

6.中断控制器:8051单片机具有中断控制器,用于处理外部中断和内部中断。

第2章 MCS-51单片机结构与时序_110905

2.3.1 运算部件及专用寄存器组

运算部件以算术逻辑单元ALU为核心,包括一个位处理器和 两个8位暂存寄存器(不对外开放),它能实现数据的算术运 算、逻辑运算、位变量处理和数据传输操作。 累加器ACC 寄存器B 专用寄存器组 程序状态字PSW 程序计数器PC 堆栈指针SP 数据指针寄存器DPTR

锁 存 器

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0 VCC VSS

地 址 总 线 (AB)

数 据 总 线 (DB)

VCC VSS

ห้องสมุดไป่ตู้(a)

(b)

MCS-51系列单片机引脚及总线结构

2.3 微 处 理 器

Program State Word

accumulator

ALU --Arithmetic and Logic Unit

图2.1 MCS-51单片机内部结构框图

1.算术逻辑单元ALU与累加器ACC、寄存器B

算术逻辑单元不仅能完成8位二进制的加、减、乘、除、加 1、减1及BCD加法的十进制调整等算术运算,还能对8位变量进 行逻辑"与"、"或"、"异或"、循环移位、求补、清零等逻辑运 算,并具有数据传输、程序转移等功能。 累加器(ACC,简称累加器A,地址E0H)为一个8位寄存器, 它是CPU中使用最频繁的寄存器。进入ALU作算术和逻辑运算的 操作数多来自于A,运算结果也常送回A保存。 寄存器B(地址F0H )是为ALU进行乘除法运算而设置的。 若不作乘除运算时,则可作为通用寄存器使用。

单片机的时钟、时序及复位

四川工程职业技术学院单片机应用技术课程电子教案Copyright © 第讲58051及P89V51RD2单片机的时钟、时序和复位本讲主要内容5-1. 标准80C51的时钟电路、时间单位与时序5-2. P89V51RD2单片机的时钟电路、时间单位与时序5-3. P89V51RD2单片机的复位与复位电路时钟电路——用于产生供单片机各部分同步工作的时钟信号方法1:用石英晶体振荡器方法2:从外部输入时钟信号(80C51)80C51振荡器C1C2CYS80C51悬空外部时钟信号XTAL1XTAL2XTAL2XTAL1单片机内部的时间单位S1S2S3S4S5S6机器周期T CY分频器振荡器晶振周期时钟周期(S 状态)80C51P1P2ALE 信号单片机内部的时间单位✧振荡频率f osc = 石英晶体频率或外部输入时钟频率振荡周期= 振荡频率的倒数✧机器周期机器周期是单片机应用中衡量时间长短的最主要的单位在多数51系列单片机中:1机器周期= 12×1/ fosc✧指令周期——执行一条指令所需要的时间单位:机器周期51单片机中:单周期指令、双周期指令、四周期指令单片机内部的时间单位课堂练习:如果某单片机的振荡频率f=12MHz,则:osc振荡周期=S=mS=uS;机器周期=uS;已知乘法指令“MUL AB”是一条4周期指令,则执行这条指令需要uS;加法指令“ADD A,#01H”是单周期指令,那么1S内该单片机可以进行次加法运算。

单片机内部的时序单片机执行各种操作时,CPU都是严格按照规定的时间顺序完成相关的工作,这种时间上的先后顺序成为时序。

✧单周期指令的操作时序S1S2S3S4S5S61个机器周期P1P2ALE读操作码空读S1S2S3S4S5S61个机器周期P1P2ALE读操作码读第二字节单字节指令双字节指令单片机内部的时序✧双周期指令的操作时序S1S2S3S4S5S6第1机器周期P1P2ALE读操作码空读3次S1S2S3S4S5S6第2机器周期时钟电路✧时钟电路参数:频率范围:0~40MHz C1、C2:20~30pF80C51振荡器C1C2CYSXTAL2XTAL1P89V51RD2的两种时钟模式✧X1模式✧X2模式器件含有一个时钟加倍选项,可以加速器件的运行速度。

单片机的时序

单片机的时序在电子世界中,单片机就像是一个小巧而强大的智慧核心,掌控着各种设备的运行。

而要理解单片机如何准确无误地执行任务,关键就在于掌握它的时序。

什么是单片机的时序呢?简单来说,时序就是单片机在执行指令和操作外部设备时,各种信号在时间上的先后顺序和持续时间。

就好比我们日常生活中的流程,先做什么,后做什么,每个步骤持续多久,都有一定的规律和节奏。

为了更清晰地理解,我们先来看看单片机的内部结构。

单片机内部有中央处理器(CPU)、存储器、输入输出端口等部分。

这些部分之间的协同工作,都依赖于精确的时序控制。

当我们给单片机下达一个指令时,它并不是立刻就能执行的。

首先,指令会被存储在存储器中,然后 CPU 按照一定的节奏从存储器中读取指令,并进行解码和执行。

这个节奏就是由时钟信号来控制的。

时钟信号就像是单片机的心跳,它以固定的频率跳动,决定了单片机每一步操作的时间间隔。

比如,如果时钟频率是 10MHz,那就意味着每秒钟单片机内部会进行 1000 万次的操作。

单片机在与外部设备进行通信时,时序同样至关重要。

以常见的串口通信为例,发送和接收数据都有严格的时序要求。

发送方要按照特定的时间间隔发送数据位,接收方也要在准确的时刻进行采样,才能保证数据的正确传输。

再来说说单片机对存储器的读写操作。

无论是读取程序存储器中的指令,还是读写数据存储器中的数据,都有明确的时序规定。

比如,在读取数据时,需要先发出读信号,然后等待一定的时间,才能获取到稳定有效的数据。

单片机的时序还与指令的执行周期有关。

不同的指令可能需要不同的执行时间。

有些简单的指令可能在一个时钟周期内就能完成,而复杂的指令可能需要多个时钟周期。

在实际的应用中,如果时序出现问题,可能会导致各种错误。

比如,数据传输错误、设备无法正常工作,甚至整个系统崩溃。

为了确保时序的准确性,在设计单片机系统时,我们需要仔细考虑时钟源的选择和配置。

时钟源可以是外部晶体振荡器,也可以是内部的 RC 振荡器。

2.1 89C51单片机的内部结构

4. 数据存储器 (1) 功能: 用于存放运算的中间结果、数据暂存和缓冲、 标志位等。

(2) 编址:

FFH 52子系列才有 FFH

SFR分布在 80H-FFH

其中11个可 位寻址

的RAM区

80H 7FH 80H

普通RAM区

89C51 128字节

30H 2FH 20H 1FH 00H

位寻址区 工作寄存器区

片内RAM前32个单元是工作寄存器区(00H—1FH)

FFH 52子系列才有 的RAM区 1FH 18H 17H 10H 0FH 08H 07H 06H 05H 04H 03H 02H 01H 00H

工作寄存器区3

工作寄存器区2

工作寄存器区1

R7 R6 R5 R4 R3 R2 R1 R0

80H 7FH

2

15

1

5

2/3

32

1

5/6

3. 程序存储器 (1) 功能: 用于存放编好的程序和表格常数。 (2) 编址:

0FFFFH

外部 ROM

1000H 0FFFH 内部 ROM 0000H (EA=1) 外部 ROM (EA=0) 0000H 0FFFH

片内ROM和片外ROM取指的速度相同

0000H 0003H 000BH 0013H 001BH 0023H 002BH

51系列单片机的存储器分为数据存储器和程序存储 器,其地址空间,存取指令和控制信号各有一套。

1. 物理结构

片内程序存储器

程序存储器ROM

89C51存储器

片外程序存储器 片内数据存储器 片外数据存储器

数据存储器ROM

2. 逻辑结构

FFH 特 殊 功 能 寄 存 器 80H 7FH 通用 RAM区 位寻址区 30H 2FH 20H 1FH 0FFFH 工作寄 存器区 0000H 0000H 1000H F0H E0H D0H B8H B0H A8H A0H 98H 90H 88H 80H 特 殊 FFFFH 功 能 寄 存 器 中 位 寻 址 F移位功能;位操作。

单片机的四种基本时序单位

单片机的四种基本时序单位一、时钟周期时钟周期是单片机中最基本的时序单位,它是由晶振产生的稳定的方波信号驱动的。

在一个完整的时钟周期内,单片机的所有操作都会被执行完毕。

时钟周期包括上升沿和下降沿两个阶段,每个阶段都有相应的操作完成。

时钟周期的长短决定了单片机的工作速度,一般用Hertz(赫兹)来表示。

常见的单片机工作频率有8MHz、16MHz等。

时钟周期越短,单片机的运算速度越快,但也会增加功耗和噪声。

二、机器周期机器周期是指单片机执行一条指令所需要的时间。

每个机器周期包含若干个时钟周期,具体数量取决于单片机的架构和指令集。

不同的指令需要的机器周期数不同,一般来说,简单的指令需要较少的机器周期,而复杂的指令需要较多的机器周期。

例如,一条简单的加法指令可能只需要一个机器周期,而一条复杂的循环指令可能需要多个机器周期。

机器周期的长短决定了单片机的指令执行速度,它与时钟周期有一定的关系。

在一个机器周期内,单片机可以执行多个时钟周期的操作,因此机器周期的长短取决于时钟周期的倍数。

三、指令周期指令周期是指单片机执行一条指令所需要的时间,它由若干个机器周期组成。

在一个指令周期内,单片机完成指令的取指、执行、访存和写回等操作。

指令周期的长短取决于机器周期的数量,不同的指令可能需要不同数量的机器周期。

指令周期的长短决定了单片机的指令执行速度,它与机器周期的数量有关。

在一个指令周期内,单片机可以执行多个机器周期的操作,因此指令周期的长短取决于机器周期的数量。

四、机器指令周期机器指令周期是指单片机执行一条机器指令所需要的时间,它由若干个指令周期组成。

在一个机器指令周期内,单片机完成机器指令的取指、执行、访存和写回等操作。

机器指令周期的长短取决于指令周期的数量,不同的机器指令可能需要不同数量的指令周期。

机器指令周期的长短决定了单片机的指令执行速度,它与指令周期的数量有关。

在一个机器指令周期内,单片机可以执行多个指令周期的操作,因此机器指令周期的长短取决于指令周期的数量。

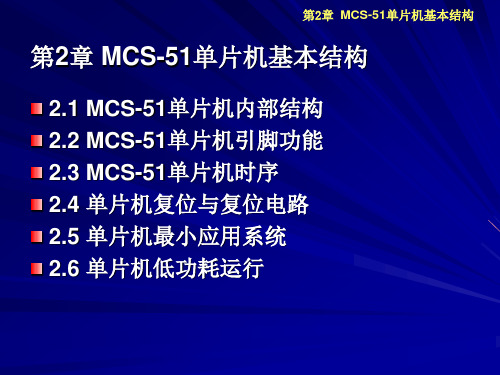

第2章 MCS-51单片机基本结构

第2章 MCS-51单片机基本结构

2.1 MCS-51单片机内部结构 2.2 MCS-51单片机引脚功能 2.3 MCS-51单片机时序 2.4 单片机复位与复位电路 2.5 单片机最小应用系统 2.6 单片机低功耗运行

第2章 MCS-51单片机基本结构

2.1 MCS-51单片机内部结构

第2章 MCS-51单片机基本结构

2.1.2存储器

第2章 MCS-51单片机基本结构

2.1.2存储器

存储器小结:

第2章 MCS-51单片机基本结构

(1)地址的重叠性。数据存储器与程序存储器全 部64K地址重叠;程序存储器中的片内和片外低 4K地址重叠;数据存储器片内和片外最低的128 个字节地址重叠。虽然有这些重叠,但是由于采 取了不同的操作指令和外部引脚电平的控制,是 不会产生操作混乱的。 (2)程序存储器和数据存储器在使用上是严格区 分的,不同的操作指令不能混用。 (3)片外数据存储器中,数据区与用户外部扩展 的I/O口统一编址。因此,应用系统中所有外围接 口的地址均占用RAM地址单元。与外围接口进行 数据传送时,使用与访问外部数据存储器相同的 传送指令。

①CY(Carry Flag)

进位标志位。在执行运算过程中,如果结果的最高位 在加法运算时有进位或减法运算时有借位,Cy=1;否则, Cy=0。在进行位操作时,CY作为位累加器,作用相当于 CPU中的累加器A。

②AC(Auxiliary Carry Flag)

辅助进位标志位。进行加法或减法运算中,若低4位向 高4位有进位或借位,AC将被硬件置1,否则清0。AC位 常用于进行十进制调整指令和压缩BCD码运算。

第2章 MCS-51单片机基本结构

单片机:51单片机的延时及时序分析

计算机工作时,是在统一的时钟脉冲控制下一拍一拍地进行的。

这个脉冲是由单片机控制器中的时序电路发出的。

单片机的时序就是CPU在执行指令时所需控制信号的时间顺序,为了保证各部件间的同步工作,单片机内部电路应在唯一的时钟信号下严格地控时序进行工作,在学习51单片机的时序之前,我们先来了解下时序相关的一些概念。

既然计算机是在统一的时钟脉冲控制下工作的,那么,它的时钟脉冲是怎么来的呢?要给我们的计算机CPU提供时序,就需要相关的硬件电路,即振荡器和时钟电路。

我们学习的8051单片机内部有一个高增益反相放大器,这个反相放大器的作用就是用于构成振荡器用的,但要形成时钟,外部还需要加一些附加电路。

8051单片机的时钟产生有以下两种方法:1. 内部时钟方式:利用单片机内部的振荡器,然后在引脚XTAL1(18脚)和XTAL2(19脚)两端接晶振,就构成了稳定的自激振荡器,其发出的脉冲直接送入内部时钟电路,外接晶振时,晶振两端的电容一般选择为30PF左右;这两个电容对频率有微调的作用,晶振的频率范围可在1.2MHz-12MHz之间选择。

为了减少寄生电容,更好地保证振荡器稳定、可靠地工作,振荡器和电容应尽可能安装得与单片机芯片靠近。

2. 外部时钟方式:此方式是利用外部振荡脉冲接入XTAL1或XTAL2。

HMOS和CHMOS单片机外时钟信号接入方式不同,HMOS型单片机(例如8051)外时钟信号由XTAL2端脚注入后直接送至内部时钟电路,输入端XTAL1应接地。

由于XTAL2端的逻辑电平不是TTL的,故建议外接一个上接电阻。

对于CHMOS型的单片机(例如80C51),因内部时钟发生器的信号取自反相器的输入端,故采用外部时钟源时,接线方式为外时钟信号接到XTAL1而XTAL2悬空。

如下图外接时钟信号通过一个二分频的触发器而成为内部时钟信号,要求高、低电平的持续时间都大于20ns,一般为频率低于12MHz的方波。

片内时钟发生器就是上述的二分频触发器,它向芯片提供了一个2节拍的时钟信号。

单片机的工作时序

单片机的工作时序

单片机是在时钟脉冲的控制下工作的,有的电路来一个时钟脉冲就可完成一次工作,而有的电路需要来多个时钟脉冲才能完成一次工作。

为了方便分析工作时序,单片机中规定了几种周期:时钟周期、状态周期、机器周期和指令周期。

1.时钟周期

时钟周期是指振荡器产生的时钟信号周期,也即时钟振荡频率的倒数。

例如:单片机时钟信号的频率为12MHz,那么时钟周期就为1/12μs。

2. 状态周期

状态周期由两个时钟周期组成,它分为P1节拍和P2节拍,第1个时钟周期为P1节拍,第2个时钟周期为P2节拍。

3.机器周期

单片机在执行指令时,通常把执行过程划分成几个基本的操作,完成一个基本操作所需要的时间称为机器周期。

一个机器周期由6个状态周期,也即12个时钟周期组成。

4.指令周期

指令周期是指执行一条指令所需要的全部时间,它通常为1~4个机器周期。

例如,单片机在执行“MOV A,#C3H”指令时,需要2个机器周期,即24个时钟周期,若时钟周期为1/

12μs,那么执行该指令需要2μs。

单片机第2章

控制器-程序计数器PC(Program Counter)

程序计数器PC The microprocessor ‘keeps its place’ in the program by means of the Program Counter, which always holds the address of the next instruction to be executed. In order to fetch the next instruction, the processor places the value held in the Program Counter on the address bus, and signals through the control lines that it wishes to read data. Memory corresponding to that address will, upon receiving the address and control signals, place the instruction word on the data bus,

程序存储器中保留的用于特定程序入口地址的单元

0000H单元,单片机复位后,PC=0000H,一般放

一条绝对转移指令,使程序转向用户主程序。

因此,0000H-0002H单元被保留用于初始化。 0003H-0032H单元,用于6个中断源的中断服

务程序入口地址。

0003H:外部中断0 000BH:定时器T0溢出中断

which the processor can then read.

As each word is read from program memory, the Program Counter is incremented.

单片机结构(共46张PPT)

8051是MCS-51系列单片机的典型产品, 我们以这一代表性的机型进行系统的讲 解。

➢ 内部结构

➢ 外部引脚 ➢ 工作时序

➢ 实例分析

第1页,共46页。

典型单片机结构

T0 T1

时钟电路 ROM

内部总线 CPU

RAM

定时/计数器

并行接口

串行接口

中断系统

中央处理器 数据存储器(RAM)

输入输出引脚

P1.0

➢ P0:P0.1~P0.7

P1.1

➢ 漏极开路双向I/O

P1.2 P1.3

➢ 一般为数据总线口

P1.4

➢ P1:P1.1~P1.7

P1.5 P1.6

➢ 拟双向I/O通道

➢ P2:P2.1~P2.7

P1.7 RST

RXD/P3.0

➢ 拟双向I/O通道

TXD/P3.1 INT0/P3.2

P3口的第二功能表

I/O口

第二功能

注释

2个定时器T0、T1溢3,.0 然后从中间往两R头X逐D 个灭,周而复始 为1时:负边沿触发中断请求;

串行口数据接收端

分别由8位寄存器TH0、TL0 和 TH1、TL1组成。

else return(0);

28

14

27

15

26

16

25

17

24

18

23

19

22

20

21

第10页,共46页。

V CC P0.0/AD 0 P0.1/AD 1 P0.2/AD 2 P0.3/AD 3 P0.4/AD 4 P0.5/AD 5 P0.6/AD 6 P0.7/AD 7 EA/V PP ALE/PROG PSEN P2.7/A 15 P2.6/A 14 P2.5/A 13 P2.4/A 12 P2.3/A 11 P2.2/A 10 P2.1/A 9 P2.0/A 8

第2章 单片机的内部结构及工作原理

(9)定时器0和定时器1寄存器 TCON:定时器控制寄存器。 TMOD:定时器方式寄存器。 TL0、TH0:定时器0寄存器。 TL1、TH1:定时器1寄存器。 (10)P0~P3端口寄存器 (11)栈指针SP寄存器 栈指针SP寄存器指示出堆栈顶部在内部数据存储器 中的位置。系统复位后,SP初始化为07H,如果不重新 设置,就使得堆栈由08H单元开始。但08H~1FH单元属 于工作寄存器区,所以在程序设计中,最好把SP的值 设置的大一些,一般将堆栈开辟在30H~7FH区域中。 SP的值越小,堆栈容量就越大,但最大为128字节。

专用寄存器(Special Function Registers)也叫特殊功能寄存 器,就是将内部RAM的高128单元作为特殊功能寄存器使用。 其单元地址为80H~FFH。

寄存器 0 F8H F0H E8H E0H D8H D0H C8H C0H B8H B0H A8H A0H 98H 90H

88H 80H

P3口的特殊功能 口的特殊功能

引脚 1(80C52) 2(80C52) 10 11 12 13 14 15 16 17 特殊功能符号 P1.0/ T2 P1.1/ T2 P3.0/ RXD P3.1/ TXD P3.2/ INT0 P3.3/ INT1 P3.4/ T0 P3.5/ T1 P3.6/ WR P3.7/ RD 功能说明 定时/计数器 T2 计数输入端 T2 的捕捉/重新加载的触发输入 串行数据输入端 串行数据输出端 外部中断 0 申请信号 外部中断 1 申请信号 定时/计数器 T0 计数输入端 定时/计数器 T1 计数输入端 外部数据 RAM 写控制信号 外部数据 RAM 读控制信号

单片机引脚

(9)ALE/PROG(30脚):地址锁存允许信号。 有以下三个作用: 当外接存储器(RAM/ROM)时,ALE(允许地 址锁存)的输出用于锁存地址的低8位。一般 ALE接锁存器的EN端。 当没有外部存储器时,ALE端可输出脉冲信号, 此频率为石英振荡频率的1/6。因此,它可用作 对外部芯片提供输出的时钟,或用于定时的目 的。 (10)(29脚):外部程序存储器的读选通 信号

4-5 AT89C52单片机的结构与工作原理

第2章 AT89C52单片机的结构和工作原理

� AT89C52单片机的基本结构 � AT89C52单片机的主要组成部分 � AT89C52单片机的引脚功能 � AT89C52单片机的时钟与复位电路 � AT89C52单片机的低功耗工作方式 � AT89C52单片机的时序

特殊功能寄存器地址分布图

符号 地址 B ACC PSW IP P3 IE P2 SBUF SCON P1 TH1 TH0 TL1 TL0 TMOD TCON PCON DPH DPL SP P0 87 86 85 84 83 82 81 80 8F 8E 8D 8C 8B 8A 89 88 9F 97 9E 96 9D 95 9C 94 9B 93 9A 92 99 91 98 90 F7 E7 D7 B7 AF A7 F6 E6 D6 B6 A6 位 地 址 字节 地址 F1 E1 D1 B9 B1 A9 A1 F0 E0 D0 B8 B0 A8 A0 F0H E0H D0H B8H B0H A8H A0H 99H 98H 90H 8DH 8CH 8BH 8AH 89H 88H 87H 83H 82H 81H 80H

程序状态字PSW

PSW.7 PSW.6 PSW.5 PSW.4 PSW.3 PSW.2 PSW.1 PSW.0

Cy

AC

F0

RS1 RS0

OV

-

P

Cy (PSW.7) 进位标志位 AC (PSW.6) 辅助进位(或称半进位)标志 F0 (PSW.5) 用户标志位 RS1和RS0(PSW.4,PSW.3)工作寄存器组选择位 OV (PSW.2) 溢出标志位 PSW.1 未定义位 P (PSW.0) 奇偶标志位

在指令中可作为转移的条件

第四讲单片机结构-CPU时序

六、CPU时序

计算机在执行指令时, 通常将一条指令分解为 若干基本的微操作, 这些微操作所在时间上都 有严格的先后次序,这些次序就是计算机的时 序。 单片机振荡电路的振荡周期和时钟电路的时钟 周期决定了CPU时序。 振荡周期: 为单片机提供定时信号的振荡源的 周期(晶振周期或外加振荡源周期)。 时钟周期,又称状态周期: 2个振荡周期为1个 状态周期, 用S表示。分为两个节拍,即P1和P2。

读引脚

MOV P0, #0FFH MOV A, P0 作为输入口使用时,必须先向输出锁存器写“1”此时引脚 内部的两个场效应管均截止,读入的信号就是引脚上的信号。 写端口: MOV P0, A

2 P1口

P1口 为 准 双向 口, 其1 位的 内 部结 构 如图 2―8所示。 它在结构上与P0口的区别在于 输出驱动部分, 其输出驱动部分由场效应管 V1与内部上拉电阻组成。 当其某位输出高 电平时, 可以提供拉电流负载, 不必象P0口 , , P0 那样需要外接电阻。 从功能上来看P1只有一种功能(对MCS—51 子系列), 即通用输入输出I/O接口, 具有输 入、输出、 端口操作3种工作方式, 每1位口 线能独立地用作输入或输出线。

七、并行I/O端口

MCS-51单片机的四个并行I/O口,共占32个管理,其 中两个管脚可以作全双工异步串行I/O口。 1.并行I/O端口 P0、P1、P2、P3

都是双向口 都是三态口(高、低、高阻) 输出有锁存、输入有缓冲 都可以作为通用I/O P0口作通用I/O需上拉电阻 都有三种读写方式

写端口、读端口、读引脚

P1口的结构原理图

3 P2口

P2口也是一准双向口, 其1位的内部结构如 图2―9所示。 它具有通用I/O接口或高8位 地址总线输出两种功能, 所以其输出驱动结 构比P1口输出驱动结构多了一个输出模拟转 换开关MUX和反相器3。 MUX 3 当作为准双向通用I/O接口使用时, 控制信号 使转换开关接向左侧, 锁存器Q端经反相器3 接V1, 其工作原理与P1相同, 也具有输入、 输出、 端口操作三种工作方式, 负载能力也 与P1口相同

第2章 AT89S52单片机的片内硬件结构(4)时钟电路时序复位操作

22

23

2.7.2 复位电路设计

复位电路采用上电自动复位和按钮复位两种方式。最简单 的上电自动复位电路。

1.上电自动复位电路 给电容C 充电加给RST引脚一个短

器、内部RAM和SFR中内容均保持进入空闲模式前状态。 2. 空闲模式退出 两种方法退出,

响应中断方式, 硬件复位方式。

35

2.8.2 掉电运行模式 1. 掉电模式的进入 用指令把PCON寄存器的PD位置1,便进入掉电模式。在

掉电模式下,进入时钟振荡器的信号被封锁,振荡器停止 工作。

0 0

33

2.8.1 空闲模式 1. 空闲模式进入 如把PCON中的IDL位置1,则把通往CPU的时钟信号关断,便进

入空闲模式。

0

34 34

2.8.1 空闲模式 虽然振荡器运行,但是CPU进入空闲状态。 所有外围电路(中断系统、串行口和定时器)仍继续工作,

CPU内部SP、PC、PSW、A、P0~P3端口等所有其他寄存

30

看门狗的启动和清0的方法是一样的。

实际应用中,用户只要向寄存器WDTRST(地址为A6H) 先写入1EH,接着写入E1H,看门狗定时器便启动计数。

为防止看门狗定时器启动后产生不必要的溢出,在执行程 序的过程中,应在16384µs(时钟为12MHz时)内不断地复 位清“0” 看门狗。

31

2.10 低功耗节电模式 两种低功耗节电工作模式:空闲模式(idle mode)和掉

电保持模式(power down mode)。 掉电保持模式下,Vcc可由后备电源供电。 两种节电模式的内部控制电路。

第2章 AT89系列单片机的硬件体系结构(结构、引脚、存储器配置、专用寄存器、时钟与时序、工作方式)

2021/8/1

3

2.1 AT89系列单片机概述

2.1.1 AT89系列单片机简介

AT89系列单片机是与MCS—51系列单片机兼容 的低功耗高性能8位Flash单片机。它是在MCS-51 的技术内核为主导的基础上倾注了ATMEL公司优良 技术进行新的设计和开发,使之功能更强、更具特色, 尤其是AT89S系列单片机具有在系统可程序设计功能, 使生产维护更加方便灵活。

当CPU访问64KB的外部数据存储器时,就用

DPTR作地址指针,存放外部内存的地址;

当CPU访问64KB的程序存储器时,DPTR用作基

址寄存器。

CPU也可单独对DPH、DFra bibliotekL操作,即将DPTR分成

两个寄存器使用。

2021/8/1

21

2.3 AT89系列单片机的存储器

结构AT89系列单片机采用哈佛结构,有单独的程序存储器和

(2) 堆栈指针SP 堆栈指针SP(stack pointer)是一个8位特殊功能寄存器。

它指示出堆栈顶部在内部RAM中的位置。系统复位后,SP初 始化为07H,使得堆栈事实上由08H单元开始。考虑到08H ~1FH单元分属于工作寄存器区1~3,若程序设计中要用到 这些区,则最好把SP值改置为1FH或更大的值如60H。

处理情况。

例如:有一个单片机型号为“AT89C51—12PI”,

则表示意义为该单片机是 ATMEL公司的Flash单片

机,内部是CMOS结构,速度为12 MHz,封装为塑

封DIP,是工业用产品,按标准处理工艺生产。

2021/8/1

9

2.2 AT89系列单片机的结构原

2.2理.1 AT89系列单片机的基本组成

2021/8/1

单片机时序

单片机时序单片机时序指的是单片机在执行指令时所需要的时间和顺序,也就是指令周期。

在单片机的运行中,时序上的设定对于单片机的正确运行具有至关重要的作用。

下面将从时钟频率、指令周期、中断处理和定时器/计数器四个方面来探讨单片机的时序。

1. 时钟频率时钟频率指的是单片机的时钟信号的频率,一般来说,时钟频率越高,单片机的执行速度越快,但也会带来一系列问题,比如功耗、EMI等。

因此,时钟频率的选择需要根据实际应用场景来决定。

在单片机中,时钟出现的时间和时钟上升沿的时间都是非常关键的。

2. 指令周期指令周期是指单片机执行一条指令所需要的时间,它包括指令周期的各个阶段。

指令周期由时钟信号控制,时钟信号上升沿产生时单片机开始执行指令,经过若干个时钟周期后完成指令。

指令周期受到时钟频率和处理器内部结构的影响。

在设计单片机系统时,要根据要求和实际情况来选择指令周期长度。

3. 中断处理中断处理是指单片机在执行程序的过程中遇到某些特殊的事件时,由硬件产生中断信号,单片机暂停当前的执行,转而去执行特殊的中断程序。

中断处理相当于在当前执行的程序上打补丁,很大程度上影响了程序的时序。

在实际应用中,中断处理的时间不应该过长,否则会影响正常的程序执行。

4. 定时器/计数器定时器和计数器是单片机中常用的时序控制器。

定时器可以根据设置的定时时间,周期性地向单片机发送中断信号。

而计数器可以对输入信号进行计数,达到一定的值后向单片机发送中断信号。

这两个模块的存在,不仅可以控制程序的时序,也可以实现一些复杂的任务,比如Pulse Width Modulation(PWM)技术。

综上所述,单片机的时序对于系统的正确运行至关重要,它不仅仅是硬件实现的问题,也涉及到软件的编写。

在实际应用中,需要根据实际需求来精细的设计单片机的时序。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第2章 章

MCS-51单片机结构与时序 单片机结构与时序

2.定时控制部件

(1)指令寄存器 :存放指令执行的操作码 )指令寄存器IR: (2)振荡器 )振荡器OSC: OSC是控制器的心脏,提供时钟脉冲方波 :

(这个方波的频率是单片机的重要指标之一)

输入端--两个引脚外 输入端--两个引脚外接晶体振荡器和电容 --两个引脚 输出端--产生时钟脉冲系列 输出端--产生时钟脉冲系列 -- (3)定时控制逻辑:根据IR内容结合OSC,产生节拍脉冲序列 )定时控制逻辑: (形成控制节拍),完成不同指令的执行

第2章 章

MCS-51单片机结构与时序 单片机结构与时序

3.专用寄存器组( Register) 3.专用寄存器组(Special Function Register) 专用寄存器组

用来指示当前要执行指令的内存地址,存放操作数和指 示指令执行后的状态. Counter): (1)程序计数器PC(Program Counter): 16位的计数器 程序计数器PC( PC 作用是控制程序的执行顺序. 累加器A Accumulator): ):8位寄存器 (2) 累加器A(Accumulator): 最常用的专用寄存器.作用是存放操作数或运算的中 间结果. 通用寄存器B (3) 通用寄存器B: 8位寄存器 主要用于乘除运算.

64K

1 2 3 4 5 6 7 RAM 8 6264 9 10 11 12 13 14

28 27 26 25 24 23 22 21 20 19 18 17 16 15

1 2 3 4 5 6 7 8 9 10 11 12 13 14

2764

28 27 26 25 24 23 22 21 20 19 18 17 16 15

第2章 章

MCS-51单片机结构与时序 单片机结构与时序

程序状态字PSW Word) (4) 程序状态字PSW (Program Status Word): 8位寄存器 用于存放指令执行后的各种状态信息.各个状态位由 硬件自动设置或软件人工设定.作用是根据PSW有些位的 状态,进行程序转移.

PSW的各位定义如下: 的各位定义如下: 的各位定义如下

EA=0

0FFFH (4K) 0000H

(PC)

000BH 0003H 0002H 0001H 0000H

中断2 中断1

8位 位

程序存储器 程序存储器

程序存储器资源分布 程序存储器资源分布

第2章 章

MCS-51单片机结构与时序 单片机结构与时序 PSW位地址

CY

AC

F0

RS1

1 1 0 0

RS0

1 0 1 0

LSB

78 70 68 60 58 50 48 40 38 30 28 20 18 10 08 00

MSB——Most Significant Bit (最高有效位) Most 最高有效位) MSB 最低有效位) LSB ——Least Significant Bit (最低有效位) Least

第2章 章

2.1.2 存储器结构

MCS-51单片机的芯片内部有RAM和ROM两类存储器, 还支持扩展外部的RAM和ROM. 1,存储器地址分配

第2章 章

MCS-51单片机结构与时序 单片机结构与时序

4K

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

片内 ROM 8751

第2章 章

MCS-51单片机结构与时序 单片机结构与时序

第二章 课堂思考1

请说明下列缩略语的含义: CPU:Central Processing Unit, 中央处理单元 OSC: oscillator 振荡器 PC: PSW: SP: DPTR:

第2章 章

MCS-51单片机结构与时序 单片机结构与时序

EPROM

2764

64K

1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 15

EPROM

256B(字节)

第2章 章

MCS-51单片机结构与时序 单片机结构与时序

(1)程序存储器 (1)程序存储器

0FFFH 0FFEH

位地址

7C 74 6C 64 5C 54 4C 44 3C 34 2C 24 1C 14 0C 04 7B 73 6B 63 5B 53 4B 43 3B 33 2B 23 1B 13 0B 03 7A 72 6A 62 5A 52 4A 42 3A 32 2A 22 1A 12 0A 02 79 71 69 61 59 51 49 41 39 31 29 21 19 11 09 01

第2章 章

MCS-51单片机结构与时序 单片机结构与时序

2.1 MCS-51单片机内部结构 单片机内部结构

以8051为例,说明MCS-51系列单片机的内部组成,图2.5 .

2.1.1 CPU结构 结构 2.1.2 存储器结构 2.1.3 I/O端口 端口 2.1.4 定时器 计数器 定时器/计数器 2.1.5 中断系统

7F 07 R7 R0 R7 R0 R7 R0 R7 R0 78

30H 2FH 20H

可位寻址区

00 3区 区 2区 区 1区 区 0区 区

外部

FFH (高128B) 80H 7FH (低128B) 00H 专用 寄存器 内部 RAM 0000H

1FH 18H 17H 10H 0FH 08H 07H 00H

第2章 章

MCS-51单片机结构与时序 单片机结构与时序

I/O

RAM ROM

CPU

定时器

I/O

中断

第2章 章

MCS-51单片机结构与时序 单片机结构与时序

T0 T1

时钟电路

ROM

RAM

定时计数器

CPU

并行接口 串行接口 中断系统

P0 P1 P2 P3

TXD RXD

INT0 INT1

图2.5 MCS-51 单片机结构框图

工作寄存器区

数据存储器 数据存储器

内部RAM存储器 内部RAM存储器 RAM

第2章 章

MCS-51单片机结构与时序 单片机结构与时序

2. 片内 片内ROM MCS-51的程序存储器用于存放编好的程序和表格常数.8051片内 有4 KB的ROM,89C51片内有4 KB的EPROM,8031片内无. 是否使用片内的ROM? 3. 片内 片内RAM MCS-51的内部RAM共有256个单元,通常把这256个单元按其功能划 分为两部分:低128单元(单元地址00H~7FH)和高128单元(单元地 址80H~FFH). (1)工作寄存器区 (2)位寻址区 (3)便笺区

8051有四个寄存器组,每一组里都有R0-R7八个工作寄存器. 用RS1和RS0选定一个寄存器组.

OV(PSW.2)——溢出标志位. ( ) P(PSW.0)——奇偶标志位. ( )

第2章 章

MCS-51单片机结构与时序 单片机结构与时序

堆栈指针SP Pointer) (5) 堆栈指针SP (Stack Pointer): 8位寄存器 SP能自动加1或减1. 堆栈是一个特殊的存储区,用来暂存数据和地址,它是按"先进后 出"的原则存取数据的.堆栈共有两种操作:进栈和出栈. 数据指针DPTR Pointer) (6) 数据指针DPTR (Data Pointer): 16位寄存器 DPTR存放的是地址,作用是访问外部数据. 编程时,DPTR既可以按16位寄存器使用,也可以按两个8位寄存器 分开使用,即: DPH-- DPTR高位字节 DPL-- DPTR低位字节

PSW位 地址 字节地址 D0H

D7H CY

D6H AC

D5H F0

D4H RS1

D3H RS0

D2H OV

D1H -

D0H P

第2章 章

MCS-51单片机结构与时序 单片机结构与时序

Cy(PSW.7)——进位标志位:用于加减运算 ( ) AC(PSW.6)——辅助进位标志位:用于加减运算 ( ) F0(PSW.5)——用户标志位:用户软件设定. ( ) RS1和RS0(PSW.4,PSW.3)——寄存器组选择位 和 ( , )

中断入口地址

FFFFH

002BH

. . .

中断5 串行口中断 定时器1中断 外部中断1 定时器0中断 外部中断0 0000H是程序执行的起始单元, 在这三个单元存放一条 无条件转移指令

0023H

(64K)

001BH 0013H

中断4 中断3

0FFFH (4K) 0000H

内部

EA=1 0000H

外部

第2章 章

MCS-51单片机结构与时序 单片机结构与时序

2.1.1 CPU结构 结构

CPU 是 单 片 机 的 核 心 , 完 成 运 算 和 控 制 功 能 . 以 字 节 (8bit)为单位处理数据.

算术逻辑部件( Unit) 1.算术逻辑部件(A Logic Unit)

(1)加法器 )加法器:8位,加,减,乘,除四则运算 (2)布尔处理器:与,或,非,异或等逻辑运算 )布尔处理器: (3)暂存器:对用户不开放 )暂存器: 总之:进行四则运算 逻辑运算和数据传送 移位, 四则运算, 数据传送, 总之 : 进行 四则运算 , 逻辑运算和 数据传送 , 移位 , 判断和 程序转移

8031

8051 89C51

片内 RAM

40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 24 22 21

1 2 3 4 5 6 7 RAM 8 6264 9 10 11 12 13 14