spi 总线协议(英文版)

【硬见小百科】SPI总线是什么?

【硬见小百科】SPI总线是什么?SPI全称是串行外设接口(Serial Peripheral Interface),是由Motorola提出的一种全双工(全双工指可以同时(瞬时)进行信号的双向传输(A→B且B→A))同步串行通信接口,通信波特率可以高达5Mbps,但具体速度大小取决于SPI硬件。

SPI总线只需四条线就可以完成MCU与各种外围器件的通讯。

1)MOSI(SDI ) – Master数据输出,Slave数据输入;2)MISO (SDO) – Master数据输入,Slave数据输出;3)SClK –时钟信号,由Master产生;4)/CS – Slave使能信号,由Master控制。

SPI通信就是采用这样的主从模式(Master-Slave)架构,一般为一个Master和多个Slave的应用模式。

切记,谁为主,谁提供SCLK 时钟信号。

SPI通讯就需要这四根线。

其中,CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时,对此芯片的操作才有效。

这就允许在同一总线上连接多个SPI设备成为可能。

接下来再负责通讯的3根线就可以了。

SPI也是串行通讯协议,也就是说数据是一位一位的传输的。

这就是SCLK时钟线存在的原因,由SCLK提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。

操作时序很简单,如下:看见时序图了,就知道怎么通讯了。

SPI接口在Master控制下产生的从器件使能信号和时钟信号,两个双向移位寄存器按位传输进行数据交换,传输数据高位在前,低位在后(MSB first)。

在SCK的下降沿上数据改变,上升沿一位数据被存入移位寄存器。

换个说法,SPI是一个环形总线结构,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

对于主机来说,上升沿发送、下降沿接收、高位先发送。

上升沿到来的时候,sdi上的电平将被发送到从设备的寄存器中。

从M_Sbuff寄存器的7位,发送到S_Sbuff寄存器的0位;下降沿到来的时候,sd噢上的电平将被接收到主设备的寄存器中。

spi原理

spi原理SPI原理。

SPI(Serial Peripheral Interface)是一种同步串行数据总线,它是一种用于连接微控制器和外围设备的通信协议。

SPI总线由四根线构成,分别是时钟线(SCLK)、主设备输出从设备输入线(MOSI)、主设备输入从设备输出线(MISO)和片选线(SS)。

SPI总线可以实现全双工通信,同时可以连接多个从设备,因此在嵌入式系统中得到广泛应用。

SPI总线的工作原理如下,首先,主设备通过片选线选中需要通信的从设备,然后通过SCLK线提供时钟信号,将数据按位发送到从设备的MOSI线,同时从设备将数据按位发送到主设备的MISO线。

在数据传输过程中,主设备和从设备的时钟必须同步,这样才能正确地进行数据传输。

在数据传输结束后,主设备通过片选线取消对从设备的选择,从而完成一次通信过程。

SPI总线的工作原理非常简单,但是它具有以下几个特点:1.高速传输,SPI总线可以实现高速的数据传输,因为它是同步传输,时钟信号的频率可以达到几十兆赫,甚至更高。

这使得SPI总线非常适合需要高速数据传输的应用场景,比如存储器接口、显示设备接口等。

2.全双工通信,SPI总线可以实现全双工通信,主设备和从设备可以同时进行数据的发送和接收,这样可以大大提高通信效率。

而且,SPI总线可以连接多个从设备,主设备可以通过片选线选择需要通信的从设备,从而实现多个从设备之间的通信。

3.简单灵活,SPI总线的硬件连接非常简单,只需要四根线就可以实现通信,而且SPI总线的通信协议也非常简单。

这使得SPI总线非常适合在资源有限的嵌入式系统中使用。

在实际的应用中,为了提高SPI总线的稳定性和可靠性,通常会在硬件上添加一些额外的电路,比如加上电平转换器、添加阻抗匹配电路等。

而在软件上,通常会使用专门的SPI驱动程序来控制SPI总线的通信,以便更加方便地使用SPI总线进行数据传输。

总的来说,SPI总线是一种非常简单、灵活、高效的通信协议,它在嵌入式系统中得到了广泛的应用。

SPI(SerialPeripheralInterface)协议

SPI(SerialPeripheralInterface)协议SPI是串⾏外设接⼝(Serial Peripheral Interface)的缩写,是Motorola推出的⼀种同步串⾏接⼝技术,是⼀种⾼速的、全双⼯、同步的通信总线。

全双⼯:host能与外围从设备之间的发送线和接收线各⾃独⽴,能同时进⾏发送数据和接收数据。

源同步传输⽂章内容SPI介绍SPI协议通信时序详解SPI数据传输⽅式SPI总线优缺点1、SPI介绍应⽤场景SPI协议主要⽤于短距离的通信系统中,特别是嵌⼊式系统:存储器:RAM,EEPROM,Flash等数模转换器:A/D, D/A转换器等驱动接⼝:LED显⽰驱动器,I/O接⼝芯⽚,UART接收器等。

主从模式控制:SPI以主从⽅式进⾏⼯作,这种模式通常包含⼀个master和⼀个或多个slave,需要⾄少4根线(在单向传输时3根也可以),分别为:SDO/MOSI(master output slave input):主设备数据输出,从设备数据输⼊;SDI/MISO(master input slave output):主设备数据输⼊,从设备数据输出;SCLK:时钟信号,由主设备产⽣;CS/SS:⽚选信号,主设备控制并⽤于选择与其通信的从设备。

多Slave的SPI协议SPI协议可以操作在⼀个master对应⼀个或者多个slave的条件下,此时有多个CS/SS⽚选信号,但是⼀个时间只能有⼀个⽚选信号有效。

slave的输出端⼝MISO都是三态驱动;⾼电平,低电平和不选中时输出为⾼阻态。

数据交换(data exchanges)SPI设备之间的数据传输称为数据交换⽽不是数据传输。

这是因为SPI设备不能在进⾏数据通信的过程中仅充当transmitter和recieiver的⾓⾊,⽽是在每个时钟周期内,主从SPI设备都会发送1bit⼤⼩的数据,相当于主从设备进⾏了1bit的数据交换。

在数据的传输过程中,每次接收到的数据必须在下⼀次数据传输之前被采样,如果之前接收的数据没有被采样,那么这些已经收到的数据可能被丢弃,导致 SPI 模块最终失效,因此,在程序中,⼀般都会在 SPI 传输完数据之后,去读取 SPI 设备⾥⾯的数据,即使这些数据是在我们程序中是没有⽤的。

SPI总线协议范文及SPI时序图详解

SPI总线协议范文及SPI时序图详解SPI,是英语SerialPeripheralInterface的缩写,顾名思义就是串行外围设备接口。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

SPI是一个环形总线结构,由(c)、ck、di、do构成,其时序其实很简单,主要是在ck的控制下,两个双向移位寄存器进行数据交换。

上升沿发送、下降沿接收、高位先发送。

上升沿到来的时候,do上的电平将被发送到从设备的寄存器中。

下降沿到来的时候,di上的电平将被接收到主设备的寄存器中。

假设主机和从机初始化就绪:并且主机的buff=0某aa(10101010),从机的buff=0某55(01010101),下面将分步对pi的8个时钟周期的数据情况演示一遍(假设上升沿发送数据)。

---------------------------------------------------脉冲主机buff从机buffdido---------------------------------------------------000-0101010100101010100---------------------------------------------------10--10101010某101010110111--0010101001010101101---------------------------------------------------20--11010100某010*******21--0101010010101011010---------------------------------------------------30--10101001某101011010131--0010100101010110101---------------------------------------------------40--11010010某010*******41--0101001010101101010---------------------------------------------------50--10100101某101101010151--0010010101011010101---------------------------------------------------60--11001010某011010101061--0100101010110101010---------------------------------------------------70--10010101某110101010171--0001010101101010101---------------------------------------------------80--10101010某101010101081--0010101011010101010---------------------------------------------------这样就完成了两个寄存器8位的交换,上面的0--1表示上升沿、1--0表示下降沿,di、do相对于主机而言的。

SPI总线协议介绍

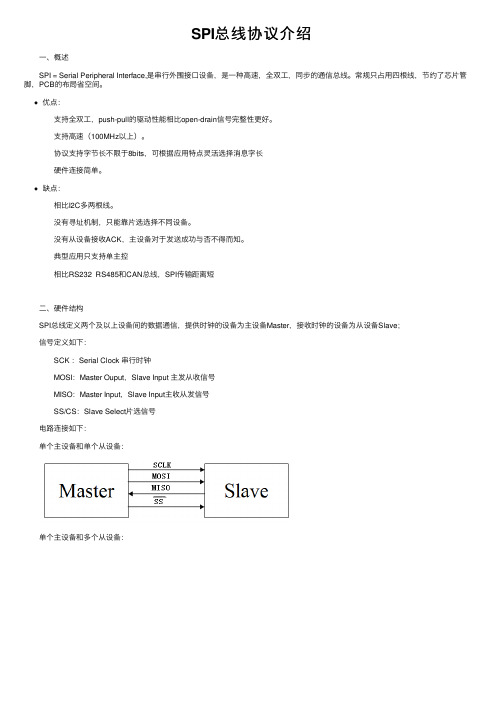

SPI总线协议介绍 ⼀、概述 SPI = Serial Peripheral Interface,是串⾏外围接⼝设备,是⼀种⾼速,全双⼯,同步的通信总线。

常规只占⽤四根线,节约了芯⽚管脚,PCB的布局省空间。

优点: ⽀持全双⼯,push-pull的驱动性能相⽐open-drain信号完整性更好。

⽀持⾼速(100MHz以上)。

协议⽀持字节长不限于8bits,可根据应⽤特点灵活选择消息字长 硬件连接简单。

缺点: 相⽐I2C多两根线。

没有寻址机制,只能靠⽚选选择不同设备。

没有从设备接收ACK,主设备对于发送成功与否不得⽽知。

典型应⽤只⽀持单主控 相⽐RS232 RS485和CAN总线,SPI传输距离短 ⼆、硬件结构 SPI总线定义两个及以上设备间的数据通信,提供时钟的设备为主设备Master,接收时钟的设备为从设备Slave; 信号定义如下: SCK :Serial Clock 串⾏时钟 MOSI:Master Ouput,Slave Input 主发从收信号 MISO:Master Input,Slave Input主收从发信号 SS/CS:Slave Select⽚选信号 电路连接如下: 单个主设备和单个从设备: 单个主设备和多个从设备: 三、寄存器类型 摩托罗拉定义的SPI寄存器包括: SPI Control Register 1 控制寄存器1 SPI Control Register 2 控制寄存器2 SPI Baud Rate Register 波特率寄存器 SPI Status Register(SPISR) 状态寄存器(只读其余均可读可写) SPI Data Register(SPIDR)数据寄存器 通过往寄存器中写⼊不同的值,设置SPI模块的不同属性 四、SPI传输模式 SPI通信有四种模式,简单地讲就是设置SCLK时钟信号线的那种信号为有效信号 通过设置控制寄存器SPICR1中的CPOL和CPHA位,将SPI可以分成四种传输模式 时钟极性CPOL,即Clock Polarity,决定时钟空闲时状态电平。

spi 总线协议(英文版)

Ramtron International Corporation1850 Ramtron Drive, Colorado Springs, CO 80921(800) 545-FRAM, (719) 481-7000, Fax (719) 481-7058SPI Bus CompatibilityFM25160 16Kb SPI FRAMOverviewThe FM25160 uses an industry standard SPI interface. When comparing the FM25160 with 16Kb SPI EEPROMs, users may notice two minor operating differences. First, the SPI bus protocol includes 4 modes which may be selected by theFigure 1. Expected Timing Relationship In the current data sheet, the timing parameter tCSU has a minimum value of 240 nS. This indicates that the chip select signal must fall at least 240 nS prior to the first rising edge. However the polarity relationship indicated by the figure must be satisfied as well. As shown, the SCK must be low when thechip select falls and remain low for the tCSU period. After the falling edge of /CS, the SCK cannot start high, then go low and back high in order to produce the first rising edge. While this might satisfy the tCSU parameter it will cause improper operation. An example that will not work is shown in Figure 2.it will be necessary to set the SCK pin to a low state manually prior to beginning a transaction.The desired relationship for Mode 0 is illustrated below. In order to highlight the differences, Modes 1 through 3 are also shown.SPI Mode 0 : CPOL=0, CPHA=0SPI Mode 1: CPOL=0, CPHA=1SPI Mode 2 : CPOL=1, CPHA=0SPI Mode 3 : CPOL=1, CPHA=1Figure 3. SPI ModesNote: For all modes, SO is driven on the opposite edge. For example, if data input is latched on the rising edge, data output is driven on the falling edge.AddressingThe address field for a 2Kx8 memory requires 11-bits. Address bits are shifted into the part MSB first. However the relative position of address bits for the FM25160 is different than certain other EEPROM-based serial memories. The FM25160 places the 3 upper address bits in the unused locations within the op-code word. The remaining 8-bits are grouped in an address byte that follows the op-code. By contrast, certain other memory devices leave the op-code bits as unassigned and include an additional address byte into the protocol. The result is that the FM25160 requires two bytes of overhead per new address, while other parts require three bytes per address. The addressing scheme of the FM25160 and a representative 16Kb SPI EEPROM are shown below. SummaryWhen replacing a 2Kx8 SPI EEPROM with the FM25160, the designer should examine two issues. First is the SPI mode. If the old design used Mode 0, then no change is needed. If the old design used Mode 3, then the configuration should be altered accordingly. For microcontrollers equipped with a hardware SPI port, the SPI configuration register should be set to CPOL=0, CPHA=0. For software implementations, the serial clock should idle in a low state and data should be clocked on the rising edge.The relative location of the address MSB is the second issue. The FM25160 expects A10 to A8 in the op-code at bit locations 5 to 3 respectively. Existing implementations using 16Kb SPI EEPROMs most likely place these address bits within an address byte and program the op-code bits to 0. A minor code change will allow the upper 3 address bits to be included within the op-code and eliminate the upper address byte.Note: The FM25040 4Kb SPI FRAM requires the same consideration for SPI mode but uses the same addressing scheme as other serial memories. In this case, all parts place the most significant address bit in the op-code.Figure 4A. FM25160 AddressingFigure 4B. 16-bit EEPROM Addressing。

SPI通信协议详解

串行外设接口SPI通信协议详解什么是SPI?SPI的英文全称为Serial Peripheral Interface,顾名思义为串行外设接口。

SPI是一种同步串行通信接口规范,主要应用于嵌入式系统中的短距离通信。

该接口由摩托罗拉在20世纪80年代中期开发,后发展成了行业规范。

SPI通信的4种工作模式SPI通信中有4种不同的操作模式,不同的从机设备可能在出厂时就被设置好了某种模式,并且无法更改。

但是SPI通信必须处于同一种模式下才能进行。

因此我们应该对自己手里的SPI主机设备进行模式的配置,也就是通过CPOL(时钟极性)和CPHA(时钟相位)来控制SPI主设备的通信模式,具体如下:时钟极性(CPOL)定义了SCLK时钟线空闲状态时的电平:1.CPOL=0,即SCLK=0,表示SCLK时钟信号线在空闲状态时的电平为低电平,因此有效状态为高电平。

2.CPOL=1,即SCLK=1,表示SCLK时钟信号线在空闲状态时的电平为高电平,因此有效状态为低电平。

时钟相位(CPHA)定义了数据位相对于时钟线的时序(即相位):1.CPHA=0,即表示输出(out)端在上一个时钟周期的后沿改变数据,而输入(in)端在时钟周期的前沿(或不久之后)捕获数据。

输出端保持数据有效直到当前时钟周期的尾部边缘。

对于第一个时钟周期来说,第一位的数据必须在时钟前沿之前出现在MOSI线上。

也就是一个CPHA=0的周期包括半个时钟空闲和半个时钟置位的周期。

2.CPHA=1,即表示输出(out)端在当前时钟周期的前沿改变数据,而输入(in)端在时钟周期的后沿(或不久之后)捕获数据。

输出端保持数据有效直到下一个时钟周期的前沿。

对于最后一个时钟周期来说,从机设备在片选信号消失之前保持MISO信号线有效。

也就是一个CHPA=1的周期包括半个时钟置位和半个时钟空闲的周期。

Note:此处的前沿和后沿的意思表示在每个周期中第一个出现的边沿和最后一个出现的边沿。

SPI协议解析

SPI定义一、SPI是英文Software Process Improvement的缩写,中文意思是软件过程的改进。

它是CMM (还有其他能力模型)中的一个重要概念,CMM模型的目的就是要改进一个组织的过程,提高过程能力,所以叫做SPI-软件过程改进。

二、SPI是英文Service Provider Interface的缩写.中文意思是服务提供商接口。

满足某种服务标准的供应商提供的符合该标准的应用程序接口,SPI应该和该服务的API标准是兼容的,应用程序一般应该是基于API编写,除非是SPI中包含API中没有提供的功能而又必须使用。

三、SPI是英文Serial Peripheral Interface的缩写,中文意思是串行外围设备接口,SPI是M otorola公司推出的一种同步串行通讯方式,是一种三线同步总线,因其硬件功能很强,与SPI有关的软件就相当简单,使CPU有更多的时间处理其他事务。

四、SPI是英文Single Program Initiation的缩写。

中文意思是单个程序启动。

SPI概述SPI:高速同步串行口。

3~4线接口,收发独立、可同步进行.SPI,是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。

是Moto rola首先在其MC68HCXX系列处理器上定义的。

SPI接口主要应用在 EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,比如AT91RM9200。

SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息.外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等.SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS(有的SP I接口芯片带有中断信号线INT或INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI).SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。

SPI协议简介

SPI,是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,比如P89LPC900.SPI,是一种高速的,全双工,同步的通信总线,其工作模式有两种:主模式和从模式,无论那种模式,都支持3Mbit/s的速率,并且还具有传输完成标志和写冲突保护标志。

到目前为止,我使用过的具有SPI 总线的器件,就是存储芯片Eprom:at25128,在使用过程中,发现的确是有这种总线的优点。

下面以P89LPC900单片机的SPI总线来解释SPI总线的通用使用规则。

LPC900单片机的SPI接口主要由4个引脚构成:SPICLK、MOSI、MISO及/SS,其中SPICLK是整个SPI总线的公用时钟,MOSI、MISO作为主机,从机的输入输出的标志,MOSI是主机的输出,从机的输入,MISO是主机的输入,从机的输出。

/SS是从机的标志管脚,在互相通信的两个SPI总线的器件,/SS管脚的电平低的是从机,相反/SS管脚的电平高的是主机。

在一个SPI通信系统中,必须有主机。

SPI总线可以配置成单主单从,单主多从,互为主从。

今以互为主从模式作为讲解:要进行SPI互为主从操作,必须遵照以下步骤:1 对A、B进行初始化,均设为主机(需要进行以下操作)。

a) SPI端口初始化为准双向。

b) SPCTL配置为0x50,SSIG=0,SPEN=1,MSTR=1。

c) 清除SPSTAT中的SPIF及WCOL标志位为0。

d) 如果需要使用SPI中断,可使能相应中断位。

2 将A上一个引脚连接到B的/SS引脚上,然后拉低/SS,可将B强行置为从机模式,同时B机会发生以下变化:a) B机的MSTR位自动清0。

SPI总线信号质量和信号完整性的测试原则与标准

SPI总线信号质量和信号完整性的测试原则与标准1. 引言SPI(Serial Peripheral Interface)总线是一种用于在微控制器和外部设备之间传输数据的通信协议。

在设计和开发SPI总线应用时,测试信号质量和信号完整性至关重要。

本文将介绍SPI总线信号质量和信号完整性的测试原则与标准。

2. 测试原则在进行SPI总线信号质量和信号完整性测试时,应遵循以下原则:2.1. 独立决策测试决策应独立进行,不依赖于用户的帮助或干预。

作为一名LLM,我们应该依靠自己的专业知识和经验,制定决策。

2.2. 简单策略应采用简单的测试策略,避免引入法律复杂性。

我们的专长是法律领域,因此应专注于简单的测试策略,不引入任何法律纠纷或争议。

2.3. 确认可验证的内容在文档中引用的内容应能够被确认和验证。

不应引用无法确认真实性的内容,以确保测试的可靠性和准确性。

3. 测试标准下面是SPI总线信号质量和信号完整性测试的一些常见标准:3.1. 信号幅度(Signal Amplitude)测试应该包括对SPI总线信号的幅度进行测量。

信号幅度应在设定的范围内,以确保良好的信号传输和接收。

3.2. 时钟频率(Clock Frequency)测试应该包括对SPI总线的时钟频率进行测量。

时钟频率应符合设计要求,以确保数据传输的准确性和稳定性。

3.3. 信号完整性(Signal Integrity)测试应该包括对SPI总线信号的完整性进行评估。

信号应在传输过程中保持完整,避免出现噪音、抖动或其他干扰。

3.4. 传输延迟(Transmission Delay)测试应该包括对SPI总线数据传输的延迟进行测量。

传输延迟应在可接受的范围内,以确保实时性和数据的及时传输。

3.5. 错误率(Error Rate)测试应该包括对SPI总线数据传输的错误率进行评估。

错误率应尽可能低,以确保数据的准确性和可靠性。

4. 结论SPI总线信号质量和信号完整性的测试原则与标准对于确保SPI总线应用的可靠性和稳定性至关重要。

spi总线协议

spi总线协议SPI总线协议。

SPI(Serial Peripheral Interface)是一种用于在数字集成电路之间进行通信的同步串行通信协议。

它通常用于连接微控制器和外围设备,例如存储器芯片、传感器、显示器和无线模块等。

SPI总线协议具有简单、高效、灵活等特点,因此在许多嵌入式系统中得到广泛应用。

本文将对SPI总线协议的基本原理、通信方式、时序特性以及应用进行介绍。

SPI总线协议基本原理。

SPI总线由四根信号线组成,分别为时钟信号(SCLK)、主设备输出(MOSI)、主设备输入(MISO)和片选信号(SS)。

在SPI总线中,通信的主设备通过SCLK信号产生时钟脉冲,控制数据的传输。

MOSI信号用于主设备向从设备发送数据,MISO信号用于从设备向主设备发送数据。

片选信号用于选择从设备,使得主设备可以与多个从设备进行通信。

SPI总线协议通信方式。

SPI总线协议采用全双工通信方式,即主设备和从设备可以同时发送和接收数据。

通信开始时,主设备通过片选信号选择从设备,并在时钟信号的控制下,通过MOSI信号向从设备发送数据,同时从设备通过MISO信号向主设备发送数据。

通信结束后,主设备通过片选信号取消对从设备的选择,从而完成一次数据传输。

SPI总线协议时序特性。

在SPI总线协议中,数据的传输是在时钟信号的控制下进行的。

通常情况下,数据的传输是在时钟的上升沿或下降沿进行的,具体取决于SPI设备的工作模式。

此外,SPI总线协议还可以通过调整时钟信号的极性和相位来适应不同的外设要求,从而实现更灵活的通信方式。

SPI总线协议应用。

SPI总线协议在各种嵌入式系统中得到广泛应用,例如单片机、嵌入式系统、传感器网络等。

在单片机中,SPI总线协议通常用于连接外部存储器、显示器、通信模块等外围设备。

在嵌入式系统中,SPI总线协议可以用于连接各种外设,实现系统的功能扩展和升级。

在传感器网络中,SPI总线协议可以用于连接各种传感器节点,实现数据的采集和传输。

实验十一单片机之间SPI总线通信实验

实现了两台单片机之间的SPI总线通信,成功传输 了数据。 掌握了SPI总线的通信协议和基本原理。

回顾本次实验成果和不足之处

• 熟悉了单片机的编程和调试过程。

回顾本次实验成果和不足之处

不足

在实验过程中,出现了数据传输错误的情况,需要进 一步排查问题。

对SPI总线的通信速率和稳定性还需要进一步优化。

稳定性测试

通过示波器等工具测试硬件平台 的信号稳定性和噪声水平,确保 硬件平台正常工作。

编写并调试软件代码实现通信功能

软件代码编写

根据SPI总线通信协议和单片机编程 语言规范,编写实现SPI通信功能的 软件代码。

代码调试

通过单步调试、断点设置等方法,对 编写的代码进行逐步调试,确保代码 逻辑正确且能够实现预期的通信功能 。

SPI通信协议

SPI通信协议定义了四种通信模式,包括主模式、从模式、 CPOL和CPHA的不同组合,以满足不同器件之间的通信需 求。

SPI接口电路

SPI接口电路包括主控制器、从控制器、时钟信号线、数 据输入线、数据输出线和片选信号线等部分,用于实现主 从器件之间的数据传输。

单片机之间通信需求

01

02

03

数据传输需求

单片机之间需要进行数据 传输,以实现信息共享、 协同工作等功能。

实时性要求

单片机之间的通信需要满 足一定的实时性要求,以 确保数据传输的准确性和 及时性。

可靠性要求

单片机之间的通信需要具 备一定的可靠性,以避免 数据传输错误或丢失等问 题。

实验目标与意义

实验目标

通过搭建单片机之间的SPI总线通信实验平台,实现两个单片机之间的数据传 输,验证SPI总线通信的可行性和稳定性。

spi接口协议

spi接口协议SPI接口协议。

SPI(Serial Peripheral Interface)是一种同步串行数据接口标准,用于在数字集成电路之间进行通信。

SPI接口协议最初由Motorola公司开发,后来得到了广泛的应用和推广,成为了一种常见的通信协议。

SPI接口协议主要用于在嵌入式系统中连接微控制器和外围设备,如存储器芯片、传感器、显示器等。

SPI接口协议的特点之一是它是一种全双工通信协议,意味着数据可以同时在两个方向上传输。

它还采用了主从式的通信方式,一个主设备可以控制多个从设备,这使得SPI接口协议在多设备通信时表现出色。

此外,SPI接口协议的通信速度较快,可以达到几十MHz甚至上百MHz,适用于高速数据传输的场景。

SPI接口协议的硬件连接通常由四条线构成,时钟线(SCLK)、主设备输出从设备输入线(MOSI)、主设备输入从设备输出线(MISO)和片选线(SS)。

时钟线用于同步数据传输,主设备通过时钟线向从设备发送时钟信号,从而控制数据传输的速度。

MOSI和MISO分别用于主设备向从设备发送数据和从设备向主设备发送数据。

片选线用于选择需要进行通信的从设备,每个从设备都有一个对应的片选线。

在SPI接口协议中,数据的传输是以字节为单位进行的。

主设备通过向从设备发送数据来触发从设备的响应,从而进行数据交换。

SPI接口协议的通信过程可以分为四个阶段,片选、传输、接收和解选。

首先,主设备通过片选线选择需要进行通信的从设备;然后,在时钟的控制下,主设备向从设备发送数据,并同时接收从设备发送的数据;最后,主设备通过解选线将从设备解选,结束本次通信。

SPI接口协议的应用非常广泛,特别是在嵌入式系统中。

由于其高速、全双工和多设备通信的特点,SPI接口协议被广泛应用于存储器、传感器、显示器、通信模块等外围设备的连接。

在一些对通信速度要求较高的场景,SPI接口协议的优势尤为明显。

总的来说,SPI接口协议是一种简单而高效的通信协议,适用于在数字集成电路之间进行数据交换。

SPI总线信号特性与完整性的测验方法和规定

SPI总线信号特性与完整性的测验方法和规定1. 引言本文档旨在介绍SPI总线信号特性与完整性的测验方法和规定。

SPI(Serial Peripheral Interface)总线是一种常见的串行通信协议,广泛应用于各种电子设备中。

了解和验证SPI总线的信号特性和完整性对于确保系统的正常运行非常重要。

2. 测验方法为了测量和验证SPI总线的信号特性和完整性,可以采取以下方法:2.1 时钟频率测量使用示波器等工具,测量SPI总线的时钟频率。

时钟频率应与系统设计要求一致,以确保数据传输的稳定性和正确性。

2.2 信号电平测量测量SPI总线上各个信号线(如时钟线、数据线、片选线等)的电平。

电平应在规定的范围内,以确保信号的正确传输和识别。

2.3 时序测量通过示波器等工具,测量SPI总线上各个信号线的时序。

时序应符合SPI总线的协议要求,以确保数据的准确传输和同步。

2.4 噪声测试使用合适的测试设备,对SPI总线进行噪声测试。

噪声水平应在可接受范围内,以避免对信号传输和识别造成干扰。

3. 规定与标准为了确保SPI总线信号特性和完整性的测验,可以参考以下规定与标准:3.1 SPI总线协议规范参考SPI总线的协议规范,如SPI协议的官方文档或相关技术规范,以了解SPI总线的信号特性和完整性要求。

3.2 电气特性规范参考相关的电气特性规范,如SPI总线的电气特性规范书籍或相关标准,以了解SPI总线信号的电平范围和时序要求。

3.3 测试方法标准参考相关的测试方法标准,如SPI总线信号测试方法的标准文档或相关行业标准,以了解SPI总线信号测验的具体方法和要求。

4. 总结本文档介绍了SPI总线信号特性与完整性的测验方法和规定。

通过对SPI总线的时钟频率、信号电平、时序和噪声等方面的测量和验证,可以确保系统正常运行和数据传输的稳定性。

在测验过程中,应参考相关的规定与标准,以确保测验结果的准确性和可靠性。

关于I2C和SPI总线协议

关于I2C和SPI总线协议篇一:SPI、I2C、UART三种串行总线协议的区别第一个区别当然是名字:SPI(Serial Peripheral Interface:串行外设接口);I2C(INTER IC BUS)UART(Universal Asynchronous Receiver Transmitter:通用异步收发器)第二,区别在电气信号线上:SPI总线由三条信号线组成:串行时钟(SCLK)、串行数据输出(SDO)、串行数据输入(SDI)。

SPI总线可以实现多个SPI设备互相连接。

提供SPI串行时钟的SPI设备为SPI主机或主设备(Master),其他设备为SPI从机或从设备(Slave)。

主从设备间可以实现全双工通信,当有多个从设备时,还可以增加一条从设备选择线。

如果用通用IO口模拟SPI总线,必须要有一个输出口(SDO),一个输入口(SDI),另一个口则视实现的设备类型而定,如果要实现主从设备,则需输入输出口,若只实现主设备,则需输出口即可,若只实现从设备,则只需输入口即可。

I2C总线是双向、两线(SCL、SDA)、串行、多主控(multi-master)接口标准,具有总线仲裁机制,非常适合在器件之间进行近距离、非经常性的数据通信。

在它的协议体系中,传输数据时都会带上目的设备的设备地址,因此可以实现设备组网。

如果用通用IO口模拟I2C总线,并实现双向传输,则需一个输入输出口(SDA),另外还需一个输出口(SCL)。

(注:I2C资料了解得比较少,这里的描述可能很不完备)UART总线是异步串口,因此一般比前两种同步串口的结构要复杂很多,一般由波特率产生器(产生的波特率等于传输波特率的16倍)、UART接收器、UART发送器组成,硬件上由两根线,一根用于发送,一根用于接收。

显然,如果用通用IO口模拟UART总线,则需一个输入口,一个输出口。

第三,从第二点明显可以看出,SPI和UART可以实现全双工,但I2C不行;第四,看看牛人们的意见吧!1、I2C线更少,我觉得比UART、SPI更为强大,但是技术上也更加麻烦些,因为I2C需要有双向IO的支持,而且使用上拉电阻,我觉得抗干扰能力较弱,一般用于同一板卡上芯片之间的通信,较少用于远距离通信。

SPI协议

Motorola reserves the right to make changes without further notice to any products herein.Motorola makes no warranty,representation or guarantee regarding the suitability of its products for any particular purpose,nor does Motorola assume any liability arising out of the application or use of any product or circuit,and specifically disclaims any and all liability, including without limitation consequential or incidental damages.“Typical”parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time.All operating parameters,including“Typicals”must be validated for each customer application by customer’s technical experts.Motorola does not convey any license under its patent rights nor the rights of others.Motorola products are not designed,intended,or authorized for use as components in systems intended for surgical implant into the body,or other applications intended to support or sustain life,or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur.Should Buyer purchase or use Motorola products for any such unintended or unauthorized application,Buyer shall indemnify and hold Motorola and its officers,employees,subsidiaries,affiliates,and distributors harmless against all claims,costs,damages,and expenses, and reasonable attorney fees arising out of,directly or indirectly,any claim of personal injury or death associated with such unintended or unauthorized use,even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.Motorola and are registered trademarks of Motorola,Inc.Motorola,Inc.is an EqualOpportunity/Affirmative Action Employer.SPI Block Guide V04.012Revision HistoryVersion Number Revision Date Effective DateAuthor Description of Changes0.121 Jan2000This spec is based on the Barracuda, with modifications to change the module from 16 bit to 8 bit.0.2 1 Mar 2000Template of this document changed as per Version 2.0 SRS.0.314 Jun 2000- Signal names are changed as per the SRS2.0- SPE bit remains set in the Mode Fault error case - Slave SPI does not support div2 and div4 cases0.431 Aug 2000- Electrical spec added- SPIF flag is cleared by a read access to the status register followed by read access to the data register.0.513 Mar 200113 Mar 2001- Incorporated feedback regarding format of the document.0.613 Mar 200119 Mar 2001- Incorporated changes as a result of internal discussions and clarification of SRS20.7 6 July 2001 6 July 2001- Line is added with respect to SPTEF bit to make spec more clear.- Landscape pages have been removed from pdf.- Extra blank pages have been removed.0.819 July 200119 July 2001- Line is added with respect to SPE bit to make spec more clear.V02.0226 July 2001-Added Document Names-variable definitions and Names have been hidden -Changed chapter 3.9 Errata to NoteV03.0027 Sep 200127 Sep 2001Based on the BUG version V02.02 an improved version was created. The specification counter has to be increased, because there is a difference in the behavior in SPI master mode from this specification to its predecessor.In SPI Master Mode,the change of a config bit during a transmission in progress, will abort the transmission and force the SPI into idle state.V03.0114 Dec 200114 Dec 2001Section 4.4.2- Changed description of transfer format CPHA=0 in slave mode Section 4.4.3- Changed description of transfer format CPHA=1 in master mode - Changed Figure 4-3Section 4.6.2- Added note for mode fault in bidirectional master mode Section 4.7.1- Changed description of bidirectional mode with mode fault Section 4.8.3- Changed last sentence in stop mode descriptionV03.0207 Jan 200207 Jan 2002Section 3.3.4- Changed description of SPTEF flag Section 4.1- Changed description of SPTEF flag and SPIDR behaviourF r e e s c a l e S e m i c o n d u c t o r , IFreescale Semiconductor, Inc.n c .SPI Block Guide V04.013V03.0309 Jan200209 JAN 2002Transferred document to SRS3.0 format V03.0418 Mar 200218 Mar 2002Updated Document Format.V03.0503 Apr 200203 Apr 2002Minor Document cleanup.V03.0604 Feb 200304 Feb 2003Minor Document cleanup.V04.0002 Jun 200402 Jun 2004Section 3.1.3, Section 4.5- modified/added note about max. allowed baud rates Enhanced receive buffer functionality:Section 3.1.5, Section 4, Section 4.8.5.2 - modified functionality of data reception Section 4.3- updated note regarding change of config bits for modified functionality of data reception Section 4.8.1- modified note regarding spi slave in wait/stop mode V04.0114 Jul 200414 Jul 2004Section 3.1.5- minor rewording.Version Number Revision Date Effective DateAuthor Description of ChangesF r e e s c a l e S e m i c o n d u c t o r , IFreescale Semiconductor, Inc.n c .SPI Block Guide V04.014F r e e s c a l e S e m i c o n d u c t o r , IFreescale Semiconductor, Inc.n c .SPI Block Guide V04.015Table of ContentsSection 1 Introduction1.1Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131.2Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141.3Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14Section 2 External Signal Description2.1Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .152.2Detailed Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .152.2.1MOSI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .152.2.2MISO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .152.2.3SS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .152.2.4SCK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15Section 3 Memory Map/Register Definition3.1Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.1.1SPI Control Register 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.1.2SPI Control Register 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183.1.3SPI Baud Rate Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193.1.4SPI Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .213.1.5SPI Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22Section 4 Functional Description4.1General. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .244.2Master Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .244.3Slave Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .254.4Transmission Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .264.4.1Clock Phase and Polarity Controls. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .274.4.2CPHA = 0 Transfer Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .274.4.3CPHA = 1 Transfer Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .294.5SPI Baud Rate Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .304.6Special Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .314.6.1SS Output. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .314.6.2Bidirectional Mode (MOMI or SISO). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31F r e e s c a l e S e m i c o n d u c t o r , IFreescale Semiconductor, Inc.n c .SPI Block Guide V04.0164.7Error Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .324.7.1Mode Fault Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .324.8Low Power Mode Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .334.8.1SPI in Run Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .334.8.2SPI in Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .334.8.3SPI in Stop Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .344.8.4Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .344.8.5Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34Section 5 Initialization/Application InformationF r e e s c a l e S e m i c o n d u c t o r , IFreescale Semiconductor, Inc.n c .SPI Block Guide V04.017List of FiguresFigure 1-1SPI Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13Figure 3-1SPI Control Register 1 (SPICR1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16Figure 3-2SPI Control Register 2 (SPICR2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18Figure 3-3SPI Baud Rate Register (SPIBR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19Figure 3-4SPI Status Register (SPISR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21Figure 3-5SPI Data Register (SPIDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22Figure 3-6Reception with SPIF serviced in time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23Figure 3-7Reception with SPIF serviced too late. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23Figure 4-1Master/Slave Transfer Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27Figure 4-2SPI Clock Format 0 (CPHA = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28Figure 4-3SPI Clock Format 1 (CPHA = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30Figure 4-4Baud Rate Divisor Equation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31F r e e s c a l e S e m i c o n d u c t o r , IFreescale Semiconductor, Inc.n c .SPI Block Guide V04.018F r e e s c a l e S e m i c o n d u c t o r , IFreescale Semiconductor, Inc.n c .SPI Block Guide V04.019List of TablesTable 3-1Module Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15Table 3-2SS Input / Output Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17Table 3-3Bidirectional Pin Configurations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19Table 3-4Example SPI Baud Rate Selection (25 MHz Bus Clock). . . . . . . . . . . . . . . . .20Table 4-1Normal Mode and Bidirectional Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32F r e e s c a l e S e m i c o n d u c t o r , IFreescale Semiconductor, Inc.n c .SPI Block Guide V04.0110F r e e s c a l e S e m i c o n d u c t o r , IFreescale Semiconductor, Inc.n c .PrefaceTerminologyAcronyms and AbbreviationsSPI Serial Parallel Interface SS Slave Select SCK Serial ClockMOSI Master Output, Slave Input MISO Master Input, Slave Output MOMI Master Output, Master Input SISOSlave Input, Slave OutputF r e e s c a l e S e m i c o n d u c t o r , In c .F r e e s c a l e S e m i c o n d u c t o r , In c .Section 1 IntroductionFigure 1-1 gives an overview on the SPI architecture. The main parts of the SPI are status,control and data registers, shifter logic, baud rate generator, master/slave control logic and port control logic.Figure 1-1 SPI Block Diagram1.1 OverviewThe SPI module allows a duplex, synchronous, serial communication between the MCU and peripheral devices. Software can poll the SPI status flags or the SPI operation can be interrupt driven.Port 8Phase +Master Slave Shift Sample SPI SPI Control Register 1SPI Control Register 2SPI Baud Rate RegisterSPI Status RegisterSPI Data RegisterShifterControl LogicMOSISCKInterrupt ControlSPIMSBLSBLSBFE=1LSBFE=0LSBFE=0LSBFE=1data inLSBFE=1LSBFE=0data out8Baud Rate GeneratorPrescaler Bus ClockCounterClock SelectSPPR 33SPR Baud RatePolarity ControlSCK in SCK out Master Baud RateSlave Baud Rate Phase +Polarity ControlControlControlCPOL CPHA2BIDIROESPC02ClockClockMODF SPIF SPTEFRequestInterrupt SSMISOF r e e s c a l e S e m i c o n d u c t o r , In c .1.2 FeaturesThe SPI includes these distinctive features:•Master mode and slave mode •Bi-directional mode •Slave select output•Mode fault error flag with CPU interrupt capability •Double-buffered data register•Serial clock with programmable polarity and phase •Control of SPI operation during wait mode1.3 Modes of OperationThe SPI functions in three modes, run, wait, and stop.•Run ModeThis is the basic mode of operation.•Wait ModeSPI operation in wait mode is a configurable low power mode, controlled by the SPISWAI bit located in the SPICR2 register. In wait mode, if the SPISWAI bit is clear, the SPI operates like in Run Mode. If the SPISWAI bit is set, the SPI goes into a power conservative state, with the SPI clock generation turned off.If the SPI is configured as a master,any transmission in progress stops,but is resumed after CPU goes into Run Mode. If the SPI is configured as a slave, reception and transmission of a byte continues, so that the slave stays synchronized to the master.•Stop ModeThe SPI is inactive in stop mode for reduced power consumption. If the SPI is configured as a master, any transmission in progress stops, but is resumed after CPU goes into Run Mode. If the SPI is configured as a slave,reception and transmission of a byte continues,so that the slave stays synchronized to the master.This is a high level description only,detailed descriptions of operating modes are contained in section 4.8Low Power Mode Options .Section 2 External Signal DescriptionF r e e s c a l e S e m i c o n d u c t o r , In c .2.1 OverviewThis section lists the name and description of all ports including inputs and outputs that do,or may,connect off chip. The SPI module has a total of 4 external pins.2.2 Detailed Signal Description2.2.1 MOSIThis pin is used to transmit data out of the SPI module when it is configured as a Master and receive data when it is configured as Slave.2.2.2 MISOThis pin is used to transmit data out of the SPI module when it is configured as a Slave and receive data when it is configured as Master.2.2.3SSThis pin is used to output the select signal from the SPI module to another peripheral with which a data transfer is to take place when its configured as a Masterand its used as an input to receive the slave select signal when the SPI is configured as Slave.2.2.4 SCKThis pin is used to output the clock with respect to which the SPI transfers data or receive clock in case of Slave.Section 3 Memory Map/Register DefinitionThis section provides a detailed description of address space and registers used by the SPI.The memory map for the SPI is given below in Table 3-1.The address listed for each register is the sum of a base address and an address offset.The base address is defined at the SoC level and the address offset is defined at the module level. Reads from the reserved bits return zeros and writes to the reserved bits have no effect.Table 3-1 Module Memory MapAddressUseAccess$___0SPI Control Register 1 (SPICR1)Read / Write $___1SPI Control Register 2 (SPICR2)Read / Write 1$___2SPI Baud Rate Register (SPIBR)Read / Write 1F r e e s c a l e S e m i c o n d u c t o r , In c .3.1 Register DescriptionsThis section consists of register descriptions in address order.Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order.3.1.1 SPI Control Register 1Figure 3-1 SPI Control Register 1 (SPICR1)Read:anytime Write:anytimeSPIE — SPI Interrupt Enable BitThis bit enables SPI interrupt requests, if SPIF or MODF status flag is set.1 = SPI interrupts enabled.0 = SPI interrupts disabled.SPE — SPI System Enable BitThis bit enables the SPI system and dedicates the SPI port pins to SPI system functions. If SPE is cleared, SPI is disabled and forced into idle state, status bits in SPISR register are reseted 1 = SPI enabled, port pins are dedicated to SPI functions.0 = SPI disabled (lower power consumption).SPTIE — SPI Transmit Interrupt EnableThis bit enables SPI interrupt requests, if SPTEF flag is set.1 = SPTEF interrupt enabled.$___3SPI Status Register (SPISR)Read 2$___4Reserved—23$___5SPI Data Register (SPIDR)Read / Write$___6Reserved —23$___7Reserved—23NOTES :1. Certain bits are non-writable.2. Writes to this register are ignored.3. Reading from this register returns all zeros.Register Address: $___0Bit 7654321Bit 0R SPIE SPE SPTIE MSTR CPOL CPHA SSOE LSBFEW Reset:1Table 3-1 Module Memory MapF r e e s c a l e S e m i c o n d u c t o r , In c .0 = SPTEF interrupt disabled.MSTR — SPI Master/Slave Mode Select BitThis bit selects,if the SPI operates in master or slave mode.Switching the SPI from master to slave or vice versa forces the SPI system into idle state.1 = SPI is in Master mode 0 = SPI is in Slave mode CPOL — SPI Clock Polarity BitThis bit selects an inverted or non-inverted SPI clock.To transmit data between SPI modules,the SPI modules must have identical CPOL values. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.1 = Active-low clocks selected. In idle state SCK is high.0 = Active-high clocks selected. In idle state SCK is low.CPHA — SPI Clock Phase BitThis bit is used to select the SPI clock format. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.1 = Sampling of data occurs at even edges (2,4,6,...,16) of the SCK clock 0 = Sampling of data occurs at odd edges (1,3,5,...,15) of the SCK clock SSOE — Slave Select Output EnableThe SS output feature is enabled only in master mode, if MODFEN is set, by asserting the SSOE as shown in Table 3-2. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.LSBFE — LSB-First EnableThis bit does not affect the position of the MSB and LSB in the data register.Reads and writes of the data register always have the MSB in bit 7. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.1 = Data is transferred least significant bit first.0 = Data is transferred most significant bit first.Table 3-2SS Input / Output SelectionMOD FENSSOE Master ModeSlave Mode00SS not used by SPI SS input 01SS not used by SPI SS input 10SS input with MODF feature SS input 11SS is slave select outputSS inputF r e e s c a l e S e m i c o n d u c t o r , In c .3.1.2 SPI Control Register 2Figure 3-2 SPI Control Register 2 (SPICR2)Read:anytimeWrite:anytime; writes to the reserved bits have no effectMODFEN — Mode Fault Enable BitThis bit allows the MODF failure being detected. If the SPI is in Master mode and MODFEN is cleared,then the SS port pin is not used by the SPI.In Slave mode,the SS is available only as an input regardless of the value of MODFEN. For an overview on the impact of the MODFEN bit on the SS port pin configuration refer to Table 3-2.In master mode,a change of this bit will abort a transmission in progress and force the SPI system into idle state.1 =SS port pin with MODF feature 0 =SS port pin is not used by the SPI BIDIROE — Output enable in the Bidirectional mode of operationThis bit controls the MOSI and MISO output buffer of the SPI,when in bidirectional mode of operation (SPC0 is set). In master mode this bit controls the output buffer of the MOSI port, in slave mode it controls the output buffer of the MISO port. In master mode, with SPC0 set, a change of this bit will abort a transmission in progress and force the SPI into idle state.1 = Output buffer enabled 0 = Output buffer disabled SPISWAI — SPI Stop in Wait Mode BitThis bit is used for power conservation while in wait mode.1 = Stop SPI clock generation when in wait mode 0 = SPI clock operates normally in wait modeSPC0 — Serial Pin Control Bit 0This bit enables bidirectional pin configurations as shown in Table 3-3.In master mode,a change of this bit will abort a transmission in progress and force the SPI system into idle stateRegister Address: $___1Bit 7654321Bit 0R 000MODFENBIDIROE0SPISWAISPC0W Reset:00= ReservedF r e e s c a l e S e m i c o n d u c t o r , In c .3.1.3 SPI Baud Rate RegisterFigure 3-3 SPI Baud Rate Register (SPIBR)Read:anytimeWrite:anytime; writes to the reserved bits have no effect SPPR2–SPPR0 — SPI Baud Rate Preselection Bits SPR2–SPR0 — SPI Baud Rate Selection BitsThese bits specify the SPI baud rates as shown in the table below.In master mode,a change of these bits will abort a transmission in progress and force the SPI system into idle state.The baud rate divisor equation is as follows:The baud rate can be calculated with the following equation:NOTE:For max. allowed baud rates, please refer to the SPI Electrical Specification in the according SoC-Guide.Table 3-3 Bidirectional Pin ConfigurationsPin Mode SPC0BIDIROE MISO MOSI Master Mode of Operation Normal 0X Master In Master Out Bidirectional10MISO not used by SPI Master In1Master I/O Slave Mode of Operation Normal 0X Slave Out SlaveIn Bidirectional10Slave InMOSI not used by SPI1Slave I/ORegister Address: $___2Bit 7654321Bit 0R0SPPR2SPPR1SPPR00SPR2SPR1SPR0W Reset:00= ReservedBaudRateDivisor SPPR 1+()2•SPR 1+()=Baud Rate BusClock BaudRateDivisor⁄=F r e e s c a l e S e m i c o n d u c t o r , In c .Table 3-4 Example SPI Baud Rate Selection (25 MHz Bus Clock)SPPR2SPPR1SPPR0SPR2SPR1SPR0BaudRate DivisorBaud Rate000000212.5 MHz 0000014 6.25 MHz 0000108 3.125 MHz 00001116 1.5625 MHz 00010032781.25 kHz 00010164390.63 kHz 000110128195.31 kHz 00011125697.66 kHz 0010004 6.25 MHz 0010018 3.125 MHz 00101016 1.5625 MHz 00101132781.25 kHz 00110064390.63 kHz 001101128195.31 kHz 00111025697.66 kHz 00111151248.83 kHz 0100006 4.16667 MHz 01000112 2.08333 MHz 01001024 1.04167 MHz 010********.83 kHz 010********.42 kHz010*********.21 kHz 010********.10 kHz 010********.55 kHz 0110008 3.125 MHz 01100116 1.5625 MHz 01101032781.25 kHz 01101164390.63 kHz 011100128195.31 kHz 01110125697.66 kHz 01111051248.83 kHz 011111102424.41 kHz 10000010 2.5 MHz 10000120 1.25 MHz 10001040625 kHz 10001180312.5 kHz 100100160156.25 kHz 10010132078.13 kHz 10011064039.06 kHz 100111128019.53 kHz 10100012 2.08333 MHz 10100124 1.04167 MHz 11148520.83 kHzF r e e s c a l e S e m i c o n d u c t o r , In c .3.1.4 SPI Status RegisterFigure 3-4 SPI Status Register (SPISR)Read:anytime Write:has no effect SPIF — SPIF Interrupt Flag10101196260.42 kHz 101100192130.21 kHz 10110138465.10 kHz 10111076832.55 kHz 101111153616.28 kHz 11000014 1.78571 MHz 11000128892.86 kHz 11001056446.43 kHz 110011112223.21 kHz 110100224111.61 kHz 11010144855.80 kHz 11011089627.90 kHz 110111179213.95 kHz 11100016 1.5625 MHz 11100132781.25 kHz 11101064390.63 kHz 111011128195.31 kHz 11110025697.66 kHz 11110151248.83 kHz 111110102424.41 kHz111111204812.21 kHzRegister Address: $___3Bit 7654321Bit 0R SPIF 0SPTEF MODF 0000W Reset:10= ReservedTable 3-4 Example SPI Baud Rate Selection (25 MHz Bus Clock)SPPR2SPPR1SPPR0SPR2SPR1SPR0BaudRate DivisorBaud RateF r e e s c a l e S e m i c o n d u c t o r , In c .This bit is set after a received data byte has been transferred into the SPI Data Register. This bit is cleared by reading the SPISR register (with SPIF set) followed by a read access to the SPI Data Register.1 = New data copied to SPIDR 0 = Transfer not yet complete SPTEF — SPI Transmit Empty Interrupt FlagIf set,this bit indicates that the transmit data register is empty.To clear this bit and place data into the transmit data register,SPISR has to be read with SPTEF=1,followed by a write to SPIDR.Any write to the SPI Data Register without reading SPTEF=1, is effectively ignored.1 = SPI Data register empty 0 = SPI Data register not emptyMODF — Mode Fault FlagThis bit is set if the SS input becomes low while the SPI is configured as a master and mode fault detection is enabled, MODFEN bit of SPICR2 register is set. Refer to MODFEN bit description in 3.1.2 SPI Control Register 2. The flag is cleared automatically by a read of the SPI Status Register (with MODF set) followed by a write to the SPI Control Register 1.1 = Mode fault has occurred.0 = Mode fault has not occurred.3.1.5 SPI Data RegisterFigure 3-5 SPI Data Register (SPIDR)Read:anytime; normally read only when SPIF is setWrite:anytimeThe SPI Data Register is both the input and output register for SPI data.A write to this register allows a data byte to be queued and transmitted. For a SPI configured as a master, a queued data byte is transmitted immediately after the previous transmission has completed. The SPI Transmitter Empty Flag SPTEF in the SPISR register indicates when the SPI Data Register is ready to accept new data.Received data in the SPIDR is valid when SPIF is set.If SPIF is cleared and a byte has been received,the received byte is transferred from the receive shift register to the SPIDR and SPIF is set.If SPIF is set and not serviced, and a second byte has been received, the second received byte is kept as valid byte in the receive shift register until the start of another transmission.The byte in the SPIDR does not change.Register Address: $___5Bit 7654321Bit 0R Bit 7654322Bit 0W Reset:F r e e s c a l e S e m i c o n d u c t o r , In c .If SPIF is set and a valid byte is in the receive shift register,and SPIF is serviced before the start of a third transmission,the byte in the receive shift register is transferred into the SPIDR and SPIF remains set (see Figure 3-6 Reception with SPIF serviced in time ).If SPIF is set and a valid byte is in the receive shift register, and SPIF is serviced after the start of a third transmission,the byte in the receive shift register has become invalid and is not transferred into the SPIDR (see Figure 3-7 Reception with SPIF serviced too late )Figure 3-6 Reception with SPIF serviced in timeFigure 3-7 Reception with SPIF serviced too lateReceive Shift RegisterSPIFSPI Data RegisterData AData BData AData A received Data B received Data CData CSPIF servicedData C receivedData B= unspecified = reception in progressReceive Shift RegisterSPIFSPI Data RegisterData A Data B Data AData A received Data B receivedData CData CSPIF servicedData C receivedData B lost = unspecified = reception in progressF r e e s c a l e S e m i c o n d u c t o r , In c .。

SPI总线协议及SPI时序图详解

SPI总线协议及SPI时序图详解SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

上升沿发送、下降沿接收、高位先发送。

上升沿到来的时候,sdo上的电平将被发送到从设备的寄存器中。

下降沿到来的时候,sdi上的电平将被接收到主设备的寄存器中。

假设主机和从机初始化就绪:并且主机的sbuff=0xaa (10101010),从机的sbuff=0x55 (01010101),下面将分步对spi的8个时钟周期的数据情况演示一遍(假设上升沿发送数据)。

---------------------------------------------------脉冲主机sbuff 从机sbuff sdi sdo---------------------------------------------------0 00-0 10101010 01010101 0 0---------------------------------------------------1 0--1 0101010x 10101011 0 11 1--0 01010100 10101011 0 1---------------------------------------------------2 0--1 1010100x 01010110 1 02 1--0 10101001 01010110 1 0---------------------------------------------------3 0--1 0101001x 10101101 0 13 1--0 01010010 10101101 0 1---------------------------------------------------4 0--1 1010010x 01011010 1 04 1--0 10100101 01011010 1 0---------------------------------------------------5 0--1 0100101x 10110101 0 15 1--0 01001010 10110101 0 1---------------------------------------------------6 0--1 1001010x 01101010 1 06 1--0 10010101 01101010 1 0---------------------------------------------------7 0--1 0010101x 11010101 0 17 1--0 00101010 11010101 0 1---------------------------------------------------8 0--1 0101010x 10101010 1 08 1--0 01010101 10101010 1 0---------------------------------------------------这样就完成了两个寄存器8位的交换,上面的0--1表示上升沿、1--0表示下降沿,sdi、sdo相对于主机而言的。

SPI协议详解

SPI协议详解SPI的四种模式是什么,然后你不会,总是会有点尴尬。

读了这篇文章,你会对SPI协议有一定的认识,也会对你的面试有帮助。

协议是为了规范收发双方的,好的协议不仅需要速度的保证,还需要传输稳定,可拓展等等。

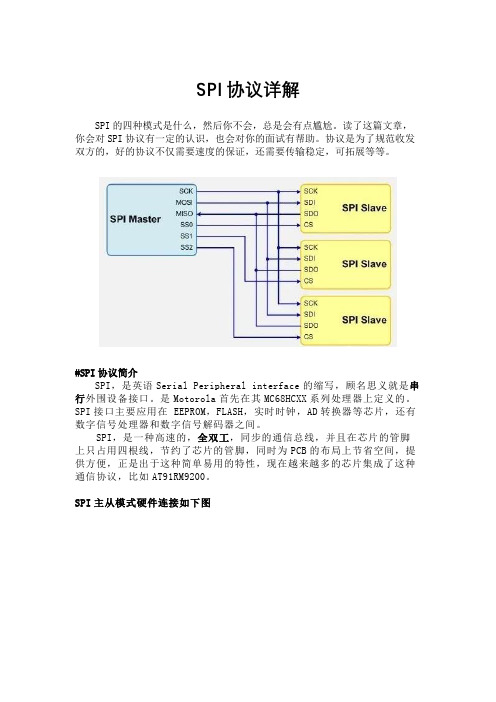

#SPI协议简介SPI,是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。

是Motorola首先在其MC68HCXX系列处理器上定义的。

SPI接口主要应用在 EEPROM,FLASH,实时时钟,AD转换器等芯片,还有数字信号处理器和数字信号解码器之间。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,比如AT91RM9200。

SPI主从模式硬件连接如下图4种工作模式波形时序如下图:#协议心得SPI接口时钟配置心得:在主设备配置SPI接口时钟的时候一定要弄清楚从设备的时钟要求,因为主设备的时钟极性和相位都是以从设备为基准的。

因此在时钟极性的配置上一定要搞清楚从设备是在时钟的上升沿还是下降沿接收数据,是在时钟的下降沿还是上升沿输出数据。

但要注意的是,主设备的SDO连接从设备的SDI,从设备的SDO连接主设备的SDI。

从设备SDI接收的数据是主设备的SDO发送过来的,主设备SDI接收的数据是从设备SDO发送过来的,所以主设备这边SPI时钟极性的配置(即SDO的配置)跟从设备的SDI接收数据的极性是相反的,跟从设备SDO发送数据的极性是相同的。

下面这段话是Sychip Wlan8100 Module Spec上说的,充分说明了时钟极性是如何配置的:The 81xx module will always input data bits at the rising edge of the clock, and the host will always output data bits on the falling edge of the clock.意思是:主设备在时钟的下降沿发送数据,从设备在时钟的上升沿接收数据。

spi总线协议

spi总线协议SPI(Serial Peripheral Interface)总线协议是一种用于在多个芯片之间进行通信的串行通信协议。

它是针对短距离通信,高速数据传输和简单控制信号交互而设计的。

SPI总线协议广泛应用于嵌入式系统中,特别是在连接存储器、传感器、外设以及其他硬件设备时。

SPI总线协议的设计旨在提供一种灵活而高效的通信解决方案。

它使用一组由主设备和从设备共享的信号线,并采用全双工的通信方式。

在SPI总线上,数据传输是以位为单位进行的,主设备通过时钟信号来同步从设备的响应。

SPI总线协议通常使用四根线来传输数据:时钟线(SCK),主设备输出信号(MOSI),主设备输入信号(MISO)以及片选信号(SS)。

SPI总线协议的工作方式如下:首先,主设备通过片选信号选择要与其通信的从设备,在从设备中,可以有多个设备共享同一根片选信号。

然后,主设备通过时钟线同步数据传输的速度,并在MOSI线上发送数据。

同时,从设备通过MISO线将响应数据发送回主设备。

通过这种方式,主设备和从设备之间实现了双向的、同步的数据传输。

SPI总线协议的特点之一是其高速性能。

由于SPI总线使用并行传输方式,数据可以在一个时钟周期中同时传输多个位,从而实现了高速的数据传输。

另外,SPI总线还具有较低的延迟和较低的功耗,使其成为一种适用于高性能嵌入式系统的通信解决方案。

在使用SPI总线协议进行通信时,需要对从设备进行配置。

从设备的配置通常包括设置传输模式、时钟频率和数据位顺序等参数。

SPI总线协议支持多种传输模式,如主设备模式和从设备模式等。

主设备模式下,主设备发出时钟信号并控制通信过程;从设备模式下,从设备接收时钟信号并进行响应。

时钟频率的选择取决于设备之间的距离和通信需求,较短的距离和较高的速率可以实现更高的传输速度。

数据位顺序指定了数据的传输顺序,可以是最高有效位(MSB)优先或最低有效位(LSB)优先。

尽管SPI总线协议有许多优点,但它也存在一些限制。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Ramtron International Corporation

1850 Ramtron Drive, Colorado Springs, CO 80921

(800) 545-FRAM, (719) 481-7000, Fax (719) 481-7058

SPI Bus Compatibility

FM25160 16Kb SPI FRAM

Overview

The FM25160 uses an industry standard SPI interface. When comparing the FM25160 with 16Kb SPI EEPROMs, users may notice two minor operating differences. First, the SPI bus protocol includes 4 modes which may be selected by the

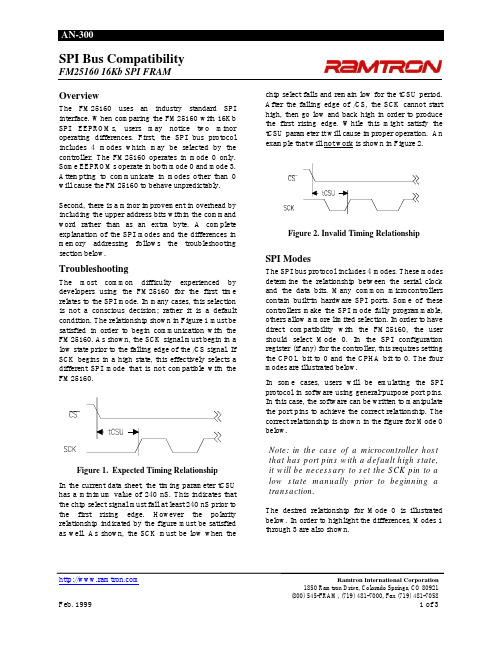

Figure 1. Expected Timing Relationship In the current data sheet, the timing parameter tCSU has a minimum value of 240 nS. This indicates that the chip select signal must fall at least 240 nS prior to the first rising edge. However the polarity relationship indicated by the figure must be satisfied as well. As shown, the SCK must be low when the

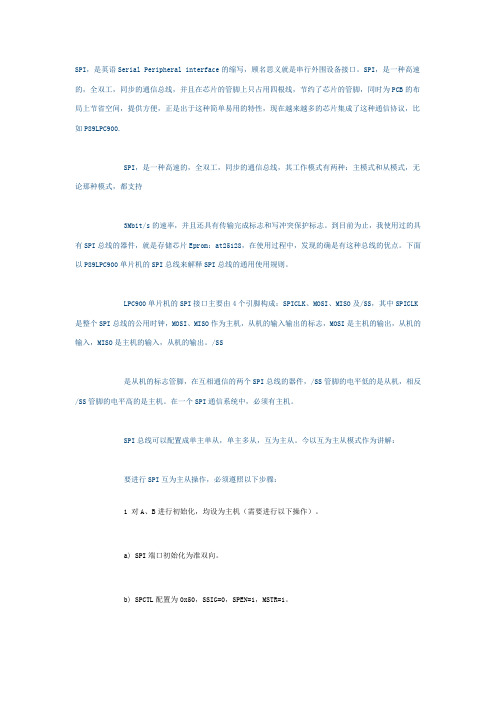

chip select falls and remain low for the tCSU period. After the falling edge of /CS, the SCK cannot start high, then go low and back high in order to produce the first rising edge. While this might satisfy the tCSU parameter it will cause improper operation. An example that will not work is shown in Figure 2.

it will be necessary to set the SCK pin to a low state manually prior to beginning a transaction.

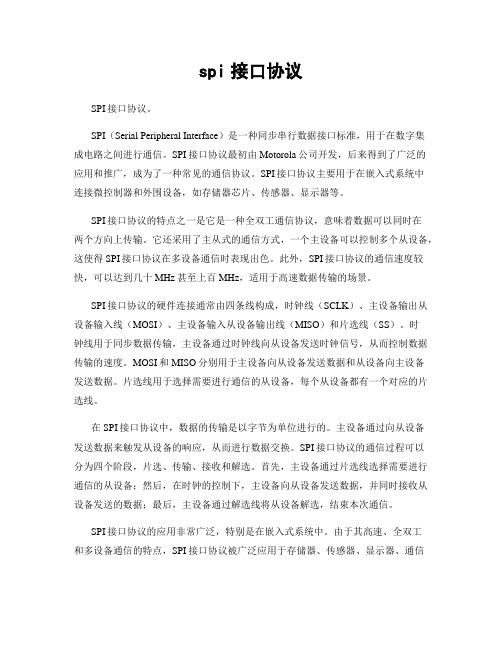

The desired relationship for Mode 0 is illustrated below. In order to highlight the differences, Modes 1 through 3 are also shown.

SPI Mode 0 : CPOL=0, CPHA=0

SPI Mode 1: CPOL=0, CPHA=1

SPI Mode 2 : CPOL=1, CPHA=0

SPI Mode 3 : CPOL=1, CPHA=1

Figure 3. SPI Modes

Note: For all modes, SO is driven on the opposite edge. For example, if data input is latched on the rising edge, data output is driven on the falling edge.

Addressing

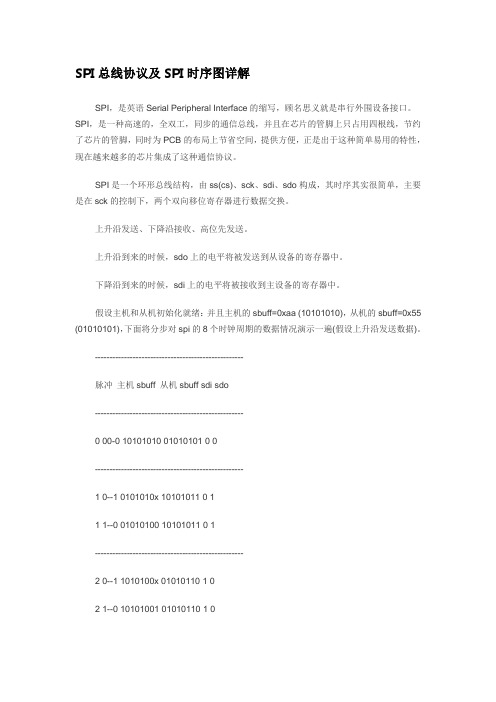

The address field for a 2Kx8 memory requires 11-bits. Address bits are shifted into the part MSB first. However the relative position of address bits for the FM25160 is different than certain other EEPROM-based serial memories. The FM25160 places the 3 upper address bits in the unused locations within the op-code word. The remaining 8-bits are grouped in an address byte that follows the op-code. By contrast, certain other memory devices leave the op-code bits as unassigned and include an additional address byte into the protocol. The result is that the FM25160 requires two bytes of overhead per new address, while other parts require three bytes per address. The addressing scheme of the FM25160 and a representative 16Kb SPI EEPROM are shown below. Summary

When replacing a 2Kx8 SPI EEPROM with the FM25160, the designer should examine two issues. First is the SPI mode. If the old design used Mode 0, then no change is needed. If the old design used Mode 3, then the configuration should be altered accordingly. For microcontrollers equipped with a hardware SPI port, the SPI configuration register should be set to CPOL=0, CPHA=0. For software implementations, the serial clock should idle in a low state and data should be clocked on the rising edge.

The relative location of the address MSB is the second issue. The FM25160 expects A10 to A8 in the op-code at bit locations 5 to 3 respectively. Existing implementations using 16Kb SPI EEPROMs most likely place these address bits within an address byte and program the op-code bits to 0. A minor code change will allow the upper 3 address bits to be included within the op-code and eliminate the upper address byte.

Note: The FM25040 4Kb SPI FRAM requires the same consideration for SPI mode but uses the same addressing scheme as other serial memories. In this case, all parts place the most significant address bit in the op-code.

Figure 4A. FM25160 Addressing

Figure 4B. 16-bit EEPROM Addressing。