静态时序分析(Static Timing Analysis)基础及应用

静态时序分析原理解读及实例应用

静态时序分析原理解读及实例应用摘要:静态时序分析(Static Timing Analysis)是FPGA(现场可编程逻辑器件)分析电路时序的最坏情况,验证此时的电路性能是否满足用户的时序要求。

静态时序分析的目的是提高系统工作主频及增加系统的稳定性。

关键词:静态时序分析;FPGA;关键路径引言静态时序分析是基于电路的拓扑结构,计算逻辑单元延时和互联延时,提取出整个电路的所有时序路径,找出延时最大的关键路径,确定电路工作时所能达到的最大频率,并检查建立时间和保持时间余量,其目的是检查FPGA 芯片中设计电路的延时和速度等性能指标,分析电路时序的最坏情况,验证此时的电路性能是否满足用户的时序要求。

相比较于动态时序仿真具备更加高效和完备的特点。

目前比较流行的静态时序分析工具有Prime Time,TimeQuest Timing Analyzer、Vivado系列等工具。

1时序中的基本概念1.1时钟周期和最高频率时序路径分为输入端口到内部寄存器路径,内部寄存器到寄存器路径,内部寄存器到输出端口路径,FPGA内部时序分析的对象为“寄存器—寄存器”路径,时序逻辑设计都是基于时钟沿的。

在Quar tusⅡ下的时序分析器TimeQuest的时序报告中有启动沿和锁存沿的概念,它们是针对时钟而言的。

启动沿(launch edge):前级寄存器发送数据时对应的时钟沿,是时序分析的起点。

锁存沿(latch edge):后级寄存器捕获数据时对应的时钟沿,是时序分析的终点。

锁存沿一般默认与启动沿相差一个时钟周期。

时钟周期的概念是FPGA 中时序定义的基础,根据图1计算时钟最小周期。

图1时钟周期的计算时钟最小时钟周期计算式为:T clk= τco+ τdata_dalay+ τsu−τclk_skew(式1)其中τclkskew= τclk1−τclk2(式2)式1中,T clk是时钟的最小周期。

τco是寄存器固有的时钟到输出延迟,是寄存器的固有属性,指的是寄存器相应时钟沿有效,将数据送到输出端口的内部延时参数,典型值一般小于1ns。

静态时序分析基础及应用1(下)

前言在制程进入深次微米世代之后,晶片(IC)设计的高复杂度及系统单晶片(SOC)设计方式兴起。

此一趋势使得如何确保IC品质成為今日所有设计从业人员不得不面临之重大课题。

静态时序分析(Static Timing Analysis简称STA)经由完整的分析方式判断IC是否能够在使用者指定的时序下正常工作,对确保IC品质之课题,提供一个不错的解决方案。

在「静态时序分析(Static Timing Analysis)基础及应用(上)」一文中笔者以简单叙述及图例说明的方式,对STA的基础概念做了详尽的说明。

接下来,就让我们藉由实际设计范例来瞭解STA在设计流程的应用。

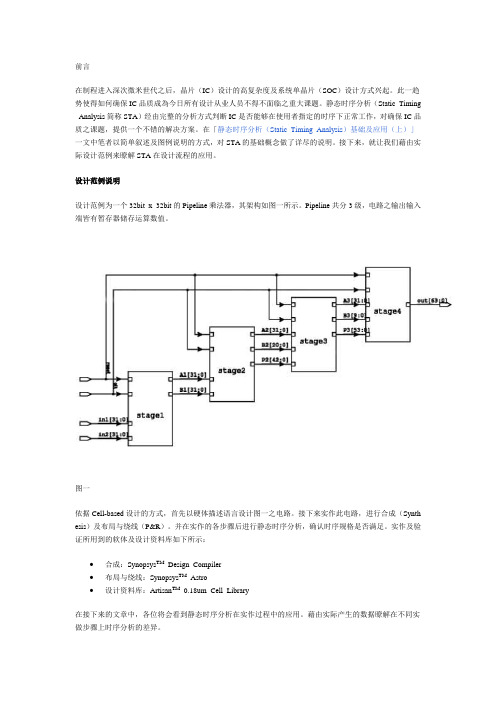

设计范例说明设计范例为一个32bit x 32bit的Pipeline乘法器,其架构如图一所示。

Pipeline共分3级,电路之输出输入端皆有暂存器储存运算数值。

图一依据Cell-based设计的方式,首先以硬体描述语言设计图一之电路。

接下来实作此电路,进行合成(Synth esis)及布局与绕线(P&R)。

并在实作的各步骤后进行静态时序分析,确认时序规格是否满足。

实作及验证所用到的软体及设计资料库如下所示:∙合成:Synopsys TM Design Compiler∙布局与绕线:Synopsys TM Astro∙设计资料库:Artisan TM0.18um Cell Library在接下来的文章中,各位将会看到静态时序分析在实作过程中的应用。

藉由实际产生的数据瞭解在不同实做步骤上时序分析的差异。

时序限制(Timing Constraint)要作静态时序分析,首先要有时序限制。

此设计范例的时序限制如下所述。

(→后為设定时序限制之SD C指令)1 时脉规格(Clock Specification)1.1 週期:6ns →create_clock -name "MY_CLOCK" -period 6 -waveform {0 3} [get_ports {clk}]1.2 Source Latency:1ns →set_clock_latency -source 1 [get_clocks {MY_CLOCK}]1.3 Network Latency:1ns →set_clock_latency 1 [get_clocks {MY_CLOCK}]1.4 Skew:0.5ns →set_clock_uncertainty 0.5 [get_clocks {MY_CLOCK}]2 周边状况(Boundary Condition)2.1 输入延迟(Input Delay):1.2ns →set allin_except_CLK [remove_from_collection [all_inputs] [get_po rts clk] ]set_input_delay $I_DELAY -clock MY_CLOCK $allin_except_CLK2.2 输出延迟(Output Delay):1.2ns →set_output_delay $O_DELAY -clock MY_CLOCK [all_outputs]2.3 输出负载(Output Loading):0.5pF →set_load $O_LOAD 0.5 [all_outputs]3 时序例外(Timing Exception):无合成软体之时序报告当Synopsys Design Compiler将电路合成完毕后,执行下面指令可以產生时序报告:report_timing -path full -delay max -max_paths 10 -input_pins \-nets -transition_time -capacitance > timing_syn.txt时序报告会储存在timing_syn.txt此档案中。

静态时序分析(Static Timing Analysis)

STA Vs Event Simulation

Event Driven Timing simulation STA

Vector Generation Design Coverage Runtime Capacity

Required Vector dependent(limited) coverage Takes several days/weeks of CPU time Can run out of memory for multimillion designs No special features for timing sis

静态时序分析

潘伟涛

主要内容

• • • • • What is STA? Why STA? What STA do? When STA? How to do STA?

STA的概念

静态时序分析简称STA(Static Timing Analysis),是一种针对大 规模门级电路进行时序验证的有效方法。它只需要根据电路网表 的拓扑,就可以检查电路设计中所有路径的时序特性,测试路径 的覆盖率理论上可以达到100%,从而保证时序验证的完备性; 同时由于不需要测试向量,所以STA验证所需时间远小于门级仿 真时间。

Analysis/Debug features

Design style support

No Restrictions

STA in the ASIC Design Flow

Tech Library HDL Source

Pre-layout STA

Module netlists Constraints STA models Logic synthesis

• The STA tool: Builds netlist in memory Exhaustively traces every possible timing path Computes and propagates delays and skews Determines critical paths Reports timing paths, violations, etc

何谓静态时序分析

何谓静态时序分析(Static Timing Analysis,简称STA)何谓静态时序分析(Static Timing Analysis,简称STA)?它可以简单的定义为:设计者提出一些特定的时序要求(或者说是添加特定的时序约束),套用特定的时序模型,针对特定的电路进行分析。

分析的最终结果当然是要求系统时序满足设计者提出的要求。

下面举一个最简单的例子来说明时序分析的基本概念。

假设信号需要从输入到输出在FPGA内部经过一些逻辑延时和路径延时。

我们的系统要求这个信号在FPGA内部的延时不能超过15ns,而开发工具在执行过程中找到了如图4.1所示的一些可能的布局布线方式。

那么,怎样的布局布线能够达到我们的要求呢?仔细分析一番,发现所有路径的延时可能为14ns、14ns、16ns、17ns、18ns,有两条路径能够满足要求,布局布线就会选择满足要求的两条路径之一。

1.静态时序分析模型因此,有些说法是错误的,不分什么情况就说时序不收敛,其实在不加约束的情况下谈时序约束是没有意义的。

附加约束的基本作用1.提高设计的工作频率对很多数字电路设计来说,提高工作频率非常重要,因为高工作频率意味着高处理能力。

通过附加约束可以控制逻辑的综合、映射、布局和布线,以减小逻辑和布线延时,从而提高工作频率。

2.获得正确的时序分析报告几乎所有的FPGA设计平台都包含静态时序分析工具,利用这类工具可以获得映射或布局布线后的时序分析报告,从而对设计的性能做出评估。

静态时序分析工具以约束作为判断时序是否满足设计要求的标准,因此要求设计者正确输入约束,以便静态时序分析工具输出正确的时序分析报告。

3.指定FPGA/CPLD引脚位置与电气标准FPGA/CPLD的可编程特性使电路板设计加工和FPGA/CPLD设计可以同时进行,而不必等FPGA/CPLD引脚位置完全确定,从而节省了系统开发时间。

这样,电路板加工完成后,设计者要根据电路板的走线对FPGA/CPLD加上引脚位置约束,使FPGA/CPLD与电路板正确连接。

非常详细的静态时序分析教程

非常详细的静态时序分析教程静态时序分析是电子设计自动化领域中的重要方法之一,用于评估数字电路中的时序性能。

本教程将介绍静态时序分析的基本概念、方法和步骤,并提供一些实例来帮助读者深入了解这个领域。

一、静态时序分析的基本概念在进行静态时序分析之前,我们需要了解一些基本概念:1.时钟边沿:时钟是数字电路中的基本信号之一,它的边沿可以分为上升沿和下降沿。

时序分析通常以时钟的上升沿作为参考边沿进行分析。

2.关键路径:在一个数字电路中,存在多条路径可以连接输入和输出。

关键路径是指在特定时钟频率下,数据从输入到输出的延时最长的路径。

时序分析的目标之一就是找到并优化关键路径,以提高电路的性能。

3.时序约束:时序约束是对数字电路的时序性能要求的规定。

通常由设计者在进行时序分析之前进行设置,用于指导分析工具进行正确的分析和优化。

二、静态时序分析的方法和步骤静态时序分析的主要方法是通过对电路中的时钟域、数据路径和约束条件进行建模和分析,从而判断关键路径和优化方案。

下面是静态时序分析的基本步骤:1. 建立电路模型:首先,需要将数字电路转化为时序分析工具可以理解的模型,通常可以使用硬件描述语言(如Verilog或VHDL)对电路进行描述。

2.设定时序约束:根据设计规范和目标性能要求,制定适当的时序约束,如最大延时、最小脉冲宽度等。

时序约束的制定需要根据具体的电路应用和设计要求进行。

3.进行静态时序分析:使用时序分析工具对电路进行分析,找到关键路径,并计算出关键路径的延时。

关键路径上的最大延时指示了电路的最坏情况性能。

4.优化关键路径:在找到关键路径后,可以通过各种手段进行优化,如增加缓冲器、减少逻辑门延时等。

优化的目标是减小关键路径的延时,以提高整个电路的性能。

5.重新进行时序分析:在优化关键路径之后,需要重新进行时序分析,确保所做的优化在整个电路中得到正确应用,并满足时序约束。

三、实例分析让我们通过一个简单的例子来说明静态时序分析的具体过程。

静态时序分析 STA

/html/EDAjishu/2007/0323/1810.html 前言 在制程进入深次微米世代之后,晶片(IC)设计的高复杂度及系统单晶片(SOC)设计方式 兴起。此一趋势使得如何确保 IC 品质成为今日所有设计从业人员不 得不面临之重大课题。静 态时序分析(Static Timing Analysis 简称 STA)经由完整的分析方式判断 IC 是否能够在使用 者的时序环境下正常工作,对确保 IC 品质之课题,提供一个不错的解决方案。然而, 对于许 多 IC 设计者而言, STA 是个既熟悉却又陌生的名词。本文将力求以简单叙述及图例说明的方式, 对 STA 的基础概念及其在 IC 设计流程中的应用做详尽 的介绍。 什么是 STA? STA 的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违 反设计者给定的时序限制(Timing Constraint)。以分析的方式区分,可分为 Path-Based 及 Block-Based 两种。

1

来判断所设计的电路是否符合给定的 Timing Constraint。由于最常用来做静态时序分析验证核 可( STA Signoff )的 EDA 软体 PrimeTime?采用 Path-Based 的分析方式, 所以本文将以 Path-Based 的分析方式介绍为主。 再来看看 Block-Based 的分析方式。此时时序资讯(Timing Information)的储存不再是以 路径为单位,而是以电路节点(Node)为单位。由 Timing Constraint 我们仅能得知 A 节点的 AT 为 2,B 节点的 AT 为 5 以及 Y 节点的 RT 为 10。Block-Based 的分析方式会找出每个节点的 AT 和 RT,然后比对这两个数值。当 RT 的值大于 AT 时表示讯号比 Timing Constrain 中要求的 时间还早到达,如此则 Timing 是满足的,反之则不满足。

静态时序分析(statictiminganalysis)

静态时序分析(statictiminganalysis)静态时序分析(static timing analysis,STA)会检测所有可能的路径来查找设计中是否存在时序违规(timing violation)。

但STA只会去分析合适的时序,⽽不去管逻辑操作的正确性。

其实每⼀个设计的⽬的都相同,使⽤Design Compiler和IC Compile来得到最快的速度,最⼩的⾯积和最少的耗能。

根据设计者提供的约束,这些⼯具会在⾯积,速度和耗能上做出权衡。

更深层的来看,STA⼀直都寻找⼀个问题的答案:在所有条件下,当时钟沿到达时,数据会正确地在每个同步device的输⼊端正确显⽰吗?这问题可以⽤下图来表⽰:如图中所⽰,虚线表⽰了时序路径。

两者使⽤了同⼀个时钟驱动,理想情况下FF1的数据变化之后在下个时钟沿能够准确到达FF2。

两者的时序图如下:在FF1的时钟沿到来时,会把FF1的D端的数据送⼊flip-flop。

在经过⼀个clock-to-Q的延时之后,数据会送⼊FF1的Q端。

此过程叫做时序路径的launch event。

信号经过了两个FF之间的组合逻辑之后,到达了组合逻辑的输出,也就是FF2的输⼊端(FF2.D),这个叫做arrival time。

然⽽数据并不是在时钟沿到达FF2的同时到达,⽽是要⽐时钟沿早到那么⼀点点。

早到的这个时间叫做required time,不同的device的required time不⼀样。

数据装载到FF2的时间点叫做capture event。

device的required time和数据到达的时间(arrival time)两者之差则叫做slack。

图中所⽰,数据⽐时钟早到很多,则slack为正。

如果数据刚好在required time时间点到达,则slack为0,若是数据晚到的话则是负了。

例如required time是launch event之后的1.8ns,⽽arrival time是launch event之后的1.6ns,则slack = 1.8-1.6=0.2ns。

静态时序分析(Static_Timing_Analysis)基础与应用

静态时序分析Static Timing Analysis基础与应用前言在制程进入深次微米世代之后,晶片(IC)设计的高复杂度及系统单晶片(SOC)设计方式兴起。

此一趋势使得如何确保IC品质成为今日所有设计从业人员不得不面临之重大课题。

静态时序分析(Static Timing Analysis简称STA)经由完整的分析方式判断IC是否能够在使用者的时序环境下正常工作,对确保IC品质之课题,提供一个不错的解决方案。

然而,对于许多IC设计者而言,ST A是个既熟悉却又陌生的名词。

本文将力求以简单叙述及图例说明的方式,对S TA的基础概念及其在IC设计流程中的应用做详尽的介绍。

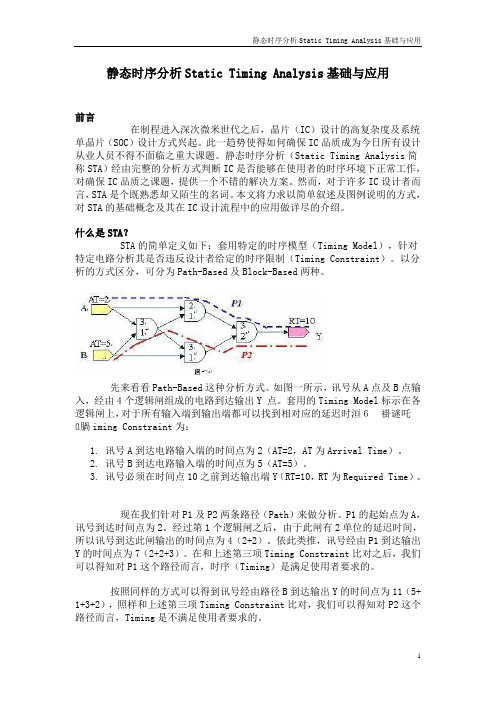

什么是STA?STA的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。

以分析的方式区分,可分为Path-Based及Block-Based两种。

先来看看Path-Based这种分析方式。

如图一所示,讯号从A点及B点输入,经由4个逻辑闸组成的电路到达输出Y 点。

套用的Timing Model标示在各逻辑闸上,对于所有输入端到输出端都可以找到相对应的延迟时洹6 褂谜吒 ǖ腡iming Constraint为:1.讯号A到达电路输入端的时间点为2(AT=2,AT为Arrival Time)。

2.讯号B到达电路输入端的时间点为5(AT=5)。

3.讯号必须在时间点10之前到达输出端Y(RT=10,RT为Required Time)。

现在我们针对P1及P2两条路径(Path)来做分析。

P1的起始点为A,讯号到达时间点为2。

经过第1个逻辑闸之后,由于此闸有2单位的延迟时间,所以讯号到达此闸输出的时间点为4(2+2)。

依此类推,讯号经由P1到达输出Y 的时间点为7(2+2+3)。

在和上述第三项Timing Constraint比对之后,我们可以得知对P1这个路径而言,时序(Timing)是满足使用者要求的。

静态时序分析

静态时序分析静态时序分析电子科技大学詹璨铭什么是静态时序分析静态时序分析STA(static timing analysis)?定义与动态时序分析的差异怎样做静态时序分析使用工具primetime (简称pt)与DC ?两者的兼容性为什么使用primetime?Primetime与DC的兼容性使用同样的工艺库和设计文件许多指令一样相同的算法,很多结果也一样从一个synthesizable subcircuit 中,pt能捕获一个时序环境,并写成一系列的dc指令,在dc中用其为这个subcircuit定义时间约束和时序优化--值得关注为dc写的dcsh格式的脚本可以翻译成在pt上用的格式。

在pt 中定义为抄本(transcript)格式这两个都支持用SDC(synopsys design constraints)格式指定设计规则,包括时间面积约束。

为什么用pt更快效率更高占用更少的内存具有高级的芯片级的分析能力和高级的建模能力。

STA中的对象Design -完整的设计Cell(instance)-设计中使用的一个元件?Net -金属连线Port -design 的I/O口Pin -cell 的I/O口Reference -是元件的参考的源定义Clock -创建的时钟信号时序弧(timing arc)定义:如果把电路看作是一张很大的拓扑图,那么图中的结点就是电路中的引脚(pin)。

结点与结点之间的部分,我们称作是时序弧(timing arc)。

他定义了任意两个结点之间的时序关系。

最直观基本的理解:cell delay与net delay。

这两个也是计算下面时序弧的基础。

每段时序弧的延时就是把这两个值不断相加时序弧分类一:时序的延时组合时序弧(combinational timing arc)?边沿时序弧(edge timing arc)重置和清除时序弧(preset and clear timing arc)三态使能/无效时序弧(three state enable/disable timing arc)时序弧分类二:时序约束建立时序弧(setup timing arc)保持时序弧(hold timing arc)恢复时序弧(recovery timing arc)?清除时序弧(removal timing arc)?宽度时序弧(width timing arc)组合时序弧(combinationaltiming arc)负函数(negative unate)正函数(positive unate)非函数(non-unate)calculation)--cell delay是从一个逻辑门的输入到输出的延迟量通过工艺库(technology library)来查找的这是个2维表,查找项是输入的过渡时间(input transition),输出的电容负载(output load capacitance)没有对应的值,做一个线性的推导,计算出相应的值。

静态时序分析基础与应用2(上)

除了Clock之外,对于电路其他输出输入端点及其周边的环境(Boundary Condition)也要加以描述。

在说明Boundary Condition之前,我们得对路径(Path)有更进一步的了解。

上文曾提及STA会将电路中所有的Path找出来加以分析,但Path的定义是什么呢?Path根据起点及终点可以分为4种:1.由Flip-Flop Clock输入到Flip-Flop资料输入(图十七左上)。

2.由主要输入(Primary Input,简称PI)到Flip-Flop资料输入(图十七右上)。

3.由Flip-Flop Clock输入到主要输出(Primary Output,简称PO)(图十七左下)。

4.由主要输入到主要输出(图十七右下)。

当Clock规格确定了之后,第1种Path的时序限制(Timing Constraint)就自动的给定了。

为了给定其他3种Path的时序限制,我们必须定义Boundary Condition。

一般来说,我们会定义下列的Boundary Condition:1.Driving Cell:定义输入端点的推动能力(图十八)。

2.Input Transition Time:定义输入端点的转换时间(图十八)。

3.Output Capacitance Load:定义输出负载(图十八)。

4.Input Delay:输入端点相对于某个Clock领域的延迟时间。

(图十九,Delayclk-Q+ a)5.Output Delay:自输出端点往外看相对于某个Clock领域的延迟时间。

(图十九,c)在这些Boundary Condition定义之后,上述4种Path事实上都可看成是第1种Path(Flip-Flop到Flip-Flop)。

也就是说,加上Boundary Condition后,只要Clock给定,所有Path 的Timing Constraint就会自动给定。

图十八图十九由于每个Path都有Timing Constraint,所以时序分析都能够进行。

静态时序分析基本原理和时序分析模型

静态时序分析基本原理和时序分析模型静态时序分析是指对程序在其编译阶段或者运行阶段进行的一种分析方法,通过对程序的代码进行解析和推理,从而分析出程序执行的正确性、性能、资源消耗等方面的信息。

静态时序分析可以帮助开发人员在代码实现阶段尽早发现和解决问题,提高代码的可靠性和可维护性。

1.控制流分析:静态时序分析首先通过控制流分析,构建程序的控制流图。

控制流图由程序中的所有语句和它们之间的控制流关系构成,用来描述程序的执行路径和顺序。

静态时序分析可以通过控制流图来寻找潜在的执行路径问题,如死循环、无法到达的代码等。

2.数据流分析:静态时序分析还可以进行数据流分析,通过对程序中变量的定义和使用关系进行分析,确定变量在不同的执行路径上的值。

数据流分析可以帮助发现未初始化变量、未使用变量等问题。

3.依赖分析:静态时序分析可以进行依赖分析,分析程序中不同语句之间的依赖关系,确定一些语句执行的前提条件。

依赖分析可以帮助发现多线程竞争、资源争用等问题。

静态时序分析的依赖分析可以通过指针分析、函数调用分析等方式实现。

4.前向分析和后向分析:静态时序分析可以进行前向分析和后向分析。

前向分析从程序的入口点开始,根据程序的控制流图,逐个语句地分析程序的执行路径。

后向分析从程序的出口点开始,反向分析程序的执行路径。

通过前向分析和后向分析,可以找到程序的执行路径,帮助发现执行路径上的问题。

时序分析模型是静态时序分析的抽象表示,可以用来描述程序的执行顺序和时序约束。

常见的时序分析模型包括Petri网、有限状态机等。

1. Petri网:Petri网是一种常用的时序分析模型,它可以描述系统中不同活动之间的顺序和并发关系。

Petri网由节点和有向弧组成,节点表示活动,弧表示活动之间的关系。

通过对Petri网的分析,可以推理出系统的行为和时序约束。

2.有限状态机:有限状态机是描述系统行为的一种抽象模型,它可以把系统的执行顺序表示为一个状态转移图。

静态时序分析(Static

静态时序分析(Static Timing Analysis)基础与应用前言在制程进入深次微米世代之后,晶片(IC)设计的高复杂度及系统单晶片(SOC)设计方式兴起。

此一趋势使得如何确保IC品质成为今日所有设计从业人员不得不面临之重大课题。

静态时序分析(Static Timing Analysis简称STA)经由完整的分析方式判断IC是否能够在使用者的时序环境下正常工作,对确保IC品质之课题,提供一个不错的解决方案。

然而,对于许多IC设计者而言,STA 是个既熟悉却又陌生的名词。

本文将力求以简单叙述及图例说明的方式,对STA 的基础概念及其在IC设计流程中的应用做详尽的介绍。

什么是STA?STA的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。

以分析的方式区分,可分为Path-Based及Block-Based两种。

先来看看Path-Based这种分析方式。

如图一所示,讯号从A点及B点输入,经由4个逻辑闸组成的电路到达输出Y 点。

套用的Timing Model标示在各逻辑闸上,对于所有输入端到输出端都可以找到相对应的延迟时间。

而使用者给定的Timing Constraint为:1.讯号A到达电路输入端的时间点为2(AT=2,AT为Arrival Time)。

2.讯号B到达电路输入端的时间点为5(AT=5)。

3.讯号必须在时间点10之前到达输出端Y(RT=10,RT为Required Time)。

现在我们针对P1及P2两条路径(Path)来做分析。

P1的起始点为A,讯号到达时间点为2。

经过第1个逻辑闸之后,由于此闸有2单位的延迟时间,所以讯号到达此闸输出的时间点为4(2+2)。

依此类推,讯号经由P1到达输出Y的时间点为7(2+2+3)。

在和上述第三项Timing Constraint比对之后,我们可以得知对P1这个路径而言,时序(Timing)是满足使用者要求的。

静态时序分析课件

案例三:时钟偏差与时钟抖动问题解决

总结词

详细描述

案例四:时序违规问题解决

要点一

总结词

要点二

详细描述

时序违规问题是指在设计中的时序信号不能满足时序约束 条件,可能导致数据传输错误或系统不稳定。

在静态时序分析中,需要仔细检查设计的时序信号是否满 足约束条件,并采取相应的措施来解决时序违规问题。可 以采用优化设计、调整时序约束条件或使用静态时序分析 工具等方法来解决时序违规问题。

时钟源与负载不匹配问题

总结词

详细描述

时钟偏差与时钟抖动问题

总结词

时钟偏差与时钟抖动问题是指时钟信号 在传输过程中出现的偏差和抖动现象, 可能导致数据的不稳定和时序违规。

VS

详细描述

时钟信号在传输过程中会受到各种因素的 影响,如线路长度、连接器、时钟源的抖 动等,导致时钟信号的偏差和抖动。这种 偏差和抖动可能导致数据的不稳定和时序 违规。为了解决这个问题,需要减小传输 过程中的偏差和抖动,并加强时钟网络的 同步和稳定性。

THANKS

感谢观看

时钟偏差是指时钟信号到达不同寄存器的时间偏差,通常由时钟源、时钟网络和寄 存器本身引起。

时钟抖动和偏差是影响数字电路时序分析的重要因素,需要进行有效的管理和优化。

03

静态时序分析方法

路径延迟分析

路径延迟分析是静态时序分析中的重 要步骤,它通过计算信号在电路中传 输的延迟时间,来确定信号到达时间 是否满足时序要求。

时序违规问题

总结词

详细描述

06

静态时序分析案例研究

案例一:时钟域交叉问题解决

总结词

详细描述

案例二:时钟源与负载不匹配问题解决

总结词

时钟源与负载不匹配问题是指时钟源的频率与负载的要求不匹配,可能导致数据 传输错误或资源浪费。

静态时序分析

静态时序分析电子科技大学詹璨铭什么是静态时序分析⏹静态时序分析STA(static timing analysis)⏹定义⏹与动态时序分析的差异怎样做静态时序分析⏹使用工具primetime (简称pt)与DC ⏹两者的兼容性⏹为什么使用primetime?Primetime与DC的兼容性⏹使用同样的工艺库和设计文件⏹许多指令一样⏹相同的算法,很多结果也一样⏹从一个synthesizable subcircuit 中,pt能捕获一个时序环境,并写成一系列的dc指令,在dc中用其为这个subcircuit定义时间约束和时序优化--值得关注⏹为dc写的dcsh格式的脚本可以翻译成在pt上用的格式。

在pt中定义为抄本(transcript)格式⏹这两个都支持用SDC(synopsys design constraints)格式指定设计规则,包括时间面积约束。

为什么用pt⏹更快效率更高⏹占用更少的内存⏹具有高级的芯片级的分析能力和高级的建模能力。

STA中的对象⏹Design -完整的设计⏹Cell(instance)-设计中使用的一个元件⏹Net -金属连线⏹Port -design 的I/O口⏹Pin -cell 的I/O口⏹Reference -是元件的参考的源定义⏹Clock -创建的时钟信号时序弧(timing arc)⏹定义:如果把电路看作是一张很大的拓扑图,那么图中的结点就是电路中的引脚(pin)。

结点与结点之间的部分,我们称作是时序弧(timing arc)。

他定义了任意两个结点之间的时序关系。

⏹最直观基本的理解:cell delay与net delay。

这两个也是计算下面时序弧的基础。

每段时序弧的延时就是把这两个值不断相加时序弧分类一:时序的延时⏹组合时序弧(combinational timing arc)⏹边沿时序弧(edge timing arc)⏹重置和清除时序弧(preset and clear timing arc)⏹三态使能/无效时序弧(three state enable/disable timing arc)时序弧分类二:时序约束⏹建立时序弧(setup timing arc)⏹保持时序弧(hold timing arc)⏹恢复时序弧(recovery timing arc)⏹清除时序弧(removal timing arc)⏹宽度时序弧(width timing arc)组合时序弧(combinationaltiming arc)⏹负函数(negative unate)⏹正函数(positive unate)⏹非函数(non-unate)calculation)--cell delay⏹是从一个逻辑门的输入到输出的延迟量⏹通过工艺库(technology library)来查找的⏹这是个2维表,查找项是输入的过渡时间(input transition),输出的电容负载(output load capacitance)没有对应的值,做一个线性的推导,计算出相应的值。

Lesson+31+时序分析基础

Lesson 31 时序分析基础一、静态时序分析的概念何谓静态时序分析(STA,Static Timing Analysis)?首先,设计者应该对FPGA内部的工作方式有一些认识。

FPGA的内部结构其实就好比一块PCB板,FPGA的逻辑阵列就好比PCB板上的一些分立元器件。

PCB通过导线将具有相关电气特性的信号相连接,FPGA也需要通过内部连线将相关的逻辑节点导通。

PCB板上的信号通过任何一个元器件都会产生一定的延时,FPGA的信号通过逻辑门传输也会产生延时。

PCB的信号走线有延时,FPGA的信号走线也有延时。

这就带来了一系列问题,一个信号从FPGA的一端输入,经过一定的逻辑处理后从FPGA的另一端输出,这期间会产生多大的延时呢?有多个总线信号从FPGA的一端输入,这条总线的各个信号经过逻辑处理后从FPGA的另一端输出,这条总线的各个信号的延时一致吗?之所以关心这些问题,是因为过长的延时或者一条总线多个信号传输时间的不一致,不仅会影响FPGA本身的性能,而且也会给FPGA之外的电路或者系统带来诸多问题。

言归正传吧,之所以引进静态时序分析的理论也正是基于上述的一些思考。

它可以简单的定义为:设计者提出一些特定的时序要求(或者说是添加特定的时序约束),套用特定的时序模型,针对特定的电路进行分析。

分析的最终结果当然是要求系统时序满足设计者提出的要求。

下面举一个最简单的例子来说明时序分析的基本概念。

假设信号需要从输入到输出在FPGA内部经过一些逻辑延时和路径延时。

系统要求这个信号在FPGA内部的延时不能超过15ns,而开发工具在执行过程中找到了如图4.1所示的一些可能的布局布线方式。

那么,怎样的布局布线能够达到系统的要求呢?仔细分析一番,发现所有路径的延时可能为14ns、14ns、16ns、17ns、18ns,有两条路径能够满足要求,那么最后的布局布线就会选择满足要图4.1 静态时序分析模型静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,即有约束才会有分析。

静态时序分析基础及应用2(下)

S2/U10/Y (BUFX20) 0.23 0.21 2.51 r这一行是描述Buffer从输入端到输出端的时间延迟,其值為0.21,所以信号到达Buffer输出端的时间為2.3+0.21=2.51ns(图五)。

接下来是一堆类似的元件时序资讯,我们略过它们不讨论,直接跳到最后面几个元件。

S3/add_106/U0_5_47/A (XNOR2X2) 0.18 0.00 7.74 fS3/add_106/U0_5_47/Y (XNOR2X2) 0.12 0.22 7.96 f这是到Critical Path终点前的最后一个元件,信号到达的时间是7.96ns。

各位可以看到最右边的标示已经变成f了,这表示信号由1变0的状况元件延迟时间较长。

S3/add_106/SUM[47] (net) 1 0.01 0.00 7.96 fS3/add_106/SUM[47] (stage3_DW01_add_54_0) 0.00 7.96 fS3/N94 (net) 0.01 0.00 7.96 fS3/P3_reg_47_/D (DFFTRXL) 0.12 0.00 7.96 fdata arrival time 7.96这几行都是同一个节点的时序资讯,只是逻辑阶层(Logic Hierarchy)不同。

信号最后到达Critical Path终点的时间為7.96ns(图六)。

以上是Arrival Time(AT)的计算,接下来我们看Required Time(RT)的计算。

图五图六clock MY_CLOCK (rise edge) 6.00 6.00clock network delay (ideal) 2.00 8.00clock uncertainty -0.50 7.50S3/P3_reg_47_/CK (DFFTRXL) 0.00 7.50 rlibrary setup time -0.28 7.22data required time 7.22Critical Path终点的Flip-Flop的时脉输入一样有2ns的network delay,所以本来1个时脉週期后(6ns)要抓取资料就变成了6+2=8ns后抓取资料,也就是Required Time(RT)变成8 ns。

静态时序分析

--于斌

报告概要

时序分析概述 时序分析中的基本概念 常用工具简介

2

概念+市场研究

结构说明和RTL编码

RTL模拟

转换时钟树到DC 形式验证 (扫描插入的网表 与CT插入的网表) 布局后STA 时序正确 是 详细布线 否

逻辑综合、优化、扫描插入 形式验证(RTL和门级) 布局前STA

7

静态时序分析-Static Timing Analysis

STA是一种验证方法 STA的前提是同步逻辑设计 STA是使用工具通过路径计算延迟的综合,并比较相对预 定义时钟的延迟 STA仅关注时序间的相对关系而不是评估逻辑功能 无需用向量去激活某个路径,而是对所有的时序路径进行 错误分析,能处理百万门级的设计,分析速度比时序仿真 工具快几个数量级,在同步逻辑情况下,可以达到100% 的时序路径覆盖 STA的目的是找出隐藏的时序问题,根据时序分析结果优 化逻辑或约束条件,使设计达到时序闭合(timing closure)

39

40

PrimeTime

建立时间检查

clock delay1- clock delay2+max data path+tSU≦clock period Max data path是寄存器的tCO加上寄存器间的组合逻辑延迟

41

建立时间检查

clock delay1=0ns clock delay2=0ns max data path=tco+path delay=1.449ns+0.258ns=1.707ns 若T=4ns,则slack=4ns-1.707ns=2.293ns

静态时序分析

静态时序分析(Static Timing Analysis)技术是一种穷尽分析方法,用以衡量电路性能。

它提取整个电路的所有时序路径,通过计算信号沿在路径上的延迟找出违背时序约束的错误,主要是检查建立时间和保持时间是否满足要求,而它们又分别通过对最大路径延迟和最小路径延迟的分析得到。

静态时序分析的方法不依赖于激励,且可以穷尽所有路径,运行速度很快,占用内存很少。

它完全克服了动态时序验证的缺陷,适合进行超大规模的片上系统电路的验证,可以节省多达20%的设计时间。

PT是Synopsys的sign-off quality的STA工具,是一个单点的全芯片、门级静态时序分析器。

PrimeTime工作在设计的门级层次,并且和Synopsys其它工具整合得很紧密。

基本特点和功能:建立和保持时间的检查(setup and hold checks)时钟脉冲宽度的检查门控时钟检查(clock-gating checks)recovery and removal checksunclocked registers未约束的时序端点(unconstrained timing endpoints)multiple clocked registers组合反馈回路(combinational feedback loops)基于设计规则的检查,包括对最大电容、最大传输时间、最大扇出的检查等。

设置设计环境设置查找路径和链接路径The search_path variable specifies a list of directory pathsthatPrimeTime uses to find the designs, libraries, and other files.The link_path variable specifies a list of libraries that PrimeTime uses tolink designs读入设计(和库文件)链接顶层设计对必要的操作条件进行设置,这里包括了线上负载的模型、端口负载、驱动、以及转换时间等指定时序约束(timing constraints)定义时钟周期、波形、不确定度(uncertainty)、延时(latency)指明输入输出端口的延时等设置时序例外(timing exceptions)设置多周期路径(multicycle paths)设置虚假路径(false paths)定义最大最小延时(max | min delay)无效的arcs(disable timing)进行时序分析:在作好以上准备工作的基础上,可以对电路进行静态时序分析,生成constraint reports 和path timing reports。

静态时序分析入门

静态时序分析入门1.代码分析:对程序的源代码进行静态分析,识别程序中的各种程序片段(如函数、循环、条件语句等)以及它们之间的关系。

2.构建控制流图:通过分析程序的控制结构,构建程序的控制流图。

控制流图是一种图形化表示,它将程序的执行流程以节点和边的形式表示出来。

3.构建数据流图:通过分析程序中的变量定义和使用,构建程序的数据流图。

数据流图描述了程序中数据的传递关系和依赖关系。

4.时序分析:基于控制流图和数据流图,计算各个程序片段的执行顺序和依赖关系。

通过分析程序中的并发操作、共享资源、消息传递等情况,检查是否存在时序错误。

5.错误检测和验证:根据时序分析的结果,检查程序中可能存在的并发问题、死锁等错误,并进行验证。

验证可以通过模拟程序的执行来检查时序分析的准确性,或者通过手动检查来确认错误的存在。

静态时序分析工具可以帮助开发人员快速发现程序中的时序错误,并提供相关的修复建议。

然而,静态时序分析并不能找出所有的问题,它只能检查程序中可能存在的错误。

因此,静态时序分析通常需要与其他测试技术(如动态测试)结合使用,以提高测试的覆盖率和准确性。

在使用静态时序分析进行软件测试时,需要注意以下几点:1.选择适当的工具:市面上有很多静态时序分析工具可供选择,开发人员需要根据自己的需求选择适合的工具。

一般来说,工具应具备良好的分析能力、准确性和易用性。

2.理解程序的执行流程和数据流程:静态时序分析需要对程序的执行流程和数据流程有清晰的理解。

因此,开发人员需要对程序的代码结构和逻辑有深入的了解。

3.高效使用工具:使用静态时序分析工具时,应根据具体情况进行合理的配置和参数设置,以提高工具的分析效率和准确性。

4.结合其他测试方法:静态时序分析只是软件测试过程中的一种方法,为了提高测试的全面性和准确性,还应结合其他测试技术进行综合测试。

总之,静态时序分析是一种重要的软件测试技术,它可以帮助开发人员及时发现程序中可能存在的并发问题、死锁等错误,提高软件的质量和可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

静态时序分析(Static Timing Analysis)基础及应用

◎陈麒旭

前言

在制程进入深次微米世代之后,芯片(IC)设计的高复杂度及系统单芯片(SOC)设计方式兴起。

此一趋势使得如何确保IC质量成为今日所有设计从业人员不得不面临之重大课题。

静态时序分析(Static Timing Analysis简称STA)经由完整的分析方式判断IC是否能够在使用者的时序环境下正常工作,对确保IC质量之课题,提供一个不错的解决方案。

然而,对于许多IC设计者而言,STA是个既熟悉却又陌生的名词。

本文将力求以简单叙述及图例说明的方式,对STA的基础概念及其在IC设计流程中的应用做详尽的介绍。

什么是STA?

STA的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。

以分析的方式区分,可分为Path-Based及Block-Based两种。

先来看看Path-Based这种分析方式。

如图一所示,信号从A点及B点输入,经由4个逻辑闸组成的电路到达输出Y点。

套用的Timing Model标示在各逻辑闸上,对于所有输入端到输出端都可以找到相对应的延迟时间。

而使用者给定的Timing Constraint为:

1.信号A到达电路输入端的时间点为2(AT=2,AT为Arrival Time)。

2.信号B到达电路输入端的时间点为5(AT=5)。

3.信号必须在时间点10之前到达输出端Y(RT=10,RT为Required Time)。

现在我们针对P1及P2两条路径(Path)来做分析。

P1的起始点为A,信号到达时间点为2。

经过第1个逻辑闸之后,由于此闸有2单位的延迟时间,所以信号到达此闸输出的时间点为4(2+2)。

依此类推,信号经由P1到达输出Y的时间点为7(2+2+3)。

在和上述第三项Timing Constraint比对之后,我们可以得知对P1这个路径而言,时序(Timing)是满足使用者要求的。

按照同样的方式可以得到信号经由路径B到达输出Y的时间点为11(5+1+3+2),照样和上述第三项Timing Constraint比对,我们可以得知对P2这个路径而言,Timing 是不满足使用者要求的。

对图一的设计而言,总共有6个信号路径。

对于采用Path-Based分析方式的STA 软件来说,它会对这6个信号路径作逐一的分析,然后记录下结果。

IC设计者藉由检视其分析报告的方式来判断所设计的电路是否符合给定的Timing Constraint。

由于最常用来做静态时序分析验证核可(STA Signoff)的EDA软件PrimeTime™采用Path-Based的分析方式,所以本文将以Path-Based的分析方式介绍为主。

再来看看Block-Based的分析方式。

此时时序信息(Timing Information)的储存不再是以路径为单位,而是以电路节点(Node)为单位。

由Timing Constraint我们仅能得知A节点的AT为2,B节点的AT为5以及Y节点的RT为10。

Block-Based的分析方式会找出每个节点的AT和RT,然后比对这两个数值。

当RT的值大于AT时表示信号比Timing Constrain中要求的时间还早到达,如此则Timing是满足的,反之则不满足。

STA资料准备

在做STA之前,我们必须对其准备工作有充分的了解。

STA所需的资料如图三所示,以下我们分项说明。

其中Design Data部分,由于Block Model和STA软件相关性太高,我们不在此加以说明,请直接参阅您STA软件的使用手册。

图三

Library Data:

STA所需要的Timing Model就存放在标准组件库(Cell Library)中。

这些必要的时序信息是以Timing Arc的方式呈现在标准组件库中。

Timing Arc定义逻辑闸任两个端点之间的时序关系,其种类有Combinational Timing Arc、Setup Timing Arc、Hold Timing Arc、Edge Timing Arc、Preset and Clear Timing Arc、Recovery Timing Arc、Removal Timing Arc、Three State Enable & Disable Timing Arc、Width Timing Arc。

其中第1、4、5、8项定义时序延迟,其它各项则是定义时序检查。

图四

Combinational Timing Arc是最基本的Timing Arc。

Timing Arc如果不特别宣告的话,就是属于此类。

如图四所示,他定义了从特定输入到特定输出(A到Z)的延迟时间。

Combinational Timing Arc的Sense有三种,分别是inverting(或 negative unate),non-inverting(或 positive unate)以及non-unate。

当Timing Arc相关之特定输出(图四Z)信号变化方向和特定输入(图四A)信号变化方向相反(如输入由0变1,输出由1变0),则此Timing Arc为inverting sense。

反之,输出输入信

号变化方向一致的话,则此Timing Arc为non-inverting sense。

当特定输出无法由特定输入单独决定时,此Timing Arc为non-unate。

图五

图六 图七

图八 图九 图十 图十一 图十二

其它的Timing Arc说明如下。

Setup Timing Arc:定义序向组件(Sequential Cell,如Flip-Flop、Latch等)所需的Setup Time,依据Clock上升或下降分为2类(图五)。

Hold Timing Arc:定义序向组件所需的Hold Time,依据Clock上升或下降分为2类(图六)。

Edge Timing Arc:定义序向组件Clock Active Edge到数据输出的延迟时间,依据Clock上升或下降分为2类(图七)。

Preset and Clear Timing Arc:定义序向组件清除信号(Preset或Clear)发生后,数据被清除的速度,依据清除信号上升或下降及是Preset或Clear分为4类(图八)。

这个Timing Arc通常会被取消掉,因为它会造成信号路径产生回路,这对STA而言是不允许的。

Recovery Timing Arc:定义序向组件Clock Active Edge之前,清除信号不准启动的时间,依据Clock上升或下降分为2类(图九)。

Removal Timing Arc:定义序向组件Clock Active Edge之后,清除信号不准启动的时间,依据Clock上升或下降分为2类(图十)。

Three State Enable & Disable Timing Arc:定义Tri-State组件致能信号(Enable)到输出的延迟时间,依据Enable或Disable分为2类。

(图十一)Width Timing Arc:定义信号需维持稳定的最短时间,依据信号维持在0或1的位准分为2类。

(图十二)

上文列出了标准组件库内时序模型的项目,但对其量化的数据却没有加以说明。

接下来,我们就来看看到底这些时序信息的确实数值是如何定义在标准组件库中的。

以Combinational Timing Arc为例,信号从输入到输出的延迟时间可以描述成以输入的转换时间(Transition Time)和输出的负载为变量的函数。

描述的方式可以是线性的方式,如图十三所示。

也可以将这2个变量当成指针,建立时序表格(Timing Table),让STA软件可以查询出正确的延迟时间。

这种以表格描述的方式会比上述线性描述的方式准确许多,因此现今市面上大部分的标准组件库皆采用产生时序表格的方式来建立Timing Model。