fly-by,不可不知的两大布线细节

FLYBACK设计

FLYBACK设计FLYBACK(又称为回放式电源转换器或反馈电源回路)是一种常见的开关电源拓扑结构,它是一种离散电源转换器,为DC-DC电路提供稳定的输出电压。

FLYBACK设计需要考虑的因素包括输入电压范围、输出电压和电流要求、功率损耗、稳定性和效率等。

FLYBACK基本原理是通过变压器进行能量传递。

变压器由输入端的电感、输出端的电感和绕组匝数的比值组成。

当开关管导通时,电感储存能量;当开关管关断时,能量通过二极管传递给输出端。

通过调整开关管的导通时间,可以实现输出电压的调节。

FLYBACK设计的第一步是确定输入电压范围和输出电压要求。

输入电压范围通常由您的应用需求决定,而输出电压需要根据所驱动的负载电路来选择。

例如,如果需要驱动一组LED灯,输出电压应与LED的电压匹配。

您可能还需要考虑到电压的调整范围和调整精度。

第二步是选择适当的电力元件,如变压器、开关管和二极管等。

变压器的匝比决定了输入电压和输出电压的比例,因此需要根据输出电压来选择合适的变压器。

开关管的选择也很重要,您需要选择具有适当承载电流和开关频率的开关管。

二极管应具有足够的反向耐压和快速恢复时间。

第三步是设计控制电路。

控制电路的作用是实时监测输出电压并调整开关管的导通时间。

一种常见的控制电路是基于反馈的控制方法。

它通常由比较器、误差放大器和PWM控制器组成。

误差放大器通过比较设定值和实际输出电压来产生误差信号,然后传递给比较器。

比较器会将误差信号与参考信号进行比较,并产生PWM信号,控制开关管的导通时间。

最后一步是进行性能和稳定性分析。

您需要进行电路稳定性、转换效率和功率损失等方面的计算和测试。

这些分析可以帮助您优化设计,提高转换效率并降低功率损耗。

总之,FLYBACK设计需要考虑输入输出电压、功率因数校正、电流调节、短路保护、过电压保护等各项设计指标。

通过选择适当的电力元件,设计合适的控制电路并进行性能和稳定性分析,可以实现高效且稳定的DC-DC电路。

fly back电路原理

fly back电路原理Flyback电路原理解析1. 引言在电子领域中,Flyback电路是一种常见的开关电源电路。

它通过电感和开关管来实现能量存储和转换,被广泛应用于各种电子设备中。

本文将从浅入深,逐步解释Flyback电路的相关原理。

2. Flyback电路概述Flyback电路是一种基于能量存储原理的开关电源电路。

它由输入电源、开关管、变压器和输出负载组成。

其基本原理是:通过开关管周期性地将输入电流进行开关,使得能量储存在变压器的磁场中,然后通过缓冲电容和输出负载实现电能的转换。

3. Flyback电路的工作原理Flyback电路的工作原理可以归纳为以下几个关键步骤:断开开关管当开关管断开时,输入电源与变压器之间没有电流流动。

此时,由于变压器的磁场储能,其两端的电流不会突变,而是逐渐减小。

开关管闭合当开关管闭合时,输入电源与变压器之间建立起电流。

此时,变压器的磁场能量开始转化为电流能量,使得变压器两端的电流迅速增加。

磁场崩溃在开关管闭合的过程中,当输入电流持续流入时,变压器的磁场能量逐渐积累。

然而,当开关管断开时,输入电流突然中断,使得磁场能量无法继续储存。

这时,磁场能量会以感应电动势的形式引发在变压器绕组中产生电压。

能量转移由于断开开关管后的崩溃磁场引发的感应电动势,变压器绕组上的电压会增大,甚至达到输出负载所需的电压。

随后,该电压通过输出电路传递给负载。

同时,输出电路中的缓冲电容会储存一部分能量,以保持输出电压的稳定性。

4. Flyback电路的特点Flyback电路具有以下几个突出的特点: - 隔离性:由于变压器的存在,输入电源与输出负载之间可以实现电气隔离。

- 多输出:通过合理设计变压器绕组,Flyback电路可以实现多路输出。

- 反馈控制:通过添加反馈控制回路,可以实现对输出电压、电流等参数的精确控制。

- 高效性:Flyback电路具备较高的能量转换效率,能够满足不同应用场景的要求。

不是所有DDR3都可以用Fly by结构

不是所有DDR3都可以用Fly by结构!趁着时间还早,打开电脑正想百度下今天是什么好日子,突然桌上的电话铃声叮叮叮叮的响起来了,平时很少响的电话一大早怎么会有人找呢,不会打错电话了吧。

我索性拿起电话,原来是公司分部的设计人员小A。

小A说他最近摊上大事了,正急得满头大汗呢,希望我能给他找找原因,原来事情是这样的:前不久小A设计了一块单板,单板很简单,上面有一个主控芯片拖着2片DDR3颗粒,客户也没有任何要求,就说按照常规布线即可。

小A也觉得这个设计很简单,凭着自己好几年的设计经验那还不是小菜一碟、信手拈来之事,所以也没有太多顾虑,三下五除二就完工了,DDR3布线,常规还不就是用Fly_by拓扑,走线简单又省空间,哈哈,等着拿奖金吧。

最近板子进入调试阶段,DDR3系统却死活运行不到额定频率,还老是死机,但是降频又能正常工作,各种办法用尽也无济于事,客户只好又来找小A,怀疑是不是PCB板设计有问题,小A此时也摸不着头脑,这么简单的板子怎么可能有问题呢,自己都是按照公司设计规范来做的啊,如果有问题那不是规范有问题?所以小A在束手无策的情况下也就只好找到我们制定规范的SI工程师了。

听了小A的描述,DDR3运行不到额定频率,但降频却工作正常,第一反应是时序问题,肯定是什么影响到了DDR3的时序。

小A也算是经验较丰富的设计人员了,对于等长、线间距及电源设计等注意事项应该是烂熟于心的,而且公司也会不定期的培训,查板后也排除了这些问题,板子见如下图一所示。

图一看来要查看芯片手册了,打开芯片功能规范手册,直接找到DDR控制器部分,下面这句话真是亮瞎了我的“24K钛合金火眼金睛”:问题找到了,原来这个主控芯片不支持读写平衡功能!既然不支持读写平衡功能,那么这个设计就不能使用Fly_by的拓扑结构,这确实是典型的疏忽大意。

由于无法修改主控芯片内部的参数,也不想降频使用,看来只能使用T型拓扑改版了,可惜啊,小A的疏忽大意差点酿成了大错,还好客户只是前期的小批量测试版本。

DDRx技术介绍-Write leveling、Fly_by拓扑、DBI功能与POD电平

DDRx的技术介绍-Write leveling、Fly_by拓扑、DBI功能与POD电平原创:此文由一博科技原创,转载请注明出处。

Write leveling功能与Fly_by拓扑Write leveling功能和Fly_by拓扑密不可分。

Fly_by拓扑主要应用于时钟、地址、命令和控制信号,该拓扑可以有效的减少stub的数量和他们的长度,但是却会导致时钟和Strobe信号在每个芯片上的飞行时间偏移,这使得控制器(FPGA或者CPU)很难保持tDQSS、tDSS 和tDSH这些参数满足时序规格。

因此write leveling应运而生,这也是为什么在DDR3里面使用fly_by结构后数据组可以不用和时钟信号去绕等长的原因,数据信号组与组之间也不用去绕等长,而在DDR2里面数据组还是需要和时钟有较宽松的等长要求的。

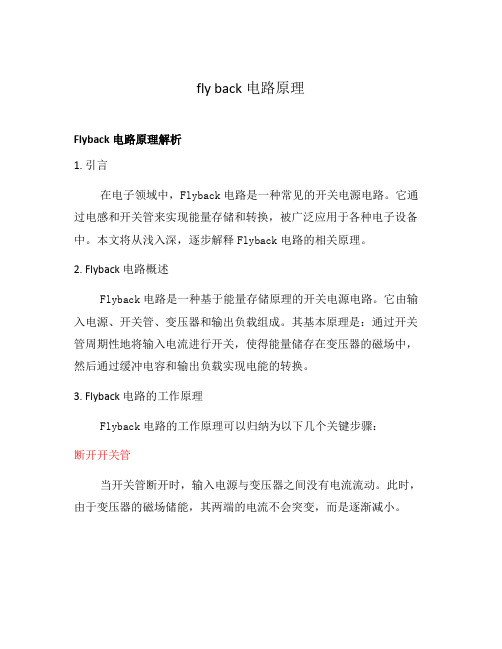

DDR3控制器调用Write leveling功能时,需要DDR3 SDRAM颗粒的反馈来调整DQS与CK之间的相位关系,具体方式如下图一所示。

图一、 Write levelingWrite leveling 是一个完全自动的过程。

控制器(CPU或FPGA)不停的发送不同时延的DQS 信号,DDR3 SDRAM 颗粒在DQS-DQS#的上升沿采样CK 的状态,并通过DQ 线反馈给DDR3 控制器。

控制器端反复的调整DQS-DQS#的延时,直到控制器端检测到DQ 线上0 到1 的跳变(说明tDQSS参数得到了满足),控制器就锁住此时的延时值,此时便完成了一个Write leveling过程;同时在Leveling 过程中,DQS-DQS#从控制器端输出,所以在DDR3 SDRAM 侧必须进行端接;同理,DQ 线由DDR3 SDRAM 颗粒侧输出,在控制器端必须进行端接;需要注意的是,并不是所有的DDR3控制器都支持write leveling功能,所以也意味着不能使用Fly_by 拓扑结构,通常这样的主控芯片会有类似以下的描述:DBI功能与POD电平DBI的全称是Data Bus Inversion数据总线反转/倒置,它与POD电平密不可分,它们也是DDR4区别于DDR3的主要技术突破。

DDR3FlyBy走线精讲

DDR3FlyBy⾛线精讲泪痕⼀互联拓扑结构互联拓扑结构的选择,直接决定DDR 布线结构和DDR 信号完整性。

常见的拓扑结构有:点对点拓扑(Point-to-Point Scheduling)该拓扑结构简单,整个⽹络的阻抗特性容易控制,时序关系也容易控制,常见于⾼速双向传输信号线;常在源端加串电阻来防⽌源端的⼆次反射。

菊花链结构(Daisy Chain Scheduling)如图 3.3-1,菊花链结构也⽐较简单,阻抗也⽐较容易控制。

菊花链的特征就是每个接收端最多只扣2个另外的接收端/发送端项链,连接每个接收端的stub 线较短。

该结构的阻抗匹配常在终端做。

Fly-By Scheduling 结构如图3.3-2,该结构是特殊的菊花链结构,是stub 线为0的菊花链。

不同于DDR2的T 形分⽀拓扑结构,DDR3采⽤了fly-by 拓扑结构,以更⾼的速度提供更好的信号完整性。

fly-by 信号是命令、地址、控制和时钟信号线。

树形拓扑结构(Tree Scheduling)该结构看起来⽐较简单,但阻抗不容易控制,如图3.3-3所⽰图3.3-1 Daisy Chain图3.3-2 Fly By 图3.3-3 Tree 对于DDR2和DDR3,其中数据线都是点对点的互联⽅式,很容易通过ODT 功能来实现阻抗匹配。

⽽对于地址线、命令线、控制线和时钟线,它们都是需要多点互联的,所以需要⼀个合适的拓扑结构。

对于DDR3,上述结构中树形结构、菊花链结构和Fly-By 结构都适⽤,但前提条件是⾛线要尽可能的短。

Fly-By 拓扑结构在处理噪声⽅⾯,具有很好的信号完整性,然⽽在⼀块4层板上很难实现Fly-By 结构,需要6层以上的板⼦,⽽菊花链式拓扑结构在⼀块4层板上要容易实现⼀些。

⽽树形拓扑结构要求AB 和AC 的长度⾮常接近,考虑到信号完整性,要求尽可能的提⾼分⽀⾛线长度,同时⼜要满⾜板层的约束要求。

在4层板的DDR3设计中,最合理的拓扑结构就是带有最少桩线的菊花链拓扑结构。

flyback原副边电流关系 -回复

flyback原副边电流关系-回复Flyback变压器是一种常见的开关电源变压器,广泛应用于各种电子设备中。

它的工作原理与普通变压器有所不同,其中一个重要的关系就是其原边和副边电流之间的关系。

本文将一步一步回答关于flyback原副边电流关系的问题。

Flyback变压器的结构和原理首先,让我们了解一下Flyback变压器的结构和工作原理。

Flyback变压器主要由一个磁性芯、一个原边线圈和一个副边线圈组成。

原边线圈由交流电源驱动,副边线圈则通过开关管控制以产生输出电压。

当开关管导通时,原边线圈会储存能量,而当开关管关闭时,储存的能量通过磁耦合传输到副边线圈。

Flyback变压器的开关周期Flyback变压器的工作周期分为两个阶段:导通阶段和断开阶段。

在导通阶段,开关管导通,原边线圈储存能量;而在断开阶段,开关管关闭,储存的能量通过磁耦合传输到副边线圈。

这两个阶段的时间比例称为开关周期。

开关周期的长度由开关管的导通时间和断开时间决定。

Flyback原边电流当开关管导通时,原边线圈会接收电源的电流,并将其转化为磁能。

根据电流连续性原理,原边电流的平均值与副边电流的平均值应相等,即:I_primary_avg = I_secondary_avg其中,I_primary_avg代表原边电流的平均值,I_secondary_avg代表副边电流的平均值。

Flyback副边电流当开关管关闭时,存储在原边线圈中的能量通过磁耦合传输到副边线圈。

副边电流的变化与原边电流的变化成反比,即原边电流下降,副边电流增加。

这是由于变压器的能量守恒原理所决定的。

根据变压器的能量守恒原理:V_primary_avg ∙ I_primary_avg ∙ t = V_secondary_avg ∙I_secondary_avg ∙ t其中,V_primary_avg代表原边电压的平均值,V_secondary_avg代表副边电压的平均值,t代表开关周期的长度。

T型及FLY-BY拓扑之应用总结

拓扑和端接知多少T型及Fly_by拓扑之应用总结前面的文章有分别介绍过T型拓扑及Fly_by拓扑结构,这两种拓扑结构应用最多的应该是在DDR3里面,说到这里,小编又想开始聊聊DDR3的设计了,我想很多人都比较有兴趣。

因为DDR3的设计还是比较复杂,而且应用也比较广泛,如下图是常见的T型及Fly_by 型的拓扑应用。

通常来讲,谈到DDR3的拓扑结构(这里主要是针对时钟或地址控制信号),大家马上就会想到T型或者Fly_by结构,但什么时候使用T型或者Fly_by型呢?答案是:it depends!(如果大家有经常参加老外的培训,这应该是个用得最多的回答了,可见老外也是比较狡猾的)。

这个问题确实是没法确切回答的,因为要看情况,小编在此也来试着把这个问题回答得更具体点。

首先,从颗粒数目的情况来考虑。

一般在4个或者4个以下的拓扑,使用T型或者Fly_by型都没有太大问题,主要看个人喜好了,如果板子布线空间足够的话,还是建议使用T型拓扑,信号质量也不赖,后期调试也较简单;如果颗粒数目超过4个,那么果断使用Fly_by拓扑,不要问我为什么,等你去绕等长的时候你就知道为什么要用Fly_by拓扑了。

其次,从布线空间来考虑。

板内布线空间较充裕,有足够的空间绕等长,可以使用T型拓扑,如果板内布线空间较紧张,没有足够空间绕等长,那么还是使用Fly_by拓扑。

再次,从信号速率来考虑。

一般T型拓扑频率超过1GHz信号质量就会出现大幅的下降,所以此时应考虑使用fly_by拓扑结构。

当然,使用何种拓扑并不是单一情况的考虑,而是综合的一个考虑,就像前面说到的需要综合考虑颗粒数目、板内布线空间、信号速率以及个人喜好(或者对各拓扑的熟悉程度)等。

下面来简单总结下T型拓扑和Fly_by拓扑的优缺点以及使用注意事项。

T型拓扑结构的特点是主控到每个颗粒的长度基本一致,也就是说每个颗粒的信号质量都差不多;缺点就是绕等长时需要更多的布线空间,所以不适合较多颗粒数目的情况,其次是需要同等地位的分支完全对称(包括长度及阻抗等),如果不对称那么信号质量的影响比较大。

Flyback电路及其Layout

4.660ms

4.680ms

VQ1

-GS

IC2

ID5

ID7

4.700ms 4.715ms

IQ1

2.3 Snubber电路电流波形及时序关系

500mA

250mA SEL>>

0A

4.0A

I(R3)

0A

-4.0A I(C3)

2.5A 0A I(D7)

5.0A

0A IC(Q1)

5.0A 2.5A

0A 7.25ms I(TX1:1)

TR = 0.1u

TF = 0.1u

PW = 10u

PER = 50u

IXGM20NI 60A

0

V

D5

MUR890 I

C2 I

R1

1000u

30

0

图1.1

1.2.当开关管Q1 off时的电流路径,如下图1.2:

V+

D1

V1

VOFF = 0 VAMPL = 310v

I

FREQ = 50Hz

MUR890 D3

MUR890 I

V-

0

K K8

E25_13_7_3E25

COUPLING=0.95

1

D2

MUR890 I

R3 C3 800 0.1u

L1

2

300

L2

20

D6

2

D4

1

MUR890

C1

V

220u

MUZR1890 I

I

R2

V1 = 0 V2 = 20v

V2 10

TD = 0.1u

TR = 0.1u

TF = 0.1u

PCB板布线的规则和技巧

PCB板布线的规则和技巧在PCB板设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的。

在整个PCB板设计中,以布线的设计过程限定最高,技巧最细、工作量最大。

PCB板布线分单面布线、双面布线及多层布线。

PCB板布线的方式也有两种:自动布线及交互式布线。

在自动布线之前,可以用交互式预先进行要求比较严格的布线。

输入端与输出端的边线应避免相邻平行,以免产生反射干扰,必要时应加地线隔离。

两相邻层的布线要互相垂直,平行容易产生寄生耦合。

PCB板自动布线的布通率,依赖于良好的PCB板布局,布线规则可以预先设定,包括走线的弯曲次数、导通孔的数目、步进的数目等。

一般先进行探索式布经线,快速地把短线连通,然后进行迷宫式布线,先把要布的连线进行全局的布线路径优化,它可以根据需要断开已布的线,并试着重新再布线,以改进总体效果。

对目前高密度的PCB板设计已感觉到贯通孔不太适应了,它浪费了许多宝贵的布线通道,为解决这个问题,出现了盲孔和埋孔技术。

它不仅完成了导通孔的作用,还省出许多布线通道,使布线过程完成得更加流畅,更加完善。

PCB板设计过程是一个复杂而又简单的过程,要想很好地掌握它,还需电子工程设计人员去自已体会,总结经验。

1、电源、地线的处理在整个PCB板设计中,即使布线完成得都很好,但因为电源、地线的考虑不周到而引起的干扰,会使产品的性能下降,有时甚至影响到产品的成功率。

所以对电源、地线的布线要认真对待,把电源、地线所产生的噪音干扰降到最低限度,以保证产品的质量。

对每个从事电子产品设计的工程人员来说都明白地线与电源线之间噪音所产生的原因,现只对降低式抑制噪音作以表述。

众所周知的是在电源、地线之间加上去耦电容。

尽量加宽电源、地线宽度,最好是地线比电源线宽,它们的关系是:地线>电源线>信号线,通常信号线宽为:0.2~0.3mm,最经细宽度可达0.05~0.07mm,电源线为1.2~2.5 mm,对数字电路的PCB可用宽的地导线组成一个回路,即构成一个地网来使用(模拟电路的地不能这样使用) 用大面积铜层作地线用,在印制板上把没被用上的地方都与地相连接作为地线。

DDR3 fly-by拓扑设计

DDR3 fly-by 拓扑设计作者:汉普电子随着数字存储设备数据传输速率越来越快,拓扑结构对于信号质量的影响越来越大,对于DDR3数据传输速率已经达到1600Mbps 以上,设计采用fly-by 拓扑结构,但是在使用的过程中我们需要注意一些问题,否则会带来严重的信号完整性和时序问题,导致设计跑不到想要的高速率。

Fly-by 拓扑要求stub 走线很短,当stub 走线相对于信号边沿变化率很短时,stub 支线和负载就可以看作电容,该电容的大小为stub 电容和硅片I/O 电容的总和。

当存储颗粒沿分支均匀分布,且各存储颗粒之间的电气时延相比于信号上升/下降时间较小时,stub 和硅片引入的电容会显示出分布式效应,从而改变分支走线处的传输线特征阻抗和传播速度。

下图描绘了传输线上若干抽头对应的分布式容性负载。

对于容性负载均匀的总线,其等效阻抗由下面的公式计算分布式容性负载的影响X NC C L Z L /'0+=其中,L 和C 是分布式传输线的寄生效应,C L 是负载的总电容,N 是负载的数量,X 是分布式负载对应的传输线长度,即分支长度。

从上面公式可以看出,负载引入的电容,实际被分摊到了走线上,所以造成走线的单位电容增加,从而降低了走线的有效阻抗。

所以在设计中,我们应该将负载部分的走线设计为较高的阻抗,经过负载电容的平均后,负载部分的走线才会和主线段阻抗保持一致,从而达到阻抗连续,降低反射的效果。

下面用Hampoo 在实际中的一个DDR3设计案例,来分析对比采用高阻抗负载走线和采用主线和负载走线同阻抗两种情况的差异。

如上图,Case1采用的是从内层控制器到各个SDRAM均为50ohm的阻抗设计。

Case2则采用了主线40ohm,负载线60ohm的设计。

对此通过仿真工具进行对比分析。

从以上仿真波形可以看出,使用较高阻抗负载走线的Case2在信号质量上明显优于分支主线都采用同一种阻抗的Case1设计。

fly-by的拓扑结构

fly-by的拓扑结构

fly-by 拓扑结构的优点是布线相对简单,其中数据组不需要和时钟信号绕等长,这样就可以节省较多的布线空间,同时也可以支持更高的信号速率;缺点就是信号到达每片颗粒的时间不一致,带来了一定的skew,这个skew需要一定的技术来弥补。

fly-by拓扑是针对DDR3的时钟、地址控制和命令信号而言,数据信号就不存在fly-by拓扑的说法。

时钟(CK.CK#)、地址(A15~A0)、控制和命令信号(RAS#,CAS#,WE#)。

对fly-by拓扑影响最大的是主干到颗粒的那段Stub线,所以必须严格控制stub的长度(时钟信号100mil左右,地址、控制等信号150mil 左右),这个长度当然是越短越好。

可见颗粒与颗粒间的长度影响也不及stub的影响大,但太长了对信号还是有一定的影响,所以根据板内空间及信号质量的综合考虑,我们建议颗粒与颗粒的长度控制在1inch(1000mil)内较好。

另外不管是T型拓扑还是Fly_by拓扑,还需要考虑合理的端接,常用的端接方式是T型拓扑在第一个分支节点处上拉50欧姆或其他端接电阻到Vtt,而Fly_by则是在最后一个颗粒处上拉50欧姆或其他端接电阻到Vtt;除了端接电阻,其实当颗粒数目较多时,都可以将两种拓扑的主干线路阻抗降低到40欧姆左右(主网络走线要比到各个分支走线粗,称为容性负载补偿),这样有利于提升信号的质量。

如果主控芯片不支持读写平衡功能,则必须用T型(DDR1/DDR2)。

Altium Designer实战攻略与高速PCB设计16

《Altium Designer实战攻略与高速PCB设计》 第十六章 DDR3的PCB设计 书籍专区:

布局操作

将PCB的原点设置在CPU中心。 然后将设计栅格和显示栅格都设置为0.4mm,并将两片

DDR3根据CPU的位置进行对称放置。

布线思路和操作

布线思路和操作

1.电源和地网络的扇出

布线思路和操作

2.地址、命令网络的扇出

布线思路和操作

3.数据线互连 布线顺序:DQS差分→DQ数据线。

4.差分时钟、地址、命令线互连 布线顺序:差分时钟→地址ls等长设置

布线思路和操作

6、等长 数据线等长布线的先后顺序:差分时钟线→DQS差分→数据 线。 (1)处理差分时钟线的等长。 (2)处理DQS差分线的等长。 (3)处理DQ数据线的等长。

Q&A

Thank You

布局思路

从CPU的管脚网络分布中可以看到,地址 和命令线主要分布在CPU的左侧,而CPU 的上方是低位和高位的数据总线。

在布局时,应将两片DDR3根据CPU的位 置来进行中心对称布局。同时,PCB的左 侧应留出地址和命令线的布线空间。

另外,由于DDR3是0.8mm pitch的BGA封 装,在布局时我们可以将设计栅格设置为 0.4mm。这样两片DDR3在布局时就可以 摆放在格点上,在手工布线时有利于过孔 和布线的过齐,显得整齐美观。

内容提要

• • • • • DDR3介绍 DDR3 Fly-by设计 布局思路 布局操作 布线思路和操作

PCB布线规则与技巧

PCB布线规则与技巧PCB(Printed Circuit Board,印刷电路板)布线是电子产品设计中非常重要的一项工作,它决定了电路的性能和可靠性。

正确的布线可以确保信号传输的稳定性,降低噪音干扰,提高产品的工作效率和可靠性。

下面将介绍一些常用的PCB布线规则与技巧。

1.保持信号完整性:信号完整性是指信号在传输过程中不受噪音、串扰等干扰影响,保持原有的稳定性。

为了保持信号完整性,应尽量减少信号线的长度和走线面积,减少信号线与功率线、地线等的交叉和平行布线。

同时,在高速信号线上使用传输线理论进行布线,如匹配阻抗、差分信号布线等。

2.分离高频和低频信号:为了避免高频信号的干扰,应将高频信号线与低频信号线分开布线,并保持一定的距离。

例如,在布线时可以采用地隔离层将不同频率的信号线分离或者采用地隔离孔将不同频率的信号线连接到不同的地层。

这样可以减少高频信号的串扰和干扰。

3.合理布局:布线时应合理规划电路板的布局,将功率线和地线尽量靠近,以减少电磁干扰。

同时,尽量避免信号线与功率线、地线等平行布线,减少互穿引起的干扰。

在设计多层板时,还要考虑到信号引线的短暂电容和电感,尽量减小信号线长度,以减少信号传输时的延迟。

4.适当使用扩展板和跳线:在复杂的PCB布线中,有时无法直接连接到目标位置,这时可以使用扩展板或跳线来实现连接。

扩展板是一个小型的PCB板,可以将需要连接的器件布线到扩展板上,再通过导线连接到目标位置。

跳线可以直接用导线连接需要的位置,起到连接的作用。

但是,在使用扩展板和跳线时要注意保持信号完整性,尽量缩短导线长度,避免干扰。

5.优化地线布局:地线是电路中非常重要的部分,它不仅提供回路给电流,还能减少电磁干扰和噪音。

在布线时应保证地线的连续性和稳定性,地线应尽量靠近功率线,对于高频信号,还应采用充足的地平面来隔离。

同时,地线的走线应尽量短且直,减少环状或绕圈的走线。

6.合理规划电源线:电源线的布线要尽量靠近负载,减小电流环形和接地环形。

英语热词:flyby 飞掠

Pluto1 shows a "heart" in a most detailed2 photo yet returned by NASA's approaching New Horizons probe, which has now begun its final run for its historic flyby of Pluto.美国宇航局发射的“新视野”号探测器即将传回的一张冥王星清晰照片上竟有一块心形的图案,“新视野”号当时正在最后一次历史性飞掠冥王星。

In the early morning hours on Wednesday, mission scientists received the clearest image of the reddish-brownish dwarf3 planet by the Long Range Reconnaissance Imager (LORRI) aboard New Horizons, NASA said in a statement.美国宇航局在一份声明中表示,15日凌晨时分,该行动的科学家收到了“新视野”号上的远距离勘测成像仪拍摄到的最为清晰的一张冥王星的照片。

Flyby指航天器的近天体探测飞行(a flight made by a spacecraft over a particular place in order to record details about it),通常称为“飞掠”。

1 Pluton.冥王星参考例句:Pluto is the furthest planet from the sun.冥王星是离太阳最远的行星。

Pluto has an elliptic orbit.冥王星的轨道是椭圆形的。

2 detailedadj.详细的,详尽的,极注意细节的,完全的参考例句:He had made a detailed study of the terrain.他对地形作了缜密的研究。

PCB拓扑结构

PCB拓扑结构常见的拓扑结构有:1.点对点拓扑point-to-point scheduling 该拓扑结构简单,整个网络的阻抗特性容易控制,时序关系也容易控制,常见于高速双向传输信号线;常在源端加串行匹配电阻来防止源端的二次反射。

2.菊花链结构daisy-chain scheduling 如下图所示,菊花链结构也比较简单,阻抗也比较容易控制。

菊花链的特征就是每个接收端最多只和2个另外的接收端/发送端项链,连接每个接收端的stub线需要较短。

该结构的阻抗匹配常在终端做,用戴维南端接比较合适。

3. fly-by scheduling 该结构是特殊的菊花链结构,stub线为0的菊花链。

不同于DDR2的T 型分支拓扑结构,DDR3采用了fly-by拓扑结构,以更高的速度提供更好的信号完整性。

fly-by信号是命令、地址,控制和时钟信号。

如下图所示,源于存储器控制器的这些信号以串行的方式连接到每个DRAM器件。

通过减少分支的数量和分支的长度改进了信号完整性。

然而,这引起了另一个问题,因为每一个存储器元件的延迟是不同的,取决于它处于时序的位置。

通过按照DDR3规范的定义,采用读调整和写调整技术来补偿这种延迟的差异。

fly-by拓扑结构在电源开启时校正存储器系统。

这就要求在DDR3控制器中有额外的信息,允许校准工作在启动时自动完成。

在写调整期间,存储器控制器需要补偿额外的跨越时间偏移(对每个存储器器件,信号延迟是不同的),这是由于fly-by拓扑结构及选通和时钟引入的。

源CK和DQS信号到达目的地有延迟。

对于存储器模块的每个存储器元件,这种延迟是不同的,必须逐个芯片进行调整,如果芯片有多于一个字节的数据,甚至要根据字节来进行调整。

该图说明了一个存储器元件。

存储器控制器延迟了DQS,一次一步,直到检测到CK信号从0过渡到到1。

这将再次对齐DQS和CK,以便DQ总线上的目标数据可以可靠地被捕获。

由于这是由DDR3存储器控制器自动做的,电路板设计人员无须担心实施的细节。

PHY芯片布局布线注意事项

PHY芯片布局布线注意事项:

1、推荐使用4层PCB板从顶层到底层:主要信号层、地层、电源层、信号层;

2、网络变压器尽量靠近RJ45或DB9端子;

3、50Ω电阻终端电阻尽量靠近PHY芯片的RXI+/-和TXO+/-引脚;

4、优先布RXI+/-和TXO+/-线对,尽量保持线对平行、等长、短距,避免过孔、交叉;

5、若空间足够,考虑在RXI+/-和TXO+/-线对间布保护地线,保护地线必须每隔一段距离

要有接地孔;

6、在网络接口布线区域PHY+网络变压器+RJ45/DB9端子应避免除网络信号以外的其它

信号线;

7、网络变压器至RJ45/DB9端子区域不能有任何电源或地平面,如图2示;

8、信号线远离大地chassis ground,如图2示;

9、RJ45/DB9端子金属外壳和未用引脚通过电阻网络和2KV旁路电容连接至大地,如图1

示;

10、Band Gap电阻±1%尽量靠近PHY芯片引脚,并在此电阻附近不要走高速信号线,如图

1示;

11、AVCC与DVCC用磁珠连接75Ω,100MHz,磁珠的每一边用10uf旁路电容连接至地,参

考图3;

12、PHY芯片每个电源引脚接两个退耦电容,和各一个,退耦电容必须尽量靠近电源焊盘;

13、网络变压器中心抽头AVDD和AGND之间布一个的退耦电容,且使退耦电容尽量靠近

中心抽头;

14、PHY芯片所有模拟地引脚PIN 5,6,46不能直接短接,直接连到模拟地平面上;

15、模拟地AGND、数字地DGND、大地chassis GND如何连接参见图2、3,思考原因

16、电源、地平面分割线宽度应在100mil以上;。

讲义Flyback电路原理

开始很高兴有这么一个机会,和大家一起学习和讨论Flaback电路的原理。

今天介绍的内容中,公式比较多,有些枯燥;但是经过理论推导,期望能让大家对于Flyback电路的“工作原理,伏秒平衡定律,以及 C.C.M.和D.C.M两种工作模式”等内容的理解,能更加透彻些。

Flyback转换器原理主要内容:一、Flyback电路简述二、Buck-Boost转换器原理三、Flyback转换器原理四、Flyback电路改进版本介绍附录:I Flyback变压器设计II Flyback电路的EMI分析序言Flyback转换器应用相当广泛,其原因有:从电路的角度看,Flyback电路有最少元件的特性;从设计的角度看,Flyback电路有简单高可靠度的特点;从经济的角度看,Flyback电路成本最低,醉适合一般小功率的电源使用。

在实际的应用中,用在接市电的低瓦数电源,多半用Flyback电路来实现,例如:30-40W的笔记本电脑,70-80W的个人电脑,40-50W的传真机与影像扫描机,20W以下的Adapter(适配器)……未来的电子产品讲究轻薄短小又省电,所以Flyback电路会更风行。

Flyback转换器电路是由Buck-Boost电路,利用磁性元件耦合的功能衍生而来,所以要探讨Flyback电路,必须先从Buck-Boost电路开始。

一、Flyback电路简介(一)Flyback电路架构Flyback变换器,俗称单端反激式DC-DC 变换器,又称为返驰式(Flyback)转换器,或"Buck-Boost"转换器,因其输出端在原边绕组断开电源时获得能量,因此得名.Flyback变换器是在主开关管导通期间,电路只储存而不传递能量;在主开关管关断期间,才向负载传递能量的一种电路架构。

(1)Flyback变换器理论模型如图。

(2)实际电路结构根据Flyback变压器的同名端绕制方式,有下面两种形式,这两个电路实质上是一样的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FLY-BY,你不可不知的两大布线细节

原创:一博科技,转载请注明出处。

作者听过这样一种说法,DDR的历史,就是一个SI技术变革的过程,说白了就是拓扑与端接之争。

DDR2使用的是T拓扑,发展到DDR3,引入了全新的菊花链—fly-by结构。

使用fly-by并不完全因为现在的线路板越来越高密,布局空间越来越受限,主要原因还是DDR3信号传输速率变得更快了,T 型拓扑已经不能满足高速传输的要求。

一博科技前期的文章中提到了fly-by,并且早期的文章对fly-by结构也做过一些介绍, 例如:不是所有的DDR都可以使用fly-by;为提高负载的信号质量,fly-by结构可以进行容性负载补偿…

Stub长度决定信号质量

我们经常见到的使用fly-by结构将内存颗粒串联起来的实例如图1和图2

图1

图2

图1中,stub长度约为200mil,图2stub约为20mil。

这两种做法哪种信号质量更好些呢?一博科技为此专门做仿真验证了一下。

建立如下图3拓扑结构。

图3

图3各段线阻抗都取50ohm。

只改变stub长度,四个接收端波形如下图4所示:

图4

从波形可以看出,随着stub长度的增加,波形的过冲现象越来越严重。

为更好的评估stub变长对信号带来的影响,我们将近端和远端接收端的眼图对比如下:

图5

由上图5可知,随着Stub变长,眼高逐渐变小,这再次验证了:stub越长信号质量越差。

阻抗补偿有利于改善信号质量

设计过DIMM条的小伙伴们都会注意这样一个细节,就是主网络走线要比到各个分支走线粗,如下图

图6

这么做真的可以改善信号质量?空口无凭,我们还是用仿真数据来说话。

搭建如下拓扑结构,只是改变主线段阻抗(最初阻抗都是50ohm),其他变量不变。

主线段阻抗分别取40ohm与50ohm,近端和最远端负载眼图对比如下图7,图7中蓝色眼图代表的是主干线阻抗为40ohm情况,紫色眼图代表的是主干线阻抗是50ohm的情况。

图7

由上图可知,蓝色眼图比紫色眼图张的更开,也就意味着主线段阻抗偏低信号质量会更好。

降低主线段阻抗或者提高后面分支的阻抗的确可以改善信号质量,这个方法业内把它叫做容性负载补偿。

特别是那种负载很多的结构,一条链路上串了8片或者10片DDR颗粒的,做一下容性负载补偿对提升信号质量有很大的帮助。