DDS实验报告 南理工 优秀

DDS信号发生器实验报告

DDS信号发生器一、实验目的:学习利用EDA技术和FPGA实现直接数字频率综合器DDS的设计。

二、实验原理实验原理参考教材6.4节和6.11节相关内容。

三、实验内容1、实验原理参考教材6.4节相关内容。

根据6.4.2节和例6-10,在Quartus II上完成简易正弦信号发生器设计,进行编辑、编译、综合、适配、仿真;2、使用SignalTap II测试;3、硬件测试:进行引脚锁定及硬件测试。

信号输出的D/A使用DAC0832,注意其转换速率是1μs。

下载到实验系统上,接上D/A模块,用示波器测试输出波形;4、按照教材图6-72完成DDS信号发生器设计,进行编辑、编译、综合、适配、仿真,引脚锁定及硬件测试。

5、建立.mif格式文件。

四、实验步骤1、建立.mif文件:(1)设定全局参数:(2)设定波形:(3)文件保存:2、新建工程:3、LPM—ROM定制:(1)(2)(3)(4)(5)(6)(7)sinrom源程序:module SIN_CNT(RST,CLK,EN,Q,AR); output [7:0] Q;input [6:0] AR;input EN,CLK,RST;wire [6:0] TMP;reg[6:0] Q1;reg[7:0] F;reg C;always @(posedge CLK)if(F<AR) F<=F+1;elsebeginF=8'b00;C=~C;endalways @(posedge CLK or negedge RST)if(!RST) Q1<=7'b0000000;else if(EN) Q1<=Q1+1;else Q1<=Q1;assign TMP=Q1;sinrom IC1(.address(TMP),.clock(CLK),.q(Q)); endmodule4、锁相环:5、顶层文件:6、SignalTap II的使用7、锁定引脚8、下载。

DDS 直接数字频率合成器 实验报告(DOC)

直接数字频率合成器(DDS)实验报告课程名称电类综合实验实验名称直接数字频率合成器设计实验日期2015.6.1—2013.6.4学生专业测试计量技术及仪器学生学号114101002268学生姓名陈静实验室名称基础实验楼237教师姓名花汉兵成绩摘要直接数字频率合成器(Direct Digital Frequency Synthesizer 简称DDFS 或DDS)是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术。

本篇报告主要介绍设计完成直接数字频率合成器DDS的过程。

其输出频率及相位均可控制,且能输出正弦波、余弦波、方波、锯齿波等五种波形,经过转换后在示波器上显示。

经控制能够实现保持、清零功能。

除此之外,还能同时显示出频率控制字、相位控制字和输出频率的值。

实验要求分析整个电路的工作原理,并分别说明了各子模块的设计原理,依据各模块之间的逻辑关系,将各电路整合到一块,形成一个总体电路。

本实验在Quartus Ⅱ环境下进行设计,并下载到SmartSOPC实验系统中进行硬件测试。

最终对实验结果进行分析并总结出在实验过程中出现的问题以及提出解决方案。

关键词:Quartus Ⅱ直接数字频率合成器波形频率相位调节AbstractThe Direct Digital Frequency Synthesizer is a technology based on fully digital technique, a frequency combination technique syntheses a required waveform from concept of phase. This report introduces the design to the completion of the process of direct digital frequency synthesizer DDS. The output frequency and phase can be controlled, and can output sine, cosine, triangle wave, square wave, sawtooth wave, which are displayed on the oscilloscope after conversation. Can be achieved by the control to maintain clear function. Further can simultaneously display the value of the frequency, the phase control word and the output frequency. The experimental design in the Quartus Ⅱenvironment, the last hardware test download to SmartSOPC experimental system. The final results will be analyzed, the matter will be put forward and the settling plan can be given at last.Key words:Quartus ⅡDirect Digital Frequency Synthesizer waveform Frequency and phase adjustment目录一、设计内容 (4)二、设计原理 (4)2.1 DDS概念 (4)2.2 DDS的组成及工作原理 (4)三、设计要求 (6)3.1 基本要求 (6)3.2 提高要求 (6)四、设计内容 (6)4.1 分频电路 (6)4.2 频率预置与调节电路 (10)4.3 累加器 (12)4.4 波形存储器(ROM) (13)4.5 测频电路 (19)4.6 译码显示电路 (21)4.7 消颤电路 (22)4.8 总电路 (23)五、电路调试仿真与程序下载 (24)六、示波器波形图 (25)七、实验中遇到的问题及解决方法 (25)八、电路改进 (26)九、实验感想 (28)十、参考文献 (28)一、设计内容设计一个频率及相位均可控制的具有正弦和余弦输出的直接数字频率合成器(Direct Digital Frequency Synthesizer 简称DDFS 或DDS)。

DDS实验报告 南理工

南京理工大学——DDS实验报告姓名:学号:09042202学院:电子工程与光电技术学院专业:通信工程专业题目:多功能数字钟指导老师:蒋立平、花汉兵2011年11月目录一.摘要及关键词 (2)二.设计要求及说明 (3)三.工作原理和整体电路图 (3)四.各子模块的工作原理及电路图 (5)1、分频电路 (5)2、频率与相位控制字产生 (7)3、频率和相位控制器模块 (8)4、DA转换模块 (12)5、测频模块 (13)6、显示模块 (14)五、调试仿真 (15)六、实验中遇到的问题及解决方法 (16)七、实验感想 (17)八、致谢 (17)九、参考文献 (17)摘要本篇报告主要介绍了用EDA设计完成直接数字频率合成器DDS的过程。

该直接数字频率合成器输出的频率及相位均可控制,且能输出正弦、余弦、三角波、锯齿波、方波五种波形,经过转换之后还能在示波器上显示,在控制电路的作用下能实现保持、清零功能,另外还能同时显示输出频率、相位控制字、频率控制字。

本设计利用QuartusII 7.0软件进行DDS的设计,最后下载到SmartSOPC实验系统中进行硬件测试。

AbstractThis report introduces the EDA design is completed with Direct Digital Synthesis DDS process. The direct digital frequency synthesis of the output frequency and phase can control, and can output sine, cosine, triangle wave, sawtooth, square waveform five, after conversion after also displayed on the oscilloscope, in the role of the control circuit can be Implementation maintained cleared function, and also shows the output frequency, phase control characters, frequency control word. This design uses DDS QuartusII 7.0 software design, the final download SmartSOPC experimental system hardware testing.关键词EDA设计、直接数字频率合成器DDS、QuartusII 7.0软件、SmartSOPC 实验系统Key wordsEDA design,Direct Digital Synthesizer DDS, QuartusII7.0software, SmartSOPC experiment system二、设计要求及说明1.基本要求(1)利用QuartusII软件和SmartSOPC实验箱实现DDS的设计;(2)DDS中的波形存储器模块用Altera公司的Cyclone系列FPGA芯片中的ROM实现,ROM结构配置成4096×10类型;(3)系统具有清零和使能的功能;(4)利用实验箱上的D/A转换器件将ROM输出的数字信号转换为模拟信号,能够通过示波器观察到正弦波形;(5)通过开关(实验箱上的Ki)输入DDS的频率和相位控制字,并能用示波器观察加以验证;2.提高部分:测频电路测频电路是对输出波形的频率进行测量并显示出来,以便观察输出波形的频率。

南理工EDA2 DDS实现 基于quartus

一、设计内容简介DDS即Direct Digital Synthesizer数字合成器,是一种基于全数字技术从相位概念出发直接合成所需波形的一种频率合成技术。

具有相对带宽大,频率转换时间短,分辨力高,相位连续性好等优点,很容易实现频率相位和幅度的数控调制,广泛应用于通讯领域。

本实验是设计一个频率和相位均可控制的具有正弦和余弦输出的直接数字频率合成器。

二、设计目的1·学习运用EDA技术,使用FPGA实现直接数字频率合成器(DDS)。

2·熟悉掌握QuartusⅡ软件的使用方法。

3·熟悉掌握各芯片的逻辑功能及使用。

4·了解下载板结构及其引脚分配。

5·提高动手能力以及提出问题分析问题解决问题的能力。

三、实验设计要求(1)设计基本要求1、利用QuartusII软件和SmartSOPC实验箱实现DDS的设计;2、DDS中的波形存储器模块用Altera公司的Cyclone系列FPGA芯片中的RAM实现,RAM结构配置成212×10类型;3、具体参数要求:频率控制字K取4位;基准频率fc=1MHz,由实验板上的系统时钟分频得到;4、系统具有使能功能;5、利用实验箱上的D/A转换器件将ROM输出的数字信号转换为模拟信号,能够通过示波器观察到正弦波形;6、通过开关(实验箱上的Ki)输入DDS的频率和相位控制字,并能用示波器观察加以验证;(2)设计提高部分要求1、通过按键(实验箱上的Si)输入DDS的频率和相位控制字,以扩大频率控制和相位控制的范围;(注意:按键后有消颤电路)2、能够同时输出正余弦两路正交信号;3、在数码管上显示生成的波形频率;4、充分考虑ROM结构及正弦函数的特点,进行合理的配置,提高计算精度;5、设计能输出多种波形(三角波、锯齿波、方波等)的多功能波形发生器;6、基于DDS的AM调制器的设计;7、自己添加其他功能。

四、实验设计原理直接数字频率合成器(Direct Digital Frequency Synthesizer)是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术。

DDS信号发生器实验报告

DDS信号发生器一、实验目的:学习利用EDA技术和FPGA实现直接数字频率综合器DDS的设计。

二、实验原理实验原理参考教材6.4节和6.11节相关内容。

三、实验内容1、实验原理参考教材6.4节相关内容。

根据6.4.2节和例6-10,在Quartus II上完成简易正弦信号发生器设计,进行编辑、编译、综合、适配、仿真;2、使用SignalTap II测试;3、硬件测试:进行引脚锁定及硬件测试。

信号输出的D/A使用DAC0832,注意其转换速率是1μs。

下载到实验系统上,接上D/A模块,用示波器测试输出波形;4、按照教材图6-72完成DDS信号发生器设计,进行编辑、编译、综合、适配、仿真,引脚锁定及硬件测试。

5、建立.mif格式文件。

四、实验步骤1、建立.mif文件:(1)设定全局参数:(2)设定波形:(3)文件保存:2、新建工程:3、LPM—ROM定制:(1)(2)(4)(5)(7)sinrom源程序:module SIN_CNT(RST,CLK,EN,Q,AR); output [7:0] Q;input [6:0] AR;input EN,CLK,RST;wire [6:0] TMP;reg[6:0] Q1;reg[7:0] F;reg C;always @(posedge CLK)if(F<AR) F<=F+1;elsebeginF=8'b00;C=~C;endalways @(posedge CLK or negedge RST)if(!RST) Q1<=7'b0000000;else if(EN) Q1<=Q1+1;else Q1<=Q1;assign TMP=Q1;sinrom IC1(.address(TMP),.clock(CLK),.q(Q)); endmodule4、锁相环:5、顶层文件:6、SignalTap II的使用7、锁定引脚8、下载。

实验五 DDS信号发生器设计

实验五DDS信号发生器的设计(1) 实验目的:学习利用EDA技术和FPGA实现直接数字频率综合器DDS的设计。

(2) 实验原理:直接数字频率综合技术,即DDS技术,是一种新型的频率合成技术和信号产生方法。

其电路系统具有较高的频率分辨率,可以实现快速的频率切换,并且在改变时能够保持相位的连续,很容易实现频率、相位和幅度的数控调制。

f SIN = M(f clk/2n)DDS基本结构相位累加器位宽和采样点关系【例11-12】LIBRARY ieee; --波形数据ROMUSE ieee.std_logic_1164.all;LIBRARY altera_mf;USE altera_mf.altera_mf_components.all;ENTITY data_rom ISPORT( address : IN STD_LOGIC_VECTOR (9 DOWNTO 0);inclock : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );END data_rom;. . .init_file => "./data/ rom_data.mif ", --波形数据初始化文件路径lpm_hint => "ENABLE_RUNTIME_MOD=YES, INSTANCE_NAME=rom2",. . .END;【例11-13】LIBRARY IEEE; --32位加法器模块USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER32B ISPORT ( A : IN STD_LOGIC_VECTOR(31 DOWNTO 0);B : IN STD_LOGIC_VECTOR(31 DOWNTO 0);S : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );END ADDER32B;ARCHITECTURE behav OF ADDER32B ISBEGINS <= A + B;END behav;【例11-14】--32位寄存器模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY REG32B ISPORT ( Load : IN STD_LOGIC;DIN : IN STD_LOGIC_VECTOR(31 DOWNTO 0);DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );END REG32B;ARCHITECTURE behav OF REG32B ISBEGINPROCESS(Load, DIN)BEGINIF Load'EVENT AND Load = '1' THEN -- 时钟到来时,锁存输入数据DOUT <= DIN;END IF;END PROCESS;END behav;【例11-15】rom_data.mif 10位正弦波数据文件,读者可用MATLAB/DSP Builder 生成 WIDTH=10;DEPTH=1024;ADDRESS_RADIX=DEC;DATA_RADIX=DEC;CONTENT BEGIN0 : 513; 1 : 515; 2 : 518; 3 : 521; 4 : 524; 5 : 527; 6 : 530; 7 : 533; 8 : 537; 9 : 540; 10 : 543; 11 : 546; 13 : 549; 13 : 552; 14 : 555;. . . . . .(略去部分数据)1018 : 493; 1019 : 496; 1020 : 499; 1021 : 502; 1022 : 505; 1023 : 508; END;(3) 实验内容1:详细述叙DDS 的工作原理,依据例11-12至例11-15完成仿真,并由仿真结果进一步说明DDS 的原理。

南理工电子信息工程综合实验实验报告

南京理工大学电子信息工程综合实验实验报告题目:电子信息工程综合实验实验报告院系:电子工程与光电技术学院姓名(学号):指导教师:实验日期: 2015年11月6号目录实验一正交调制器实验 (2)实验二正交相干检波器 (7)实验三匹配滤波器 (12)实验四动目标检测及相参积累 (17)实验五线性调频脉冲压缩 (29)实验总结 (35)实验一 正交调制器实验一、实验目的1.掌握正交调制器的工作原理;2.掌握正交调制器的电路组成。

二、实验仪器信号源、示波器、直流稳压电源 三、实验原理正交调制是一种特殊的复用技术,一般是指利用两个频率相同但相位相差90度的正弦波作为载波,同时传送两路互相独立的信号的一种调制方式。

图一是具体的调制器功能框图。

图一 正交调制器功能框图如图一所示,两路互相正交的信号i(t)和q(t)分别调制角频率为W c 的互相正交的正弦波调制,调制后两路相加的波形为:(t)i(t)cosw (t)sinw c c x t q t=+如果两路正交的信号i(t)和q(t)分别为线性调频脉冲信号的复包络的实部和虚部,即:2(t)cos(k t )i π=,2q(t)sin(k t )π= 正交调制器的输出则为:222x(t)(t)cos (t)sin cos(k t )cos()sin(k t )sin()cos(k t )c c c c c i t q t t t t ωωπωπωωπ=+=-=+显然,正交调制器的输出为载频频率为W c 的线性调频脉冲信号。

四、实验电路本实验装置主要由波形产生电路以及正交调制电路两个模块组成,硬件方面主要使用了单片机和FPGA 两种可编程的器件联合实现的。

单片机处理开关扫描和显示电路,FPGA 实现波形产生与输出选择,具有很大的灵活性和开放性,系统原理框图如图二所示。

图二正交调制器实验装置原理框图本实验装置的单片机选用的是Atmel公司的单片机AT89C55WD,如图三单片机的数据地址复用口全部与FPGA相连,此外地址的高三位也与FPGA相连,这主要是为了让FPGA承担为单片机地址译码器选通外设的作用。

南理工EDA2 DDS实现 基于quartus..

一、设计内容简介DDS即Direct Digital Synthesizer数字合成器,是一种基于全数字技术从相位概念出发直接合成所需波形的一种频率合成技术。

具有相对带宽大,频率转换时间短,分辨力高,相位连续性好等优点,很容易实现频率相位和幅度的数控调制,广泛应用于通讯领域。

本实验是设计一个频率和相位均可控制的具有正弦和余弦输出的直接数字频率合成器。

二、设计目的1·学习运用EDA技术,使用FPGA实现直接数字频率合成器(DDS)。

2·熟悉掌握QuartusⅡ软件的使用方法。

3·熟悉掌握各芯片的逻辑功能及使用。

4·了解下载板结构及其引脚分配。

5·提高动手能力以及提出问题分析问题解决问题的能力。

三、实验设计要求(1)设计基本要求1、利用QuartusII软件和SmartSOPC实验箱实现DDS的设计;2、DDS中的波形存储器模块用Altera公司的Cyclone系列FPGA芯片中的RAM实现,RAM结构配置成212×10类型;3、具体参数要求:频率控制字K取4位;基准频率fc=1MHz,由实验板上的系统时钟分频得到;4、系统具有使能功能;5、利用实验箱上的D/A转换器件将ROM输出的数字信号转换为模拟信号,能够通过示波器观察到正弦波形;6、通过开关(实验箱上的Ki)输入DDS的频率和相位控制字,并能用示波器观察加以验证;(2)设计提高部分要求1、通过按键(实验箱上的Si)输入DDS的频率和相位控制字,以扩大频率控制和相位控制的范围;(注意:按键后有消颤电路)2、能够同时输出正余弦两路正交信号;3、在数码管上显示生成的波形频率;4、充分考虑ROM结构及正弦函数的特点,进行合理的配置,提高计算精度;5、设计能输出多种波形(三角波、锯齿波、方波等)的多功能波形发生器;6、基于DDS的AM调制器的设计;7、自己添加其他功能。

四、实验设计原理直接数字频率合成器(Direct Digital Frequency Synthesizer)是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术。

DDS实验报告

设计要求说明一.设计内容本实验的内容是使用DDS的方法设计一个任意频率的正弦信号发生器,利用Quartus II编辑、编译、综合、适配、仿真测试等工作,并绑定管脚进行硬件测试,最后通过嵌入式逻辑分析仪观察输出信号波形,并验证波形正确以后,再接入DA进行最终模拟输出。

二.设计目的1、进一步熟悉QuartusⅡ的软件使用方法;2、熟悉利用VHDL设计数字系统并学习LPM ROM的使用方法;3、学习FPGA硬件资源的使用和控制方法;4、掌握DDS基本原理,学习利用此原理进行信号发生器的设计。

三.设计要求基本要求:1、完成8位输出数据宽度的频率可调的移相正弦信号发生器。

提高部分:2、完成8位输出数据宽度的移相三角波、方波信号发生器。

3、波形发生器实现幅度可调。

基本原理直接数字频率合成器(DDS)是通信系统中常用到的部件,利用DDS可以制成很有用的信号源。

与模拟式的频率锁相环PLL相比,它有许多优点,突出为(1)频率的切换迅速;(2)频率稳定度高。

一个直接数字频率合成器由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

DDS的原理框图如下所示:图1 直接数字频率合成器原理图其中K为频率控制字,f c为时钟频率,N为相位累加器的字长,D为ROM 数据位及D/A转换器的字长。

相位累加器在时钟f c的控制下以步长K作为累加,输出N位二进制码作为波形ROM的地址,对波形ROM进行寻址,波形ROM 输出的幅码S(n)经D/A转换器变成梯形波S(t),再经低通滤波器平滑后就可以得到合成的信号波形了。

合成的信号波形形状取决于波形ROM中存放的幅码,因此用DDS可以产生任意波形。

本设计中直接利用D/A转换器得到输出波形,省略了低通滤波器这一环节。

1、频率预置与调节电路不变量K被称为相位增量,也叫频率控制字。

DDS方程为:f0= f c K/2n,f0为输出频率,f c为时钟频率。

当K=1时,DDS输出最低频率(也既频率分辩率)为f c /2nDDS的最大输出频率由Nyguist 采样定理决定,即f c /2,也就是说K的最大值为2n-1.因此,只要N足够大,DDS可以得到很细的频率间隔。

南理工电子信息工程综合实验实验报告

南理工电子信息工程综合实验实验报告南京理工大学电子信息工程综合实验实验报告题目:电子信息工程综合实验实验报告院系:电子工程与光电技术学院姓名(学号):指导教师:实验日期: 2015年11月6号目录实验一正交调制器实验 (2)实验二正交相干检波器 (7)实验三匹配滤波器 (12)实验四动目标检测及相参积累 (17)实验五线性调频脉冲压缩 (29)实验总结 (35)实验一 正交调制器实验一、实验目的1.掌握正交调制器的工作原理;2.掌握正交调制器的电路组成。

二、实验仪器信号源、示波器、直流稳压电源三、实验原理正交调制是一种特殊的复用技术,一般是指利用两个频率相同但相位相差90度的正弦波作为载波,同时传送两路互相独立的信号的一种调制方式。

图一是具体的调制器功能框图。

图一 正交调制器功能框图如图一所示,两路互相正交的信号i(t)和q(t)分别调制角频率为W c 的互相正交的正弦波调制,调制后两路相加的波形为:(t)i(t)cosw (t)sinw c c x t q t =+如果两路正交的信号i(t)和q(t)分别为线性调频脉冲信号的复包络的实部和虚部,即:2(t)cos(k t )i π=,2q(t)sin(k t )π= 正交调制器的输出则为:222x(t)(t)cos (t)sin cos(k t )cos()sin(k t )sin()cos(k t )c c c c c i t q t t t t ωωπωπωωπ=+=-=+ 显然,正交调制器的输出为载频频率为W c 的线性调频脉冲信号。

四、实验电路本实验装置主要由波形产生电路以及正交调制电路两个模块组成,硬件方面主要使用了单片机和FPGA 两种可编程的器件联合实现的。

单片机处理开关扫描和显示电路,FPGA 实现波形产生与输出选择,具有很大的灵活性和开放性,系统原理框图如图二所示。

图二正交调制器实验装置原理框图本实验装置的单片机选用的是Atmel公司的单片机AT89C55WD,如图三单片机的数据地址复用口全部与FPGA相连,此外地址的高三位也与FPGA相连,这主要是为了让FPGA承担为单片机地址译码器选通外设的作用。

南京理工大学电类综合实验报告

电类综合实验实验报告(数字FM调制解调器的设计)姓名:金威学号:115110001089学院名称:自动化学院指导老师:薛文刘光祖2016年6月一、实验名称数字FM 调制解调器的设计二、实验目的1、理解FM 数字调制解调的基本原理;2、掌握FPGA 的基本结构及开发的一般流程;3、掌握Quartus Ⅱ软件的基本使用。

三、实验内容基于FPGA 开发板(DE2-115)和AD/DA 板(THDB-ADA )设计一个数字式FM 调制解调器,并要求测试调制解调器的功能和解调性能:1、按照FM 调制的实现框图,设计一个FM 数字调制器,完成对设定波形的FM 数字调制。

并验证调制信号的正确性。

2、按照FM 解调的实现框图,选择合理方案设计一个FM 数字解调器,完成对输入已调信号的FM 数字解调,并验证其功能及性能。

四、实验要求1、基本要求(1)要求调制信号为正弦波,调制信号频率为100kHz ,最大频偏为100kHz ,载波频率为3MHz 。

(2)输入已调载波信号峰峰值幅度不超过1V ,调制信号频率不大于50kHz ,载波频率为3MHz 的正弦波。

五、FM 调制解调基本原理1、FM 信号的数学表达式FM 是一种以载波的瞬时频率变化来表示信息的调制方式,其载波的频率跟随输入信号的幅度直接成等比例变化,其数学表达式如下:若调制信号为()m x t ,其振幅()1m x t ≤,载波信号为()cos(2)c c x t A f t π= (1)其中A为振幅,cf为载波中心频率,则已调信号为()cos(22())tcm c mx t A f t fx dππττ=+∆⎰(2) 其中f∆为最大频偏,表示相对于载波的最大频率偏离量。

2、FM调制信号的时域及频域波形图图 1 已调信号时域波形图O fcΩfcΩf|A|图 2 FM已调信号幅度谱2、实现FM信号调制的两种方式有两种方法分别是直接调频和间接调频。

直接调频就是,根据FM信号的瞬时频率与调制信号幅度程线性关系这一特征,可将调制信号的电压作为压控振荡器的控制电压,使其输出频率直接受调制信号电压的控制,这样压控振荡器的中心频率就是已调信号的中心频率,而信号的瞬时频率恰好由调制信号的电压幅度决定,这种方式是最直接的频率调制实现方式。

DDS报告

目录1 DDS算法原理 (1)1.1 DDS的工作原理 (1)1.2 DDS模块的输出频率 (3)1.3 存储器中读数据 (4)2 基于DDS技术的任意波形发生器 (5)3 Verilog语言实现基于DDS技术的余弦信号发生器,输出位宽16Bit (7)3.1 verilog代码 (7)3.2 ROM中加正余弦波形数值 (10)4实验中遇到的问题及解决办法 (11)基于FPGA的DDS的余弦信号设计伴随着超高速数字电路的发展以及对DDS的深入研究, DDS的高工作频率以及它的抗噪声性能已接近并达到锁相频率合成器相当的水平。

随着这种技术的发展,其将被广泛应用于电子通讯、电子雷达、卫星导航、电子对抗以及现代化的仪器仪表工业等领域。

传统直接数字频率合成器(DDS)技术,一般采用像单片机等类似的 MCU,其产生正弦信号的输出频率比较小,很难符合现代的通讯等各方面的要求。

基于FPGA的直接数字频率合成器, 相比于其它频率合成方法,具有其特定的优越性能和特点,目前它已经成为现代频率合成技术中的领先者。

其主要体现在相对带宽较宽,频率转换时间短,输出频率是数字可调的,频率分辨率高。

输出相位连续,可产生宽带正交信号及其他多种调制信号,可编程和全数字化,控制灵活方便等方面,并具有极高的性价比。

而且频率和相位可调,适用不同通讯信号占据不同的频率范围,符合现代化通讯的要求。

1 DDS算法原理1.1 DDS的工作原理DDS的工作原理为:在参考时钟的驱动下,相位累加器对频率控制字进行线性累加,得到的相位码对波形存储器寻址,使之输出相应的幅度码,经过模数转换器得到相应的阶梯波,最后在使用低通滤波对其进行平滑,得到所需频率的平滑连续的波形,其结构框图如图1.1所示。

图1.1 DDS的结构框图DDS技术是建立在采样定理的基础上的,它首先对需要产生的波形进行采样将采样值数字化后存入存储器作为查找表,然后再通过查表将数据读出,经过D /A转换器转换成模拟量,把存入的波形重新合成出来。

实验1DDS信号源实验报告

实验1DDS信号源实验报告一、实验目的1. 了解DDS(Direct Digital Synthesis)技术的原理和基本功能。

2.掌握DDS信号源的使用方法。

3.学会通过DDS信号源产生不同频率的正弦波信号。

二、实验原理DDS技术是一种通过数字方式直接产生信号的技术,它可以根据输入的参考信号和相位累加器的频率控制字,生成任意频率的正弦波信号。

DDS信号源的主要组成部分包括相位累加器、频率控制字、查找表和数字控制逻辑。

1.相位累加器:通过不断累加相位控制字产生相位累加值,控制波形的频率。

2.频率控制字:根据所需的频率值,将其转换为相位控制字并输入给相位累加器。

3.查找表:根据相位累加器的输出值,查找并输出对应的正弦波数据。

4.数字控制逻辑:实现DDS信号源的控制和配置功能。

三、实验器材及仪器1.定频信号发生器。

2.DDS信号源。

3.示波器。

4.双踪示波器。

四、实验步骤1.将定频信号发生器的输出连接到DDS信号源的外部参考时钟输入端。

2.将DDS信号源的输出连接到示波器的输入端。

3.打开定频信号发生器和DDS信号源,并设置其输出频率。

4.调整示波器的时间基准和电压基准,观察并记录示波器上显示的信号波形。

五、实验结果与分析根据所设置的频率值和相位控制字,DDS信号源可以产生相应频率的正弦波信号。

通过示波器可以观察到生成的信号波形。

实验中可以设置不同的频率值,观察其对应的正弦波信号。

当频率较低时,示波器上显示的波形周期较长,波峰和波谷的间距较大;而当频率较高时,示波器上显示的波形周期较短,波峰和波谷的间距较小。

通过不断调整频率值,可以观察到正弦波信号的频率变化规律。

六、实验总结通过本次实验,我对DDS信号源的原理和基本功能有了更深入的了解,掌握了DDS信号源的使用方法,并学会了通过DDS信号源产生不同频率的正弦波信号。

实验中,我们通过连接定频信号发生器和示波器,设置不同的频率值,观察到了相应频率的正弦波信号,并对信号波形进行了分析和观察。

DDS合成原理及低通滤波器的设计

上世纪六十年代, 相位反馈理论和模拟锁相技术的应用,产生了间接合成技术, 由 此引发了 频率合成理论的 第一次革命。 接模拟频率合成技术就是一个或多个基准 间 频率源, 通过谐波发生器、 混频、 分频等变换, 产生大量的谐波或组合频率, 然后用 锁相环( L将频率锁定在某一谐波或组合频率上。 于锁相环相当于一个窄带跟踪 ( ) P L 由 滤波器, 可以 所以 很好地选择所需频率信号, 抑制杂散分量, 并且避免了使用大量滤 波器, 十分有利于集成化和小型化。 此外, 一个设计良 好的压控振荡器(C ) V O 具有高 的短期频率稳定性, 而标准频率源具有高的长期频率稳定度, 锁相环频率合成器将二 者结合在一起, 使得合成信号的 稳定度大大提高。 另外锁相环频率合成器还具有控制 方便、 体积较小、 较好的 性价比 等优点, 因此广泛地应用于同步跟踪、 信号提取、 解 调等雷达与通信系统中。不过由于锁相环存在捕获时间问题,其频率转换时间较长,

V 730 653

南京理工大学硕士学位论文 基于 D S D 技术的多波形信号源设计

摘

要

直接数字频率合成 ( D , cDgaF qe y t i 是一种新的频率合成 D SDr t t r un Sn s) i i l c y h s e i e 方法, 是频率合成技术的一次革命, 随着数字集成电 路和微电子技术的发展, 直接数

上世纪后期提出的直接数字频率合成理论是频率合成史上的第二次革命。17 91

年, 学者J in , . d , o 发表的关于 美国 .e e C R e B l T ry . a r . d M G 直接数字 合成的 结果, 频率 研究 第一次提出了 D 的 念[, 于受当时 子 D S 概 [ 但由 2 6 ] 微电 技术和数字 信号处理技术的限 制,

DDS实验报告

DDS实验报告基于MATLAB的数字频率合成DDS设计一、实验目的:1:理解数字频率合成DDS的原理。

2:掌握DDS的设计方法与理念。

3:学会用MALTLAB对DDS进行程序实现。

二、实验背景:随着技术和器件水平的提高,称之为直接数字式频率合成器(DDS)新的频率合成技术得到飞速的发展。

DDS 在相对带宽、频率转换时间、相位连续性、正交输出、高分辨力以及集成化等一系列指标方面,已远远超过了传统频率合成器所能达到的水平,完成了频率合成技术的又一次飞跃。

DDS 与传统的 DS 和 IS 一起构成了现代频率合成技术体系,将频率合成技术推向了一个新阶段。

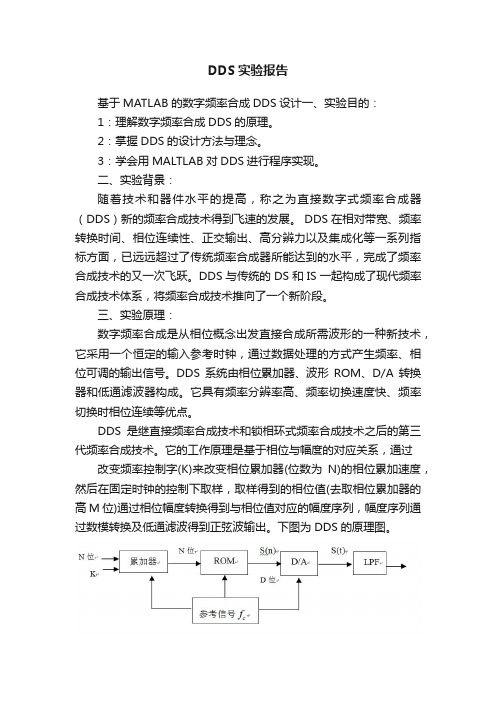

三、实验原理:数字频率合成是从相位概念出发直接合成所需波形的一种新技术,它采用一个恒定的输入参考时钟,通过数据处理的方式产生频率、相位可调的输出信号。

DDS系统由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

它具有频率分辨率高、频率切换速度快、频率切换时相位连续等优点。

DDS是继直接频率合成技术和锁相环式频率合成技术之后的第三代频率合成技术。

它的工作原理是基于相位与幅度的对应关系,通过改变频率控制字(K)来改变相位累加器(位数为N)的相位累加速度,然后在固定时钟的控制下取样,取样得到的相位值(去取相位累加器的高M位)通过相位幅度转换得到与相位值对应的幅度序列,幅度序列通过数模转换及低通滤波得到正弦波输出。

下图为DDS的原理图。

图(1)原理框图其中,K为频率控制字,c f为基准时钟频率,N为相位累加器的字长,D为ROM数据位及D/A转换器的字长。

相位累加器在基准时钟fc的控制下以步长K做累加,把相加后的结果送至相位累加器的输入断,相位累加器一方面将在上一时钟周期作用后产生的新的相位数据反馈到自身的输入端,在下一个时钟的作用下继续与频率控制数据K 相加,另一方面将这个值作为取样地址输出,送人正弦查找表ROM,作为波形ROM的地址,对波形ROM进行寻址。

南京理工大学eda设计(1)报告(优秀)

EDA设计(I)实验报告院系:专业:班级:学号:姓名:指导老师:实验一 单级放大电路的设计与仿真一.实验目的1. 掌握放大电路静态工作点的调整和测试方法。

2. 观察静态工作点的选择对输出波形的影响。

3. 掌握电路输入电阻、输出电阻的测试方法。

4. 观察电路的频率响应曲线以及掌握电路上、下限频率的测试方法。

二.实验原理当三极管工作在放大区时具有电流放大作用,只有给放大电路中的三极管提供合适的静态工作点才能保证三极管工作在放大区,如果静态工作点不合适,输出波形则会产生非线性失真——饱和失真和截止失真,而不能正常放大。

当静态工作点设置在合适的位置时,即保证三极管在交流信号的整个周期均工作在放大区时,三极管有电流放大特性。

通过适当的外接电路,可实现电压放大。

表征放大电路放大特性的交流参数有电压放大倍数、输入电阻、输出电阻。

由于电路中有电抗组件电容,另外三极管中的PN 结有等效电容存在,因此,对于不同频率的输入交流信号,电路的电压放大倍数不同,电压放大倍数与频率的关系定义为频率特性,频率特性包括:幅频特性——即电压放大倍数的幅度与频率的关系;相频特性——即电压放大倍数的相位与频率的关系。

三.实验要求1)设计一个分压偏置的单管电压放大电路,要求信号源频率5kHz(幅度1mV) ,负载电阻5.1k Ω,电压增益大于50。

2)调节电路静态工作点(调节电位计),观察电路出现饱和失真和截止失真的输出信号波形,并测试对应的静态工作点值。

3)加入信号源频率5kHz(幅度1mV) ,调节电路使输出不失真,测试此时的静态工作点值。

测电路的输入电阻、输出电阻和电压增益; 4)测电路的频率响应曲线和L f 、H f 值。

四.实验内容与步骤1.设计一个分压偏置的单管电压放大电路,要求信号源频率5kHz(幅度1mV) ,负载电阻5.1kΩ,电压增益大于50。

单级放大的设计原理图如下:若把调节电位器的大小,从而使电路具有不同的静态工作点,则从与节点4相连的示波器上可以观察到饱和失真、截止失真、不失真三种不同的现象。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子线路课程设计——DDS直接频率合成器学院:电子信息与光电技术学院学号:姓名:指导老师:谭雪琴完成时间:2014.11.24~2014.11.28摘要本次实验利用DDS技术原理,设计了一个基于QuartusII7.1软件和SmartSOPC实验系统的直接数字频率合成器,能够输出多种波形:正弦波、余弦波、方波、三角波、锯齿波。

并且可以通过开关输入四位的频率控制字来改变采样频率和输入四位的相位控制字来改变波形的相位。

添加测频和译码显示模块,可以将测得输出波形的频率、频率控制字及相位控制字通过数码管显示出来。

然后利用正弦信号的对称性质,实现ROM的空间节省。

最后利用AM调制原理设计实现基于DDS的AM调制功能。

在利用QuartusⅡ进行相应的设计、仿真、调试后下载到SmartSOPC实验实现D/A转换,验证实验的准确性,并用示波器观察输出波形。

关键词:直接数字频率合成器频率控制相位控制测频节省空间ROM AM调制AbstractA direct digital frequency synthesizer(DDS) based on QuartusII software and SmartSOPC experimental system which can output a variety of waveforms: sine, cosine wave, square wave, triangle wave,sawtooth wave was designed. And it can input four-width frequency control word using switch to change the sampling frequency and four-width phase control word to change the phase of the waveform. Also the frequency measuring and display decoding module are added,so the frequency of the output waveform,frequency control word and phase control word can be measured and displayed by the digital display. Based on the basic design,I also design extra functions,including ROM memory saving by utilizing the symmetry of sine and AM modulation based on DDS .A fter all the work finished on computer, I downloaded the final circuit to SmartSOPC experiment system to realize the transformation of D/A ,and thentest the accuracy of the design by meansof oscilloscope observing the wave forms.Key words:DDS Frequency-controlling Phase-controlling Frequency-measuring ROM memory saving AM modulation目录一、设计要求说明 (4)二、方案论证 (5)三、基础电路子模块设计原理 (7)3.1 分频电路 (7)3.2频率(相位)预置与调节电路的设计 (10)3.3累加器的设计 (11)3.4相位控制电路 (12)3.5波形存储器ROM的设计 (13)3.6节省ROM电路 (14)3.7测频电路 (16)3.8不同波形选择电路 (17)3.9 模16控制电路 (18)3.10译码显示电路 (19)3.11总电路图 (20)四、基于DDS的AM调制电路 (20)4.1AM 调制原理 (20)4.2AM调制电路设计 (21)4.3子模块设计1)有符号波形存储ROM (21)2)调制模块 (22)3)调制度mA设置电路 (23)4)测频及译码显示 (24)5)载波和调制信号频率控制 (24)6)调制波形选择 (25)4.4基于DDS的AM调制总电路图 (25)五、程序的下载和调试 (25)六、示波器结果 (26)参考文献 (29)附:实验感想一、设计要求说明1.设计完成内容设计了一个直接数字频率合成器(DDS)能够输出多种波形:正弦波、余弦波、方波、三角波、锯齿波。

并且可以通过开关输入四位的频率控制字来改变采样频率和四位的相位控制字来改变波形的相位。

可以测试输出波形的频率,并将波形频率、频率控制字及相位控制字通过数码管显示。

最后改进完成ROM的空间节省和基于DDS的AM调制功能。

2.设计基础要求:1)利用QuartusII软件和SmartSOPC实验箱实现DDS的设计;2)DDS中的波形存储器模块用Altera公司的CycloneIII系列FPGA芯片中的RAM实现,RAM结构配置成212×10类型;3)具体参数要求:频率控制字K取4位;基准频率fc=1MHz,由实验板上的系统时钟分频得到;4)系统具有使能功能;5)利用实验箱上的D/A转换器件将ROM输出的数字信号转换为模拟信号,能够通过示波器观察到正、余弦两路波形;6)通过开关(实验箱上的Ki)输入DDS的频率和相位控制字,并能用示波器观察加以验证;3.设计提高部分要求:1)通过按键(实验箱上的Si)输入DDS的频率和相位控制字,以扩大频率控和相位控制的范围;(注意:按键后有消颤电路)2)在数码管上显示生成的波形频率;3)设计能输出多种波形(三角波、锯齿波、方波等)的多功能波形发生器;4)充分考虑ROM结构及正弦函数的特点,进行合理的配置,提高计算精度;5)基于DDS的AM调制器的设计;6)自己添加其他功能。

二、方案论证1、DDS概念直接数字频率合成器(Direct Digital Frequency Synthesizer)是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术。

2、DDS的组成及工作原理1)频率预置与调节电路作用:实现频率控制量的输入;不变量K被称为相位增量,也叫频率控制字。

2)累加器相位累加器的组成= N位加法器+N位寄存器;作用:在时钟的作用下,进行相位累加。

当相位累加器累加满量时就会产生一次溢出,完成一个周期性的动作。

DDS的输出频率为:f0=fCK/2N ;DDS输出的最低频率:K=1时,fC/2NDDS输出的最高频率:由Nyquist采样定理决定,即fC/2;K的最大值为2N-1,只要N足够大,DDS可以得到很细的频率间隔。

要改变DDS的输出频率,只要改变频率控制字K即可。

\3)波形存储器作用:进行波形的相位—幅值转换。

原理:ROM的N位地址:把0°—360°的正弦角度离散成具有2N个样值的序列ROM的D位数据位:把2N个样值的幅值量化为D位二进制数据(有符号数) 4)D/A转换器D/A转换器的作用:把已经合成的正弦波的数字量转换成模拟量。

5)低通滤波器D/A转换器的作用:滤除生成的阶梯形正弦波中的高频成分,将其变成光滑的正弦波。

三、基础电路子模块设计原理1、分频电路通过分频电路将48MHz的脉冲分为1MHz,1KHz,1Hz和0.5Hz。

其中,1MHz 脉冲频率为累加器电路中的寄存器时钟信号、1KHz脉冲频率为动态译码显示电路提供频率,1Hz脉冲频率为频率、相位控制电路、模16电路提供频率,0.5Hz 脉冲频率为测频电路提供频率。

注意:因为太多的异步会导致最后实际分频出的信号产生误差,所以将EDA2中通过2分频、3分频级联产生48分频,用10分频级联产生1000分频的方案改成同步置数,直接搭出48分频,1000分频。

①2分频电路使用D触发器,把D与Q非连接在一起,并保证其他端口处于正常工作状态,在一个时钟范围内变化两次,达到2分频的目的。

仿真结果:②48分频电路用两块74160来实现十进制计数,左别的一块记个位,右边的记十位。

将十位的Qc作为输出端,并且在记到48即个位QaQbQc和十位Qc均为1时,重新置数0。

仿真结果:封装后,如图:③1000分频电路3片74160分别表示个位、十位、百位,以百位的Qd作为输出端。

仿真结果:封装后,如下图:分频总电路图:仿真结果:封装后,如下图:2、频率(相位)预置与调节电路的设计频率预置与调节电路由1片模16的74161计数器组成,1Hz信号输入让其变化。

通过开关K1和K2分别控制清零和保持端,以便计数到需要值时保持或清零。

频率频率预置与调节电路实现频率控制量(步长)的输入。

相位预置电路同频率预置电路完全相同,用K3和K4分别控制相位清零和保持。

电路图如下图:仿真结果:封装后,如下图:其中,keep为频率保持端clear为频率清零端1hz为1hz信号输入端K[3..0]为频率控制字的大小3、累加器的设计累加器由3片7483全加器和3片74175寄存器构成。

每来一个时钟脉冲,加法器就将步长与寄存器输出的累加相位数据相加,再把相加后的结果送至寄存器的数据输入端。

寄存器将加法器在上一个时钟作用后所产生的相位数据反馈到加法器的输入端;以使加法器在下一个时钟作用下继续与频率控制字进行相加。

这样,相位累加器在时钟的作用下,进行相位累加。

当相位累加器达到满量时就会产生一次溢出,完成一个周期性的动作。

因为ROM中设定的相位取样地址为12位,而本实验中我们取频率控制字K=4,所以将频率步长k[3..0]加在低4位,高8位置0。

第一片7483产生的进位进入到第二片7483进行累加,依次往后从而实现累加的过程。

电路图如下图:封装后,如下图:4、相位控制电路相位控制电路实现对产生波形相位进行控制。

该电路由1片74175和3片7483构成的12位全加器组成。

相位控制字从74175输入端输入,送入12位加器器7483的高四位,低8位置零,这样相位的变化能更明显。

电路图如下:封装后,如下图:5、波形存储器ROM的设计波形数据表ROM 用于存放波形数据,这里用它存放正弦波、余弦波、三角波、方波、锯齿波的波形数据。

每一位地址对应一个数值,输出为10 位。

ROM 中必须包含完整的波形采样值,本实验采样2^12 个点。

用相位控制电路输出的数据作为波形存储器的取样地址,进行波形的相位—幅值转换,即可在给定的时间上确定输出的波形的抽样幅值。