4乘4位阵列乘法器设计

基于msc51单片机实现的四位4乘4矩阵键盘计算器的C语言程序和PROTUES电路和仿真课程设计报告

单片机原理及接口技术课程设计报告设计题目:计算器设计信息与电气工程学院二零一三年七月计算器设计单片机体积小,功耗小,价格低,用途灵活,无处不在,属专用计算机。

是一种特殊器件,需经过专门学习方能掌握应用,应用中要设计专用的硬件和软件。

近年来,单片机以其体积小、价格廉、面向控制等独特优点,在各种工业控制、仪器仪表、设备、产品的自动化、智能化方面获得了广泛的应用。

与此同时,单片机应用系统的可靠性成为人们越来越关注的重要课题。

影响可靠性的因素是多方面的,如构成系统的元器件本身的可靠性、系统本身各部分之间的相互耦合因素等。

其中系统的抗干扰性能是系统可靠性的重要指标。

数学是科技进步的重要工具,数据的运算也随着科技的进步越发变得繁琐复杂,计算器的出现可以大大解放人在设计计算过程中的工作量,使计算的精度、速度得到改善,通过msc51单片机,矩阵键盘和LED数码管可以实现简单的四位数的四则运算和显示,并当运算结果超出范围时予以报错。

注:这一部分主要描述题目的背景和意义,对设计所采取的主要方法做一下简要描述。

字数不要太多,300-500字。

另注:本文要当做模板使用,不要随意更改字体、字号、行间距等,学会使用格式刷。

文中给出的各项内容都要在大家的报告中体现,可采用填空的方式使用本模板。

1. 设计任务结合实际情况,基于AT89C51单片机设计一个计算器。

该系统应满足的功能要求为:(1) 实现简单的四位十进制数字的四则运算;(2) 按键输入数字,运算法则;(3) LED数码管移位显示每次输入的数据和运算结果;(4) 当运算结果超出范围时实现报错。

主要硬件设备:AT89C51单片机、LED数码管、矩阵键盘。

注:这一部分需要写明系统功能需求,用到的主要硬件(参考实验箱的说明书)。

2. 整体方案设计计算器以AT89C51单片机作为整个系统的控制核心,应用其强大的I/O 功能和计算速度,构成整个计算器。

通过矩阵键盘输入运算数据和符号,送入单片机进行数据处理。

乘法器设计

EDA设计基础实验课程论文题目乘法器学院通信专业班级学生姓名指导教师2013年6月25 日摘要随着工艺水平的发展,集成电路设计向着速度更快,面积更小的方向稳步发展着。

处理器作为集成电路设计产品的代表,更是需要体现出这种发展趋势。

为了使整体性能有较好的表现,各方面的优化在处理器的各组成部件的设计中都应有所体现。

乘法器是处理器中的一个重要组成部分。

在多媒体应用、图像处理等领域中,大量的循环乘法运算使得乘法器的作用尤为突出,其对处理器的整体性能也起到了至关重要的影响。

本文就是要针对速度和面积方面的性能提高提出查找表乘法器:4bit*4bit查找表乘法器的设计及具体实施方案。

采用了4 - 2 和5 - 2 混合压缩器对部分积进行压缩, 减少了乘法器的延时和资源占率;经Quartus II 集成开发环境下的综合仿真测试, 与用Verilog HDL 语言实现的两位阵列乘法器和传统的Booth编码乘法器进行了性能比较, 得出用这种混合压缩的器乘法器要比传统的 4 - 2 压缩器构成的乘法器速度提高了10 % , 硬件资源占用减少了1 % 。

关键词:乘法器;改进Booth算法;Verilog HDL语言AbstractAs technical level develops, IC design progresses in both the ways of higher speed and smaller area steadily. CPU is more likely to represent this trend for it is a typical product of IC design. To get a better performance of the whole target,we should optimize all the components of the CPU in all possible ways.Multiplier is an important component of the CPU. In the domains of multimedia application, image process and so on, plenty of multiplications in cycles make multiplier a significant part, which plays an important role in deciding the performance of the whole CPU.This paper is about to focus on improvement on speed as well as area and present lookup table multipliers varied by data width:4bit*4bit lookup table multipliers and actualization.Using 4 - 2 compressor and 5 - 2 compressor to compress partial products , while designing multiplier to reduce the delay of time and ratio of resource . Comparing performance of multiplier described in Verilog HDL on speed 、area and the utilization ratio of resource in the integrated exploitation environment of Quartus II . the speed of this multiplier is increased by 10 % and its hardware resource is reduced by 1 % .Keywords multiplier; modified Booth algorithm;Verilog HDL language目录中文摘要 (I)ABSTRACT (II)第一章绪论 (1)1.1课题背景 (1)1.2国内外发展现状 (1)1.2.1国外研究情况 (1)1.2.2国内研究情况 (2)1.3乘法器设计原理 (2)第二章乘法器简介 (4)2.1乘法器工作原理 (4)2.2乘法器实现方法 (4)2.2.1线性结构 (4)2.2.2Wallace 树结构 (5)第三章查找表乘法器的功能仿真 (7)3.1查找表原理 (7)3.1.1部分积压缩器功能简介 (7)3.2设计端口信号描述 (7)3.3查找表乘法器的功能仿真图 (8)第四章相关类型乘法器算法的简介 (9)4.1改进Boosh算法 (9)4.2 关键路径上Booth 编码模块电路设计 (11)第五章Verilog HDL语言 (13)5.1什么是Verilog HDL语言 (13)5.1.1Verilog HDL 简介 (13)5.2Verilog HDL语言与VHDL语言的比较 (13)5.3用Verilog HDL语言编写的程序仿真图 (14)结论 (15)参考文献 (16)致谢 (18)附录 (20)第一章绪论1.1课题背景Ve rilog HDL 是当今最为流行的一种硬件描述语言, 完整的Ve rilog HDL 足以对最复杂的芯片和完整的电子系统进行描述。

数字电路课程设计之乘法器精选全文完整版

基于Verilog 的乘法器设计一、设计目标使用Verilog 语言实现4bit*4bit 乘法器设计,并使用Quartes 编写程序,使用modelsin 进行仿真验证设计二、基本原理2.1半加器半加器是为两输入两输出的加法电路,输入无进位,真值表如下图所示,输入X,Y,输出C,SX Y C S 0 0 0 0 0 1 0 1 1 0 0 1 111最简积之和式为 S=X`Y+XY`=X ○+Y;C=XY. 电路图为:2.2全加器全加器是为三输入两输出,输入存在进位,真值表如下图所示,输入X,Y,Z,输出C,SX Y Z C S 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 11111化简最简积之和式为:S=X`Y`Z+X`YZ`+XY`Z`+XYZ; C=XY+XZ+YZ; 通过使用半加器组成全加器进行化简为:S=Z(X`Y`+XY)+Z`(X`Y+XY`)=Z(X ○+Y)`+Z`(X ○+Y)=X ○+Y ○+Z123YX C123123Y X`X Y`123S123C123X YSguan tian liangC 的卡诺图如下图X YZ 00 01 11 10 0 0 0 1 0 1111按两两结合 C=XY+YZ+XZ 换一种结合方式 C= XY+XY`Z+X`YZ=Z(XY`+X`Y)+XY=Z(X ○+Y)+XY 电路图如下所示(使用两个半加器与一个或门)123123X Y123123SZ123C多位二进制加法实现 2.2.1 行波进位加法器B2A3B3C3C4C2C1C0S0S1S2S3FA FALL_ADD A1B2Cout 3Cin4S5FA FALL_ADD A1B2Cout 3Cin4S5FAFALL_ADDA1B2Cout 3Cin4S5FAFALL_ADD A1B 2Cout 3Cin4S5A0B0A1B1A2行波进位加法器优点在于结构逻辑简单,缺点速度很慢,在最坏情况下,进位必须从最低有效位传到最高有效加法器,假设同时给出所有加数位,则总的最长延迟为:CinSCinCout ABCout ADD t t n t t +⨯−+=)2(ABCoutt 为最低有效级上从A 或B 到Cout 的延迟,CinCoutt 为中间级上Cin 与Cout 的延迟,CinSt 为最高有效位上从Cin 到S 的延迟。

乘位阵列乘法器设计

乘位阵列乘法器设计集团文件版本号:(M928-T898-M248-WU2669-I2896-DQ586-M1988)课程设计报告课程设计题目: 4乘4位阵列乘法器设计学生姓名:杨博闻学号专业:计算机科学与技术班级: 1120701指导教师:汪宇玲2014年 1月 4日一、设计目的1.掌握乘法器的原理及其设计方法。

2 .熟练应用CPLD 设计及 EDA 操作软件。

二、设计设备1.TDN-CM+或 TDN-CM++教学实验系统一套。

2 ·PC 微机一台。

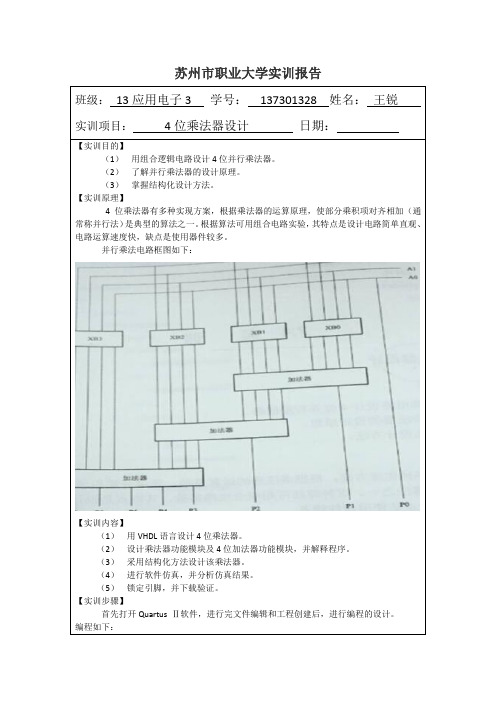

3·ispDesignEXPERT 软件模型机数据通路结构框图三、设计原理本实验用 CPLD 来设计一个 4 ×4 位乘法器,相对于画电路图输入,用 ABEL 语言描述是比较方便的。

其算式如下(其中括号中的数字表示在 ABEL 源程序描述中的功能块调用编号):a3 a2 a1 a0× b3 b2 b1 b0----------------------------------------------------------------------------------------------------------a3b0(10) a2b0(6)a1b0(3) a0b0(1)a3b1(13) a2b1(9) a1b1(5)a0b1(2)a3b2(15) a2b2(12) a1b2(8) a0b2(4) + a3b3(16) a2b3(14) a1b3(11) a0b3(7)-----------------------------------------------------------------------------------------------------------p7 p6 p5 p4 p3 p2 p1 p0四、设计步骤1.安装EDA 软件打开计算机电源,进入 Windows 系统,安装上述 ispDesignEXPERT软件。

计算机组成原理 阵列乘法器的设计

沈阳航空工业学院课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:阵列乘法器的设计院(系):计算机学院专业:计算机科学与技术班级:学号:姓名:指导教师:完成日期:2006年12月31日目录第1章总体设计方案................................. 错误!未指定书签。

设计原理........................................ 错误!未指定书签。

设计思路..................................... 错误!未指定书签。

设计环境........................................ 错误!未指定书签。

第2章详细设计方案................................ 错误!未指定书签。

顶层方案图的设计与实现.......................... 错误!未指定书签。

创建顶层图形设计文件........................... 错误!未指定书签。

器件的选择与引脚锁定........................... 错误!未指定书签。

编译、综合、适配............................... 错误!未指定书签。

功能模块的设计与实现......................... 错误!未指定书签。

(A)一位全加器的设计与实现 (I)(B)一位全加器的仿真图如下图所示:............ 错误!未指定书签。

位输入端加法器的设计与实现..................... 错误!未指定书签。

输入端加法器的封装图如下图所示:............... 错误!未指定书签。

输入端加法器的仿真图如下图所示:............... 错误!未指定书签。

(A)阵列乘法器的设计与实现................. 错误!未指定书签。

4位阵列乘法器[整理版]

![4位阵列乘法器[整理版]](https://img.taocdn.com/s3/m/f4dc640c84254b35effd34aa.png)

4位阵列乘法器[整理版]目录一、设计题目 ......................................................2 二、设计目的 (2)三、设计过程 (2)3.1设计原理 .......................................................23.2器件选择 .......................................................33.3逻辑原理 .......................................................33.4阵列乘法器的逻辑原理 (4)3.5 时序图..........................................................4 四、设计心得 (5)五、参考文献 (6)4位阵列乘法器一、设计题目 4位阵列乘法器二、设计目的计算机组成原理是计算机专业的核心专业基础课。

课程设计属于设计型实验,不仅锻炼学生简单计算机系统的设计能力,而且通过进行设计及实现,进一步提高分析和解决问题的能力。

同时也巩固了我们对课本知识的掌握,加深了对知识的理解。

在设计中我们发现问题,分析问题,到最终的解决问题。

凝聚了我们对问题的思考,充分的锻炼了我们的动手能力、团队合作能力、分析解决问题的能力。

三、设计过程3.1设计原理阵列乘法器是类似于人工计算(如图1.1所示)的方法,乘数与被乘数都是二进制数。

所以可以通过乘数从最后一位起一个一个和被乘数相与,自第二位起要依次向左移一位,形成一个阵列的形式。

这就可将其看成一个全加的过程,将乘数某位与被乘数某位与完的结果加上乘数某位的下一位与被乘数某位的下一位与完的结果再加上前一列的进位进而得出每一位的结果。

一个阵列乘法器要完成X(Y乘法运算(X=X4X3X2X1,Y=Y4Y3Y2Y1)。

阵列乘法

沈阳航空工业学院课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:阵列乘法器的设计院(系):计算机学院专业:计算机科学与技术班级:学号:姓名:指导教师:完成日期:2006年12月31日沈阳航空工业学院课程设计报告目录第1章总体设计方案 (1)1.1设计原理 (1)1.2设计环境 (3)第2章详细设计方案 (4)2.1顶层方案图的设计与实现 (4)2.1.1创建顶层图形设计文件 (4)2.1.2器件的选择与引脚锁定 (4)2.2功能模块的设计与实现 (5)2.2.1四位阵列乘法模块的设计与实现 (5)2.2.2细胞模块的设计与实现 (7)2.3仿真调试 (9)第3章编程下载与硬件测试 (11)3.1编程下载 (11)3.2硬件测试及结果分析 (11)参考文献 (14)第1章总体设计方案1.1 设计原理由于采用普通的方法计算两个数的相乘比较慢,为了进一步提高乘法运算的运算速度,可以采用类似于人工计算的方法,用阵列乘法器来进行计算,给人们带来了很大的方便。

四位阵列乘法器的原理框图如图1.1所示,X=X1X2X3X4 Y=Y1Y2Y3Y4且X为被乘数的输入端,Y为乘数的输入端,M=M0M1M2M3M4M5M6M7为乘积的输出端。

其基本原理是阵列的每一行送入乘数Y的每一位数位,而各行错开形成的每一斜列则送入被乘数的每一数位。

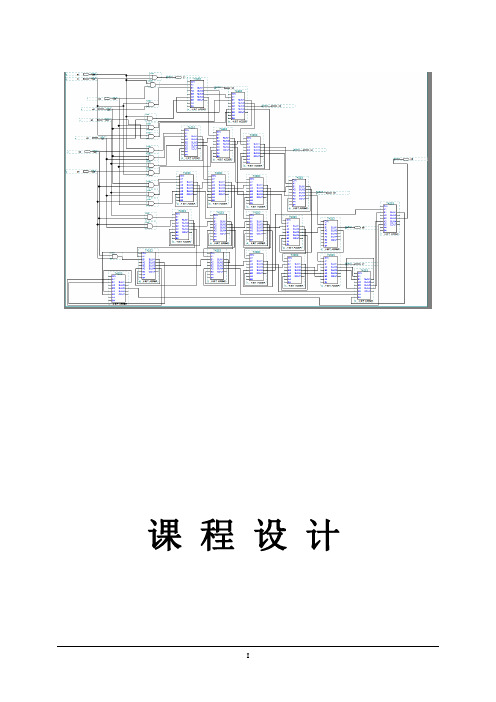

四位阵列乘法器的整体设计包含十六个加法器模块,加法器模块中由一个与门和一个全加器构成,由四个与门、两个异或门、一个三端接口的或门构成的全加器为底层设计,采用原理图设计输入方式,所谓的全加器就是两个数X、Y及进位输入Cn相加可得全加和Fn和进位输出Cn。

顶层的四位阵列乘法器也采用原理图设计输入方式,在以十六个加法器为基础而构成的四位阵列乘法器,其主要以四个被乘数输入端、四个乘数输入端以及八个乘积输出端为主,外加还包括中间过程参与计算的进位输入端、部分积输入端和进位输出端、部分积输出端,这样一来就构成了一个完整的四位阵列乘法器。

计算机组成原理_阵列乘法器的设计

沈阳航空航天大学课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:阵列乘法器的设计与实现院(系):计算机学院专业:计算机科学与技术班级:学号:姓名:指导教师:完成日期:2014年1月10日目录第1章总体设计方案 (1)1.1设计原理 (1)1.2设计思路 (2)1.3设计环境 (3)第2章详细设计方案 (3)2.1总体方案的设计与实现 (4)2.1.1总体方案的逻辑图 (4)2.1.2器件的选择与引脚锁定 (4)2.1.3编译、综合、适配 (5)2.2功能模块的设计与实现 (5)2.2.1一位全加器的设计与实现 (6)2.2.2 4位输入端加法器的设计与实现 (7)2.2.3 阵列乘法器的设计与实现 (10)第3章硬件测试 (13)3.1编程下载 (13)3.2 硬件测试及结果分析 (13)参考文献 (15)附录(电路原理图) (16)第1章总体设计方案1.1 设计原理阵列乘法器采用类似人工计算的方法进行乘法运算。

人工计算方法是用乘数的每一位去乘被乘数,然后将每一位权值对应相加得出每一位的最终结果。

如图1.1所示,用乘数的每一位直接去乘被乘数得到部分积并按位列为一行,每一行部分积末位与对应的乘数数位对齐,体现对应数位的权值。

将各次部分积求和,即将各次部分积的对应数位求和即得到最终乘积的对应数位的权值。

为了进一步提高乘法的运算速度,可采用大规模的阵列乘法器来实现,阵列乘法器的乘数与被乘数都是二进制数。

可以通过乘数从最后一位起一个一个和被乘数相与,自第二位起要依次向左移一位,形成一个阵列的形式。

这就可将其看成一个全加的过程,将乘数某位与被乘数某位与完的结果加上乘数某位的下一位与被乘数某位的下一位与完的结果再加上前一列的进位进而得出每一位的结果,假设被乘数与乘数的位数均为4位二进制数,即m=n=4,A×B可用如下竖式算出,如图1.1所示。

X 4 X3X2X1=A× Y4 Y3Y2Y1=BX4Y1X3Y1X2Y1X1Y1X4Y2X3Y2X2Y2X1Y2X4Y3X3Y3X2Y3X1Y3(进位) X4Y4 X3Y4 X2Y4 X1Y4Z8 Z7Z6Z5Z4Z3Z2Z1图1.1 A×B计算竖式X4 ,X3,X2,X1,Y4,Y3,Y2,Y1为阵列乘法器的输入端,Z1-Z8为阵列乘法器的输出端,该逻辑框图所要完成的功能是实现两个四位二进制既A(X)*B(Y)的乘法运算,其计算结果为C(Z) (其中A(X)=X4X3X2X1,B(Y)=Y4Y3Y2Y1,C(Z)=Z8Z7Z6Z5Z4Z3Z2Z1而且输入和输出结果均用二进制表示 )。

计算机组成原理阵列乘法器课程设计报告.

课程设计教学院计算机学院课程名称计算机组成原理题目4位乘法整列设计专业计算机科学与技术班级2014级计本非师班姓名唐健峰同组人员黄亚军指导教师2016 年10 月 5 日1 课程设计概述1.1 课设目的计算机组成原理是计算机专业的核心专业基础课。

课程设计属于设计型实验,不仅锻炼学生简单计算机系统的设计能力,而且通过进行设计及实现,进一步提高分析和解决问题的能力。

同时也巩固了我们对课本知识的掌握,加深了对知识的理解。

在设计中我们发现问题,分析问题,到最终的解决问题。

凝聚了我们对问题的思考,充分的锻炼了我们的动手能力、团队合作能力、分析解决问题的能力。

1.2 设计任务设计一个4位的二进制乘法器:输入信号:4位被乘数A(A1,A2,A3,A4), 4位乘数B(B1,B2,B3,B4),输出信号:8位乘积q(q1,q2,q3,q4,q5,q6,q7,q8).1.3 设计要求根据理论课程所学的至少设计出简单计算机系统的总体方案,结合各单元实验积累和课堂上所学知识,选择适当芯片,设计简单的计算机系统。

(1)制定设计方案:我们小组做的是4位阵列乘法器,4位阵列乘法器主要由求补器和阵列全加器组成。

(2)客观要求要掌握电子逻辑学的基本内容能在设计时运用到本课程中,其次是要思维灵活遇到问题能找到合理的解决方案。

小组成员要积极配合共同达到目的。

2 实验原理与环境2.1 1.实验原理计算机组成原理,数字逻辑,maxplus2是现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

用乘数的每一位去乘被乘数,然后将每一位权值直接去乘被乘数得到部分积,并按位列为一行每一行部分积末位与对应的乘数数位对齐,体现对应数位的权值,将各次部分积求和得到最终的对应数位的权值。

2.2 2.实验环境2.2.1双击maxplu2II软件图标,启动软件(1).新建工程,flie->new project ....,出现存储路径的选项框,指定项目保存路径并且为工程命名,第三行设置实体名,保持与工程名一致。

基于EDA的4位乘法器的设计

4位乘法器的设计一、设计目的设计一个四位乘法器。

编写VHDL 源代码,得出正确的仿真波形,并在实验开发系统上进行硬件演示。

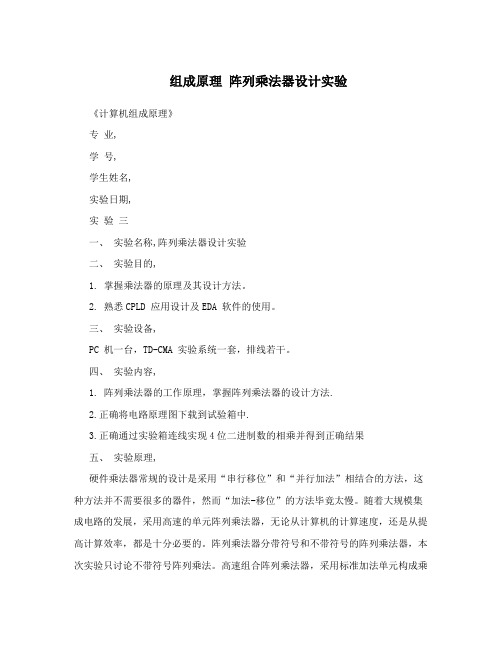

二、乘法器设计原理四位二进制乘法采用移位相加的方法。

即用乘数的各位数码,从高位开始依次与被乘数相乘,每相乘一次得到的积称为部分积,将第一次得到的部分积左移一位并与第二次得到的部分积相加,将加得的和左移一位再与第三次得到的部分积相加,再将相加的结果左移一位与第四次得到的部分积相加,直到所的部分积都被加过一次。

原理框图:三、设计程序代码1)选通与门模块的源程序ANDARITH.VHDlibrary ieee;use ieee.std_logic_1164.all;entity andarith isport(abin:in std_logic;din:in std_logic_vector(3 downto 0);dout:out std_logic_vector(3 downto 0));end;architecture art3 of andarith isbeginprocess(abin,din)beginfor i in 0 to 3 loopdout(i)<=din(i) and abin;end loop; 锁存器 寄存器加法器选通与门 clk输入 输出end process;end art3;2)4位右移寄存器的源程序SREG4B.VHD library ieee;use ieee.std_logic_1164.all;entity sreg4b isport(clk,en:in std_logic;load:in std_logic;din:in std_logic_vector(3 downto 0);qb:out std_logic);end;architecture art1 of sreg4b issignal reg4:std_logic_vector(3 downto 0); beginprocess(clk,load,en)beginif clk'event and clk ='1' and en='1' then if load='0' then reg4<=din;elsereg4(2 downto 0)<=reg4(3 downto 1);end if;end if;end process;qb<=reg4(0);end art1;3)8位锁存器的源程序REG8.VHDlibrary ieee;use ieee.std_logic_1164.all;entity reg8 isport(clk,clr,en:in std_logic;d:in std_logic_vector(4 downto 0);q: out std_logic_vector(7 downto 0)); end;architecture art4 of reg8 issignal r8s:std_logic_vector(7 downto 0); beginprocess(clk,clr)beginif clr='0' then r8s<=(others=>'0');elsif clk'event and clk='1' and en='1' then r8s(2 downto 0)<=r8s(3 downto 1);r8s(7 downto 3)<=d;end if;end process;q<=r8s;end art4;4)乘法运算控制器的源程序ARICTL.VHD library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity arictl isport(clk,start: in std_logic;en,rstall,ariend:out std_logic);end;architecture art5 of arictl issignal cnt2b:std_logic_vector(2 downto 0); beginrstall<=start;process(clk,start) isbeginif start='0' then cnt2b<="000";elsif clk'event and clk='1' thenif cnt2b<4 thencnt2b<=cnt2b+1;end if;end if;end process;process(clk,cnt2b,start) isbeginif start='1' thenif cnt2b<4 thenen<='1';ariend<='0';else en<='0';ariend<='1';end if;else en<='1';ariend<='0';end if;end process;end art5;5)译码器的源程序YIMAQI.VHDlibrary ieee;use ieee.std_logic_1164.all;entity YIMAQI isPORT(code:IN STD_LOGIC_VECTOR(3 DOWNTO 0); LED7S: OUT STD_LOGIC_VECTOR(6 DOWNTO 0) ); end;architecture ART6 of YIMA7 isbeginPROCESS(code)BEGINCASE code ISWHEN "0000" => LED7S <="0000001";WHEN "0001" => LED7S <="1001111";WHEN "0010" => LED7S <="0010010";WHEN "0011" => LED7S <="0000110";WHEN "0100" => LED7S <="1001100";WHEN "0101" => LED7S <="0100100";WHEN "0110" => LED7S <="0100000";WHEN "0111" => LED7S <="0001111";WHEN "1000" => LED7S <="0000000";WHEN "1001" => LED7S <="0000100";WHEN "1010" => LED7S <="0001000";WHEN "1011" => LED7S <="1100000";WHEN "1100" => LED7S <="0110001";WHEN "1101" => LED7S <="1000010";WHEN "1110" => LED7S <="0110000";WHEN "1111" => LED7S <="0111000";WHEN OTHERS => NULL;END CASE;END PROCESS;end ART6;6)4位乘法器的顶层文件四、程序设计步骤1.打开ispEXPERT软件,建立一个新的工程cnt10;1 单击菜单Fil e→New Project2 输入工程路径,工程名2.建立VHDL文件单击File→New菜单项,选择VHDL File选项,单击OK按钮以建立VHDL文件,分别建立4位乘法器的vhd文件ANDARITH.VHD,ARICTL.VHD,REG8.VHD,SREG4B.VHD。

4乘4位阵列乘法器设计

课程设计报告课程设计题目:4乘4位阵列乘法器设计学生姓名:杨博闻学号:201120070115专业:计算机科学与技术班级:1120701指导教师:汪宇玲2014年1月4日一、设计目的1.掌握乘法器的原理及其设计方法。

2 .熟练应用CPLD 设计及EDA 操作软件。

二、设计设备1.TDN-CM+或TDN-CM++教学实验系统一套。

2 ·PC 微机一台。

3·ispDesignEXPERT 软件模型机数据通路结构框图三、设计原理本实验用CPLD 来设计一个4 ×4 位乘法器,相对于画电路图输入,用ABEL 语言描述是比较方便的。

其算式如下(其中括号中的数字表示在ABEL 源程序描述中的功能块调用编号):a3 a2 a1 a0 ×b3 b2 b1 b0----------------------------------------------------------------------------------------------------------a3b0(10) a2b0(6) a1b0(3) a0b0(1)a3b1(13) a2b1(9) a1b1(5) a0b1(2)a3b2(15) a2b2(12) a1b2(8) a0b2(4)+a3b3(16) a2b3(14) a1b3(11) a0b3(7)----------------------------------------------------------------------------------------------------------- p7 p6 p5 p4 p3 p2 p1 p0四、设计步骤1.安装EDA 软件打开计算机电源,进入Windows 系统,安装上述ispDesignEXPERT 软件。

安装完成后,桌面和开始菜单中则建有ispDesignEXPERT 软件图标。

组成原理 阵列乘法器设计实验

组成原理阵列乘法器设计实验《计算机组成原理》专业,学号,学生姓名,实验日期,实验三一、实验名称,阵列乘法器设计实验二、实验目的,1. 掌握乘法器的原理及其设计方法。

2. 熟悉CPLD 应用设计及EDA 软件的使用。

三、实验设备,PC 机一台,TD-CMA 实验系统一套,排线若干。

四、实验内容,1. 阵列乘法器的工作原理,掌握阵列乘法器的设计方法.2.正确将电路原理图下载到试验箱中.3.正确通过实验箱连线实现4位二进制数的相乘并得到正确结果五、实验原理,硬件乘法器常规的设计是采用“串行移位”和“并行加法”相结合的方法,这种方法并不需要很多的器件,然而“加法-移位”的方法毕竟太慢。

随着大规模集成电路的发展,采用高速的单元阵列乘法器,无论从计算机的计算速度,还是从提高计算效率,都是十分必要的。

阵列乘法器分带符号和不带符号的阵列乘法器,本次实验只讨论不带符号阵列乘法。

高速组合阵列乘法器,采用标准加法单元构成乘法器,即利用多个一位全加器(FA)实现乘法运算。

对于一个4 位二进制数相乘,有如下算式:这个4 × 4 阵列乘法器的原理如图1-3-1 所示。

FA(全加器)的斜线方向为进位输出,竖线方向为和输出。

图中阵列的最后一行构成了一个串行进位加法器。

由于FA 一级是无需考虑进位的,它的进位被暂时保留下来不往前传递,因此同一极中任意一位FA 加法器的进位输出与和输出几乎是同时形成的,与“串行移位”相比可大大减少同级间的进位传递延迟,所以送往最后一行串行加法器的输入延迟仅与FA 的级数(行数)有关,即与乘数位数有关。

本实验用CPLD 来设计一个4×4 位加法器,且全部采用原理图方式实现。

六、实验步骤,(1) 根据上述阵列乘法器的原理,使用Quartus II 软件编辑相应的电路原理图并进行编译,其在EPM1270 芯片中对应的引脚如图1-3-2 所示,框外文字表示I/O 号,框内文字表示该引脚的含义。

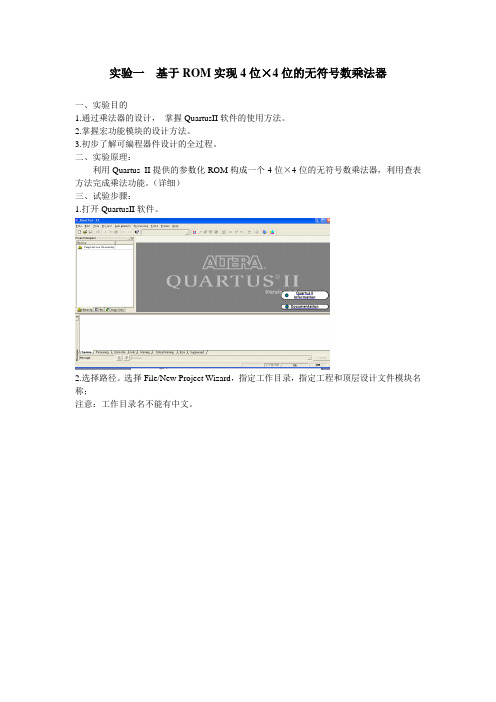

实验1 基于ROM实现4位×4位的无符号数乘法器

实验一基于ROM实现4位×4位的无符号数乘法器一、实验目的1.通过乘法器的设计,掌握QuartusII软件的使用方法。

2.掌握宏功能模块的设计方法。

3.初步了解可编程器件设计的全过程。

二、实验原理:利用Quartus II提供的参数化ROM构成一个4位×4位的无符号数乘法器,利用查表方法完成乘法功能。

(详细)三、试验步骤:1.打开QuartusII软件。

2.选择路径。

选择File/New Project Wizard,指定工作目录,指定工程和顶层设计文件模块名称;注意:工作目录名不能有中文。

3.添加设计文件。

将设计文件加入工程中。

单击“Next”,如果有已经建立好的Verilog或者原理图等文件可以在File name中选择路径然后添加,或者选择Add All添加所有可以添加的设计文件(.VHDL, .Verilog原理图等)。

如果没有直接点击“Next”,等建立好工程后再添加也可以,这里我们暂时不添加。

4.选择FPGA器件。

Family选择Cyclone,Available device选择EP1C12Q240C8, Package选择Any QFP, Pin Count 选择240,Speed grade选择8;点击“Next”。

5.选择外部综合器、仿真器和时序分析器。

Quartus II支持外部工具,可通过选中来指定工具的路径。

这里我们不做选择,默认使用Quartus II自带的工具。

6.结束设置。

单击“Next”,弹出“工程设置系统”窗口,上面列出了工程的相关设置情况。

最后单击“Finish”,结束工程设置。

7.建立原理图文件。

如果在建立工程时没有添加设计文件,这时可以新建文件再添加。

也可通过选择Project/Add/Remove Files In Project来添加外部文件。

8.添加文件到工程中。

点击“OK”,并选择File/Save As,选择和工程相同的文件名。

四位数字乘法器的设计

摘要现代社会在飞速发展,科学技术的发展越来越快。

4位二进制乘法器在十几种的应用相当广泛,是一些计算器的基本组成部分,其远离适用于很多计算器和大型计算机,他涉及到实训逻辑电路如何设计。

分析和工作等方面。

通过次电路更深刻的了解时许逻辑不见的工作原理,从而掌握如何根据需要设计满足要求的各种电路图,解决生活中的实际问题,将知识应用于实践中。

根据课题研究的目地是,绘制出电路的原理图,并且诠释每部分的功能;根据设计的电路图分析所需要的元器件种类和个数;根据技术指标指定实验反感,验证所设计的电路;进行实验数据处理和分析。

研究此课题,目地在于使我们了解4位乘法器在实际中的应用,了解它的具体工作原理以及它的基本电路图,使我们以后可以应用它解决一些实际问题。

通过对4位乘法器的设计,让我们懂得了理论与实际相结合是很重要的,只有理论知识是远远不够的,只有把所学的理论知识与实践相结合起来,从理论中得出结论,才能真正为社会服务,从而提高自己实际动手能力和独立思考的能力。

关键词:乘法器;VHDL;Max+plusII仿真4*4数字乘法器设计1.设计任务试设计一4位二进制乘法器。

4位二进制乘法器的顶层符号图如图1所示。

ENDP A B START1 0 1 11 1 0 1×1 0 1 10 0 0 01 0 1 11 0 1 111011001图1 4位乘法器顶层符号图 图2 4位乘法运算过程输入信号:4位被乘数A (A 3 A 2 A 1 A 0),4位乘数B (B 3 B 2 B 1 B 0),启动信号START 。

输出信号:8位乘积P (P 7 P 6 P 5 P 4 P 3 P 2 P 1 P 0),结束信号END 。

当发出一个高电平的START 信号以后,乘法器开始乘法运算,运算完成以后发出高电平的END 信号。

2.顶层原理图设计从乘法器的顶层符号图可知,这是一个9输入9输出的逻辑电路。

一种设计思想是把设计对象看作一个不可分割的整体,采用数字电路常规的设计方法进行设计,先列出真值表,然后写出逻辑表达式,最后画出逻辑图。

4位乘法器设计

U2:ls283 port map(o1=>sb(4 downto 1),o2=>sa,res=>result(7 downto 3));

U3:and4aport map(a=>op2,en=>op1(2),r=>sc);

signal sf:std_logic_vector(3 downto 0);

signal sg:std_logic_vector(3 downto 0);

--signal tmpl:std_logic;

begin

sg<=('0'&sf(3 downto 1));

--tmpl<=op1(1);

u0:and4aport map(a=>op2,en=>op1(1),r=>se);

(3)在芯片引脚设计时,每个脚多对应的时钟脉冲不一样,要看清要求。

(4)了解并行乘法器的设计原理,在给输入引脚输出引脚时钟脉冲时,要符合时钟脉冲的要求。

成绩:指导教师签名:

result(1)<=sd(0);

result(2)<=sb(0);

--result(7 downto 0)<='00000000'

end count;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity and4ais

signal sb:std_logic_vector(4 downto 0);

4x4乘法器的设计-lu

3、显示电路的要求

(1)显示电路的说明 两个r位的二进制数相乘,乘积为2r位。 因为r=4,计算后的乘积为8位二进制数,因 此需要将8位二进制数转换成三位BCD码的电路。 (2)电路采用动态显示

2009-7-1

卢庆莉

编写

4、8位二进制转换成三位BCD码的设计原理 (1)变换原理

?设计要求和提示在实验室教师授课半天?查阅资料设计电路同学独立完成1天半?讲述装配方法和调测要求2学时?调测第一周星期三至第二周星期三?验收第一周星期三至第二周星期四?撰写报告第二周星期五讲评收尾200971卢庆莉编写教学方法

电子电路课程设计

4×4乘法器的设计

卢庆莉 编写

2009-7-1

卢庆莉

编写

主要授课内容:

2009-7-1

卢庆莉

编写

2009-7-1

卢庆莉

编写

表 12.4.3 乘法器明细表

(2)说明 1)把可能实现的操作归并在一起,作为一个操 作步骤,再用适当的助记符表示控制信号,获 得处理器操作表。

2009-7-1 卢庆莉 编写

2)NOP表示控制器处于等待状态,处理器无操作。 3)CLR表示 A←“0”,CNT←“0”,M←X3-X0,Q←Y3-Y0 。 4)ADD表示 A← A+M 。

卢庆莉

编写

教学方法:

1. 教法

在实验室集中,分3次讲解: 电路设计提示 装配要求、调测方法 实验报告撰写要求

· 辅导实验、最后逐一验收

2.学习方法 认真自学《电子电路课程设计》相关章节 独立完成设计 独立装配、调测、撰写设计报告

2009-7-1 卢庆莉 编写

3.课程纪律:

阵列乘法器设计实验报告

阵列乘法器设计实验报告

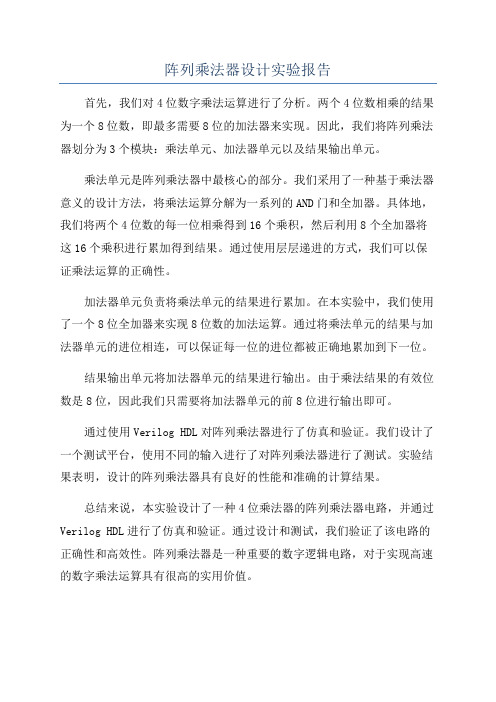

首先,我们对4位数字乘法运算进行了分析。

两个4位数相乘的结果为一个8位数,即最多需要8位的加法器来实现。

因此,我们将阵列乘法器划分为3个模块:乘法单元、加法器单元以及结果输出单元。

乘法单元是阵列乘法器中最核心的部分。

我们采用了一种基于乘法器意义的设计方法,将乘法运算分解为一系列的AND门和全加器。

具体地,我们将两个4位数的每一位相乘得到16个乘积,然后利用8个全加器将这16个乘积进行累加得到结果。

通过使用层层递进的方式,我们可以保证乘法运算的正确性。

加法器单元负责将乘法单元的结果进行累加。

在本实验中,我们使用了一个8位全加器来实现8位数的加法运算。

通过将乘法单元的结果与加法器单元的进位相连,可以保证每一位的进位都被正确地累加到下一位。

结果输出单元将加法器单元的结果进行输出。

由于乘法结果的有效位数是8位,因此我们只需要将加法器单元的前8位进行输出即可。

通过使用Verilog HDL对阵列乘法器进行了仿真和验证。

我们设计了一个测试平台,使用不同的输入进行了对阵列乘法器进行了测试。

实验结果表明,设计的阵列乘法器具有良好的性能和准确的计算结果。

总结来说,本实验设计了一种4位乘法器的阵列乘法器电路,并通过Verilog HDL进行了仿真和验证。

通过设计和测试,我们验证了该电路的正确性和高效性。

阵列乘法器是一种重要的数字逻辑电路,对于实现高速的数字乘法运算具有很高的实用价值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计报告课程设计题目:4乘4位阵列乘法器设计学生姓名:杨博闻学号:201120070115专业:计算机科学与技术班级:1120701指导教师:汪宇玲2014年1月4日一、设计目的1.掌握乘法器的原理及其设计方法。

2 .熟练应用CPLD 设计及EDA 操作软件。

二、设计设备1.TDN-CM+或TDN-CM++教学实验系统一套。

2 ·PC 微机一台。

3·ispDesignEXPERT 软件模型机数据通路结构框图三、设计原理本实验用CPLD 来设计一个4 ×4 位乘法器,相对于画电路图输入,用ABEL 语言描述是比较方便的。

其算式如下(其中括号中的数字表示在ABEL 源程序描述中的功能块调用编号):a3 a2 a1 a0 ×b3 b2 b1 b0----------------------------------------------------------------------------------------------------------a3b0(10) a2b0(6) a1b0(3) a0b0(1)a3b1(13) a2b1(9) a1b1(5) a0b1(2)a3b2(15) a2b2(12) a1b2(8) a0b2(4)+a3b3(16) a2b3(14) a1b3(11) a0b3(7)----------------------------------------------------------------------------------------------------------- p7 p6 p5 p4 p3 p2 p1 p0四、设计步骤1.安装EDA 软件打开计算机电源,进入Windows 系统,安装上述ispDesignEXPERT 软件。

安装完成后,桌面和开始菜单中则建有ispDesignEXPERT 软件图标。

2.用ispDesignEXPERT 软件根据上述乘法的逻辑原理用ABEL 语言编写功能描述程序。

其在1032 芯片中对应的管脚如图:3.编辑、编译和下载使用ispDesignEXPERT 软件编辑源程序并进行编译,然后打开实验系统电源,将生成的JEDEC 文件下载到ispLSI1032 中去。

4 .连接实验电路按下图连接实验电路。

5 .给定操作数,观察乘法器输出将SWITCH UNIT 单元中的SW-B、AR 开关置为低电平状态。

在INPUTDEVICE 单元中的8 个开关的高4 位为乘数A ,低四位为被乘数B ,而相乘的结果将在OUTPUT DEVICE单元中的数码管中以十六进制形式显示。

给 A 和B置不同的数,观察相乘的结果。

五、设计结果:六、ABEL源码MODULE multiplyTITLE '4 bit multiplier'"Inputsa3,a2, a1, a0 pin 34,35,36,37;b3,b2, b1, b0 pin 38,39,40,41;"Outputsp7,p6,p5,p4,p3,p2,p1,p0 pin 45,46,47,48,49,50,51,52 istype 'com,invert';"Set declarationsaset = [a3,a2,a1,a0];bset = [b3,b2,b1,b0];product = [p7,p6,p5,p4,p3,p2,p1,p0];"Sub-module declarations, with default input values"In this case, all inputs default to 0 if not used.adder interface (a=0, b=0, sin=0, cin=0 -> sum, carry);"Sub-module instancesablk1 functional_block adder;ablk2 functional_block adder;ablk3 functional_block adder;ablk4 functional_block adder;ablk5 functional_block adder;ablk6 functional_block adder;ablk7 functional_block adder;ablk8 functional_block adder;ablk9 functional_block adder;ablk10 functional_block adder;ablk11 functional_block adder;ablk12 functional_block adder;ablk13 functional_block adder;ablk14 functional_block adder;ablk15 functional_block adder;ablk16 functional_block adder;Equationsp7 = ablk16.carry; " Product output bit 7 p6 = ablk16.sum; " bit 6p5 = ablk14.sum; " bit 5p4 = ablk11.sum; " bit 4p3 = ablk7.sum; " bit 3p2 = ablk4.sum; " bit 2p1 = ablk2.sum; " bit 1p0 = ablk1.sum; " bit 0ablk16.sin = ablk15.carry;ablk16.cin = ablk14.carry;ablk16.a = a3;ablk16.b = b3;ablk15.sin = ablk13.carry;ablk15.cin = ablk12.carry;ablk15.a = a3;ablk15.b = b2;ablk14.sin = ablk15.sum;ablk14.cin = ablk11.carry;ablk14.a = a2;ablk14.b = b3;ablk13.cin = ablk9.carry; ablk13.a = a3;ablk13.b = b1;ablk12.sin = ablk13.sum; ablk12.cin = ablk8.carry; ablk12.a = a2;ablk12.b = b2;ablk11.sin = ablk12.sum; ablk11.cin = ablk7.carry; ablk11.a = a1;ablk11.b = b3;ablk10.a = a3;ablk10.b = b0;ablk9.sin = ablk10.sum; ablk9.cin = ablk6.carry; ablk9.a = a2;ablk9.b = b1;ablk8.sin = ablk9.sum; ablk8.cin = ablk5.carry; ablk8.a = a1;ablk8.b = b2;ablk7.sin = ablk8.sum; ablk7.cin = ablk4.carry; ablk7.a = a0;ablk7.b = b3;ablk6.a = a2;ablk6.b = b0;ablk5.sin = ablk6.sum; ablk5.cin = ablk3.carry; ablk5.a = a1;ablk5.b = b1;ablk4.sin = ablk5.sum;ablk4.cin = ablk2.carry; ablk4.a = a0;ablk4.b = b2;ablk3.a = a1;ablk3.b = b0;ablk2.sin = ablk3.sum; ablk2.cin = ablk1.carry; ablk2.a = a0;ablk2.b = b1;ablk1.a = a0;ablk1.b = b0;Test_vectors([aset, bset] -> product) [ 0 , 0 ] -> 0; [ 0 , 1 ] -> 0; [ 1 , 2 ] -> 2; [ 2 , 3 ] -> 6; [ 3 , 4 ] -> 12; [ 3 , 5 ] -> 15; [ 4 , 5 ] -> 20; [ 4 , 6 ] -> 24; [ 5 , 6 ] -> 30; [ 5 , 7 ] -> 35; [ 6 , 7 ] -> 42; [ 7 , 7 ] -> 49; [ 8 , 8 ] -> 64; [ 9 , 9 ] -> 81 ; [ 10 , 11 ] -> 110; [ 12 , 13 ] -> 156; [ 13 , 14 ] -> 182; [ 13 , 15 ] -> 195; [ 14 , 15 ] -> 210; END六、心得体会经过这次课程设计充分地实践了课上所学到的知识,提高了动手能力,把理论知识运用到实践中。

对阵列乘法运算器的结构以及原理得到了进一步的了解。

在设计的过程中也遇到了很多的问题,最大的问题就是ABEL源码的理解,在老师的教导下,了解了这一源码的形成。

通过本次课程设计受益良多。