Zynq FSBL代码导读

1、ZedBoard制作FSBL

创建一个最简单的Zynq项目,如下:选择Next点击Next,我们不需要添加Verilog/VHDL源文件或者约束文件,勾选Do not specify sources at this time点击Next,选择Boards,并选择ZedBoard Zynq Evaluation and Development Kit点击Next点击Finish完成创建向导,出现如下界面先创建一个Block Design,点击如下地方输入名称等待创建完成在Diagram视图中点击Add IP在弹出的窗口中输入Zynq进行搜索,在结果中选择第一个点击Run Block Automation,并选择/processing_system7_0完成自动连线完成之后双击ZYNQ进行自定义配置出现取消不需要的部分:首先点击Clock Configuration,展开PL Fabric Clocks,取消FCLK_CLK0该时钟是PS提供给PL的时钟,在结构图中的如下部分取消之后Diagram中的FCLK_CLK0会消失取消前如下图:取消后如下图另外,我们要取消掉如下引脚对于TTC,我们点击如下部分,取消掉TTC再点击取消掉AXI GP0 interface最后取消掉QSPI点击OK完成回到Block Design的sources视图在System上右键选择Create HDL Wrapper完成后点击左边Flow Navigator中的Generate BitStream等待Vivado完成综合、实现、生成bitstream之后,出现如下点击Cancel取消。

点击File->Export->Export Hardware for SDK点击File->Export->ExportHardware,确认后点击File->Launch SDK,系统会自动开启SDK软件在SDK中点击菜单File->New->Application Project。

zynq的启动方式

Zynq-7000AP SOC器件有效利用了片上CPU来帮忙配置。

在没有外部JTAG的情况下,处理系统(PS)与可编程逻辑(PL)都必须依靠PS来完成芯片的初始化配置。

ZYNQ的两种启动模式:从BootROM主动启动,从JTAG被动启动。

ZYNQ的启动配置分多级进行的。

配置至少需要两步,但通常按如下三个阶段进行:阶段0:该阶段简称为BootROM,控制着整个芯片的初始化过程。

放在BootROM中的代码是固化的,不可修改的,处理器核在上电或者热启动时自动执行这部分代码。

阶段1:该阶段的启动加载器(FSBL)也可以由用户代码控制。

阶段2:这阶段通常可以是用户的PS端的设计代码,当然也可以是第二阶段的启动加载器(SSBL),这个阶段可以完全由用户控制,是可选的。

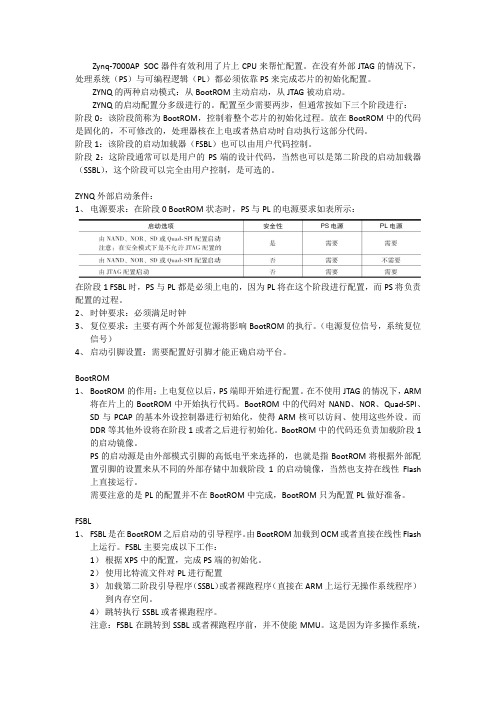

ZYNQ外部启动条件:1、电源要求:在阶段0 BootROM状态时,PS与PL的电源要求如表所示:在阶段1 FSBL时,PS与PL都是必须上电的,因为PL将在这个阶段进行配置,而PS将负责配置的过程。

2、时钟要求:必须满足时钟3、复位要求:主要有两个外部复位源将影响BootROM的执行。

(电源复位信号,系统复位信号)4、启动引脚设置:需要配置好引脚才能正确启动平台。

BootROM1、BootROM的作用:上电复位以后,PS端即开始进行配置。

在不使用JTAG的情况下,ARM将在片上的BootROM中开始执行代码。

BootROM中的代码对NAND、NOR、Quad-SPI、SD与PCAP的基本外设控制器进行初始化,使得ARM核可以访问、使用这些外设。

而DDR等其他外设将在阶段1或者之后进行初始化。

BootROM中的代码还负责加载阶段1的启动镜像。

PS的启动源是由外部模式引脚的高低电平来选择的,也就是指BootROM将根据外部配置引脚的设置来从不同的外部存储中加载阶段1的启动镜像,当然也支持在线性Flash 上直接运行。

需要注意的是PL的配置并不在BootROM中完成,BootROM只为配置PL做好准备。

可扩展处理平台Zynq的启动过程

可扩展处理平台Zynq的启动过程

本文主要介绍zynq启动过程,主要包括BootROM和FSBL等的执行过程。

硬件启动过程

重新上电或POR复位后进行硬件启动过程

扫描启动引脚设置,并存入只读寄存器slcr.BOOT_MODE中

若使能pll,则等到pll输出时钟;若旁路pll,则直接使用ps_clk时钟

更详细硬件启动过程可以参考下图

BootROMBootROM在POR复位后经过硬件启动后自动运行,也可在非POR复位后直接运行(不经过硬件启动),其内容固化在内部ROM中,不能修改,主要初始化MMU和一些系统资源(以使其满足BootROM执行的要求)以及加载FSBL程序段等。

BootROM 在CPU 0执行,而CPU 1执行WFE指令

主要过程如下:

硬件启动后BootROM将初始化MMU、NAND、NOR、QSPI、SD和PCAP等基本外设判断启动设备(决定于硬件启动过程时扫描的启动模式引脚,即寄存器slcr.BOOT_MODE)并搜索boot镜像头信息,各启动模式搜索范围:

Quad-SPI,头16 MB空间搜索

NAND,头128MB空间搜索

NOR,头32MB

SD卡中只加载一次,不会搜索

BootROM会根据启动模式配置MIO,还会根据读取的boot镜像头信息的寄存器初始化参数部分配置时间优化寄存器

从指定启动设备中加载SFBL到OCM(加载时也会读取头部信息确定加密状态,文件长度等,若加密则还需解密后加载到OCM,BootROM头信息都不会加密),另外还支持直接在QSPI或NOR中执行(从头部信息中文件长度为0时,这时就不用加载到OCM了)。

Zynq入门之GPIO操作与示例

Zynq⼊门之GPIO操作与⽰例ZYNQ中的PS部分与PL部分是独⽴的,可以独⽴运⾏,那么我们对于ZYNQ的学习研究就可以结合嵌⼊式学习的⽅法来进⾏。

⾸先是GPIO的使⽤,基于ZYNQ的特殊性,其GPIO分为MIO(multiuse I/O)和EMIO(extendable multiuse I/O)两种,GPIO的相关信号被分为了4个bank,bank0与bank1为MIO信号,bank2与bank3为EMIO信号,MIO具有54根三态GPIO引脚,EMIO可以达到192根信号,64根输⼊,128根输出。

由XILINX的官⽅⽂件还可以看出,EMIO是与PL部分直接相连的。

MIO与EMIO的控制寄存器主要有以下部分控制寄存器的位宽及每个寄存器的作⽤均给出了详细的解释。

以最基本的使⽤GPIO点灯为例,直接使⽤XPS+SDK进⾏设计。

⾸先打开XPS,进⾏PS部分的设计,这部分设计主要是针对PS中IO,uart,interrupt(均为IP核的形式)等进⾏定义,相当于在⼀个平台上搭积⽊,需要哪⼀部分的功能就将那部分的功能加⼊平台中。

我们使⽤BSB(Base System Builder) Wizard板级开发向导新建⼀个项⽬,输⼊⽂件名地址。

选择ZC702这块板卡,选项均为默认。

删除SW与LED外设。

在system assembly view中可以看到外设,XILINX公司为我们提供了ZEDboard的初始化⽂件zedboard_Revc_v1或v2,可以使⽤这个⽂件对zedboard 的外设进⾏初始化。

单击import,导⼊zedboard_Revc_v1即完成了ZEDboard的外设初始化。

添加GPIO的IP核AXI_General Purpose I/O,使⽤channel1,位宽为1,使⽤process_system7.0连接。

在Bus Interface中可以看到添加的GPIO挂载到了processing_system7下。

Zynq的启动方式学习

Zynq-7000AP SOC器件有效利用了片上CPU来帮忙配置。

在没有外部JTAG的情况下,处理系统(PS)与可编程逻辑(PL)都必须依靠PS来完成芯片的初始化配置。

ZYNQ的两种启动模式:从BootROM主动启动,从JTAG被动启动。

ZYNQ的启动配置分多级进行的。

配置至少需要两步,但通常按如下三个阶段进行:阶段0:该阶段简称为BootROM,控制着整个芯片的初始化过程。

放在BootROM中的代码是固化的,不可修改的,处理器核在上电或者热启动时自动执行这部分代码。

阶段1:该阶段的启动加载器(FSBL)也可以由用户代码控制。

阶段2:这阶段通常可以是用户的PS端的设计代码,当然也可以是第二阶段的启动加载器(SSBL),这个阶段可以完全由用户控制,是可选的。

ZYNQ外部启动条件:1、电源要求:在阶段0 BootROM状态时,PS与PL的电源要求如表所示:在阶段1 FSBL时,PS与PL都是必须上电的,因为PL将在这个阶段进行配置,而PS将负责配置的过程。

2、时钟要求:必须满足时钟3、复位要求:主要有两个外部复位源将影响BootROM的执行。

(电源复位信号,系统复位信号)4、启动引脚设置:需要配置好引脚才能正确启动平台。

BootROM1、BootROM的作用:上电复位以后,PS端即开始进行配置。

在不使用JTAG的情况下,ARM将在片上的BootROM中开始执行代码。

BootROM中的代码对NAND、NOR、Quad-SPI、SD与PCAP的基本外设控制器进行初始化,使得ARM核可以访问、使用这些外设。

而DDR等其他外设将在阶段1或者之后进行初始化。

BootROM中的代码还负责加载阶段1的启动镜像。

PS的启动源是由外部模式引脚的高低电平来选择的,也就是指BootROM将根据外部配置引脚的设置来从不同的外部存储中加载阶段1的启动镜像,当然也支持在线性Flash上直接运行。

需要注意的是PL的配置并不在BootROM中完成,BootROM只为配置PL做好准备。

关于XilinxFPGAZYNQ的引脚定义

关于XilinxFPGAZYNQ的引脚定义器件的引脚定义如何获得?在官⽹找到Pin-Out⽂件,⽹址:⽂件⾥⾯给出了引脚编号对应的引脚名称、IO Bank分组、IO种类(MIO,High Rate通⽤IO,DDR等)。

这些封装对应到Processing System 7 IP中的MIO设定,就可以得到MIO的固定引脚。

另外,ZYNQ7000系列的引脚定义⽂件在这⾥(CSV和TXT)://**********************************************************************************************************************************//**********************************************************************************************************************************//**********************************************************************************************************************************例如,IP核中选择以太⽹MAC控制器的引脚是MIO[27:16],则在下表中寻找MIO[16],……,MIO[27]即可,最左边即是引脚编号。

(电路设计时注意Bank500和Bank501的IO电压分配)在UG585(v1.12.2)中的Table 2-4:MIO-at-a-Glance中,对MIO的功能进⾏了详细的描述:表中信息包括了MIO编号、所在的IO Bank、引脚复⽤情况、引脚对应外设的功能。

如果使⽤以太⽹控制器ETH0,则MIO16是TX_CLK,MIO17~MIO20是TX_DATA[0]~TX_DATA[3],MIO21是TX_CTRL对于不明确的MIO引脚定义,将⿏标悬停在MIO编号栏就可以看到信号定义:我们还通过Block Diagram综合后的报告查看,⽬标位于:${Vivado Project Path}\eth_mac_01.srcs\sources_1\bd\block_01\ip\block_01_processing_system7_0_2,是以html格式呈现的:这样就完成了MIO功能到封装引脚的映射过程。

Zynq学习笔记(基本设计流程)

main(){

u32 Status;

u32 value = 0;

u32 period = 0;

u32 brightness = 0;

print("begin debug program\n\r");

/*

* Initialize the GPIO driver

*/

Status = XGpio_Initialize(&Gpio, GPIO_EXAMPLE_DEVICE_ID);

配置PS的bank电平,bank0:LVCMOS3.3V,bank1:LVCMOS1.8V

打开Memory Interfaces,配置QSPI。1-6,8(Feedback Clk)。点“+”可以看配置后的各个参数。

点击I/O Peripherals,配置UART1:MIO48..49,Baud Rate配置在PS-PL Configuratin中。

18.添加输出端口:LEDS。

LEDS,

output [7:0] LEDS;

19.保存文件。

20.综合。点击Run Analysis。综合完成后,点击“Open Synthesized Design”,打开综合后的网表设计,准备分配引脚。

21.选择菜单“Layout”/IO Planning,在右下部的I/O Port找到LEDS,打开选择LEDS[7]并设置Site=U14,依次设置其他LEDS的引脚。LEDS[0:7]=T22,T21,U22,U21,V22,W22,U19,U14.

11.产生时钟输出端口。右击:Create Port,鼠标移动到端口上,出现铅笔,连接FCLK_CLK0.

12.其它信号保持默认。

ZYNQ笔记(5):软中断实现核间通信

ZYNQ笔记(5):软中断实现核间通信 ZYNQ包括⼀个 FPGA 和两个 ARM,多个 ARM 核⼼相对独⽴的运⾏不同的任务,每个核⼼可能运⾏不同的操作系统或裸机程序,但是有⼀个主要核⼼,⽤来控制整个系统以及其他从核⼼的允许。

因此我们可以在 CPU0 和 CPU1 中独⽴跑不同的应⽤程序,发挥双核的⾮对称性架构的优势和性能。

从软件的⾓度来看,多核处理器的运⾏模式主要有三种: ① AMP(⾮对称多进程):多个核⼼相对独⽴的运⾏不同的任务,每个核⼼可能运⾏不同的操作系统或裸机程序,但是有⼀个主要核⼼,⽤来控制整个系统以及其它从核⼼的运⾏。

② SMP(对称多进程):⼀个操作系统同等的管理各个内核,例如 PC 机。

③ BMP(受约束多进程):与 SMP 类似,但开发者可以指定将某个任务仅在某个指定内核上执⾏默认情况下。

裸机程序 ZYNQ 仅运⾏⼀个 CPU,这⾥主要讲解 AMP 模式下,两个 CPU 同时运⾏的裸机程序开发⽅法。

⼀、核间中断原理(软中断SGI) 软中断的 ID 都是从0到15,并且都是上升沿触发,主要⽤于核间中断或者 CPU ⾃⼰中断⾃⼰。

中断函数如下:XScuGic_SoftwareIntr(&InterruptController, //指向GIC指针INTC_CPU0, //需要中断的CPU IDXSCUGIC_SPI_CPU0_MASK); //使能该CPU会接受中断⼆、ARM启动过程1.ARM ⾥有个 ROM,存储了⼀段程序,ROM起来后从 SD 卡读取数据2.启动 FSBL(First Boot Loader)第⼀启动项(有模板)3.加载 bit(FPGA配置程序),同时加载 elf(ARM应⽤程序),如果是操作系统则 elf 替换成 uBoot三、搭建软件 CPU0 和 CPU1 ⾮对称环境1.创建 amp_fsbl ⽤于⽣成烧写镜像的时候加载 core0 和 core1的代码。

Xilinx Vivado zynq7000 入门笔记

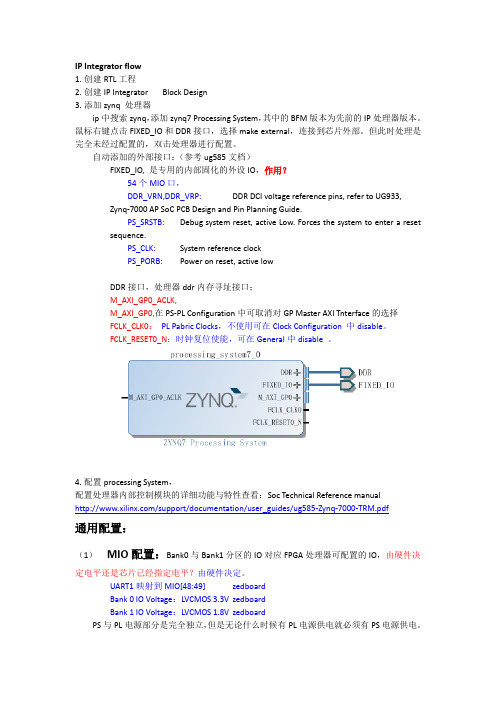

IP Integrator flow1.创建RTL工程2.创建IP Integrator Block Design3.添加zynq 处理器ip中搜索zynq,添加zynq7 Processing System,其中的BFM版本为先前的IP处理器版本。

鼠标右键点击FIXED_IO和DDR接口,选择make external,连接到芯片外部。

但此时处理是完全未经过配置的,双击处理器进行配置。

自动添加的外部接口:(参考ug585文档)FIXED_IO, 是专用的内部固化的外设IO,作用?54个MIO口,DDR_VRN,DDR_VRP: DDR DCI voltage reference pins, refer to UG933, Zynq-7000 AP SoC PCB Design and Pin Planning Guide.PS_SRSTB: Debug system reset, active Low. Forces the system to enter a reset sequence.PS_CLK: System reference clockPS_PORB: Power on reset, active lowDDR接口,处理器ddr内存寻址接口;M_AXI_GP0_ACLK,M_AXI_GP0,在PS-PL Configuration中可取消对GP Master AXI Tnterface的选择FCLK_CLK0:PL Pabric Clocks,不使用可在Clock Configuration 中disable。

FCLK_RESET0_N:时钟复位使能,可在General中disable 。

4.配置processing System,配置处理器内部控制模块的详细功能与特性查看:Soc Technical Reference manual/support/documentation/user_guides/ug585-Zynq-7000-TRM.pdf通用配置:(1)MIO配置:Bank0与Bank1分区的IO对应FPGA处理器可配置的IO,由硬件决定电平还是芯片已经指定电平?由硬件决定。

zynq读法

zynq读法Zynq是一个高度集成的系统级芯片,由Xilinx公司开发。

它将双核ARM Cortex-A9处理器与FPGA相结合,使它成为开发嵌入式系统的完美选择。

在本文中,我将向您介绍如何使用Zynq读板,并提供一些最佳实践。

首先,我们需要从特定供应商购买Zynq板。

接下来,我们需要下载并安装开发工具集。

Xilinx公司提供了一款名为Vivado的工具,它允许我们设计、仿真和编程FPGA。

此外,还需要下载一些必须的软件库或API。

接下来,我们需要为ARM核心编写代码。

我们可以使用C或C++编程语言。

开发环境包含一组头文件,允许我们访问底层硬件。

我们可以编写的一些常见的操作包括访问GPIO、读写串口数据、读写SD卡等等。

在FPGA方面,我们需要使用硬件描述语言(HDL),如Verilog或VHDL。

虽然这些语言看起来不太友好,但它们为我们提供了非常底层的控制,允许我们设计复杂的、高性能的电路。

我们可以使用Vivado 工具创建和编辑HDL文件。

Vivado工具允许我们设置各种约束,如时序、延迟等,以确保我们的电路行为符合我们的期望。

与传统微控制器相比,Zynq带来了一些新的挑战。

我们需要考虑如何有效地使用FPGA资源。

如果我们没有妥善设计电路,我们可能会发现我们没有足够的可用资源来容纳我们的设计。

此外,我们还需要考虑如何在FPGA部分和ARM部分之间进行通信。

在设计和编写代码后,我们需要将代码编译和生成可执行文件。

我们可以使用Vivado SDK工具链来生成许多形式的输出。

我们可以将代码编译为ARM可执行文件,将FPGA构建为使用的位流文件,然后将它们合并到一起。

在最后一步,我们需要将可执行文件传输到Zynq板上。

我们可以使用UART或以太网连接到板子。

如果我们正在测试一个USB设备,我们需要使用一个JTAG或OCD连接。

最后,Zynq读板是一个高度集成的芯片。

我们可以在单个芯片上执行许多复杂的任务,从FPGA控制到嵌入式处理。

Zynq启动流程

Zynq启动流程前⾔Zynq启动流程和ARM处理器类似,PS部分是启动和配置过程的主设备,芯⽚引导必须由处理器驱动,系统上电复位后会读取设备模式引脚来决定从什么设备启动芯⽚。

如下表Boot Devices条⽬所⽰,其中黄⾊代表该条⽬下的默认设置,⽐如Boot Devices默认设置是SD Card,默认从SD卡启动芯⽚下图中的JP7-JP11的5个条线帽就是⽤于设置设备模式引脚电平的启动步骤PS确定好从什么设备启动后,接着的启动过程分为以下三个阶段0. Stage-0 执⾏BootROM代码,不可修改1. Stage-1 执⾏FSBL(first boot loader)代码,⽤户可修改。

如果是裸机程序也可以不需要这个阶段直接跳到下⼀阶段。

2. Stage-2 执⾏⽤户裸机程序或者操作系统的启动引导程序SSBL(second boot loader)关于BootROM:位于Zynq⽚内,功能是初始化L1 cache和基本的总线系统,以及从指定的外部存储器加载Stage-1的FSBL代码到⽚内存储器(OCM)。

但是要使Stage-0之后的代码被Stage-0的BootROM识别,还需要为Stage-0之后的代码(可能是Stage-1的FSBL,也可能是Stage-2的裸机程序,因为没有调⽤BSP函数的裸机程序是可以不需要FSBL的)添加⼀个头部,制作成引导镜像。

可以使⽤SDK的BootGen⼯具为裸机程序elf⽂件创建引导镜像Boot.bin,将其复制到SD卡中,并且设置板⼦从SD卡启动就可以执⾏程序。

使⽤SDK⼯具创建SD卡启动镜像BOOT.BIN= f(FSBL.elf+PL.bit+PS.elf)PL.b it和PS.e lf采⽤中⽣成的PL.bit和PS.elf。

制作F SB L.e lf 新建Zynq FSBL⼯程等待⼯程建⽴完毕,FSBL.elf就在⼯程⽂件夹的Debug⽂件夹下制作B OOT.B I N使⽤SDK的Create Boot Image选择好output路径放置⽣成的BOOT.BIN和output.bif。

详细解读Zynq的三种启动方式(JTAG,SD,QSPI)

详细解读Zynq的三种启动方式(JTAG,SD,QSPI)本文介绍zynq上三种方式启动文件的生成和注意事项,包括只用片上RAM (OCM)和使用DDR3两种情况。

JTAG方式JTAG方式是调试中最常用的方式,在SDK中在Project Explorer窗口工程上右键-Debug As-Debug ConfiguraTIons可以看到以下窗口首次打开左边窗口中Xilinx C/C++ applicaTIon(GDB)下没有子项,这时双击Xilinx C/C++ applicaTIon(GDB)即可新建一个调试;这时右边窗口会自动填充如上图,若没有则手动填入;在右边ApplicaTIon窗口指定要下载调试的.elf文件;在右边STDIO Connection可以指定标准输入输出串口,即printf打印串口,若这里选择开发板上uart的com口,则调试时printf的信息打印到调试时Console窗口,同时也可从Console窗口输入数据,以此将数据通过串口发送到开发板上以上设置完成后点击Debug即可开始调试;若以上在Project Explorer窗口工程上右键-Run As-Run Configurations;配置与此类似,最后点击run即可开始运行,只是不是调试而是直接上板运行。

只用OCM只用OCM指不使用DDR3的方式,与使用DDR3的方式略有不同。

这里不用FSBL来加载PL部分的.bit文件和第二阶段启动程序(裸机程序),而直接用BootROM加载裸机程序到OCM,即将裸机程序当做FSBL来运行,当然还要以下处理才可以:包含进头文件:#include ps7_init.h在裸机程序main函数开始处调用:ps7_init()从design_1_wrapper_hw_platform_1目录复制ps7_init.c和ps7_init.h文件到裸机程序所在的src目录中注意:这里样调用ps7_init()只适用于只用OCM的情况,经测试打开DDR3后再这样调用会在ps7_init()中初始化失败,调试发现在初始化PLL时失败(原因未知)。

zynq tf卡读出函数

zynq tf卡读出函数在Zynq系列芯片中,可以使用SD卡接口来读取TF卡的内容。

以下是一个简单的C语言函数示例,用于在Zynq上读取TF卡的数据:cinclude <stdio.h>include "xil_io.h"include "xil_printf.h"include "ff.h"需要引入FatFs库define TF_CARD_MOUNT_POINT "0:/"define FILENAME "test.txt"void readTFCard() {FIL file;FRESULT res;挂载TF卡res = f_mount(&TFCard, TF_CARD_MOUNT_POINT, 1);if (res != FR_OK) {xil_printf("无法挂载TF卡,错误码:%d\r\n", res);return;}打开文件res = f_open(&file, FILENAME, FA_READ);if (res != FR_OK) {xil_printf("无法打开文件,错误码:%d\r\n", res);f_mount(NULL, TF_CARD_MOUNT_POINT, 0);卸载TF卡return;}读取文件内容UINT bytesRead;char buffer[256];memset(buffer, 0, sizeof(buffer));while (!f_eof(&file)) {res = f_read(&file, buffer, sizeof(buffer) - 1, &bytesRead);if (res != FR_OK) {xil_printf("读取文件错误,错误码:%d\r\n", res);break;}处理读取到的数据xil_printf("读取到的数据:%s\r\n", buffer);}关闭文件f_close(&file);卸载TF卡f_mount(NULL, TF_CARD_MOUNT_POINT, 0);}int main() {readTFCard();return 0;}在这个示例中,需要使用FatFs库来进行TF卡的挂载、文件操作等。

Zynq7000启动流程介绍

Zynq7000启动流程介绍打了半天。

一不小心碰到鼠标后退键,啥都木了。

再来吧一开始呢,我以为Zynq7000是一个加上了双核A9处理器的FPGA芯片。

但是看了资料后,才发现,其实不是这么回事Zynq7000就如同他的名字一样,Zynq-7000 Extensible Processing Platform,是一个可扩展处理平台,简单说就是有个FPGA做外设的A9双核处理器。

所以,它的启动流程自然也和FPGA完全不同,而与传统的ARM处理器类似。

Zynq7000支持从多种设备启动,包括Jtag, NAND, parallel NOR, Serial NOR (Quad-SPI), 以及SD卡。

按手册说明除了Jtag之外的启动方式均支持安全启动,使用AES、SHA256加密后的启动代码(不过在勘误里说到,当前硅片版本的无法正常使用secure configuration功能,所以俺就不介绍它鸟)还是按照时间顺序来介绍下具体流程吧1.在器件上电运行后,处理器自动开始Stage-0 Boot,也就是执行片内BootROM中的代码2.BootROM会初始化CPU和一些外设,以便读取下一个启动阶段所需的程序代码,FSBL(First Stage Bootloader)。

不过这又有一个问题了----之前说到,Zynq支持多种启动设备,BootROM怎么知道从哪个启动设备里去加载FSBL?这就得靠几个特殊的MIO引脚来选择了,具体见下图BootROM会去读取MIO[2..8],从而确定启动设备,将选定设备的头192Kbyte内容,也就是FSBL,复制到OCM中,并将控制器交给FSBL,。

3,FSBL启动时可以使用整块256Kb的OCM,当FSBL开始运行后,器件就正式由咱自己控制了。

Xilinx 提供了一份FSBL代码,如果没什么特殊要求,可以直接使用。

按照手册说明,FSBL应该完成以下几件事。

1). 使用XPS提供的代码,继续初始化PS2). 将bitstream写入PL(配置FPGA),不过这一步也可以以后再做3). 将接下来启动用的Second Stage Bootloader(SSBL,一般就是U-Boot一类的东西),或者裸奔程序,复制到内存中4). 跳到SSBL运行去4,接下来的步骤就没啥特别了,Uboot开始运行,初始化好Linux启动环境,然后开始运行Linux系统。

ZYNQ笔记(3):GPIO的使用(MIO、EMIO)——led灯

ZYNQ笔记(3):GPIO的使⽤(MIO、EMIO)——led灯⼀、GPIO原理1.GPIO介绍 程序员通过软件代码可以独⽴和动态地对每个 GPIO 进⾏控制,使其作为输⼊、输出或中断。

(1)通过⼀个加载指令,软件可以读取⼀个 GPIO 组内所有 GPIO 的值。

(2)通过⼀个保存指令,将数据写到⼀个 GPIO 组内的⼀个或多个 GPIO 。

(3)在 ZYNQ-7000 SOC 内,GPIO 模块的控制寄存器和状态寄存器采⽤存储器映射⽅式,它的基地址为 0xE000_A000。

(4)每个GPIO都提供了可编程的中断。

通过软件程序代码可以实现:①读原始和屏蔽中断的状态;②可选的敏感性,包括电平敏感或边沿敏感。

2.MIO与EMIO的异同 MIO(multiuse I/O):多功能IO接⼝,属于Zynq的PS部分,Zynq7000 系列芯⽚有 54 个 MIO。

它们分配在 GPIO 的 Bank0 和 Bank1 上,这些引脚可以⽤在GPIO、SPI、UART、TIMER、Ethernet、USB等功能上,每个引脚都同时具有多种功能,故叫多功能IO接⼝。

这些 IO 与 PS 直接相连。

不需要添加引脚约束,MIO 信号对 PL部分是透明的,不可见。

所以对 MIO 的操作可以看作是纯 PS 的操作。

GPIO 的控制和状态寄存器基地址为:0xE000_A000,我们 SDK 下软件操作底层都是对于内存地址空间的操作。

EMIO(extendable multiuse I/O):扩展MIO,依然属于Zynq的PS部分,只是连接到了PL上,再从PL的引脚连到芯⽚外⾯实现数据输⼊输出。

Zynq7000系列芯⽚有 64 个 EMIO,它们分配在 GPIO 的 Bank2 和 Bank3 上,当 MIO 不够⽤时,PS 可以通过驱动 EMIO 控制 PL 部分的引脚,EMIO 的使⽤相当于,是⼀个 PS + PL 的结合使⽤的例⼦。

MYiRZynqFPGA使用手册

MYiRZynqFPGA使用手册MYiR Zynq FPGA 使用手册版本V1.02015年5月28日版本记录目录目录 (3)简介 (5)第1章HelloWorld (6)1.1 新建Vivado工程 (6)1.2 新建Block Design (7)1.3 设置工程使用Verilog语言 (8)1.4 添加PS的IP核并配置 (9)1.5 生成综合文件 (11)1.6 生成FPGA顶层文件 (12)1.7 综合实现 (12)1.8 导出硬件配置文件 (13)1.9 启动SDK,新建SDK工程 (13)1.10 修改源码 (14)1.11 生成boot.bin启动文件 (15)第2章GPIO操作1 (16)2.1 新建Vivado工程 (16)2.2 添加IP核并配置 (16)2.3 综合实现 (16)2.4 新建SDK工程 (16)2.5 生成boot.bin运行 (16)第3章GPIO操作2 (17)3.1 新建Vivado工程 (17)3.2 添加IP核并配置 (17)3.3 综合 (17)3.4 分配引脚 (18)3.5 实现和生成bitstream (19)3.6 导出硬件配置文件 (19)3.7 SDK新建FSBL工程分配引脚 (20)3.8 SDK新建app工程 (20)3.9 生成boot.bin启动文件 (21)第4章GPIO操作3 (23)4.1 新建Vivado工程 (23)4.2 添加axi gpio ip核 (23)4.3 综合 (25)4.4 分配引脚 (25)4.5 生成boot.bin (26)第5章PL中断 (27)5.1 新建Vivado工程 (27)5.2 添加其他IP核 (27)5.3 综合分配引脚 (31)5.4 生成boot.bin启动文件 (31)附录A 售后服务与技术支持 (33)简介例程使用的软件版本是Vivado Design Suite 2014.4,安装之后会有4个软件,Vivado 2014.4,Xilinx SDK 2014.4,System Generator 2014.4和Vivado HLS 2014.4。

Lab06 - FSBL 2013_3_02

______________________________________________________________

ZedBoard Lab 6 : 7

Experiment 2: Investigate the FSBL

Now that we have the FSBL generated and built, it is worth taking a minute to examine what we have! Experiment 2 General Instruction: Examine the FSBL sources. Open ps7_init.c and review the code. Experiment 2 Step-by-Step Instructions: 1. Expand zynq_fsbl_0 src. Notice the various .c and .h files that SDK pulled together for the FSBL.

In Lab 5, we used the SDK JTAG connection and a TCL script to initialize the ARM processor registers. This was convenient and worked well for debugging. However, a real product is not going to be tethered to a JTAG connection. We need a method to initialize the ARM in an embedded fashion. This is done with code called the First Stage Boot Loader or FSBL. Xilinx SDK includes a template to automatically create the FSBL for us. By interpreting the provided hardware platform, SDK will generate a fully functional FSBL for us. This is one of the many useful things that SDK automates to make your job as a software developer a bit easier.

Xilinx Vivado zynq7000提高笔记

1. Modelsim仿真1.添加modelsim路径:Tool >options>2. 安装编译仿真库使用modelSIm需要xilinx library被编译。

运行1:report_property [current_project]运行2:Tcl Commandcompile_simlib -helpcompile_simlib -simulator modelsim 或compile_simlib -simulator modelsim -arch all -language all或运行3:安装modelsim库到指定目录compile_simlib -directory D:/modeltech64_10.1c/Xilinx_lib -simulator modelsim3. Modelsim中添加xilinx安装的modelsim库目录:在编译完成库后,生成了一个modelsim.ini文件。

用记事本打开复制其安(需装目录信息到modelsim安装目录中modelsim自己的modelsim.ini文件中。

要去掉modesim.ini的只读特性)重启modelsim,库自动添加到软件中。

4.测试:modelsim10.1c se行为层:通过综合层:时序仿真,测试通过功能仿真,测试通过应用层:时序仿真,测试通过功能仿真,测试通过使用vivado 仿真工具更方便快捷5.Modelsim工程中添加仿真库的命令vopt zynq.tb_simulator_all +acc -o zz1 -L simprims_ver -L unisims_ver -L xilinxcorelib_ver glbl 仿真预编译为库名zynq.tb_simulator_all(后缀tb_simulator_all为仿真testbench文件),添加simprims_ver、unisims_ver、xilinxcorelib_ver、glbl库即可。

ZYNQ:使用SDK打包BOOT.BIN、烧录BOOT.BIN到QSPI-FLASH

ZYNQ:使⽤SDK打包BOOT.BIN、烧录BOOT.BIN到QSPI-FLASH 打包程序为BOOT.BIN注意,做好备份是⼀个好习惯。

VivadoVivado 添加QSPI Flash的IP,重新编译;Launch SDK(推荐⽅法);或者⽤SDK指定⼀个workspace,根据hdf建⽴BSP。

SDK新建fsbl-1这个fsbl⽤于启动程序。

File - New - Application ProjectProject name : fsbl其他默认,注意不要选错BSP平台。

Next,选择Zynq FSBL添加代码(可选)Project Explorer展开 fsbl - src,打开 fsbl_debug.h,添加调试宏#define FSBL_DEBUG_INFO创建 boot ⽂件1. 选择 fsb ⼯程,右键选择 Create Boot Image2. 弹出的窗⼝中可以看到⽣成的BIF ⽂件路径,BIF ⽂件是⽣成BOO丁⽂件的配置⽂件,还有⽣成的BOOT.bin⽂件路径,BOOT.bin⽂件是我们需要的启动⽂件,可以放到SD卡启动,也可以烧写到QSPI FLASH.3. 在Boot image partitions 列表中是要合成的⽂件,第⼀个⽂件⼀定是bootloader⽂件,就是上⾯⽣成的fsbl.elf⽂件第⼆个⽂件是FPGA配置⽂件,点击Add添加我们的测试程序烧录BOOT.BIN到QSPI-FLASH说明Xilinx VIVADO 软件版本更新到2017以后,为了对ZYNQ和MPSOC平台进⾏统⼀,对 QSPI FLASH 下载⽅式进⾏了改动,因此,下载需要额外做⼀点⼩⼯作,⼤致步骤如下:有关步骤说明可以参考:0、Vivado配置QSPI-FLASH的IP(略)1、制作BOOT.BIN(略)2、新增⼀个FSBL⼯程(这⾥名为“fsbl-for-download”),并做如下改动:注意:为了下载QSPI FLASH 的“指定的fsbl”与⽣成boot.bin⽂件的fsbl⽂件不同,这⾥不能混淆。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FSBL代码导读

一、main函数执行之前

FSBL模板的代码是跟ISE的版本有关的,我用的是14.3,内容会比14.2版更多一点,但是基本过程是一样的。

板子上电之后,最先执行的并不是FSBL中的main函数,因为这个时候板子还没有初始化,不具备执行C语言的能力,此时只能执行汇编代码,所执行的代码是由BSP提供的。

我们打开zynq_fsbl_bsp——>ps7_cortexa9_0——>libsrc—

—>standalone_v3_07_a——>src文件夹,里面有一个asm_vector.S文件,这个文件

声明了一个代码段,位于地址0处。

开机之后,PS自动执行地址0处的指令,其第一句话就是一个跳转:B _boot。

如下:

于是就跳转到boot.S中执行_boot标号下的代码了,_boot会对系统做初始化,当它执行完后,PS将具备执行C代码的能力,接着在_boot的代码中,再次执行了一个跳转:

_start标号位于xil.crt0.S中,仍然对系统进行设置,我们看到,第一句话就是跳转到_cpu_init去执行cpu初始化。

代码部分截图如下:

在_start的末尾,BSP终于完成了自己的工作,PS将跳转到main函数开始执行。

如下:

二、main函数执行过程

终于系统进入了FSBL阶段。

我们打开zynq_fsbl——>src文件夹,然后打开main函数:

Main函数首先是一些宏定义,接下来就是执行ps7_int()函数。

SDK是一个很智能的工具,图中的灰色阴影部分是SDK判断出了PEEP_CODE这个宏没有定义,所以用灰颜色提示读者这段代码不用执行。

ps7_init函数位于ps7_init.c文件中。

这个C文件是由XPS根据用户的配置自动生成的。

我们进入ps7_init函数看一下,这个函数很短:

根据代码,很明显可以猜到,ps7_init函数其实执行了mio,pll,clock,ddr和某些外设的初始化。

我们接着看FSBL的main函数,根据XPS自动生成的ps7_init.c执行完初始化之后,FSBL将根据启动状态寄存器判断是采用的哪种启动模式。

有四种启动模式,分别是QSPI,NOR,JTAG,SD卡等模式。

每种模式都有一段独立的代码,举个例子,我们看SD卡模式的执行代码:

可以看到,系统先对SD卡初始化,并且要求SD卡中必须要有BOOT.BIN文件。

如果没有,那么从SD卡启动板子就会失败。

这也是为什么我们生成启动镜像必须命名为BOOT.BIN的原因。

需要注意的是NAND启动模式被禁用了,因为FSBL中有一个宏没有定义,所以处于灰色状态。

接下来的代码我们只看一下注释就大概知道干什么了:

在明确了启动模式之后,PS将在相应的flash中去寻找.bit文件和用户程序,通过遍历一些partition(最多15个),如果找到了.bit文件,那么就不重启,直接配置PL,然后再找用户程序。

如果没找到.bit就软件复位一下,然后调整地址,接着验证下一个partition。

充分体现这个过程的,是这个函数:

PartitionMove函数很复杂,我们只看注释:

这个注释说的就是找到了.bit文件就配置PL,找到了用户程序就加载到内存。

这个函数执行完之后,返回值就是用户程序的执行地址。

这个执行地址位于用户文件的文件头中,是由编译器或者ISE自己生成的。

找到了用户程序的执行地址,那么FSBL函数就该交接了,完成这个过程的是

FsblHandoff函数:

这个函数完成交接,并且一去不复返,再也不会返回,从此PS就开始执行了用户代码。

那么交接究竟是怎么完成的?其实我们直观上很容易猜到肯定是一个跳转指令。

带着猜测,

我们深入FsblHandoff函数,最后果然找到了:

其中bx lr指令就是跳转到用户代码执行。

三、拓展FSBL

事实上,在找到用户程序的执行地址后,FSBL并没有马上执行跳转,而是执行了这个函数:

这是一个钩子函数,它只有函数定义,但是没有任何内容,是个空函数。

是FSBL提供给用户自己扩展的,你可以在这个函数中填写任何可执行内容。

该函数会在交接到用户程序之前执行。

类似的函数还有FsblHookAfterHandoff( )。

这样在交接到用户代码之后也有钩子函数,同样,在FSBL找到.bit文件配置PL前后,也有两个钩子函数。

这几个钩子函数貌似只有14.3版本里面有,14.2里面没有。

四、FSBL的限制

FSBL有两个限制,这是写用户程序的时候需要知道的:

1,FSBL没有重新映射内存,所以内存的基地址是1M,用户代码只能在1M以上的地址中执行。

根据我的理解,只要修改FSBL,定义ECC_ENABLE,让如下代码从被禁止状态恢复成可执行状态就可以破解这个限制:

原因在于,很多系统代码都是这样的,将1M以下的地址空间作为函数出错的返回地址。

FSBL中很明显预留了这1M空间,但是没有使用。

14.2中没有这段代码。

2,FSBL在跳转到用户代码之前,禁止了指令缓存和MMU。

这个限制有很明显的代码根据:

修改这里的代码,应该就可以使能ICache和MMU。