设计一个比较电路,当输入的8421BCD码大于5时输出为1,否则输出为0教学总结

大学课程《数字电子技术基础》试题及答案(三)

大学课程《数字电子技术基础》试题及答案一、填空题组合逻辑电路1. 数字电路按逻辑功能的不同特点可分为两大类,即: 逻辑电路和 逻辑电路 。

答:组合 、时序2. 从一组输入数据中选出一个作为数据传输的常用组合逻辑电路叫做 。

答:数据选择器3.用于比较两个数字大小的逻辑电路叫做 。

答:数值比较器4. 驱动共阳极七段数码管的译码器的输出电平为 有效,而驱动共阴极的输出电平为 有效。

答:低、高5.一个8选1的多路选择器(数据选择器),应具有 个地址输入端。

答:3个6.编码器的逻辑功能是把输入的高低电平编成一个 ,目前经常使用的编码器有普通编码器和优先编码器两类。

答:二值代码7.译码器的逻辑功能是把输入的二进制代码译成对应的 信号,常用的译码器有二进制译码器,二-十进制译码器和显示译码器三类。

答:输出高、低电平8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( )。

答:10111111二、选择题组合逻辑电路1.74LS138是3线-8线译码器,译码输出为低电平有效,若输入A 2A 1A 0=100时,输出= 。

A 、00010000,B 、11101111C 、11110111D 、10000000答:B2.在下列逻辑电路中,不是组合逻辑电路的是( )。

A 、译码器B 、编码器C 、全加器D 、寄存器 答:D3.在下列逻辑电路中,不是组合逻辑电路的是( )。

A. 译码器B. 编码器C. 全加器D.寄存器 答:D4. 八选一数据选择器组成电路如下图所示,该电路实现的逻辑函数是Y= 。

A. ABC ABC ABC ABC +++ B. ABC ABC + C. BC ABC +D. ABC ABC ABC ABC +++ 答:D5.七段显示译码器是指 的电路。

A. 将二进制代码转换成0~9数字B. 将BCD 码转换成七段显示字形信号C. 将0~9数字转换成BCD 码D. 将七段显示字形信号转换成BCD 码 答:B6.组合逻辑电路通常由 组合而成。

数字电子技术基础-康华光第五版答案

第一章数字逻辑习题1.1 数字电路与数字信号1.1.2 图形代表的二进制数0101101001.1.4 一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2 数制1.2.2 将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于2−4(2)127 (4)解:(2)(127)D= 27 -1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)()D=(10.1011)B=(2.54)O=(2.B)H1.4 二进制代码1.4.1 将下列十进制数转换为8421BCD 码:(1)43 (3)254.25 解:(43)D=(01000011)BCD1.4.3 试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you 的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43 的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331.6 逻辑函数及其表示方法1.6.1 在图题1. 6.1 中,已知输入信号A,B`的波形,画出各门电路输出L 的波形。

解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答2.1.1 用真值表证明下列恒等式(3)A⊕ =B AB AB+ (A⊕B)=AB+AB解:真值表如下由最右边2栏可知,A⊕B与AB+AB的真值表完全相同。

数字电路第三章习题答案

数字电路第三章习题答案

3-10

F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B F F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B

数字电路第三章习题答案

3-11

试用六个与非门设计一个水箱控制电路。图为水箱示意图。A、B、C是三个电极。 当 电极被水浸没时,会有信号输出。水面在A,B间为正常状态,点亮绿灯G;水面在B、 C间或在A以上为异常状态,点亮黄灯Y;水面在C以下为危险状态.点亮红灯R。

3531736半加器的设计1半加器真值表2输出函数3逻辑图输入输出被加数a加数b4逻辑符号31837ab改为用与非门实现函数表达式变换形式

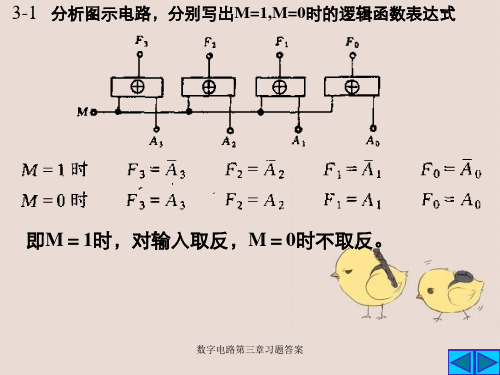

3-1 分析图示电路,分别写出M=1,M=0时的逻辑函数表达式

即M=1时,对输入取反,M=0时不取反。

数字电路第三章习题答案

3-2 分析图示补码电路,要求写出逻辑函数表达式,列出真值表。

3-10 试用与非门设计一个逻辑选择电路。

S1、S0为选择端,A、B为数据输入端。 选择电路的功能见下表。选择电路可 以有反变量输入。

数字电路第三章习题答案

3-10

F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B F F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B FS 1 S 0A B S 1 S 0(A B )S 1 S 0(A BA)B

数字电路第三章习题答案

3-5

Ai 0 0 0 0 1 1 1 1

Si Ai BiCi Ai BiCi Ai BiCi Ai BiCi

习题2

实现1位全减器的VHDL程序f_suber.vhd底层设计描述。

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY f_suber IS PORT (x,y,sub_in : IN STD_LOGIC; sub_out,diffr: OUT STD_LOGIC); END ENTITY f_suber; ARCHITECTURE fhd1 OF f_suber IS COMPONENT h_suber IS PORT (x,y:IN STD_LOGIC; s_out,diff:OUT STD_LOGIC); u1 u2 d END COMPONENT h_suber; x x diff x diff h_suber h_suder f COMPONENT or IS s_out e y y y s_out PORT (a,b:IN STD_LOGIC; u3 sub_in c: OUT STD_LOGIC); END COMPONENT OR; SIGNAL d,e,f: STD_LOGIC; BEGIN u1:h_suber PORT MAP (x=>x,y=>y,diff=>d,s_out=>e); u2:h_suber PORT MAP (x=>d,y=>sub_in,diff=>diffr,s_out=>f); u3:or PORT MAP (a=>f,b=>e,c=>sub_out); END ARCHITECTURE fhd1;

LIBRARY IEEE; IF_THEN语句 USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux41 IS PORT (A,B,C,D : IN STD_LOGIC; S0,S1,S2,S3 : IN STD_LOGIC; Y :OUT STD_LOGIC); END ENTITY mux41; ARCHITECTURE one OF mux41 IS SIGNAL S : STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN S<=S0&S1&S2&S3; process(S) BEGIN IF S=“0111” THEN Y<=A; ELSIF S=“1011”THEN Y<=B; ELSIF S=“1101”THEN Y<=C; ELSIF S=“1110”THEN Y<=D; ELSE Y<=NULL; END IF; END PROCESS; END ARCHITECTURE one;

电子技术基础数字部分第五版康光华主编第1~6章章节详细习题答案

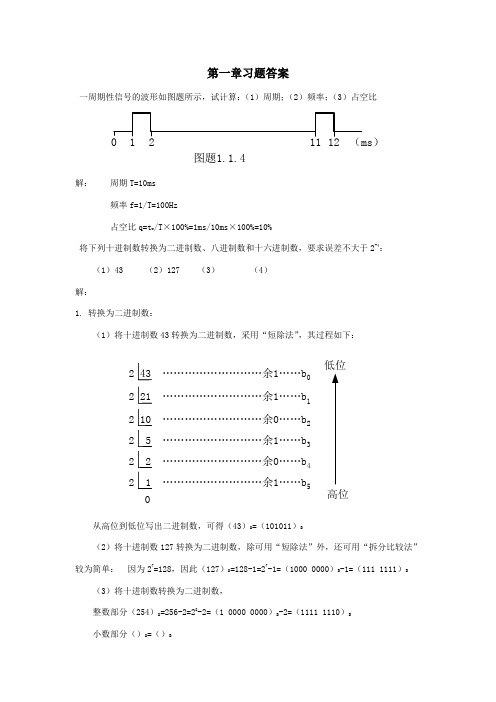

第一章习题答案一周期性信号的波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比0121112(ms)图题1.1.4解: 周期T=10ms 频率f=1/T=100Hz占空比q=t w /T ×100%=1ms/10ms ×100%=10%将下列十进制数转换为二进制数、八进制数和十六进制数,要求误差不大于2-4:(1)43(2)127(3)(4)解:1. 转换为二进制数:(1)将十进制数43转换为二进制数,采用“短除法”,其过程如下:2 43 ………………………余1……b 02 21 ………………………余1……b 12 1 ………………………余1……b 52 2 ………………………余0……b 42 5 ………………………余1……b 32 10 ………………………余0……b 2高位低位从高位到低位写出二进制数,可得(43)D =(101011)B(2)将十进制数127转换为二进制数,除可用“短除法”外,还可用“拆分比较法”较为简单: 因为27=128,因此(127)D =128-1=27-1=(1000 0000)B -1=(111 1111)B(3)将十进制数转换为二进制数,整数部分(254)D =256-2=28-2=(1 0000 0000)B -2=(1111 1110)B 小数部分()D =()B()D=(1111 )B(4)将十进制数转换为二进制数整数部分(2)D=(10)B小数部分()D=()B演算过程如下:0.718×2=1.436……1……b-1 0.436×2=0.872……0……b-2 0.872×2=1.744……1……b-3 0.744×2=1.488……1……b-4 0.488×2=0.976……0……b-5 0.976×2=1.952……1……b-6高位低位要求转换误差小于2-4,只要保留小数点后4位即可,这里算到6位是为了方便转换为8进制数。

EDA技术与Verilog_HDL(潘松)第6章习题答案

6-1 在Verilog设计中,给时序电路清零(复位)有两种不同方法,它们是什么,如何实现?答:同步清零、异步清零,在过程语句敏感信号表中的逻辑表述posedge CLK用于指明正向跳变,或negedge用于指明负向跳变实现6-2 哪一种复位方法必须将复位信号放在敏感信号表中?给出这两种电路的Verilog 描述。

答:异步复位必须将复位信号放在敏感信号表中。

同步清零:always @(posedge CLK) //CLK上升沿启动Q<=D; //当CLK有升沿时D被锁入Q异步清零:always @(posedge CLK or negedge RST) begin //块开始if(!RST)Q<=0; //如果RST=0条件成立,Q被清0else if(EN) Q<=D;//在CLK上升沿处,EN=1,则执行赋值语句end//块结束6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

module Statistics8(sum,A); output[3:0]sum;input[7:0] A;reg[3:0] sum;integer i;always @(A)beginsum=0;for(i=0;i<=8;i=i+1) //for 语句if(A[i]) sum=sum+1;else sum=sum;endendmodule module Statistics8(sum,A); parameter S=4;output[3:0]sum;input[7:0] A;reg[3:0] sum;reg[2*S:1]TA;integer i;always @(A)beginTA=A; sum=0;repeat(2*S)beginif(TA[1])sum=sum+1;TA=TA>>1;endendendmodulerepeat循环语句for循环语句module Statistics8(sum,A);parameter S=8;output[3:0]sum;input[7:0] A;reg[S:1] AT;reg[3:0] sum;reg[S:0] CT;always @(A) beginAT={{S{1'b0}},A}; sum=0; CT=S;while(CT>0) beginif(AT[1])sum=sum+1;else sum=sum;begin CT= CT-1; AT=AT>>1; end end endendmodule6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

eda作业讲解

eda作业讲解作业讲解2-2 什么是基于乘积项的可编程逻辑结构?什么是基于查找表的可编程逻辑结构?答:GAL、CPLD 之类都是基于乘积项的可编程结构;即包含有可编程与阵列和固定的或阵列的PAL(可编程阵列逻辑)器件构成。

FPGA(现场可编程门阵列)是基于查找表的可编程逻辑结构。

2-4 与传统的测试技术相⽐,边界扫描技术有何特点?答:使⽤BST(边界扫描测试)规范测试,不必使⽤物理探针,可在器件正常⼯作时在系统捕获测量的功能数据。

克服传统的外探针测试法和“针床”夹具测试法来⽆法对IC 内部节点⽆法测试的难题。

2-5 解释编程与配置这两个概念。

答:编程—基于电可擦除存储单元的EEPROM 或Flash 技术。

CPLD ⼀股使⽤此技术进⾏编程。

CPLD 被编程后改变了电可擦除存储单元中的信息,掉电后可保存。

电可擦除编程⼯艺的优点是编程后信息不会因掉电⽽丢失,但编程次数有限,编程的速度不快。

配置—基于SRAM 查找表的编程单元。

编程信息是保存在SRAM 中的,SRAM 在掉电后编程信息⽴即丢失,在下次上电后,还需要重新载⼊编程信息。

⼤部分FPGA 采⽤该种编程⼯艺。

该类器件的编程⼀般称为配置。

对于SRAM型FPGA 来说,配置次数⽆限,且速度快;在加电时可随时更改逻辑;下载信息的保密性也不如电可擦除的编程。

3-2 图3-16所⽰的是4选1多路选择器,试分别⽤IF_THEN 语句和CASE语句的表达⽅式写出此电路的VHDL程序,选择控制信号s1和s0的数据类型为STD_LOGIC_VECTOR;当s1=’0’,s0=’0’;s1=’0’,s0=’1’;s1=’1’,s0=’0’和s1=’1’,s0=’1’时,分别执⾏y<=a、y<=b、y<=c、y<=d。

解1:⽤IF_THEN语句实现4选1多路选择器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux41 ISPORT (a,b,c,d: IN STD_LOGIC;s0: IN STD_LOGIC;s1: IN STD_LOGIC;y: OUT STD_LOGIC);END ENTITY mux41;ARCHITECTURE if_mux41 OF mux41 ISSIGNAL s0s1 : STD_LOGIC_VECTOR(1 DOWNTO 0);--定义标准逻辑位⽮量数据BEGINs0s1<=s1&s0 --s1相并s0,即s1与s0并置操作PROCESS(s0s1,a,b,c,d)BEGINIF s0s1 = "00" THEN y <= a;ELSIF s0s1 = "01" THEN y <= b;ELSIF s0s1 = "10" THEN y <= c;ELSE y <= d;END IF;END PROCESS;END ARCHITECTURE if_mux41;解2:⽤WHEN_ELSE语句实现4选1多路选择器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux41 ISPORT (a,b,c,d: IN STD_LOGIC;s0: IN STD_LOGIC;s1: IN STD_LOGIC;y: OUT STD_LOGIC);END ENTITY mux41;ARCHITECTURE case_mux41 OF mux41 ISSIGNAL s0s1 : STD_LOGIC_VECTOR(1 DOWNTO 0);--定义标准逻辑位⽮量数据类型BEGINs0s1<=s1&s0 --s1相并s0,即s1与s0并置操作y<=a when s0s1=”00” elseb when s0s1=”01” elsec when s0s1=”10” elsed ;End;解3:⽤CASE语句实现4选1多路选择器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux41 ISPORT (a,b,c,d: IN STD_LOGIC;s0: IN STD_LOGIC;s1: IN STD_LOGIC;y: OUT STD_LOGIC);END ENTITY mux41;ARCHITECTURE case_mux41 OF mux41 ISSIGNAL s0s1 : STD_LOGIC_VECTOR(1 DOWNTO 0);BEGINs0s1<=s1&s0PROCESS(s0s1,a,b,c,d)BEGINCASE s0s1 IS --类似于真值表的case语句WHEN "00" => y <= a;WHEN "01" => y <= b;WHEN "10" => y <= c;WHEN "11" => y <= d;WHEN OTHERS =>NULL ;END CASE;END PROCESS;END ARCHITECTURE case_mux41;3-6 图3-18是⼀个含有上升沿触发的D触发器的时序电路(sxdl),试写出此电路的VHDL设计⽂件。

(完整word版)《电子技术基础》第五版课后答案

第一章数字逻辑习题1.1数字电路与数字信号1。

1.2 图形代表的二进制数0101101001.1.4一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms频率为周期的倒数,f=1/T=1/0。

01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1。

2数制21.2。

2将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于4(2)127 (4)2.718解:(2)(127)D=72-1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2。

718)D=(10。

1011)B=(2。

54)O=(2.B)H1。

4二进制代码1.4.1将下列十进制数转换为8421BCD码:(1)43 (3)254.25解:(43)D=(01000011)BCD1。

4。

3试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@(3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+"的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331。

6逻辑函数及其表示方法1。

6.1在图题1。

6。

1中,已知输入信号A,B`的波形,画出各门电路输出L的波形.解: (a)为与非, (b)为同或非,即异或第二章 逻辑代数 习题解答2.1.1 用真值表证明下列恒等式 (3)A B AB AB ⊕=+(A ⊕B )=AB+AB A B A B ⊕AB AB A B ⊕ AB +AB 0 0 0 1 0 1 1 0 1 1 0 0 0 0 1 0 1 0 0 0 0 11111由最右边2栏可知,A B ⊕与AB +AB 的真值表完全相同。

电子技术与实践选复习题

说明:综合考试包括理论笔试和实验操作两个部分,考核范围是课堂各单元对应的理论和实验操作内容,特别是上课例题、作业本、做在书上的习题以及实验报告内容,另以下习题供大家复习练习。

一、填空题1、杂质半导体有型和型之分。

2、PN结加正向电压,是指电源的正极接区,电源的负极接区,这种接法叫。

3、二极管的两端加正向电压时,有一段“死区电压”,锗管约为,硅管约为。

4、二极管的类型按材料分和。

5、单相半波整流电路中,利用二极管的特性,可以将正弦交流变成单方向脉动的直流电。

6、硅稳压二极管主要工作在。

7、硅二极管导通电压为________伏,锗管为_________伏。

8、测量三级三极管放大电路,得其第一级电路放大倍数为-30,第二级电路放大倍数为30,第三级电路放大倍数为0.99,输出电阻为60 ,则可判断三级电路的组态分别是、、。

9、放大电路在工作时若进入输出特性曲线的和,就会造成非线性失真,静态工作点过高,易造成失真;静态工作点过低,易造成失真。

10、在放大电路中引入负反馈,虽然使放大电路的放大倍数,但能提高放大倍数的,非线性失真。

11、测得某放大电路中三极管三个极电位分别为:U1=3.5V、U2=2.8V、U3=15V。

判断该管材料是;管型是;1、2、3三个极分别对应为极、极极。

12、在三种三极管基本放大电路中共集电极放大电路的特点:电压放大倍数,又称。

而输入电阻,输出电阻。

(填大、小)13、多级放大电路的耦合方式有、、。

总的电压放大倍数是各级电压放大倍数之。

14、三种三极管基本放大电路中,电路的输出与输入反相位;电路的输入电阻最大。

15、三极管正常的工作状态有: 状态、 状态和 状态。

16、PN 结具有( )。

当它加( )电压时,导通;加( )电压时,截止。

17、二极管的伏安特性可分三段:( )、( )、( )。

稳压管工作在( )。

硅二极管导通电压大约( )V 。

18、在放大电路中引入负反馈,虽然使放大电路的放大倍数 ,但能 放大倍数的稳定性, 非线性失真,拓展 ;当引入的是 反馈时,能使放大电路的输出电压稳定且使输出电阻 。

第6章 Verilog HDL设计进阶习题

1CLK7476N 1K ~1Q ~1CLR 14

U3A 7400N

3

V1 100 Hz 5V J1

10 9 2 7 6 5 4 3

74194N

9 QD QC QB QA 12 13 14 15 11 13 14 15 16 17 18 19 20 21 22 23 1 2 3 4 5 6 7 8 G D C B A

//Verilog设计一个4位4输入最大数值检测电路 module Maximum_value_detection(Mostlarge,a,b,c,d);//4位 4输入最大数值检测电路 output [3:0] Mostlarge; input [3:0] a,b,c,d; wire[3:0]sum1,sum2,sum3;

习

CP 1 2 3 4 5 6 QD(A2) QC(D4、~D5) 0 0 0 1 1 1 1 1 1 0 ~0 0 QB(A1) 0 1 1 0 0 1

题

QA(A0、D7) 1 0 1 0 1 0 D D1 D2 D3 D4 D5 D6 F 0 1 0 0 1 0

7

8 9 10 11

1

1 1 1 1

U1

74150N

Key = Space

XSC1

Ext Trig + _ A + _ + B _

U5A 7404N

E15 E14 E13 E12 E11 E10 E9 E8 E7 E6 E5 E4 E3 E2 E1 E0

0

1 ~1 1 1

1

0 0 1 1

1

0 1 0 1

D7

D4 D5 D6 D7

1

1 0 0 1

VDD 5V U2 U1A 74S04D

武汉理工大学数字电子技术-4套期末试卷4套(含答案)

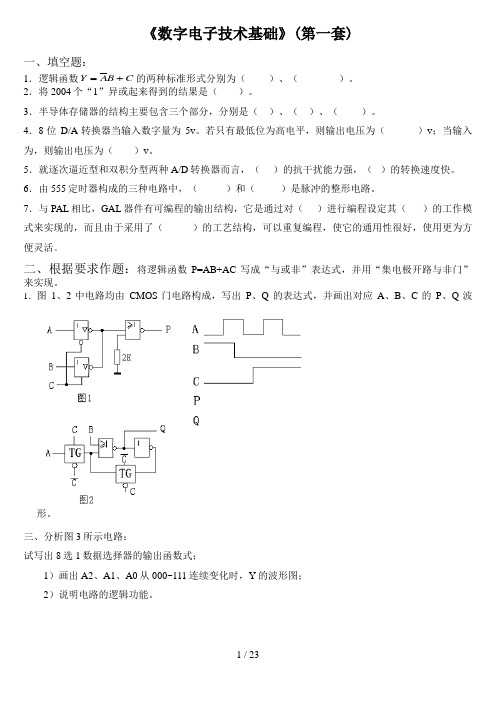

《数字电子技术基础》(第一套)一、填空题:=+的两种标准形式分别为()、()。

1.逻辑函数Y AB C2.将2004个“1”异或起来得到的结果是()。

3.半导体存储器的结构主要包含三个部分,分别是()、()、()。

4.8位D/A转换器当输入数字量为5v。

若只有最低位为高电平,则输出电压为()v;当输入为,则输出电压为()v。

5.就逐次逼近型和双积分型两种A/D转换器而言,()的抗干扰能力强,()的转换速度快。

6.由555定时器构成的三种电路中,()和()是脉冲的整形电路。

7.与PAL相比,GAL器件有可编程的输出结构,它是通过对()进行编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

二、根据要求作题:将逻辑函数P=AB+AC写成“与或非”表达式,并用“集电极开路与非门”来实现。

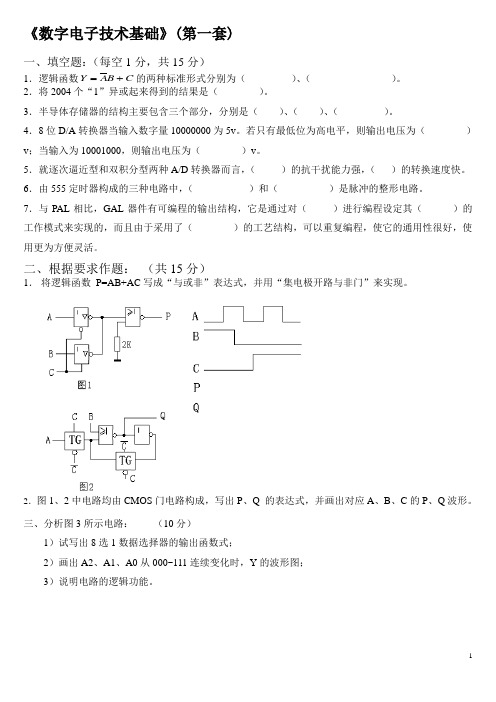

1.图1、2中电路均由CMOS门电路构成,写出P、Q 的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路:试写出8选1数据选择器的输出函数式;1)画出A2、A1、A0从000~111连续变化时,Y的波形图;2)说明电路的逻辑功能。

四、设计“一位十进制数”的四舍五入电路(采用8421BCD码)。

要求只设定一个输出,并画出用最少“与非门”实现的逻辑电路图。

五、已知电路及CP、A的波形如图4(a) (b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。

BC六、用T触发器和异或门构成的某种电路如图5(a)所示,在示波器上观察到波形如图5(b)所示。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。

七、图6所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

ROM中的数据见表1所示。

试画出在CP信号连续作用下的D3、D2、D1、D0输出的电压波形,并说明它们和CP 信号频率之比。

表1:地址输入数据输出A3 A2 A1 A0 D3 D2 D1 D00 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 11 1 1 10 0 0 00 0 1 10 1 0 00 1 0 11 0 1 01 0 0 11 0 0 01 1 1 11 1 0 00 0 0 10 0 1 00 0 0 10 1 0 00 1 1 10 0 0 0CP波形如图所示:八、综合分析图7所示电路,RAM的16个地址单元中的数据在表中列出。

数字电子技术基础自制题库

数字电子技术基础试卷试题1一、单项选择题(每小题1分,共15分)1.一位十六进制数可以用多少位二进制数来表示?( C )A. 1B. 2C. 4D. 16 2.以下电路中常用于总线应用的是( A )A.T S L 门B.O C 门C. 漏极开路门D.C M O S 与非门 3.以下表达式中符合逻辑运算法则的是( D )A.C ·C =C 2B.1+1=10C.0<1D.A +1=1 4.T 触发器的功能是( D )A . 翻转、置“0” B. 保持、置“1” C. 置“1”、置“0” D. 翻转、保持 5. 存储8位二进制信息要多少个触发器(D )A.2B.3C.4D.8 6.多谐振荡器可产生的波形是( B )A.正弦波B.矩形脉冲C.三角波D.锯齿波 7.一个16选一的数据选择器,其地址输入(选择控制输入)端的个 数是( C )A.1B.2C.4D.16 8.引起组合逻辑电路中竟争与冒险的原因是( C )A.逻辑关系错;B.干扰信号;C.电路延时;D.电源不稳定。

9.同步计数器和异步计数器比较,同步计数器的最显著优点是( A ) A.工作速度高 B.触发器利用率高C.电路简单D.不受时钟C P 控制10.N 个触发器可以构成能寄存多少位二进制数码的寄存器?( B ) A.N -1 B.N C.N +1 D.2N11.若用J K 触发器来实现特性方程AB Q A Q n 1n +=+,则J K 端的方程应为( B )A.J =A B ,K =B AB.J =A B ,K =B AC.J =B A +,K =A BD.J =B A ,K =A B12.一个无符号10位数字输入的D A C ,其输出电平的级数是( C )A.4B.10C.1024D.10013.要构成容量为4K ×8的RAM ,需要多少片容量为256×4的RAM ?( D )A.2B.4C.8D.3214.随机存取存储器R A M 中的内容,当电源断掉后又接通,则存储器中的内容将如何变换?( C )A.全部改变B.全部为1C.不确定D.保持不变 15.用555定时器构成单稳态触发器,其输出的脉宽为( B )A.0.7RC ;B.1.1RC ;C.1.4RC ;D.1.8RC ; 二、多项选择题(每小题1分,共5分)16.以下代码中,为无权码的是( C )( D )A. 8421BCD 码B. 5421BCD 码C. 余三码D. 格雷码 17.当三态门输出高阻状态时,以下说法正确的是( A )( B )A.用电压表测量指针不动B.相当于悬空C.电压不高不低D.测量电阻指针不动18.已知F=A B +BD+CDE+A D ,下列结果正确的是哪几个?( A )( C )A.F =D B A +B.F =D B A )(+C.F =))((D B D A ++D.F =))((D B D A ++19.欲使J K 触发器按Q n +1=Q n 工作,可使J K 触发器的输入端为以下哪几种情况?( A )( B )( D )A.J =K =0B.J =Q ,K =QC.J =Q ,K =QD.J =Q ,K =0 20.关于PROM 和PAL 的结构,以下叙述正确的是( A )( D )A.P R O M 的与阵列固定,不可编程B.P R O M 与阵列、或阵列均不可编程C.P A L 与阵列、或阵列均可编程D.P A L 的与阵列可编程 三、判断改错题(每小题2分,共10分)21. 数字电路中用“1”和“0”分别表示两种状态,二者无大小之分。

用八选一数据选择器 74LS151 设计一个 8421BCD 非法码检测电路

八选一数据选择器74LS151 设计一个8421BCD 非法码检测电路用八选一数据选择器 74LS151 设计一个 8421BCD 非法码检测电路,当输入为非法码组时,输出为 1,否则为零。

二进制数与B C D码的对应关系如表10所示。

写出函数Y的逻辑表达式。

画出电路图并接线调试,观察是否与表10相符。

表10 输入与输出关系由所给出二进制数与BCD码的对应关系可以列出输出Y的真值表,通过卡诺图化简得到了输出逻辑函数Y的最简表达式:Y=A3(A2A1Ao+A2A1Ao'+A2A1'Ao+A2'A1Ao+A2A1 'Ao'+A2'A1Ao)+A2'A1Ao*0+A2'A'Ao'*0所以可以用8选1数据选择器实现得D0=D1=G'=0,D2=D3=D4=Ds=D6=D,=D,A=A,B=B,C=C由此式可以画出逻辑图13如下所示:图13 8421BCD 非法码检测电路逻辑图根据图13所示所示的逻辑图,在Multisim环境下搭接电路图如图14所示,在图14所示的电路中,指示灯X1,X2,X3和X4用于指示输入的逻辑电平指示灯,X5用于指示输出的逻辑电平。

图14 8421BCD 非法码检测电路仿真图在图14所示的电路中,指示灯灭表示低电平,指示灯亮表示高电平。

当A,B,C,D 输入不同的电平时,其仿真结果如图15所示。

图15所对应的输入输出结果如表11所示。

表 11 8421BCD 非法码检测电路真值表图 15 8421BCD 非法码检测电路仿真结果由图15和表11的测试结果可知,8421BCD 非法码检测电路的测量结果与表10的真值表完全一致,说明图13所示的逻辑图完全正确。

EDA实验报告含结果图

EDA电子课程实验报告专业:班级:姓名:学号:实验一四人表决器一实验目的1、熟悉Quartus II软件的使用。

2、熟悉EDA-IV实验箱。

3、熟悉EDA开发的基本流程。

二硬件需求1、RC-EDA-IV型实验箱一台;2、RC-EDA-IV型实验箱配套USB-Blaster下载器一个;3、PC机一台。

三实验原理所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

四人表决器顾名思义就是由四个人来投票,当同意的票数大于或者等于3人时,则认为同意;反之,当否决的票数大于或者等于2人时,则认为不同意。

实验中用4个拨挡开关来表示4个人,当对应的拨挡开关输入为‘1’时,表示此人同意;否则若拨挡开关输入为‘0’时,则表示此人反对。

表决的结果用一个LED表示,若表决的结果为同意,则LED被点亮;否则,如果表决的结果为反对,则LED不会被点亮。

四实验内容VHDL程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;--------------------------------------------------------------------entity EXP3 isport(k1,K2,K3,K4 : in std_logic;ledag : out std_logic_vector(3 downto 0);m_Result : out std_logic);end EXP3;--------------------------------------------------------------------architecture behave of EXP3 issignal K_Num : std_logic_vector(2 downto 0); signal K1_Num,K2_Num: std_logic_vector(2 downto 0); signal K3_Num,K4_Num: std_logic_vector(2 downto 0);beginprocess(K1,K2,K3,K4)beginK1_Num<='0'&'0'&K1;K2_Num<='0'&'0'&K2;K3_Num<='0'&'0'&K3;K4_Num<='0'&'0'&K4;end process;process(K1_Num,K2_Num,K3_Num,K4_Num,)beginK_Num<=K1_Num+K2_Num+K3_Num+K4_Num;end process;process(K_Num) beginif(K_Num>2) thenm_Result<='1';elsem_Result<='0';end if;end process;end behave;实验电路实验二格雷码转换一实验目的1、了解格雷码变换的原理。

(完整word版)数字电子技术试题及答案(题库)

数字电子技术基础试题(一)一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

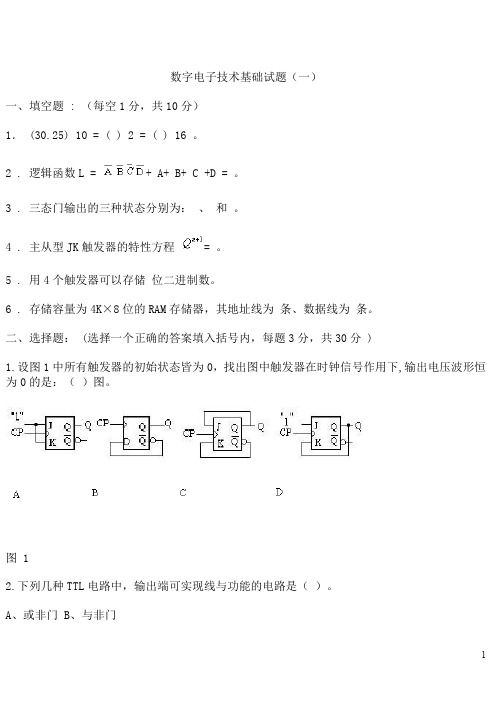

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

2014年PLD习题集(含参考答案)数字系统设计

第1章习题1.1 名词解释PROM CPLD FPGA ASICJTAG边界扫描FPGA/CPLD编程与配置逻辑综合PAL EDA GAL IP-CORE ISP ASIC RTL FPGA SOPC CPLDIP-CORE SOC和SOPC EDA/CAD1.2 现代EDA技术的特点有哪些?采用HDL描述、自顶向下、开放标准、具有完备设计库1.3 什么是Top-down设计方式?(P4)1.4 数字系统的实现方式有哪些?各有什么优缺点?74LS系列/4000系列常规逻辑门设计:设计难度大、调试复杂采用CPLD/FPGA等可编程器件来设计:用HDL描述、设计难度小、调试仿真方便,开发费用低,但单位成本较高,适合小批量应用专用集成电路设计:设计掩模成本高,适合大批量应用1.5什么是IP复用技术?IP核对EDA技术的应用和发展有什么意义?(P5)IP可重复使用的一种功能设计,可节省设计时间、缩短开发周期,避免重复劳动为大规模SOC设计提供开发基础、和开发平台。

1.6 用硬件描述语言设计数字电路有什么优势?优势:可进行行为级、RTL级、门级多层面对电路进行描述、可功能仿真时序分析,与工艺无关。

1.8 基于FPGA/CPLD的数字系统设计流程包括哪些步骤?(P8 图1.7)1.9 什么是综合?常用的综合工具有哪些?HDL→RTL→门级→网表的描述转换过程ALTERA:MAX-PLUSII,Quartus, Xilinx:ISE , Lattice: ispLERVER1.10 功能仿真与时序仿真有什么区别?功能仿真不考虑器件延时,而时序分析必须考虑在不同器件中的物理信号的延时1.11 数字逻辑设计描述分哪几个层级,各有什么特点。

1.12、为何任意组合逻辑电路可用通用的与阵列、或阵列组合来实现。

可表示为布尔代数方程,由乘积项的和表示1.13 FPGA与CPLD在实现方式或内部结构上的主要区别查表、与或阵列1.14 VerilogHDL与计算机程序设计语言主要区别(描述并行电路行为或结构、描述的串行指令流)1.15 简述“逻辑综合”功能作用。

数字电子技术_4套期末试卷_含答案综述

《数字电子技术基础》(第一套)一、填空题:(每空1分,共15分)1.逻辑函数Y AB C=+的两种标准形式分别为()、()。

2.将2004个“1”异或起来得到的结果是()。

3.半导体存储器的结构主要包含三个部分,分别是()、()、()。

4.8位D/A转换器当输入数字量10000000为5v。

若只有最低位为高电平,则输出电压为()v;当输入为10001000,则输出电压为()v。

5.就逐次逼近型和双积分型两种A/D转换器而言,()的抗干扰能力强,()的转换速度快。

6.由555定时器构成的三种电路中,()和()是脉冲的整形电路。

7.与PAL相比,GAL器件有可编程的输出结构,它是通过对()进行编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

二、根据要求作题:(共15分)1.将逻辑函数P=AB+AC写成“与或非”表达式,并用“集电极开路与非门”来实现。

2.图1、2中电路均由CMOS门电路构成,写出P、Q 的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路:(10分)1)试写出8选1数据选择器的输出函数式;2)画出A2、A1、A0从000~111连续变化时,Y的波形图;3)说明电路的逻辑功能。

四、设计“一位十进制数”的四舍五入电路(采用8421BCD码)。

要求只设定一个输出,并画出用最少“与非门”实现的逻辑电路图。

(15分)五、已知电路及CP、A的波形如图4(a) (b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。

(8分)BC六、用T触发器和异或门构成的某种电路如图5(a)所示,在示波器上观察到波形如图5(b)所示。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。

(6分)七、图6所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

ROM中的数据见表1所示。

试画出在CP信号连续作用下的D3、D2、D1、D0输出的电压波形,并说明它们和CP 信号频率之比。

数字电路分析与设计_浙江大学中国大学mooc课后章节答案期末考试题库2023年

数字电路分析与设计_浙江大学中国大学mooc课后章节答案期末考试题库2023年1.若对8个特定对象进行编制,应该选择位二进制编码器。

参考答案:32.使逻辑函数【图片】为1的最小项有个参考答案:7##%_YZPRLFH_%##七3.条件中不可能出现的组合称为任意项,条件中不允许出现的组合称为约束项,约束项和任意项统称为无关项。

参考答案:正确4.将逻辑函数L=AB+AC+BC用卡诺图表示为:【图片】参考答案:正确5.和逻辑式【图片】相等的是参考答案:B6.已知N的反码为10110011,则补码为01001101。

参考答案:错误7.十进制数(-10)10的二进制补码表示为:参考答案:(10110)28.判断对错:D/A转换器输出模拟量的大小只取决于输入的数字量。

参考答案:错误9.执行Quartus II的______命令,可以检查设计电路错误。

参考答案:Compiler10.CPLD和FPGA器件______。

参考答案:在系统加电时可以对器件的内容进行重构11.某中规模集成计数器74HCXX的功能表和简化逻辑符号如下所示。

【图片】用该集成计数器连接而成的电路如下图所示。

该电路是(同步/异步)、(加法/减法)计数器;其中74HCXX(I)片连接成进制计数器;整个电路是进制计数器。

(答案间用中文分号隔开)【图片】参考答案:异步;加法;10;4412.已知集成计数器74HC193的功能表和引脚图如下所示,若利用反馈置数法设计一个余3码编码的10进制加计数器,则需要在输出Q3Q2Q1Q0=()时使置数端【图片】置为(),并将数据输入端D3D2D1D0置为()。

(答案间用中文分号隔开)【图片】【图片】参考答案:1101;0;001113.下列A/D转换器速度最快的是()。

参考答案:并行比较型A/D转换器14.用4选一的数据选择器扩展成16选一的数据选择器,若不加其它门电路,则最少需要()片4选一数据选择器。

参考答案:515.用中规模集成计数器74LS192构成的电路如图所示,则该电路功能为进制法(加/减)计数器。

数字系统设计与VerilogHDL课后习题

数字系统设计与VerilogHDL课后习题习题11.1现代EDA技术的特点有哪些?1.2什么是T op-down设计方式?1.3数字系统的实现方式有哪些?各有什么优缺点?1.4什么是IP复用技术? IP核对EDA技术的应用和发展有什么意义?1.5用硬件描述语言设计数字电路的优势是什么?1.6结合自己的使用情况谈谈对EDA工具的认识。

1.7基于FPGA/CPLD的数字系统设计流程包括哪些步骤?1.8什么是综合?常用的综合工具有哪些?1.9功能仿真与时序仿真有什么区别?1.10 FPGA与ASIC在概念上有什么区别?习题22.1 PLA和PAL在结构上有什么区别?2.2说明GAL的OLMC有什么特点,它怎样实现可编程组合电路和时序电路?2.3简述基于乘积项的可编程逻辑器件的结构特点。

2.4基于查找表的可编程逻辑结构的原理是什么?2.5基于乘积项和基于查找表的结构各有什么优点?2.6 CPLD和FPGA在结构上有什么明显的区别?各有什么特点?2.7 FPGA器件中的存储器块有何作用?2.8 Altera的MAX II器件是属于CPLD还是FPGA,请查阅有关资料并进行分析。

2.9边界扫描技术有什么优点?2.10说说JTAG接口都有哪些功能。

2.11 FPGA/CPLD器件未来的发展趋势有哪些?习题44.1 用Verilog设计一个8位加法器,进行综合和仿真,查看综合和仿真结果。

4.2 用Verilog设计一个8位二进制加法计数器,带异步复位端口,进行综合和仿真,查看综合和仿真结果。

4.3用Verilog设计一个模60的BCD码计数器,进行综合和仿真,查看综合和仿真结果。

习题66.1阻塞赋值和非阻塞赋值有什么本质的区别?6.2用持续赋值语句描述一个4选1数据选择器。

6.3用行为语句设计一个8位计数器,每次在时钟的上升沿,计数器加1,当计数器溢出时,自动从零开始重新计数。

计数器有同步复位端。

6.4设计一个4位移位寄存器。