4or7进制计数器

数字电子技术考试题及答案

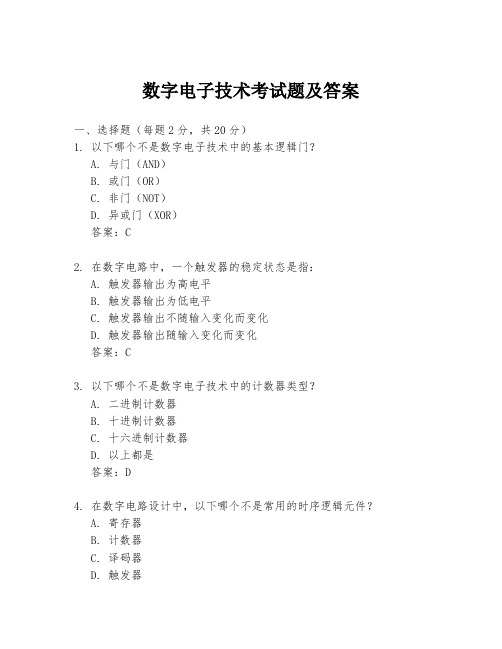

数字电子技术考试题及答案一、选择题(每题2分,共20分)1. 以下哪个不是数字电子技术中的基本逻辑门?A. 与门(AND)B. 或门(OR)C. 非门(NOT)D. 异或门(XOR)答案:C2. 在数字电路中,一个触发器的稳定状态是指:A. 触发器输出为高电平B. 触发器输出为低电平C. 触发器输出不随输入变化而变化D. 触发器输出随输入变化而变化答案:C3. 以下哪个不是数字电子技术中的计数器类型?A. 二进制计数器B. 十进制计数器C. 十六进制计数器D. 以上都是答案:D4. 在数字电路设计中,以下哪个不是常用的时序逻辑元件?A. 寄存器B. 计数器C. 译码器D. 触发器答案:C5. 以下哪个不是数字电路的分类?A. 组合逻辑电路B. 时序逻辑电路C. 模拟电路D. 混合电路答案:C6. 一个简单的数字电子系统通常包括哪些基本部分?A. 输入、处理、输出B. 电源、输入、输出C. 输入、存储、输出D. 电源、输入、处理、输出答案:D7. 以下哪个不是数字电子技术中常用的存储元件?A. 触发器B. 寄存器C. 锁存器D. 放大器答案:D8. 在数字电子技术中,一个信号的上升时间是指:A. 信号从0%到90%的最大值所需的时间B. 信号从10%到90%的最大值所需的时间C. 信号从0%到100%的最大值所需的时间D. 信号从10%到100%的最大值所需的时间答案:A9. 以下哪个是数字电子技术中的同步电路的特点?A. 所有触发器的时钟信号是独立的B. 所有触发器的时钟信号是同步的C. 电路中没有时钟信号D. 电路中只有一个触发器答案:B10. 在数字电子技术中,以下哪个不是布尔代数的基本运算?A. 与(AND)B. 或(OR)C. 非(NOT)D. 除(DIV)答案:D二、填空题(每空2分,共20分)11. 在数字电路中,逻辑“1”通常表示电压为______,逻辑“0”通常表示电压为______。

proteus元件对照表详细

p r o t e u s元件对照表详细The final revision was on November 23, 2020proteus常用元件中英文对照表元件名称中文名说明7407 驱动门1N914 二极管74Ls00 与非门74LS04 非门74LS08 与门74LS390 TTL 双十进制计数器7SEG 4针BCD-LED 输出从0-9 对应于4根线的BCD码7SEG 3-8译码器电路BCD-7SEG转换电路ALTERNATOR 交流发电机AMMETER-MILLI mA安培计AND 与门BATTERY 电池/电池组BUS 总线CAP 电容CAPACITOR 电容器CLOCK 时钟信号源CRYSTAL 晶振D-FLIPFLOP D触发器FUSE 保险丝GROUND 地LAMP 灯LED-RED 红色发光二极管LM016L 2行16列液晶可显示2行16列英文字符,有8位数据总线D0-D7,RS,R/W,EN三个控制端口(共14线),工作电压为5 V。

没背光,和常用的1602B功能和引脚一样(除了调背光的二个线脚)LOGIC ANALYSER 逻辑分析器LOGICPROBE 逻辑探针LOGICPROBE[BIG] 逻辑探针用来显示连接位置的逻辑状态LOGICSTATE 逻辑状态用鼠标点击,可改变该方框连接位置的逻辑状态LOGICTOGGLE 逻辑触发MASTERSWITCH 按钮手动闭合,立即自动打开MOTOR 马达OR 或门POT-LIN 三引线可变电阻器POWER 电源RES 电阻RESISTOR 电阻器SWITCH 按钮手动按一下一个状态SWITCH-SPDT 二选通一按钮VOLTMETER 伏特计VOLTMETER-MILLI mV伏特计VTERM 串行口终端Electromechanical 电机Inductors 变压器Laplace Primitives 拉普拉斯变换Memory IcsMicroprocessor IcsMiscellaneous 各种器件 AERIAL-天线;ATAHDD;ATMEGA6 4;BATTERY;CELL;CRYSTAL-晶振;FUSE;METER-仪表;Modelling Primitives 各种仿真器件是典型的基本元器模拟,不表示具体型号,只用于仿真,没有PCBOptoelectronics 各种发光器件发光二极管,LED,液晶等等PLDs & FPGAsResistors 各种电阻Simulator Primitives 常用的器件Speakers & SoundersSwitches & Relays 开关,继电器,键盘Switching Devices 晶阊管Transistors 晶体管(三极管,场效应管)TTL 74 seriesTTL 74ALS seriesTTL 74AS seriesTTL 74F series TTL 74HC series TTL 74HCT series TTL 74LS series TTL 74S series Analog Ics 模拟电路集成芯片 Capacitors 电容集合 CMOS 4000 series Connectors 排座,排插 Data Converters ADC, DAC Debugging Tools 调试工具 ECL 10000 Series包括电阻、电容、二极管、三极管和PCB的连接器符号包括虚拟仪器和有源器件包括二极管和整流桥包括LCD、LED包括三极管包括场效应管包括模拟元器件VALVES .LIB 包括电子管包括电源调节器、运放和数据采样IC包括电容包括 4000系列包括ECL10000系列包括通用微处理器包括运算放大器包括电阻FAIRCHLD .LIB 包括FAIRCHLD 半导体公司的分立器件包括 LINTEC公司的运算放大器包括国家半导体公司的数字采样器件包括国家半导体公司的运算放大器包括TECOOR公司的 SCR 和TRIAC包括德州仪器公司的运算放大器和比较器ZETEX .LIB 包括ZETEX 公司的分立器件分立元件库元件名称及中英对照AND 与门ANTENNA 天线BATTERY 直流电源BELL 铃,钟BVC 同轴电缆接插件BRIDEG 1 整流桥(二极管) BRIDEG 2 整流桥(集成块) BUFFER 缓冲器BUZZER 蜂鸣器CAP 电容CAPACITOR 电容CAPACITOR POL 有极性电容CIRCUIT BREAKER 熔断丝COAX 同轴电缆CON 插口CRYSTAL 晶体整荡器DB 并行插口DIODE 二极管DIODE SCHOTTKY 稳压二极管DIODE VARACTOR 变容二极管DPY_3-SEG 3段LEDDPY_7-SEG 7段LEDDPY_7-SEG_DP 7段LED(带小数点) ELECTRO 电解电容FUSE 熔断器INDUCTOR 电感INDUCTOR IRON 带铁芯电感JFET N N沟道场效应管JFET P P沟道场效应管LAMP 灯泡LAMP NEDN 起辉器LED 发光二极管METER 仪表MICROPHONE 麦克风MOSFET MOS管MOTOR AC 交流电机MOTOR SERVO 伺服电机NAND 与非门NOR 或非门NOT 非门NPN NPN 三极管NPN-PHOTO 感光三极管OPAMP 运放OR 或门PHOTO 感光二极管PNP 三极管NPN DAR NPN三极管PNP DAR PNP三极管POT 滑线变阻器PELAY-DPDT 双刀双掷继电器电阻可变电阻RESISTOR BRIDGE 桥式电阻RESPACK 电阻SCR 晶闸管PLUG 插头PLUG AC FEMALE 三相交流插头SOCKET 插座SOURCE CURRENT 电流源SOURCE VOLTAGE 电压源SPEAKER 扬声器SW 开关SW-DPDY 双刀双掷开关SW-SPST 单刀单掷开关SW-PB 按钮THERMISTOR 电热调节器TRANS1 变压器TRANS2 可调变压器TRIAC 三端双向可控硅TRIODE 三极真空管VARISTOR 变阻器ZENER 齐纳二极管 DPY_7-SEG_DP 数码管 SW-PB 开关元件名称中文名说明 7407 驱动门 1N914 二极管74Ls00 与非门74LS04 非门74LS08 与门74LS390 TTL 双十进制计数器7SEG 4针BCD-LED 输出从0-9 对应于4根线的BCD码7SEG 3-8译码器电路BCD-7SEG转换电路ALTERNATOR 交流发电机AMMETER-MILLI mA安培计AND 与门BATTERY 电池/电池组BUS 总线CAP 电容CAPACITOR 电容器CLOCK 时钟信号源CRYSTAL 晶振D-FLIPFLOP D触发器FUSE 保险丝GROUND 地LAMP 灯LED-RED 红色发光二极管LM016L 2行16列液晶可显示2行16列英文字符,有8位数据总线D0-D7, RS,R/W,EN三个控制端口(共14线),工作电压为5V。

EDA课程设计_7

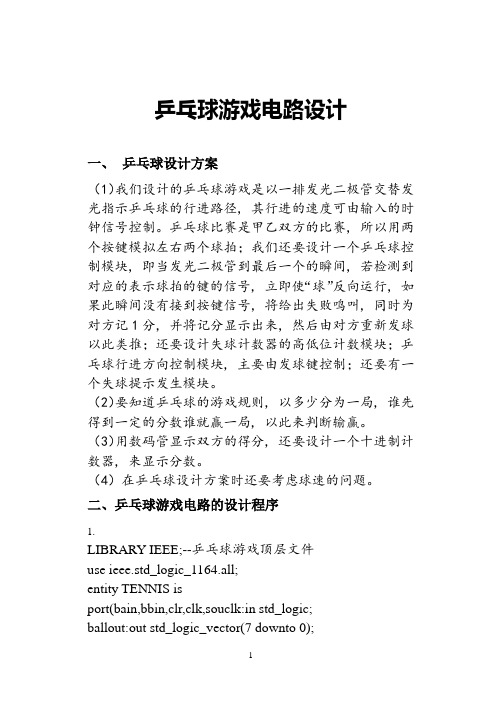

乒乓球游戏电路设计一、乒乓球设计方案(1)我们设计的乒乓球游戏是以一排发光二极管交替发光指示乒乓球的行进路径, 其行进的速度可由输入的时钟信号控制。

乒乓球比赛是甲乙双方的比赛, 所以用两个按键模拟左右两个球拍;我们还要设计一个乒乓球控制模块, 即当发光二极管到最后一个的瞬间, 若检测到对应的表示球拍的键的信号, 立即使“球”反向运行, 如果此瞬间没有接到按键信号, 将给出失败鸣叫, 同时为对方记1分, 并将记分显示出来, 然后由对方重新发球以此类推;还要设计失球计数器的高低位计数模块;乒乓球行进方向控制模块, 主要由发球键控制;还要有一个失球提示发生模块。

(2)要知道乒乓球的游戏规则, 以多少分为一局, 谁先得到一定的分数谁就赢一局, 以此来判断输赢。

(3)用数码管显示双方的得分, 还要设计一个十进制计数器, 来显示分数。

(4)在乒乓球设计方案时还要考虑球速的问题。

二、乒乓球游戏电路的设计程序1.LIBRARY IEEE;--乒乓球游戏顶层文件use ieee.std_logic_1164.all;entity TENNIS isport(bain,bbin,clr,clk,souclk:in std_logic;ballout:out std_logic_vector(7 downto 0);countah,countal,countbh,countbl:out std_logic_vector(3 downto 0);lamp,speaker:out std_logic);end entity TENNIS;architecture ful of TENNIS iscomponent soundport(clk,sig,en:in std_logic;sout:out std_logic);end component;component ballctrlport(clr,bain,bbin,serclka,serclkb,clk:in std_logic; bdout,serve,serclk,ballclr,ballen:out std_logic);end component;component ballport(clk,clr,way,en:in std_logic;ballout:out std_logic_vector(7 downto 0));end component;component boardport(ball,net,bclk,serve:in std_logic;couclk,serclk:out std_logic);end component;component cou10port(clk,clr:in std_logic;cout:out std_logic;qout:out std_logic_vector(3 downto 0));end component;component cou4port(clk,clr:in std_logic;cout:out std_logic;qout:out std_logic_vector(3 downto 0));end component;component mwayport(servea,serveb:in std_logic;way:out std_logic);end component;signalnet,couclkah,couclkal,couclkbh,couclkbl,cah,cbh:std_logic; signalserve,serclka,serclkb,serclk,ballclr,bdout,way,ballen:std_lo gic;signal bbll:std_logic_vector(7 downto 0);beginnet<=bbll(4);ballout<=bbll;lamp<=clk;uah:cou4 port map(couclkah,clr,cah,countah);ual:cou10 port map(couclkal,clr,couclkah,countal);ubh:cou4 port map(couclkbh,clr,cbh,countbh);ubl:cou10 port map(couclkbl,clr,couclkbh,countbl); ubda:board port map(bbll(0),net,bain,serve,couclkal,serclka);ubdb:board port map(bbll(7),net,bbin,serve,couclkbl,serclkb);ucpu:ballctrlportmap(clr,bain,bbin,serclka,serclkb,clk,bdout,serve,serclk, ballclr,ballen);uway:mway port map(serclka,serclkb,way);uball:ball port map(clk,ballclr,way,ballen,bbll);usound:sound port map(souclk,ballen,bdout,speaker);end ful;2.library ieee;use ieee.std_logic_1164.all;entity sound isport(clk:in std_logic; --发声时钟sig:in std_logic; --正确接球信号en:in std_logic; --球拍接球脉冲sout:out std_logic); --提示声输出, 接小喇叭end entity sound;architecture ful of sound isbeginsout<=clk and (not sig) and en;--球拍接球, 没接到时, 发提示声end ful;3.library ieee; --总控制模块use ieee.std_logic_1164.all;entity ballctrlisport(clr:in std_logic; --系统复位bain:in std_logic; --左球拍bbin:in std_logic; --右球拍seclka:in std_logic; --左拍准确接球或发球serclkb:in std_logic; --右拍准确接球或发球clk:in std_logic; --乒乓球灯移动时钟bdout:out std_logic; --球拍接球脉冲serve:out std_logic; --发球状态信号serclk:out std_logic; --球拍正确接球信号ballclr:out std_logic; --乒乓球灯清零信号ballen:out std_logic); --乒乓球灯使能end entity ballctrl;architecture ful of ballctrl issignal bd:std_logic;signal ser:std_logic;beginbd<=bain or bbin;ser<=serclka or serclkb;serclk<=ser;--球拍正确接球信号bdout<=bd; --球拍接球脉冲process(clr,clk,bd)beginif(clr='1')then --系统复位serve<='1'; --系统处在职发球状态ballclr<='1'; --乒乓球灯清零elseif(bd='1')then --系统正常--球拍发球或接球时ballclr<='1'; --乒乓球灯清零if(ser='1')then --球拍发球或准确接球ballen<='1'; --乒乓球灯使能允许serve<='0'; --系统处在接球状态else ballen<='0';serve<='1'; --系统处在发球状态end if;else ballclr<='0';--没发球或接球时乒乓球灯不清零end if;end if;end process;end ful;4.--乒乓球灯模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity ball isport(clk:in std_logic; --乒乓球灯前进时钟clr:in std_logic; --乒乓球灯清零way:in std_logic; --乒乓球灯前进方向en:in std_logic; --乒乓球灯使能ballout:out std_logic_vector(7 downto 0));--乒乓球灯end entity ball;architecture ful of ball issignal lamp:std_logic_vector(9 downto 0);beginprocess(clk,clr,en)beginif(clr='1') then lamp<="1000000001";--清零elsif en='0' thenelsif (clk'event and clk='1')then--使能允许, 乒乓球灯前进时钟上升沿if(way='1') then lamp(9 downto 1)<=lamp(8 downto 0);lamp(0)<='0';--乒乓球灯右移else lamp(8 downto 0)<=lamp(9 downto 1); lamp(9)<='0';--乒乓球灯左移end if;end if;ballout<=lamp(8 downto 1);end process;end ful;5.--乒乓拍模块library ieee;use ieee.std_logic_1164.all;entity board isport(ball:in std_logic; --接球点, 也就是乒乓球灯的末端net:in std_logic; --乒乓球灯的中点, 乒乓球过中点时, counclk、serclk复位bclk:in std_logic; --球拍接球信号serve:in std_logic; --发球信号couclk:out std_logic;serclk:out std_logic);end entity board;architecture ful of board isbeginprocess(bclk,net)beginif(net='1')then serclk<='0';couclk<='0';--乒乓球过中点时, counclk、serclk复位elsif(bclk'event and bclk='1')then—球拍接球时if(serve='1')then serclk<='1';--系统处于发球状态时—发球成功else—系统处于接球状态if(ball='1')then serclk<='1';--乒乓球刚落在接球点上, 接球成功else serclk<='0';couclk<='1';end if;end if;end if;end process;end ful;6.--十进制计数器用来做失球低位计数library ieee;use ieee.std_logic_1164.all;entity mway isport(servea:in std_logic;serveb:in std_logic;way:out std_logic);end entity mway;architecture ful of mway isbeginprocess(servea,serveb)beginif(servea='1')then way<='1';elsif(serveb='1')then way<='0';end if;end process;end ful;7、--四进制计数器用来做失球高位计数library ieee;use ieee.std_logic_1164.all;entity mway isport(servea:in std_logic;serveb:in std_logic;way:out std_logic);end entity mway;architecture ful of mway isbeginprocess(servea,serveb)beginif(servea='1')then way<='1';elsif(serveb='1')then way<='0';end if;end process;end ful;8、--乒乓球前进方向产生模块library ieee;use ieee.std_logic_1164.all;entity mway isport(servea:in std_logic;--左选手发球信号serveb:in std_logic;--右选手发球信号way:out std_logic);--乒乓球灯前进方向信号end entity mway;architecture ful of mway isbeginprocess(servea,serveb)beginif(servea='1')then way<='1';--左选手发球方向向右elsif(serveb='1')then way<='0';--右选手发球方向向左end if;end process;end ful;三、乒乓球游戏程序的仿真波形仿真波形图四、硬件测试方法然后我们就要测试硬件, 下载文件。

《数字电子技术与接口技术试验教程》课件第5章

第5章 基于HDL的时序逻辑电路实验

图5-2 边沿D触发器的仿真结果

9

第5章 基于HDL的时序逻辑电路实验 (2) 边沿D触发器的VHDL源代码如下:

--Behavioral D Flip-Flop with Clock Enable and Asynchronous Reset

entity Dflipflop is Port (D,clk,rst,ce : in STD_LOGIC; Q : out STD_LOGIC);

architecture Behavioral of DFF is begin

process(clk, rst,D) begin

if (CLK'event and CLK='1') then if rst ='1' then Q <= '0'; else Q<=D; end if;

end if; end process; end Behavioral;

end if; end process; end Behavioral;

13

第5章 基于HDL的时序逻辑电路实验

(3) 带有置位和清零端的边沿D触发器的约束文件规定

如下:

#Basys2约束文件: NET "clk" LOC ="B8"; //时钟

#Basys2约束文件: NET "clk" LOC ="B8"; //时钟

end Dflipflop;

architecture Behavioral of Dflipflop is begin

process(clk, rst,D,ce)

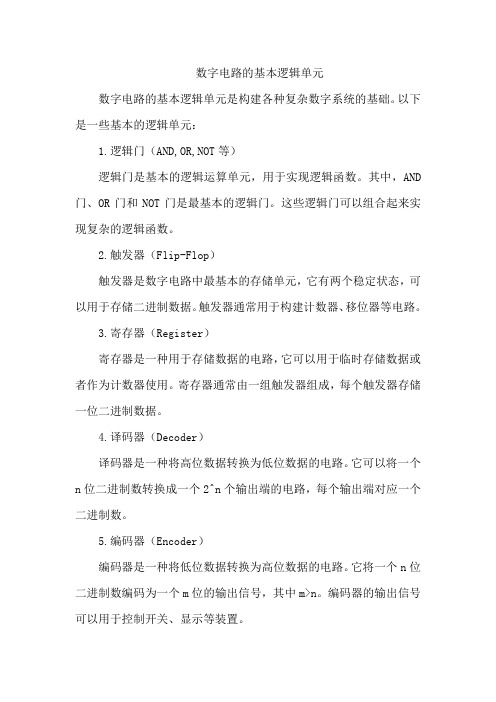

数字电路的基本逻辑单元

数字电路的基本逻辑单元数字电路的基本逻辑单元是构建各种复杂数字系统的基础。

以下是一些基本的逻辑单元:1.逻辑门(AND,OR,NOT等)逻辑门是基本的逻辑运算单元,用于实现逻辑函数。

其中,AND 门、OR门和NOT门是最基本的逻辑门。

这些逻辑门可以组合起来实现复杂的逻辑函数。

2.触发器(Flip-Flop)触发器是数字电路中最基本的存储单元,它有两个稳定状态,可以用于存储二进制数据。

触发器通常用于构建计数器、移位器等电路。

3.寄存器(Register)寄存器是一种用于存储数据的电路,它可以用于临时存储数据或者作为计数器使用。

寄存器通常由一组触发器组成,每个触发器存储一位二进制数据。

4.译码器(Decoder)译码器是一种将高位数据转换为低位数据的电路。

它可以将一个n位二进制数转换成一个2^n个输出端的电路,每个输出端对应一个二进制数。

5.编码器(Encoder)编码器是一种将低位数据转换为高位数据的电路。

它将一个n位二进制数编码为一个m位的输出信号,其中m>n。

编码器的输出信号可以用于控制开关、显示等装置。

6.多路复用器(Multiplexer)多路复用器是一种将多个输入信号组合成一个输出信号的电路。

它可以通过选择不同的输入信号来获得所需的输出信号。

多路复用器通常用于实现数据选择器、数据分配器等电路。

7.多路解复用器(Demultiplexer)多路解复用器是一种将一个输入信号分解成多个输出信号的电路。

它将一个输入信号分成多个输出信号,每个输出信号对应一个数据通道。

多路解复用器通常用于实现数据分配器、数据选择器等电路。

8.比较器(Comparator)比较器是一种用于比较两个输入信号大小的电路。

如果两个输入信号相等,则比较器的输出为高电平;否则,输出为低电平。

比较器通常用于在排序算法或查找算法中比较数值。

9.算术逻辑单元(ALU)算术逻辑单元是一种进行算术运算和逻辑运算的电路。

它可以执行加减乘除等基本算术运算,以及与、或、非等基本逻辑运算。

数字电子期末考试题及答案

数字电子期末考试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑关系有几种?A. 2种B. 3种C. 4种D. 5种答案:B2. 以下哪个不是基本的逻辑门?A. AND门B. OR门C. NOT门D. XOR门答案:D3. 一个触发器可以存储多少位二进制信息?A. 1位B. 2位C. 3位D. 4位答案:A4. 以下哪个是组合逻辑电路的特点?A. 输出状态与输入状态有关B. 输出状态与输入状态无关C. 输出状态只与当前输入状态有关D. 输出状态只与过去输入状态有关答案:A5. 以下哪个是时序逻辑电路的特点?A. 输出状态与输入状态有关B. 输出状态与输入状态无关C. 输出状态只与当前输入状态有关D. 输出状态与当前输入状态和过去输入状态都有关答案:D二、填空题(每空2分,共20分)6. 数字电路中,最基本的信号类型是______和______。

答案:数字信号;模拟信号7. 一个完整的数字系统通常由______和______两部分组成。

答案:硬件;软件8. 在数字电路中,常用的计数器类型有二进制计数器、______计数器等。

答案:十进制9. 一个8位的寄存器可以存储______个二进制位。

答案:810. 在数字电路中,信号的频率越高,其传输的______也越高。

答案:数据量三、简答题(每题10分,共30分)11. 简述数字电路与模拟电路的主要区别。

答案:数字电路处理的是离散的数字信号,而模拟电路处理的是连续的模拟信号。

数字电路具有更高的抗干扰能力,且易于实现大规模集成。

模拟电路则在信号处理的精度和连续性上有优势。

12. 解释什么是触发器,并简述其在数字电路中的作用。

答案:触发器是一种具有记忆功能的电路元件,可以存储一位二进制信息。

在数字电路中,触发器常用于存储中间结果,实现寄存器、计数器等功能。

13. 描述数字电路中同步计数器和异步计数器的区别。

答案:同步计数器的时钟信号同时控制所有触发器的时钟输入,而异步计数器的触发器时钟输入是独立控制的。

三菱PLC指令详解

三菱PLC指令详解三菱PLC指令详解一、顺控指令 19 MC 主控开始 35 AND<= 56 ANDD< 1 触点指令 20 MCR 主控复位 36 OR<= 57 ORD< 00 LD 逻辑操作开始 6 结束指令 37 LD< 当S1= 当(S1+1,S1)?(S2+1,S2),接01 LDI 逻辑非操作开始21 FEND 结束主程序当S1?S2, 断开通 02 AND 逻辑乘 22 END 总的程序末尾, 38 AND<59 ANDD>= 03 ANI 逻辑乘非返回第0步 39 OR< 60 ORD>=04 OR 逻辑加 7 其它指令 40 LD>= 当S1?S2, 接通, 2 算术运算指令05 ORI 逻辑加非 23 STOP 停止当S1= 61+ (D)+(S)?(D) 06 ANB AND逻辑块与二基本指令 42 OR>= 62 +P 07 ORB OR逻辑块或 1 比较指令 32位数据比较 63 + (S1)+(S2)?(D) 08 MPS 存储操作结果16位数据比较 43 LDD= 当(S1+1,S1)=(S2+1,S2), 接通 64 +P 09 MRD 从MPS读取操作结果25 LD= 当S1=S2, 接通,44 ANDD= 65 - (D)-(S)?(D) 10 MPP 从MPS读取操作结果当S1?S2, 断开 45 ORD= 66 -P 并清除结果 26 AND= 46 LDD<> 当(S1+1,S1)?(S2+1,S2),接67 - (S1)-(S2)?(D) 3 输出指令 27 OR= 通 68 -P11 OUT 软元件输出 28 LD<> 当S1?S2, 接通, 47 ANDD<> 二进制32位加/减12 SET 软元件置位当S1=S2, 断开48 ORD<> 69 D+ (D+1,D)+(S+1,S)?(D+1,D) 13 RST 软元件复位29 AND<> 49 LDD> 当(S1+1,S1)>(S2+1,S2), 接通 70 D+P 14 PLS 在输入信号的上升沿 30 OR<> 50 ANDD> 71 D+ (S1+1,S1)+(S2+1,S2)?(D+1,D) 15 PLF 在输入信号的下降沿 31 LD> 当S1>S2, 接通, 51 ORD> 72D+P 16 CHK软元件输出翻转当S1?S2, 断开52 LDD<= 当(S1+1,S1)?(S2+1,S2),接73 D-(D+1,D)-(S+1,S)?(D+1,D) 4 移位指令 32 AND> 通 74 D-P 17 SFT 元件移1位33 OR> 53 ANDD<= 75 D- (S1+1,S1)-(S2+1,S2)?(D+1,D) 18 SFTP 元件移1位 34LD<= 当S1?S2, 接通, 54 ORD<= 76 D-P 5 主控指令当S1>S2, 断开 55 LDD< 当(S1+1,S1)<(S2+1,S2), 接通77 * (S1)×(S2)?(D+1,D)78 *P 102 B*P 4 数据传送指令 148 EI 允许中断 79 / (S1)/(S2)?商(D),余数(D+1) 103 B/ (S1)/(S2)?商(D),余数(D+1) 125 MOV (S)?(D) 149 DI 禁止中断 80 /P 104 B/P 126 MOVP 150 IRET 从中断程序返回 81 D*(S1+1,S1)×(S2+1,S2)? 105 DB*(S1+1,S1)×(S2+1,S2)? 127 DMOV(S+1,S)?(D+1,D) 151 SUB 执行n指定的程序 (D+3,D+2,D+1,D) (D+3,D+2,D+1,D) 128 DMOVP 152 SUBP 82 D*P 106 DB*P 129 CML (S)?(D) 6 程序切换指令 83 D/ (S1+1,S1)/(S2+1,S2)? 107 DB/ (S1+1,S1)/(S2+1,S2)? 130 CMLP 153 CHG 在主副程序间切换商(D+1,D),余数(D+3,D+2) 商(D+1,D),余数(D+3,D+2) 131 DCML(S+1,S)?(D+1,D) 7 刷新指令 84 D/P 108 DB/P 132 DCML 154 COM 执行通讯刷新85 B+ (D)+(S)?(D) 109 INC (D)+1?(D) 133 DCMLP 155 EI 允许通讯刷新 86 B+P 110 INCP 134 BMOV (S)?(D)n 个156 DI 禁止通讯刷新87 B+ (S1)+(S2)?(D) 111 DINC (D+1,D)+1?(D+1,D) 135 BMOVP 157 SEG 对应软元件的刷新,仅执行188 B+P 112 DINCP 136 FMOV (S)?(D)n个个扫描周期,M9052 ON时有效89 B- (D)-(S)?(D) 113 DEC (D)-1?(D) 137FMOVP 三应用指令 90 B-P 114 DECP 138 XCH (D1)??(D2) 1 逻辑运算指令 91 B- (S1)-(S2)?(D) 115 DDEC (D+1,D)-1?(D+1,D) 139 XCHP 158 WAND (D) AND (S)?(D) 92 B-P 116 DDECP 140 DXCH (D1+1,D1)??(D2+1,D2) 159 WANDP 93 DB+ (D+1,D)+(S+1,S) ?(D+1,D) 3 BCD—二进制转换141 DXCHP 160 WAND (S1) AND (S2)?(D) 94 DB+P 117 BCD (S)?(D)BCD 转换 5 程序分支指令161 WANDP 95 DB+ (S1+1,S1)+(S2+1,S2)?(D+1,D) 118 BCDP 142 CJ 条件满足,跳转到P**处 162 DAND (D+1,D) AND (S+1,S)?(D+1,96 DB+P 119 DBCD (S+1,S)?(D+1,D) 143 SCJ 条件满足后紧接的扫描周期, D) 97DB- (D+1,D)-(S+1,S)?(D+1,D) 120 DBCDP 跳转到P**处163 DANDP 98 DB-P 121 BIN (S)?(D)二进制转换 144 JMP 无条件跳转到P**处164 WOR (D) OR (S)?(D) 99 DB- (S1+1,S1)-(S2+1,S2)?(D+1,D) 122 BINP 145 CALL 执行P**处子程序165 WORP 100 DB-P 123 DBIN (S+1,S)?(D+1,D) 146 CALLP 166 WOR (S1) OR(S2)?(D) 101 B* (S1)×(S2)?(D+1,D) 124 DBINP 147 RET 从子程序返回 167 WORP168 DOR (D+1,D) OR (S+1,S)?(D+1,D) 191 RCLP 215 SUMP 239 DFROP 169 DORP 192 DROR n位右转 216 DSUM 240 TO 向特殊功能模块写数据 170 WXOR (D) XOR (S)?(D)异或 193 DRORP 217 DSUMP 241 TOP 171 WXORP 194 DRCR n位右转(带进位) 218 DECO 译码编码 242 DTO 172 WXOR (S1) XOR (S2)?(D) 195 DRCRP 219 DECOP 243 FROM 从远程I/O站读数据 173 WXORP 196 DROL n位左转220 ENCO 244 FROMP 174 DXOR (D+1,D) XOR (S+1,S)?(D+1,197 DROLP 221 ENCOP 245 DFRO D) 198 DRCL n 位左转(带进位) 222 SEG 7段编码246 DFROP 175 DXORP 199 DRCLP 223 BSET 对字中n位置位247 TO 向远程站写数据176 WXNR (D) XOR (S)?(D) 3 移位指令 224 BSETP 248 TOP 177 WXNRP 200 SFR n位右移 225 BRST 对字中n位复位 249 DTO 178 WXNR(S1) XOR (S2)?(D) 201 SFRP 226 BRSTP 250 DTOP 179 WXNRP 202 SFL n位左移 227 DIS 组合分离 7 FOR/NEXT指令 180 DXNR (D+1,D) XOR (S+1,S)?(D+1,203 SFLP 228 DISP 251 FOR 重复n次D) 204 BSFR 1位右移 229 UNI 252 NEXT 181 DXNRP 205 BSFRP 230 UNIP 8 本地站、远程I/O 站存取指令 182 NEG 0-(D)?(D)补码206 BSFL 1位左移 231 ASC ASCII转化 253 LRDP 从本地站读数据183 NEGP 207 BSFLP 5 先进先出指令 254 LWTP 向本地站写数据 2 旋转指令 208 DSFR 1位右移 232 FIFW FIFO写 255 RFRP 从远程特殊功能模块读数据184 ROR n位右转209 DSFRP 233 FIFWP 256 RTOP 向远程特殊功能模块写数据 185 RORP 210 DSFL 1位左移 234 FIFR FIFO读9 显示指令 186RCR n位右转(带进位) 211 DSFLP 235 FIFRP 257 PR 从指定的8点字软元件输出187 RCRP 4 数据处理指令 6 内存缓冲区存取指令 16个字符的ASCII码 188 ROL n位左转 212 SER 数据搜索 236 FROM 从特殊功能模块读取数据 258 PR 顺序向输出模块输出ASCII 189 ROLP 213 SERP 237 FROMP 码, 直到结束符NUL(00H) 190 RCL n位左转(带进位) 214 SUM 位检查 238 DFRO 259 PRC 将字软元件的注释转换成ASCII码,并输出 M9000 熔丝断 M9033 2秒时钟 M9061 通讯出错 260 LED将指定的8点字软元件显示 M9002 I/O组件校验出错 M9034 1分钟时钟M9065 分离传送状态16个字符的ASCII码M9004 MINI 网通讯出错 M9036 常开 M9066 传送处理切换 261 LEDA 显示指定的英文数字字符 M9005 AC电源掉电检测 M9037常闭M9067 I/O组件出错检测262 LEDB M9006 电池电压低M9038 RUN后第一个扫描周期ON M9068 测试模式 263 LEDC 显示软元件S的注释 M9007 电池电压低锁存 M9039 运行标志 M9069 线路故障时的输出 264 LEDR 显示复位 M9008 自诊断出错 M9040 暂停PAUSE允许线圈 M9073 WDT 出错标志 10 其它指令 M9009 信号报警器检测 M9041 PAUSE状态触点 M9074 PCPU准备完成标志 265 WDT WDT复位 M9010 运算出错标志 M9042 停止状态触点 M9075 测试模式标志 266 WDTPM9011 运算出错标志锁存 M9043 采样跟踪完成 M9076 外部急停输入标志267 CHK 故障检测M9012 进位标志M9044 采样跟踪M9077 手动脉冲发生器轴设置错误标志268 SLT 按参数设定的条件,数据被锁M9016 数据存储区清零标志 M9046 采样跟踪 M9078 测试模式请求出错标志定 M9017 数据存储区清零标志 M9047 采样跟踪准备M9079 伺复程序设置出错标志269 SLTR 状态锁存复位,且执行SLTM9018 数据通讯监控切换 M9048 RUN LED闪烁标志 M9081 对远程模块的通讯请求270 STRA 按参数设定的条件,采样数据M9020 0号用户定时时钟 M9049 切换输出字符数目 M9082 最终站数不一致存入 M9021 1号用户定时时钟 M9050 存放操作结果的存储区交换触点 M9084 出错检测 271 STRAR 采样跟踪复位,且允许执行M9022 2号用户定时时钟 M9051 CHG指令执行禁止 M9086 运行标志BASIC程序272 STC 进位标志(M9012)ON M9023 3号用户定时时钟 M9052 SEG指令切换M9087 暂停(PAUSE)标志273 CLC 进位标志(M9012)OFF M9024 4号用户定时时钟 M9053EI/DI指令切换 M9091 操作运行出错细节标志 274 DUTY 用户定义时钟 M9025 时钟数据设置请求 M9054 单步运行标志 M9091 微机子程序调用出错标志 11 伺服指令 M9026 时钟数据出错 M9055 状态锁存完成标志M9092 双电源模块过热 275 DSFRP 请求启动伺服程序 M9027 时钟数据显示 M9056 主程序P, I设置请求M9093 双工电源模块出错M9028 时钟数据读请求 M9057 副程序P, I设置程序 M9094 I/O 改变标志 276 PSFLP 数据修改M9030 0.1秒时钟 M9060 副程序2P, I设置程序 M9095 双工运行校验出错特殊继电器和特殊寄存器 M9031 0.2秒时钟 M9061 副程序3P, I设置程序 M9096A3VCPU A自校出错一特殊继电器M清单M9032 1秒时钟M9060 远程终端出错M9097 A3VCPU B自校出错M9098 A3VCPU C自校出错 M9197~9198 保险丝熔断, D9026 时钟数据(日,时) D9095 A3VTS系统和A3VM9099 A3VTU自校出错D9027 时钟数据(分,秒) CPU的运行状态 I/O校核出错显示切换M9100 SFC程序登记 D9028 时钟数据(星期) D9096 A3VCPU A 自检出错M9101 SFC程序起/停D9021~D9034 远程终端组件参数设置D9097 A3VCPU B自检出错二特殊寄存器 M9102 SFC启动状态 D9035 远程I/O组件的通讯属性D9098 A3VCPU C自检出错 D9000 保险丝断 M9103 连续步转移有效/失效 D9035扩展文件寄存器D9099 A3VTU 自检测出错D9001 保险丝断M9104 连续转移防止标志D9036 总的站数D9100~D9107 断保险丝的组件D9002 I/O组件校验出错M9108 步转移监控定时器起始 D9036~9037 供指定扩展文件寄存器软件D9100 保险丝熔断的组件 D9003 SUM指令检测位数 (对应D9108) 地址 D9108~D9114 步转移监控定时器设置 D9004 MINI网主通讯组件出错 M9109 步转移监控定时器起始D9038~9039 LED显示优先级 D9116~D9123 I/O组件校验出错D9005 AC掉电计数(对应D9109) D9044 采样跟踪 D9124 信号器报警数量检测 D9006 电池不足M9110 步转移监控定时器起始D9050 SFC程序出错代码D9125~D9132 信号报警器地址号 D9008 自诊断出错 (对应D9110) D9051 出错块 D9133~D9140 远程终端卡信息 D9009 信号报警器检测 M9111 步转移监控定时器起始 D9052 出错步D9141~D9172 通讯重发次数D9010 出错步(对应D9111) D9053 转移出错 D9173 模式设置 D9011 出错步 M9112 步转移监控定时器起始 D9054 出错顺控步 D9174 设置重发次数 D9014 I/O控制模式 (对应D9112) D9055 状态锁存步序号 D9175 线缆出错模块出错代码 D9015 CPU运行状态 M9113 步转移监控定时器起始 D9061 通讯出错代码 D9180~9193远程终端模块出错代码 D9016 ROM/RAM 设置 (对应D9113) D9072 PC通讯检测D9180 轴1和轴2的限位开关D9017 最小扫描时间M9114 步转移监控定时器起始D9081 对远程终端模块的输出状态存储区D9018 当前扫描时间(对应D9114) 已执行的通讯请求数D9181 轴3和轴4的限位开关D9019 最大扫描时间 M9180 激活步采样跟踪完成标志 D9082 最后的站号输出状态存储区 D9020 恒定扫描 M9181 激活步采样跟踪执行标志 D9090 微机子程序输入数据区首软元件D9182 轴5和轴6的限位开关 D9021 扫描时间 M9182 激活步采样跟踪有效号输出状态存储区D9022 1秒计数器M9196 在块停止时控制输出D9091 指令出错 D9183 轴7和轴8的限位开关 D9025 时钟数据(年,月) D9094 待更换的I/O组件的首地址输出状态存储区D9184 CPU出错的原因D9220 就地站参数不匹配或(1~16) D9238 就地站或远程I/O站环路出错辅助继电器内部继电器 (1000点)M0~MD9185伺服放大器接线数据远程站I/O分配出错D9239 就地站或远程I/O站环路出错999 M0~M999,M2048~8191 D9187 手动脉冲发生器轴设置出错 D9221 就地站参数不匹配或(17~32) D9240 检测到接收出错的次数特殊继电器 (256点)M9000~M9255 D9188 在TEST模式下启动轴号请求出错远程站I/O分配出错 D9243 本站站号检测锁存继电器(1048点)L1000~L2048 D9189 出错程序号D9222 就地站参数不匹配或(33~48)D9244 从站的总数通讯用继电器(2048点)B0~B3FF B0~BFD9190 数据设置出错远程站I/O分配出错 D9245 检测到的接收出错次数 FFD9191 伺服放大器类型D9223 就地站参数不匹配或(49~64) D9248 就地站运行状态定时器 100ms定时器 (200点)T0~T199 D9196~9199 故障站检测远程站I/O分配出错D9249 就地站运行状态10ms定时器(56点)T200~T255 D9200 LRDP处理结果 D9224 主站与从站和远程I/O站 D9250 就地站运行状态 100ms记忆定时器 (0点) D9201 LWTP处理结果之间的初始通讯(1~16) D9251 就地站运行状态计数器 (256点)C0~C255 D9204 通讯状态 D9225 主站与从站和远程I/O站D9252 就地站出错检测寄存器数据寄存器(1024点)D0~D102D9205 执行回送的站之间的初始通讯(17~32) D9253 就地站出错检测 3 D0~D6143 D9206 执行回送的站D9226 主站与从站和远程I/O站D9254 就地站出错检测特殊寄存器 (256点)D9000~D9255 D9207 通讯扫描时间(最大值) 之间的初始通讯(33~48) 通讯寄存器 (1024点)W0~W3FF W0~WFFD9255 就地站出错检测D9208 通讯扫描时间(最小值) D9227 主站与从站和远程I/O站 F D9209 通讯扫描时间(当前值) 之间的初始通讯(49~64) 累加器 (2点)A0,A1D9210 重发次数 D9228 就地站或远程I/O站出错(1~16) 变址寄存器 (2点)Z, V Z,Z1~Z6(7D9211 环路切换计数 D9229 就地站或远程I/O站出错(17~32) 点), V,V1~V6(7点)各种软元件一览表 D9212 就地站运行状态(1~16) D9230 就地站或远程I/O站出错(33~48) 嵌套 (8点)N0~ N7项目 A1,A1NA1S A2,A2NA2C A2-S1A2N-SD9213 就地站运行状态(17~32) D9231 就地站或远程I/O站出错(49~64) 指针(256点)P0~P2551 A3,A3NA3A A2U,A3UA4U D9214 就地站运行状态(33~48) D9232 就地站或远程I/O站环路出错中断指针 (32点)I0~I31I/O软元件点 256 512 1024 2048 8192 D9215 就地站运行状态(49~64) D9233 就地站或远程I/O站环路出错常数十进制K (16位)-32768~+3276 输入继电器 X 0~FF 0~1FF 0~3FF 0~7FD9216 就地站出错检测(1~16) D9234就地站或远程I/O站环路出错 7F 0~FFF D9217 就地站出错检测(17~32) D9235 就地站或远程I/O站环路出错(32位)-2147483648 ~+2147483647输出继电器 Y 0~FF 0~1FF 0~3FF 0~7FD9218 就地站出错检测(33~48) D9236 就地站或远程I/O站环路出错十六进制H (16位)0~FFFFF 0~FFF D9219 就地站出错检测(49~64) D9237 就地站或远程I/O站环路出错(32位)0~FFFFFFFF。

数电考试题及答案大学

数电考试题及答案大学一、选择题(每题3分,共30分)1. 在数字电路中,最基本的逻辑关系不包括以下哪一项?A. 与(AND)B. 或(OR)C. 非(NOT)D. 异或(XOR)答案:D2. 二进制数1011转换为十进制数是多少?A. 8B. 11C. 13D. 15答案:D3. 下列哪个触发器可以实现边沿触发?A. SR触发器B. JK触发器C. D触发器D. T触发器答案:C4. 在CMOS技术中,一个N型MOSFET在其栅极施加()时导通。

A. 低电平B. 高电平C. 任意电平D. 不确定答案:B5. 一个4位二进制计数器的最大计数范围是多少?A. 4B. 8C. 16D. 32答案:C6. 以下哪个是数字电路的优点?A. 高速度B. 低功耗C. 高稳定性D. 所有以上答案:D7. 在数字电路中,逻辑0通常对应于哪个电压范围?A. 0VB. 接近0VC. 接近电源电压D. 任意电压答案:B8. 一个简单的RAM存储单元通常由多少个晶体管组成?A. 4B. 6C. 8D. 16答案:A9. 在数字电路设计中,布尔代数主要用于实现什么?A. 逻辑简化B. 信号放大C. 电源管理D. 时钟分配答案:A10. 以下哪个不是数字电路中的存储元件?A. 触发器B. 寄存器C. 计数器D. 门电路答案:D二、填空题(每题4分,共20分)11. 在数字电路中,一个基本的逻辑门至少需要________个输入端。

答案:212. 一个8位的寄存器可以存储的最大十进制数是________。

答案:25513. 在TTL电路中,逻辑1的最小输出电压是________V。

答案:2.014. CMOS门电路的功耗主要取决于________。

答案:开关频率15. 一个3-8线译码器可以将3位二进制信号转换为________个独立信号。

答案:8三、简答题(每题10分,共30分)16. 解释什么是同步计数器和异步计数器,并说明它们的区别。

欧姆龙PLC指令

4指令助记符:按时器TIM5编辑指令:数据移位指令,递增/递减指令,四那么运算指令,转换指令,逻辑指令,特殊算术指令,表格数据处置指令,数据操纵指令。

6指令助记符移位寄放器SFT可逆移位寄放器SFTR字移位WSFT算术左移ASL算术右移ASR循环左移ROL循环右移ROR一个数字左移SLD一个数字右移SRD左移N位NASL双字左移N位NSLL右移N位NASR双字右移N位NSRL7指令助记符二进制递增++双字二进制递增++L二进制递减--双字二进制递减--LBCD递增++B,双字BCD递增++BL,BCD递减--B,双字BCD递减--BL8指令助记符无进位带符号二进制加法+,无进位带符号双字二进制加法+L,有进位带符号二进制加法+C,有进位带符号双字二进制加法+CL,无进位BCD加法+B,无进位双字BCD加法+BL,有进位BCD加法+BC,有进位双字BCD加法+BCL,无进位带符号二进制减法-无进位带符号双字二进制减法-L,有进位带符号二进制减法-C,有进位带符号双字二进制减法-CL,无进位BCD减法-B,无进位双字BCD减法-BL,有进位BCD减法-BC 有进位双字BCD减法-BCL,带符号二进制乘法*,带符号双字二进制乘法*L,BCD乘法*B,双字BCD乘法*BL,带符号二进制除法/,带符号双字二进制除法/L,BCD除法/B双字BCD除法/BL9指令助记符BCD→二进制BIN,双字BCD→双字二进制BINL,二进制→BCD BCD双字二进制→双字BCD BCDL二进制求补NEG,数据译码MLPX,数据编码DMPX,ASCⅡ转换码ASC,ASCⅡ→HEX HEX10指令助记符逻辑与ANDW,双字逻辑与ANDL,逻辑或ORW,双字逻辑或ORWL,异或XORW双字异或XORL,求补COM,双字求补COML11指令助记符算术处置APR,位计数器BCNT12指令助记符浮点数→16位FIX,浮点数→32位FIXL,16位→浮点数FLT,32位→浮点数FLTL浮点数加法+F,浮点数减法-F,浮点数除法/F,浮点数乘法*F浮点符号比较LD, AND, OR+=FLD, AND, OR+<>FLD, AND, OR+<FLD, AND, OR+<=FLD, AND, OR+>FLD, AND, OR+>=F浮点数→ASCⅡFSTRASCⅡ→浮点数FVAL12指令助记符互换字节SWAP,帧校验和FCS13指令助记符带自调整的PID操纵PIDAT,时刻比例输出TPO,标度SCL,标度2 SCL2,标度3 SCL3平均值AVG14指令助记符子程序挪用SBS,子程序进入SBN,子程序返回RET,设置中断屏蔽MSKS,清除中断CLI,禁止中断DI,许诺中断EI,模式操纵INI,高速计数器当前值读取PRV比较表载入CTBL,速度输出SPED,设置脉冲PULS,脉冲输出PLS2,加速度模式ACC原点搜索ORG,可变占空比系数脉冲PWM15指令助记符步概念STEP,步启动SNXT,I/O刷新IORF,7段译码SDEC,数字开关输入DSW矩阵输入MTR,7段显示输出7SEG发送TXD,接收RXD,日历加法CADD,日历减法CSUB,时钟调整DATE,故障报警FAL 严峻故障报警FALS,设置进位STC,清除进位CLC,延长最大循环时刻WDT TIMX计数器:CNT,CNTX高速按时器:TIMH,TIMHX1MS按时器:TMHH,TMHHX累计按时器:TTIM,TTIMX长时刻按时器:TIML,TIMLX可逆计数器:CNTR,CNTRX按时器/计数器复位:CNR,CNRX 16指令助记符输入比较指令(无符号)LD,AND,OR+=LD,AND,OR+<>LD,AND,OR+<LD,AND,OR+<=LD,AND,OR+>LD,AND,OR+>=输入比较指令(双字长,无符号)LD,AND,OR+=+LLD,AND,OR+<>+LLD,AND,OR+<+LLD,AND,OR+<=+LLD,AND,OR+>+LLD,AND,OR+>=+L输入比较指令(带符号)LD,AND,OR+=+SLD,AND,OR+<>+SLD,AND,OR+<+SLD,AND,OR+<=+SLD,AND,OR+>+SLD,AND,OR+>=+S输入比较指令(双字长,带符号)LD,AND,OR+=+SLLD,AND,OR+<>+SLLD,AND,OR+<+SLLD,AND,OR+<=+SLLD,AND,OR+>+SLLD,AND,OR+>=+SL时刻比较指令=DT<>DT<DT<=DT>DT>=DT比较CMP,双字比较CMPL,带符号二进制比较CPS,双字长带符号二进制比较CPSL表格比较TCMP,无符号块比较BCMP,区域范围比较ZCP,双区域范围比较ZCPL17指令助记符传送MOV,双字长传送MOVL,传送非MVN,传送位MOVB,数字传送MOVD多位传送XFRB,块传送XFER,块置位BSET,数据互换XCHG,单字分派DIST数据搜集COLL6。

Verilog复习题

Verilog 复习题一、填空题1.用EDA技术进行电子系统设计的目标是最终完成ASIC的设计与实现。

2.可编程器件分为CPLD和FPGA。

3.随着EDA技术的不断完善与成熟,自顶向下的设计方法更多的被应用于Verilog HDL设计当中。

4.目前国际上较大的PLD器件制造公司有ALtera和Xilinx公司。

5.完整的条件语句将产生组合电路,不完整的条件语句将产生时序电路。

6.阻塞性赋值符号为,非阻塞性赋值符号为<=_。

7.有限状态机分为Moore和Mealy两种类型。

8.EDA缩写的含义为电子设计自动化(Electronic Design Automation) |9.状态机常用状态编码有二进制、格雷码和独热码。

10.Verilog HDL中任务可以调用其他任务和函数。

11.系统函数和任务函数的首字符标志为_$_,预编译指令首字符标志为。

12 .可编程逻辑器件的优化过程主要是对速度和资源的处理过程。

13、大型数字逻辑电路设计采用的IP核有软IP、固IP和硬IP。

二、选择题1、已知“a =1b' 1; b=3b'001; ”那么{a,b} =( C )(A) 4b'0011 (B) 3b'001 (C) 4b'1001 (D) 3b'1012、在verilog中,下列语句哪个不是分支语句? ( D )(A) if-else (B) case (C) casez (D) repeat3、V erilog HDL语言进行电路设计方法有哪几种( 8分)①自上而下的设计方法(Top-Down )②自下而上的设计方法(Bottom-Up )③综合设计的方法4、在verilog 语言中,a=4b'1011,那么&a= (D )(A) 4b'1011 (B) 4b'1111 (C) 1b'1 (D) 1b'05、在verilog语言中整型数据与(C )位寄存器数据在实际意义上是相同的。

4位全加器实验报告

4位全加器实验报告篇一:四位全加器实验报告实验一:四位全加器实验报告实验日期:学生姓名:陆小辉(学号:25)指导老师:黄秋萍加法器是数字系统中的基本逻辑器件,是构成算数运算电路的基本单元。

1位加法器有全加器和半加器两种。

多位加法器构成方式有并行进位方式和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运算速度较快;串行进位加法器是将全加器级联构成多位加法器。

并行进位加法器通常比串行进位加法器占用更多的资源,随着位数的增多,相同位数的并行进位加法器比串行进位加法器的资源占用差距快速增大。

因此,在工程中使用加法器时,要在速度与容量之间寻求平衡。

一、设计要求:设计四位全加器,完成相应的功能。

可采用并行进位方式和串行进位方式,可采用三种常用建模方式中的任意一种。

三、测试代码如(转载自:小草范文网:4位全加器实验报告)下: module text_fulladd4; 二、设计代码如下:(此处采用数据流建模)wire [3:0]sum; module fulladd4(sum,cout,a,b,cin); wire cout; output [3:0]sum; reg [3:0]a,b; output cout; reg cin; input [3:0]a,b; fulladd4 f1(sum,cout,a,b,cin);input cin; initial assign {cout,sum}=a+b+cin; begin endmodule a=4'b0; b=4'b0; cin=1'b0; #210 $stop; end always #10 a=a+1; always #5 b=b+1; always #100 cin=cin+1;endmodule 四、仿真波形如下:续图篇二:4位全加器实验报告数电第一次实验通信1402 程杰 UXX13468【实验目的】采用ISE集成开发环境,利用verilog硬件描述语言中行为描述模式、结构描述模式或数据流描述模式设计四进制全加器。

74ls系列芯片功能和参数详细介绍

74ls系列芯⽚功能和参数详细介绍74、74HC、74LS系列芯⽚资料系列电平典型传输延迟ns 最⼤驱动电流(-Ioh/Lol)mAAHC CMOS 8.5 -8/8AHCT COMS/TTL 8.5 -8/8HC COMS 25 -8/8HCT COMS/TTL 25 -8/8ACT COMS/TTL 10 -24/24F TTL 6.5 -15/64ALS TTL 10 -15/64LS TTL 18 -15/24注:同型号的74系列、74HC系列、74LS系列芯⽚,逻辑功能上是⼀样的。

74LSxx的使⽤说明如果找不到的话,可参阅74xx 或74HCxx的使⽤说明。

有些资料⾥包含了⼏种芯⽚,如74HC161资料⾥包含了74HC160、74HC161、74HC162、74HC163四种芯⽚的资料。

找不到某种芯⽚的资料时,可试着查看⼀下临近型号的芯⽚资料。

7400 QUAD 2-INPUT NAND GATES 与⾮门7401 QUAD 2-INPUT NAND GATES OC 与⾮门7402 QUAD 2-INPUT NOR GATES 或⾮门7403 QUAD 2-INPUT NAND GATES 与⾮门7404 HEX INVERTING GATES 反向器7406 HEX INVERTING GATES HV ⾼输出反向器7408 QUAD 2-INPUT AND GATE 与门7409 QUAD 2-INPUT AND GATES OC 与门7410 TRIPLE 3-INPUT NAND GATES 与⾮门7411 TRIPLE 3-INPUT AND GATES 与门74121 ONE-SHOT WITH CLEAR 单稳态74132 SCHMITT TRIGGER NAND GATES 触发器与⾮门7414 SCHMITT TRIGGER INVERTERS 触发器反向器74153 4-LINE TO 1 LINE SELECTOR 四选⼀74155 2-LINE TO 4-LINE DECODER 译码器74180 PARITY GENERATOR/CHECKER 奇偶发⽣检验74191 4-BIT BINARY COUNTER UP/DOWN 计数器7420 DUAL 4-INPUT NAND GATES 双四输⼊与⾮门7426 QUAD 2-INPUT NAND GATES 与⾮门7427 TRIPLE 3-INPUT NOR GATES 三输⼊或⾮门7430 8-INPUT NAND GATES ⼋输⼊端与⾮门7432 QUAD 2-INPUT OR GATES ⼆输⼊或门7438 2-INPUT NAND GATE BUFFER 与⾮门缓冲器7445 BCD-DECIMAL DECODER/DRIVER BCD译码驱动器7474 D-TYPE FLIP-FLOP D型触发器7475 QUAD LATCHES 双锁存器7476 J-K FLIP-FLOP J-K触发器7485 4-BIT MAGNITUDE COMPARATOR 四位⽐较器7486 2-INPUT EXCLUSIVE OR GATES 双端异或门74HC00 QUAD 2-INPUT NAND GATES 双输⼊与⾮门74HC02 QUAD 2-INPUT NOR GATES 双输⼊或⾮门74HC03 2-INPUT OPEN-DRAIN NAND GATES 与⾮门74HC04 HEX INVERTERS 六路反向器74HC05 HEX INVERTERS OPEN DRAIN 六路反向器74HC08 2-INPUT AND GATES 双输⼊与门74HC107 J-K FLIP-FLOP WITH CLEAR J-K触发器74HC109A J-K FLIP-FLOP W/PRESET J-K触发器74HC11 TRIPLE 3-INPUT AND GATES 三输⼊与门74HC112 DUAL J-K FLIP-FLOP 双J-K触发器74HC113 DUAL J-K FLIP-FLOP PRESET 双JK触发器74HC123A RETRIGGERABLE MONOSTAB 可重触发单稳74HC125 TRI-STATE QUAD BUFFERS 四个三态门74HC126 TRI-STATE QUAD BUFFERS 六三态门74HC132 2-INPUT TRIGGER NAND 施密特触发与⾮门74HC133 13-INPUT NANDGATES ⼗三输⼊与⾮门74HC137 3-TO-8 DECODERS W/LATCHES 3-8线译码器74HC138 3-8 LINE DECODER 3线⾄8线译码器74HC139 2-4 LINE DECODER 2线⾄4线译码器74HC14 TRIGGERED HEX INVERTER 六触发反向器74HC147 10-4 LINE PRIORITY ENCODER 10-4编码器74HC148 8-3 LINE PRIORITY ENCODER 8-3编码器74HC149 8-8 LINE PRIORITY ENCODER 8-8编码器74HC151 8-CHANNEL DIGITAL MUX 8通道多路器74HC153 DUAL 4-INPUT MUX 双四输⼊多路器74HC154 4-16 LINE DECODER 4线⾄16线译码器74HC155 2-4 LINE DECODER 2线⾄4线译码器74HC157 QUAD 2-INPUT MUX 四个双端多路器74HC161 BINARY COUNTER ⼆进制计数器74HC163 DECADE COUNTERS ⼗进制计数器74HC164 SERIAL-PARALLEL SHIFT REG 串⼊并出74HC165 PARALLEL-SERIAL SHIFT REG 并⼊串出74HC166 SERIAL-PARALLEL SHIFT REG 串⼊并出74HC173 TRI-STATE D FLIP-FLOP 三态D触发器74HC174 HEX D FLIP-FLOP W/CLEAR 六D触发器74HC175 HEX D FLIP-FLOP W/CLEAR 六D触发器74HC181 ARITHMETIC LOGIC UNIT 算术逻辑单元74HC182 LOOK AHEAD CARRYGENERATR 进位发⽣器74HC190 BINARY UP/DN COUNTER ⼆进制加减计数器74HC191 DECADE UP/DN COUNTER ⼗进制加减计数器74HC192 DECADE UP/DN COUNTER ⼗进制加减计数器74HC193 BINARY UP/DN COUNTER ⼆进制加减计数器74HC194 4BIT BI-DIR SHIFT 4位双向移位寄存器74HC195 4BIT PARALLEL SHIFT 4位并⾏移位寄存器74HC20 QUAD 4-INPUT NAND GATE 四个四⼊与⾮门74HC221A NON-RETRIG MONOSTAB 不可重触发单稳74HC237 3-8 LINE DECODER 地址锁3线⾄8线译码器74HC242/243 TRI-STAT TRANSCEIVER 三态收发器74HC244 OCTAL 3-STATE BUFFER ⼋个三态缓冲门74HC245 OCTAL 3-STATE TRANSCEIVER 三态收发器74HC251 8-CH 3-STATE MUX 8路3态多路器74HC253 DUAL 4-CH 3-STATE MUX 4路3态多路器74HC257 QUAD 2-CH 3-STATE MUX 4路3态多路器74HC258 2-CH 3-STATE MUX 2路3态多路器74HC259 3-8 LINE DECODER 8位地址锁存译码器74HC266A 2-INPUT EXCLUSIVE NOR GATE 异或⾮74HC27 TRIPLE 3-INPUT NOR GATE三个3输⼊或⾮门74HC273 OCTAL D FLIP-FLOP CLEAR 8路D触发器74HC280 9BIT ODD/EVEN GENERATOR 奇偶发⽣器74HC283 4BIT BINARY ADDER CARRY 四位加法器74HC299 3-STATE UNIVERSAL SHIFT 三态移位寄存74HC30 8-INPUT NAND GATE 8输⼊端与⾮门74HC32 QUAD 2-INPUT OR GATE 四个双端或门74HC34 NON-INVERTER ⾮反向器74HC354 8-CH 3-STATE MUX 8路3态多路器74HC356 8-CH 3-STATE MUX 8路3态多路器74HC365 HEX 3-STATE BUFFER 六个三态缓冲门74HC366 3-STATE BUFFER INVERTER 缓冲反向器74HC367 3-STATE BUFFER INVERTER 缓冲反向器74HC368 3-STATE BUFFER INVERTER 缓冲反向器74HC373 3-STATE OCTAL D LATCHES 三态D型锁存器74HC374 3-STATE OCTAL D FLIPFLOP 三态D触发器74HC393 4-BIT BINARY COUNTER 4位⼆进制计数器74HC4016 QUAD ANALOG SWITCH 四路模拟量开关74HC4020 14-Stage Binary Counter 14输出计数器74HC4017 Decade Counter/Divider with 10 Decoded Outputs ⼗进制计数器带10个译码输出端74HC4040 12 Stage Binary Counter 12出计数器74HC4046 PHASE LOCK LOOP 相位监测输出器74HC4049 LEVEL DOWN CONVERTER 电平变低器74HC4050 LEVEL DOWN CONVERTER 电平变低器74HC4051 8-CH ANALOG MUX 8通道多路器74HC4052 4-CH ANALOG MUX 4通道多路器74HC4053 2-CH ANALOG MUX 2通道多路器74HC4060 14-STAGE BINARY COUNTER 14阶BIN计数74HC4066 QUAD ANALOG MUX 四通道多路器74HC4075 TRIPLE 3-INPUT OR GATE 3输⼊或门74HC42 BCD TO DECIMAL BCD转⼗进制译码器74HC423A RETRIGGERABLE MONOSTAB 可重触发单稳74HC4511 BCD-7 SEG DRIVER/DECODER 7段译码器74HC4514 4-16 LINE DECODER 4⾄16线译码器74HC4538A RETRIGGERAB MONOSTAB 可重触发单稳74HC4543 LCD BCD-7 SEG LCD⽤的BCD-7段译码驱动74HC51 AND OR GATE INVERTER 与或⾮门74HC521 8BIT MAGNITUDE COMPARATOR 判决定路74HC533 3-STATE D LATCH 三态D锁存器74HC534 3-STATE D FLIP-FLOP 三态D型触发器74HC540 3-STATE BUFFER 三态缓冲器74HC541 3-STATE BUFFER INVERTER三态缓冲反向器74HC58 DUAL AND OR GATE 与或门74HC589 3STATE 8BIT SHIFT 8位移位寄存三态输出74HC594 8BIT SHIFT REG 8位移位寄存器74HC595 8BIT SHIFT REG 8位移位寄存器出锁存74HC597 8BIT SHIFT REG 8位移位寄存器⼊锁存74HC620 3-STATE TRANSCEIVER 反向3态收发器74HC623 3-STATE TRANSCEIVER ⼋路三态收发器74HC640 3-STATE TRANSCEIVER 反向3态收发器74HC643 3-STATE TRANSCEIVER ⼋路三态收发器74HC646 NON-INVERT BUS TRANSCEIVER 总线收发器74HC648 INVERT BUS TRANCIVER 反向总线收发器74HC688 8BIT MAGNITUDE COMPARATOR 8位判决电路74HC7266 2-INPUT EXCLUSIVE NOR GATE 异或⾮门74HC73 DUAL J-K FLIP-FLOP W/CLEAR 双JK触发器74HC74A PRESET/CLEAR D FLIP-FLOP 双D触发器74HC75 4BIT BISTABLE LATCH 4位双稳锁存器74HC76 PRESET/CLEAR JK FLIP-FLOP 双JK触发器74HC85 4BIT MAGNITUDE COMPARATOR 4位判决电路74HC86 2INPUT EXCLUSIVE OR GATE 2输⼊异或门74HC942 BAUD MODEM 300BPS低速调制解调器74HC943 300 BAUD MODEM 300BPS低速调制解调器74LS00 QUAD 2-INPUT NAND GATES 与⾮门74LS02 QUAD 2-INPUT NOR GATES 或⾮门74LS03 QUAD 2-INPUT NAND GATES 与⾮门74LS04 HEX INVERTING GATES 反向器74LS05 HEX INVERTERS OPEN DRAIN 六路反向器74LS08 QUAD 2-INPUT AND GATE 与门74LS09 QUAD 2-INPUT AND GATES OC 与门74LS10 TRIPLE 3-INPUT NAND GATES 与⾮门74LS109 QUAD 2-INPUT AND GATES OC 与门74LS11 TRIPLE 3-INPUT AND GATES 与门74LS112 DUAL J-K FLIP-FLOP 双J-K触发器74LS113 DUAL J-K FLIP-FLOP PRESET 双JK触发器74LS114 NEGATIVE J-K FLIP-FLOP 负沿J-K触发器74LS122 Retriggerable Monostab 可重触发单稳74LS123 Retriggerable Monostable 可重触发单稳74LS125 TRI-STATE QUAD BUFFERS 四个三态门74LS13 QUAL 4-in NAND TRIGGER 4输⼊与⾮触发器74LS160 BCD DECADE 4BIT BIN COUNTERS 计数器74LS136 QUADRUPLE 2-INPUT XOR GATE 异或门74LS138 3-8 LINE DECODER 3线⾄8线译码器74LS139 2-4 LINE DECODER 2线⾄4线译码器74LS14 TRIGGERED HEX INVERTER 六触发反向器74HC147 10-4 LINE PRIORITY ENCODER 10-4编码器74HC148 8-3 LINE PRIORITY ENCODER 8-3编码器74HC149 8-8 LINE PRIORITY ENCODER 8-8编码器74LS151 8-CHANNEL DIGITAL MUX 8通道多路器74LS153 DUAL 4-INPUT MUX 双四输⼊多路器74LS155 2-4 LINE DECODER 2线⾄4线译码器74LS156 2-4 LINE DECODER/DEMUX 2-4译码器74LS157 QUAD 2-INPUT MUX 四个双端多路器74LS158 2-1 LINE MUX 2-1线多路器74LS160A BINARY COUNTER ⼆进制计数器74LS161A BINARY COUNTER ⼆进制计数器74LS162A BINARY COUNTER ⼆进制计数器74LS163A DECADE COUNTERS ⼗进制计数器74LS164 SERIAL-PARALLEL SHIFT REG 串⼊并出74LS168 BI-DIRECT BCD TO DECADE 双向计数器74LS1694BIT UP/DN BIN COUNTER 四位加减计数器74LS173 TRI-STATE D FLIP-FLOP 三态D触发器74LS174 HEX D FLIP-FLOP W/CLEAR 六D触发器74LS175 HEX D FLIP-FLOP W/CLEAR 六D触发器74LS190 BINARY UP/DN COUNTER ⼆进制加减计数器74LS191 DECADE UP/DN COUNTER ⼗进制加减计数器74LS192 DECADE UP/DN COUNTER ⼗进制加减计数器74LS193BINARY UP/DN COUNTER ⼆进制加减计数器74LS194A 4BIT BI-DIR SHIFT 4位双向移位寄存器74LS195A 4BIT PARALLEL SHIFT4位并⾏移位寄存器74LS20 QUAD 4-INPUT NAND GATE 四个四⼊与⾮门74LS21 4-INPUT AND GATE 四输⼊端与门74LS240 OCTAL 3-STATE BUFFER ⼋个三态缓冲门74LS244 OCTAL 3-STATE BUFFER ⼋个三态缓冲门74LS245 OCTAL 3-STATE TRANSCEIVER 三态收发器74LS253 DUAL 4-CH 3-STATE MUX 4路3态多路器74LS256 4BIT ADDRESS LATCH 四位可锁存锁存器74LS257 QUAD 2-CH 3-STATE MUX 4路3态多路器74LS258 2-CH 3-STATE MUX 2路3态多路器74LS27 TRIPLE 3-INPUT NOR GATES 三输⼊或⾮门74LS279 QUAD R-S LATCHES 四个RS⾮锁存器74LS28 QUAD 2-INPUT NOR BUFFER 四双端或⾮缓冲74LS283 4BIT BINARY ADDER CARRY 四位加法器74LS30 8-INPUT NAND GATES ⼋输⼊端与⾮门74LS32 QUAD 2-INPUT OR GATES ⼆输⼊或门74LS352 4-1 LINE SELECTOR/MUX 4-1线选择多路器74LS365 HEX 3-STATE BUFFER 六个三态缓冲门74LS367 3-STATE BUFFER INVERTER 缓冲反向器74LS368A 3-STATE BUFFER INVERTER 缓冲反向器74LS373 OCT LATCH W/3-STATE OUT三态输出锁存器74LS76 Dual JK Flip-Flop w/set 2个JK触发器74LS379 QUAD PARALLEL REG 四个并⾏寄存器74LS38 2-INPUT NAND GATE BUFFER 与⾮门缓冲器74LS390 DUAL DECADE COUNTER 2个10进制计数器74LS393 DUAL BINARY COUNTER 2个2进制计数器74LS42 BCD TO DECIMAL BCD转⼗进制译码器74LS48 BCD-7 SEG BCD-7段译码器74LS49 BCD-7 SEG BCD-7段译码器74LS51 AND OR GATE INVERTER 与或⾮门74LS540 OCT Buffer/Line Driver 8路缓冲驱动器74LS541 OCT Buffer/LineDriver 8路缓冲驱动器74LS74 D-TYPE FLIP-FLOP D型触发器74LS682 8BIT MAGNITUDE COMPARATOR 8路⽐较器74LS684 8BIT MAGNITUDE COMPARATOR 8路⽐较器74LS75 QUAD LATCHES 双锁存器74LS83A 4BIT BINARY ADDER CARRY 四位加法器74LS85 4BIT MAGNITUDE COMPARAT 4位判决电路74LS86 2INPUT EXCLUSIVE OR GATE 2输⼊异或门74LS90 DECADE/BINARY COUNTER ⼗/⼆进制计数器74LS95B4BIT RIGHT/LEFT SHIFT 4位左右移位寄存74LS688 8BIT MAGNITUDE COMPARAT 8位判决电路74LS136 2-INPUT XOR GATE 2输⼊异或门74LS651 BUS TRANSCEIVERS 总线收发器74LS653 BUS TRANSCEIVERS 总线收发器74LS670 3-STATE 4-BY-4 REG 3态4-4寄存器74LS73A DUAL J-K FLIP-FLOP W/CLEAR 双JK触发器。

数字电路考研试题及答案

数字电路考研试题及答案一、单项选择题(每题2分,共10分)1. 在数字电路中,最基本的逻辑关系不包括以下哪一项?A. 与(AND)B. 或(OR)C. 非(NOT)D. 异或(XOR)答案:D2. 触发器的类型中,不包含以下哪一种?A. RS触发器B. JK触发器C. D触发器D. T触发器答案:D3. 在以下哪种情况下,一个逻辑表达式的结果不会改变?A. 输入信号增加B. 输入信号减少C. 输入信号保持不变D. 输入信号随机变化答案:C4. 一个4位二进制计数器在计数过程中,其状态变化的总数是多少?A. 8B. 16C. 32D. 64答案:B5. 在CMOS技术中,一个N型MOSFET在其栅极施加()时导通。

A. 正电压B. 负电压C. 零电压D. 任意电压答案:A二、填空题(每题3分,共15分)6. 在数字电路中,一个逻辑门的延迟时间是指从输入信号变化到输出信号变化所经历的________。

答案:最小时间7. 一个3-8线译码器可以将3位二进制信号转换为________个互斥的输出信号。

答案:88. 一个完整的数字电路系统通常包括组合逻辑电路和________。

答案:时序逻辑电路9. 在数字电路设计中,竞争和________是两种常见的不希望出现的现象。

答案:冒险10. 一个D触发器在时钟信号上升沿到来时,其输出将________输入端D的逻辑状态。

答案:复制三、简答题(每题10分,共20分)11. 什么是同步时序电路和异步时序电路?它们各自的特点是什么?答案:同步时序电路是指电路中的所有触发器都由同一个时钟信号控制,状态的改变完全依赖于这个时钟信号。

同步时序电路的特点是电路结构简单,便于设计和分析,但可能存在较大的时钟 skew 和传播延迟。

异步时序电路(也称为无钟电路)不依赖于统一的时钟信号,而是通过信号之间的因果关系来驱动状态的改变。

异步时序电路的特点是设计复杂,但可以减少时钟信号的延迟影响,提高电路的响应速度。

protues基本元件和简称

protue s元件库中英文对照表,对初学者找不到元件的很有用元件名称中文名说明7407 驱动门1N914 二极管74Ls00 与非门74LS04 非门74LS08 与门74LS390 TT L 双十进制计数器7SE G 4针BCD-LED 输出从0-9对应于4根线的BC D码7SEG3-8译码器电路BCD-7SEG转换电路ALTER NATOR交流发电机AMMET ER-MI LLI mA安培计AN D 与门B ATTER Y 电池/电池组BUS总线CA P 电容C APACI TOR 电容器CLOC K 时钟信号源CRY STAL晶振D-FL IPFLO P D触发器FUSE保险丝GR OUND地LAMP灯LED-RED红色发光二极管LM016L 2行16列液晶可显示2行16列英文字符,有8位数据总线D0-D7,R S,R/W,EN三个控制端口(共14线),工作电压为5V。

没背光,和常用的1602B功能和引脚一样(除了调背光的二个线脚)L OGICANALY SER 逻辑分析器LOG ICPRO BE 逻辑探针LOGI CPROB E[BIG] 逻辑探针用来显示连接位置的逻辑状态LO GICST ATE 逻辑状态用鼠标点击,可改变该方框连接位置的逻辑状态L OGICT OGGLE逻辑触发M ASTER SWITC H 按钮手动闭合,立即自动打开MOTOR马达OR或门PO T-LIN三引线可变电阻器PO WER 电源RES电阻RES ISTOR电阻器SW ITCH按钮手动按一下一个状态SWIT CH-SP DT 二选通一按钮VO LTMET ER 伏特计VOLTM ETER-MILLI mV伏特计V TERM串行口终端Elect romec hanic al 电机In ducto rs 变压器Lapla ce Pr imiti ves 拉普拉斯变换Me moryIcs Mi cropr ocess or Ic s Misc ellan eous各种器件AERIA L-天线;ATAH DD;AT MEGA64;BA TTERY;CELL;CRY STAL-晶振;F USE;M ETER-仪表;Mode lling Prim itive s 各种仿真器件是典型的基本元器模拟,不表示具体型号,只用于仿真,没有PCBOpt oelec troni cs 各种发光器件发光二极管,LED,液晶等等PLD s & F PGAsR esist ors 各种电阻Sim ulato r Pri mitiv es 常用的器件Spea kers& Sou ndersSw itche s & R elays开关,继电器,键盘Sw itchi ng De vices晶阊管Tra nsist ors 晶体管(三极管,场效应管)TTL 74 ser ies TT L 74A LS se riesT TL 74AS se riesT TL 74F ser ies TT L 74H C ser ies TT L 74H CT se riesT TL 74LS se riesT TL 74S ser ies An alogIcs 模拟电路集成芯片Capac itors电容集合CM OS 4000 se riesC onnec tors排座,排插Da ta Co nvert ers A DC,DA CD ebugg ing T ools调试工具ECL 10000 Ser ies 各种常用集成电路protu es常用器件2007-08-08 14:18分分立元件库元件名称及中英对照A ND 与门ANT ENNA天线B ATTER Y 直流电源BE LL 铃,钟BV C 同轴电缆接插件BRID EG 1整流桥(二极管) BRIDE G 2 整流桥(集成块)B UFFER缓冲器BUZZ ER 蜂鸣器CA P 电容CAPA CITOR电容CAPAC ITORPOL 有极性电容CAPV AR 可调电容C IRCUI T BRE AKER熔断丝COAX同轴电缆CON插口C RYSTA L 晶体整荡器D B 并行插口DI ODE 二极管D IODESCHOT TKY 稳压二极管DIOD E VAR ACTOR变容二极管DP Y_3-S EG 3段LED DPY_7-SEG7段LEDDPY_7-SE G_DP7段LED(带小数点) EL ECTRO电解电容FUS E 熔断器IND UCTOR电感INDUC TOR I RON 带铁芯电感INDU CTOR3可调电感JFE T N N沟道场效应管JF ET PP沟道场效应管L AMP 灯泡LA MP NE DN 起辉器LE D 发光二极管M ETER仪表M ICROP HONE麦克风MOSFE T MOS管MO TOR A C 交流电机MO TOR S ERVO伺服电机NAND与非门NOR或非门NOT 非门NP N NPN三极管NPN-P HOTO感光三极管OPA MP 运放OR或门P HOTO感光二极管PNP三极管NPNDAR N PN三极管PNP DARPNP三极管PO T 滑线变阻器P ELAY-DPDT双刀双掷继电器R ES1.2电阻RES3.4 可变电阻RE SISTO R BRI DGE ?桥式电阻RES PACK? 电阻SCR晶闸管PLUG? 插头PLUG AC F EMALE三相交流插头S OCKET ? 插座SOU RCE C URREN T 电流源SOU RCE V OLTAG E 电压源SPE AKER扬声器SW ?开关S W-DPD Y ? 双刀双掷开关SW-SPST? 单刀单掷开关SW-PB按钮THERM ISTOR电热调节器TR ANS1变压器TRANS2 可调变压器T RIAC? 三端双向可控硅TRIO DE ?三极真空管VAR ISTOR变阻器ZENE R ? 齐纳二极管DPY_7-SEG_DP 数码管S W-PB开关原理图常用库文件:Misce llane ous D evice s.ddbDal las M icrop roces sor.d dbI ntelDatab ooks.ddb Prote l DOS Sche matic Libr aries.ddbPCB元件常用库:Adv pcb.d dbG enera l IC.ddb Misce llane ous.d db部分分立元件库元件名称及中英对照A ND 与门ANT ENNA天线B ATTER Y 直流电源BE LL 铃,钟BV C 同轴电缆接插件BRID EG 1整流桥(二极管) BRIDE G 2 整流桥(集成块)B UFFER缓冲器BUZZ ER 蜂鸣器CA P 电容CAPA CITOR电容CAPAC ITORPOL 有极性电容CAPV AR 可调电容C IRCUI T BRE AKER熔断丝COAX同轴电缆CON插口C RYSTA L 晶体整荡器D B 并行插口DI ODE 二极管D IODESCHOT TKY 稳压二极管DIOD E VAR ACTOR变容二极管DP Y_3-S EG 3段LED DPY_7-SEG7段LEDDPY_7-SE G_DP7段LED(带小数点) EL ECTRO电解电容FUS E 熔断器IND UCTOR电感INDUC TOR I RON 带铁芯电感INDU CTOR3可调电感JFE T N N沟道场效应管JF ET PP沟道场效应管L AMP 灯泡LA MP NE DN 起辉器LE D 发光二极管M ETER仪表M ICROP HONE麦克风MOSFE T MOS管MO TOR A C 交流电机MO TOR S ERVO伺服电机NAND与非门NOR或非门NOT 非门NP N NPN三极管NPN-P HOTO感光三极管OPA MP 运放OR或门P HOTO感光二极管PNP三极管NPNDAR N PN三极管PNP DARPNP三极管PO T 滑线变阻器P ELAY-DPDT双刀双掷继电器R ES1.2电阻RES3.4 可变电阻RE SISTO R BRI DGE ?桥式电阻RES PACK? 电阻SCR晶闸管PLUG? 插头PLUG AC F EMALE三相交流插头S OCKET ? 插座SOU RCE C URREN T 电流源SOU RCE V OLTAG E 电压源SPE AKER扬声器SW ?开关S W-DPD Y ? 双刀双掷开关SW-SPST? 单刀单掷开关SW-PB按钮THERM ISTOR电热调节器TR ANS1变压器TRANS2 可调变压器T RIAC? 三端双向可控硅TRIO DE ?三极真空管VAR ISTOR变阻器ZENE R ? 齐纳二极管DPY_7-SEG_DP 数码管S W-PB开关74系列:74LS00 TTL 2输入端四与非门74LS01 TTL集电极开路2输入端四与非门74LS02 TTL 2输入端四或非门74LS03 TTL集电极开路2输入端四与非门74LS122 TT L 可再触发单稳态多谐振荡器74LS123 TT L 双可再触发单稳态多谐振荡器74LS125 T TL 三态输出高有效四总线缓冲门74L S126TTL 三态输出低有效四总线缓冲门74LS13TTL 4输入端双与非施密特触发器74LS132 TTL2输入端四与非施密特触发器74LS133 TTL 13输入端与非门74LS136 TT L 四异或门74L S138TTL 3-8线译码器/复工器74LS139 T TL 双2-4线译码器/复工器74LS14 TT L 六反相施密特触发器74L S145TTL B CD—十进制译码/驱动器74LS15TTL 开路输出3输入端三与门74LS150 T TL 16选1数据选择/多路开关74L S151TTL 8选1数据选择器74LS153 TTL双4选1数据选择器74LS154 TT L 4线—16线译码器74L S155TTL 图腾柱输出译码器/分配器74L S156TTL 开路输出译码器/分配器74LS157 T TL 同相输出四2选1数据选择器74L S158TTL 反相输出四2选1数据选择器74LS16TTL 开路输出六反相缓冲/驱动器74LS160 TTL可预置BC D异步清除计数器74LS161 TTL可予制四位二进制异步清除计数器74L S162TTL 可预置BCD同步清除计数器74LS163 TTL可予制四位二进制同步清除计数器74LS164 T TL 八位串行入/并行输出移位寄存器74LS165 TTL八位并行入/串行输出移位寄存器74L S166TTL 八位并入/串出移位寄存器74L S169TTL 二进制四位加/减同步计数器74LS17TTL 开路输出六同相缓冲/驱动器74LS170 TTL开路输出4×4寄存器堆74L S173TTL 三态输出四位D型寄存器74LS174 T TL 带公共时钟和复位六D触发器74L S175TTL 带公共时钟和复位四D触发器74LS180 TTL9位奇数/偶数发生器/校验器74LS181 TT L 算术逻辑单元/函数发生器74LS185 TT L 二进制—BCD代码转换器74LS190 TT L BCD同步加/减计数器74LS191 TTL二进制同步可逆计数器74L S192TTL 可预置BCD双时钟可逆计数器74LS193 TTL可预置四位二进制双时钟可逆计数器74LS194 TTL四位双向通用移位寄存器74L S195TTL 四位并行通道移位寄存器74LS196 T TL 十进制/二-十进制可预置计数锁存器74LS197 T TL 二进制可预置锁存器/计数器74L S20 T TL 4输入端双与非门74L S21 T TL 4输入端双与门74LS22 TT L 开路输出4输入端双与非门74LS221 TT L 双/单稳态多谐振荡器74LS240 TTL八反相三态缓冲器/线驱动器74LS241 TTL八同相三态缓冲器/线驱动器74LS243 TT L 四同相三态总线收发器74LS244 TTL八同相三态缓冲器/线驱动器74LS245 TTL八同相三态总线收发器74L S247TTL B CD—7段15V输出译码/驱动器74L S248TTL B CD—7段译码/升压输出驱动器74LS249 T TL BC D—7段译码/开路输出驱动器74LS251 TT L 三态输出8选1数据选择器/复工器74LS253 TTL三态输出双4选1数据选择器/复工器74LS256 TTL双四位可寻址锁存器74LS257 T TL 三态原码四2选1数据选择器/复工器74LS258 T TL 三态反码四2选1数据选择器/复工器74LS259 T TL 八位可寻址锁存器/3-8线译码器74LS26 TTL 2输入端高压接口四与非门74LS260 TTL 5输入端双或非门74LS266 TT L 2输入端四异或非门74L S27 T TL 3输入端三或非门74L S273TTL 带公共时钟复位八D触发器74L S279TTL 四图腾柱输出S-R锁存器74L S28 T TL 2输入端四或非门缓冲器74LS283 TT L 4位二进制全加器74LS290 T TL 二/五分频十进制计数器74LS293 TT L 二/八分频四位二进制计数器74LS295 T TL 四位双向通用移位寄存器74LS298 TT L 四2输入多路带存贮开关74LS299 TTL三态输出八位通用移位寄存器74LS30 TTL 8输入端与非门74LS32 TTL2输入端四或门74LS322 TTL带符号扩展端八位移位寄存器74LS323 TTL三态输出八位双向移位/存贮寄存器74LS33TTL 开路输出2输入端四或非缓冲器74LS347 TTL BCD—7段译码器/驱动器74LS352 TT L 双4选1数据选择器/复工器74LS353 T TL 三态输出双4选1数据选择器/复工器74LS365 T TL 门使能输入三态输出六同相线驱动器74LS365 TT L 门使能输入三态输出六同相线驱动器74LS366 TTL门使能输入三态输出六反相线驱动器74LS367 TTL4/2线使能输入三态六同相线驱动器74LS368 TTL4/2线使能输入三态六反相线驱动器74LS37TTL 开路输出2输入端四与非缓冲器74LS373 TTL三态同相八D锁存器74LS374 T TL 三态反相八D锁存器74LS375 TTL4位双稳态锁存器74LS377 TTL单边输出公共使能八D锁存器74LS378 TT L 单边输出公共使能六D锁存器74LS379 T TL 双边输出公共使能四D锁存器74L S38 T TL 开路输出2输入端四与非缓冲器74LS380 TTL多功能八进制寄存器74LS39 TTL开路输出2输入端四与非缓冲器74LS390 T TL 双十进制计数器74LS393 T TL 双四位二进制计数器74LS40TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS352 TTL双4选1数据选择器/复工器74LS353 TT L 三态输出双4选1数据选择器/复工器74LS365 TT L 门使能输入三态输出六同相线驱动器74LS366 TTL门使能输入三态输出六反相线驱动器74LS367 TTL4/2线使能输入三态六同相线驱动器74LS368 TTL4/2线使能输入三态六反相线驱动器74LS37TTL 开路输出2输入端四与非缓冲器74LS373 TTL三态同相八D锁存器74LS374 T TL 三态反相八D锁存器74LS375 TTL4位双稳态锁存器74LS377 TTL单边输出公共使能八D锁存器74LS378 TT L 单边输出公共使能六D锁存器74LS379 T TL 双边输出公共使能四D锁存器74L S38 T TL 开路输出2输入端四与非缓冲器74LS380 TTL多功能八进制寄存器74LS39 TTL开路输出2输入端四与非缓冲器74LS390 T TL 双十进制计数器74LS393 T TL 双四位二进制计数器74LS40TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS447 TTL BCD—7段译码器/驱动器74LS45 TTL BCD—十进制代码转换/驱动器74L S450TTL 16:1多路转接复用器多工器74LS451 TTL双8:1多路转接复用器多工器74LS453 T TL 四4:1多路转接复用器多工器74LS46TTL B CD—7段低有效译码/驱动器74LS460 TT L 十位比较器74LS461 TTL八进制计数器74L S465TTL 三态同相2与使能端八总线缓冲器74LS466 TT L 三态反相2与使能八总线缓冲器74L S467TTL 三态同相2使能端八总线缓冲器74LS468 TTL三态反相2使能端八总线缓冲器74LS469 T TL 八位双向计数器74LS47 TT L BCD—7段高有效译码/驱动器74LS48TTL B CD—7段译码器/内部上拉输出驱动74LS490 TTL双十进制计数器74LS491 TTL十位计数器74LS498 T TL 八进制移位寄存器74L S50 T TL 2-3/2-2输入端双与或非门74LS502 TTL八位逐次逼近寄存器74LS503 T TL 八位逐次逼近寄存器74LS51TTL 2-3/2-2输入端双与或非门74LS533 TT L 三态反相八D锁存器74L S534TTL 三态反相八D锁存器74LS54 TTL四路输入与或非门74LS540 TTL八位三态反相输出总线缓冲器74LS55 TTL 4输入端二路输入与或非门74LS563 TTL八位三态反相输出触发器74LS564 TTL八位三态反相输出D触发器74LS573 TTL八位三态输出触发器74LS574 TT L 八位三态输出D触发器74LS645 TTL三态输出八同相总线传送接收器74LS670 T TL 三态输出4×4寄存器堆74LS73 TTL带清除负触发双J-K触发器74LS74 TTL带置位复位正触发双D触发器74LS76 TTL带预置清除双J-K触发器74LS83 TTL四位二进制快速进位全加器74LS85TTL 四位数字比较器74L S86 T TL 2输入端四异或门74L S90 T TL 可二/五分频十进制计数器74LS93 TT L 可二/八分频二进制计数器74LS95 TTL四位并行输入\\输出移位寄存器74L S97 T TL 6位同步二进制乘法器C D系列::CD4000 双3输入端或非门+单非门 TIC D4001四2输入端或非门HIT/N SC/TI/GOLCD4002 双4输入端或非门 NSCCD4006 18位串入/串出移位寄存器 NSCCD4007 双互补对加反相器 NSCCD4008 4位超前进位全加器 NSCCD4009 六反相缓冲/变换器 NS CCD4010 六同相缓冲/变换器N SCCD4011四2输入端与非门H IT/TICD4012 双4输入端与非门 NSCCD4013 双主-从D型触发器 FS C/NSC/TOSCD4014 8位串入/并入-串出移位寄存器 NS CCD4015 双4位串入/并出移位寄存器 TICD4016 四传输门 FS C/TICD4017 十进制计数/分配器 FSC/TI/M OTCD4018可预制1/N计数器NSC/M OTCD4019四与或选择器 PHICD4020 14级串行二进制计数/分频器 FS CCD4021 08位串入/并入-串出移位寄存器 PHI/NSC C D4022八进制计数/分配器 NSC/MOTC D4023三3输入端与非门NSC/M OT/TICD4024 7级二进制串行计数/分频器 NSC/MOT/TI CD4025三3输入端或非门N SC/MO T/TICD4026 十进制计数/7段译码器N SC/MO T/TICD4027 双J-K触发器NSC/M OT/TICD4028 BC D码十进制译码器N SC/MO T/TICD4029 可预置可逆计数器 NSC/MOT/T ICD4030 四异或门N SC/MO T/TI/GOLC D4031 64位串入/串出移位存储器NSC/M OT/TI CD4032 三串行加法器NSC/T ICD4033 十进制计数/7段译码器 NSC/TICD40348位通用总线寄存器NSC/M OT/TICD4035 4位并入/串入-并出/串出移位寄存 NSC/MOT/T I CD4038 三串行加法器 NSC/TICD404012级二进制串行计数/分频器NSC/M OT/TICD4041 四同相/反相缓冲器 NS C/MOT/TIC D4042四锁存D型触发器NSC/M OT/TICD4043 4三态R-S锁存触发器("1"触发) NSC/MOT/TI CD4044四三态R-S锁存触发器("0"触发) N SC/MO T/TICD4046 锁相环 NSC/MOT/T I/PHICD4047 无稳态/单稳态多谐振荡器 NSC/MOT/T ICD4048 4输入端可扩展多功能门 NSC/HIT/T ICD4049 六反相缓冲/变换器N SC/HI T/TICD4050 六同相缓冲/变换器 NSC/MOT/TICD4051八选一模拟开关 NS C/MOT/TIC D4052双4选1模拟开关NSC/M OT/TICD4053 三组二路模拟开关 NSC/MOT/TICD4054液晶显示驱动器 NS C/HIT/TIC D4055 BCD-7段译码/液晶驱动器 NSC/HIT/T ICD4056 液晶显示驱动器 NSC/HIT/TICD4059“N”分频计数器N SC/TICD4060 14级二进制串行计数/分频器 NS C/TI/MOTC D4063四位数字比较器N SC/HI T/TICD4066 四传输门 NSC/TI/M OTCD406716选1模拟开关N SC/TICD4068 八输入端与非门/与门N SC/HI T/TICD4069 六反相器 NSC/HIT/TICD4070四异或门NSC/H IT/TICD4071 四2输入端或门 NSC/TICD4072双4输入端或门 NS C/TICD4073 三3输入端与门NSC/T ICD4075 三3输入端或门 NSC/TIC D4076四D寄存器CD4077 四2输入端异或非门H ITCD40788输入端或非门/或门CD4081 四2输入端与门 NSC/HIT/T ICD4082 双4输入端与门 NSC/HIT/TICD4085双2路2输入端与或非门CD4086 四2输入端可扩展与或非门CD4089 二进制比例乘法器CD4093四2输入端施密特触发器 NSC/MOT/STCD40948位移位存储总线寄存器 NSC/TI/P HICD40953输入端J-K触发器CD4096 3输入端J-K触发器C D4097双路八选一模拟开关CD4098 双单稳态触发器 NSC/MOT/T ICD4099 8位可寻址锁存器 NS C/MOT/STC D40100 32位左/右移位寄存器C D40101 9位奇偶较验器CD40102 8位可预置同步BCD减法计数器C D40103 8位可预置同步二进制减法计数器CD40104 4位双向移位寄存器CD40105 先入先出FI-FD寄存器CD40106六施密特触发器 NS C\\TICD40107 双2输入端与非缓冲/驱动器 HA R\\TICD40108 4字×4位多通道寄存器CD40109 四低-高电平位移器CD4529双四路/单八路模拟开关CD4530 双5输入端优势逻辑门CD4531 12位奇偶校验器CD4532 8位优先编码器CD4536 可编程定时器CD4538 精密双单稳CD4539双四路数据选择器C D4541可编程序振荡/***CD4543 B CD七段锁存译码,驱动器CD4544BCD七段锁存译码,驱动器C D4547 BCD七段译码/大电流驱动器CD4549 函数近似寄存器CD4551 四2通道模拟开关CD4553 三位BCD计数器CD4555双二进制四选一译码器/分离器CD4556 双二进制四选一译码器/分离器CD4558 B CD八段译码器CD4560"N"BC D加法器CD4561 "9"求补器C D4573四可编程运算放大器CD4574 四可编程电压比较器CD4575双可编程运放/比较器CD4583 双施密特触发器CD4584 六施密特触发器CD4585 4位数值比较器CD4599 8位可寻址锁存器CD40110十进制加/减,计数,锁存,译码驱动 STCD40147 10-4线编码器 NS C\\MO TCD40160可预置BC D加计数器 NSC\\MOTCD40161 可预置4位二进制加计数器 NSC\\MOTCD40162 BC D加法计数器 NSC\\MOTCD40163 4位二进制同步计数器NSC\\MOTC D40174 六锁存D型触发器 NSC\\TI\\MOTC D40175 四D型触发器N SC\\T I\\MO TCD401814位算术逻辑单元/函数发生器CD40182 超前位发生器CD40192 可预置BCD加/减计数器(双时钟) NSC\\TIC D40193 可预置4位二进制加/减计数器 NSC\\TICD40194 4位并入/串入-并出/串出移位寄存 NSC\\MOTCD40195 4位并入/串入-并出/串出移位寄存 NSC\\MOTCD40208 4×4多端口寄存器型号器件名称厂牌备注CD4501 4输入端双与门及2输入端或非门CD4502 可选通三态输出六反相/缓冲器CD4503 六同相三态缓冲器CD4504六电压转换器CD4506 双二组2输入可扩展或非门CD4508 双4位锁存D型触发器CD4510 可预置BCD码加/减计数器CD4511 BC D锁存,7段译码,驱动器CD4512八路数据选择器CD4513BCD锁存,7段译码,驱动器(消隐)C D4514 4位锁存,4线-16线译码器CD4515 4位锁存,4线-16线译码器CD4516可预置4位二进制加/减计数器CD4517 双64位静态移位寄存器C D4518双BCD同步加计数器CD4519 四位与或选择器CD4520 双4位二进制同步加计数器CD4521 24级分频器CD4522 可预置BCD同步1/N计数器CD4526可预置4位二进制同步1/N计数器CD4527 B CD比例乘法器CD4528双单稳态触发器注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

四位二进制加法计数器课程设计

图3-6芯片型号选择

(5)点击Next,系统显示如图3-7,提示是否需要其他EDA工具,这里不选任何其他工具;

(6)点击Next后,系统提示创建工程的各属性总结,若没有错误,点击Finish,工程创建向导将生成一个工程,这时软件界面如图3-8,在窗口左侧显示出设备型号和该工程的基本信息等。

2.求时钟方程、状态方程

(1)求时钟方程

采用同步方案,故取CP0=CP1=CP2=CP3=CP

CP是整个要设计的时序电路的输入时钟脉冲

(2)求状态方程

由图2所示状态转换图可直接画出如图3-20所示的电路次Q3n+1Q2n+1Q1n+1Q0n+1的卡诺图,再分解开便可以得到如图3-21所示的各触发器的卡诺图。

end zs_2;

ARCHITECTURE Behavioral OF zs_2 IS

SIGNAL

count:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(cp,r)

BEGIN

if r='0'then count<="0000";

elsiF cp'EVENT AND cp='1'THEN

(3)在Multisim环境中仿真实现四位二进制加计数器(缺0010 0011 1101

1110)的建立,并通过虚拟仪器验证其正确性。

二课设题目实现框图

在本课程设计中,四位二进制加计数用四个CP下降沿触发的JK触发器实现,其中有相应的跳变,即跳过了0010 0011 1101 1110四个状态,这在状态转换图中可以清晰地显示出来。

图3-11存盘

最全Proteus元件库元件名称及中英对照

Proteus元件库元件名称及中英对照AND 与门ANTENNA 天线BA TTERY 直流电源BELL 铃,钟BVC 同轴电缆接插件BRIDEG 1 整流桥(二极管) BRIDEG 2 整流桥(集成块) BUFFER 缓冲器BUZZER 蜂鸣器CAP 电容CAPACITOR 电容CAPACITOR POL 有极性电容CAPV AR 可调电容CIRCUIT BREAKER 熔断丝COAX 同轴电缆CON 插口CRYSTAL 晶体整荡器DB 并行插口DIODE 二极管DIODE SCHOTTKY 稳压二极管DIODE VARACTOR 变容二极管DPY_3-SEG 3段LEDDPY_7-SEG 7段LEDDPY_7-SEG_DP 7段LED(带小数点) ELECTRO 电解电容FUSE 熔断器INDUCTOR 电感INDUCTOR IRON 带铁芯电感INDUCTOR3 可调电感JFET N N沟道场效应管JFET P P沟道场效应管LAMP 灯泡LAMP NEDN 起辉器LED 发光二极管METER 仪表MICROPHONE 麦克风MOSFET MOS管MOTOR AC 交流电机MOTOR SERVO 伺服电机NAND 与非门NOR 或非门NOT 非门NPN NPN三极管NPN-PHOTO 感光三极管OPAMP 运放OR 或门PHOTO 感光二极管PNP 三极管NPN DAR NPN三极管PNP DAR PNP三极管POT 滑线变阻器PELAY-DPDT 双刀双掷继电器RES1.2 电阻RES3.4 可变电阻RESISTOR BRIDGE ? 桥式电阻RESPACK ? 电阻SCR 晶闸管PLUG ? 插头PLUG AC FEMALE 三相交流插头SOCKET ? 插座SOURCE CURRENT 电流源SOURCE VOLTAGE 电压源SPEAKER 扬声器SW ? 开关SW-DPDY ? 双刀双掷开关SW-SPST ? 单刀单掷开关SW-PB 按钮THERMISTOR 电热调节器TRANS1 变压器TRANS2 可调变压器TRIAC ? 三端双向可控硅TRIODE ? 三极真空管V ARISTOR 变阻器ZENER ? 齐纳二极管DPY_7-SEG_DP 数码管SW-PB 开关元件名称中文名说明7407 驱动门1N914 二极管74Ls00 与非门74LS04 非门74LS08 与门74LS390 TTL 双十进制计数器7SEG 4针BCD-LED 输出从0-9 对应于4根线的BCD码7SEG 3-8译码器电路BCD-7SEG转换电路AlterNATOR 交流发电机AMMETER-MILLI mA安培计AND 与门BA TTERY 电池/电池组BUS 总线CAP 电容CAPACITOR 电容器CLOCK 时钟信号源CRYSTAL 晶振Compim 串口D-FLIPFLOP D触发器FUSE 保险丝GROUND 地LAMP 灯LED-RED 红色发光二极管LM016L 2行16列液晶可显示2行16列英文字符,有8位数据总线D0-D7,RS,R/W,EN三个控制端口(共14线),工作电压为5V。

TTL芯片明细表

54/74系列集成电路的分类及区别日期:2006-4-9 浏览次数:32554/74系列集成电路大致可分为6大类:●54/74××(标准型);●54/74S××(肖特基);●54/74LS××(低功耗肖特基);●54/74AS××(先进肖特基);●54/74ALS××(先进低功耗肖特基);●54/74F××(高速)。

近年来还出现了基于高速CMOS的54/74系列,该系列可分为3大类:●HC为COMS工作电平(3-18V);●HCT为TTL工作电平(5V),可与74LS系列互换使用;●HCU适用于无缓冲级的CMOS电路。

这9种54/74系列产品,只要后边的标号相同,其逻辑功能和管脚排列就相同。

根据不同的条件和要求可选择不同类型的54/74系列产品,比如电路的供电电压为3V就应选择54/74HC系列的产品。

注1:同型号的54/74系列、54/74HC系列、54/74LS系列芯片,逻辑功能上是一样的。

找不到某种芯片的资料时,可试着查看一下临近型号的芯片资料。

注2:74系列为民品,54系列为军品(航空航天)。

注3:54/74系列是基于TTL电路,其突出缺点是只能5V电压工作,而CMOS电路(CD4000系列)的电压范围是3-18V。

为了便于互换,专门生产了高速CMOS电路构成的54/74HC系列,编号与TTL构成的54/74系列相同,电压范围3-18V。

但是,54/74HC系列的高低电平值与TTL构成的54/74系列不同,所以不能混用。

为此,又专门生产了5V电压工作的54/74HCT 系列,可以与TTL构成的54/74系列混用。

4位计数器逻辑电路

4位计数器逻辑电路以下是四位计数器逻辑电路的一个常见设计:四位计数器是一个用于计数和显示0到15之间的数值的电路。

它由四个单独的计数器组成,每个计数器负责计数一个十六进制位。

设计的逻辑电路包括以下组件:1.时钟源:提供稳定的时钟信号,用于驱动计数器计数。

可以使用一个时钟发生器或外部时钟源。

2.4个D触发器:每个触发器都负责存储一个十六进制位的计数值。

D触发器接收时钟信号和使能信号,根据时钟信号的上升沿更新和存储计数值。

3.4-1多路复用器(MUX):用于选择并显示当前计数值的四个十六进制位。

多路复用器的输入连接到每个D触发器的输出,根据计数器的使能信号选择一个输出作为显示。

4.七段数码管(或其他显示设备):用于显示选中的计数值。

根据控制信号,对应的段会被点亮,显示相应的十六进制数。

工作原理如下:1.初始状态为0。

所有D触发器的输入和使能信号接收到适当的值。

2.当时钟信号的上升沿到达时,D触发器根据当前输入状态更新其输出状态。

3.计数器使能信号决定了计数器是否开始计数。

如果使能信号为高电平,则触发器开始计数;如果为低电平,则保持当前计数值不变。

4.当计数器达到15(或其他最大计数值)时,触发器的输出将被重置为0,并从头开始重新计数。

5.通过多路复用器的选择信号,将当前计数器的输出连接到对应的数码管,显示当前计数值。

这是一个简单的四位计数器的逻辑电路,可以根据特定需求进行扩展和定制。

实际设计中可能会有其他的功能和控制信号,但以上是一个基本的工作原理示例。

[复习]MaxPlus_II__元件库_元件名_分类

![[复习]MaxPlus_II__元件库_元件名_分类](https://img.taocdn.com/s3/m/3ca49d49302b3169a45177232f60ddccda38e6d8.png)

Max+Plus II 中的元件库分类打开图形编辑器(graphic editor),双击窗口,就可出现元件选项下拉菜单;在c:\windows\temporary internet files 中,保存有用户自己编制的元件(实体);在c:\maxplus2\max2lib\prim中,有各类基本门电路及输入/输出端口;在c:\maxplus2\max2lib\mf中,有74系列各类数字集成电路在c:\maxplus2\max2lib\mega_lpm中,有在c:\maxplus2\max2lib\edif,有现将后四个文件夹中的主要元件罗列如下:c:\maxplus2\max2lib\primand12 and2 and3 and4 and6 and8 一般与门band12 band2 band3 band4 band6 band8 输入反向与门= 或非门bdir bdirc 双向端口、可控双向端口bnand12 bnand2 bnand3 bnand4 bnand6 bnand8 输入反向与非门= 或门bnor12 bnor2 bnor3 bnor4 bnor6 bnor8 输入反向或非门= 与门bor12 bor2 bor3 bor4 bor6 bor8 输入反向或门= 与非门carry cascade globol exp icell mcell opndrn sclk soft wireconstant 常量dff dffe 带低电平置位/清零的D触发器,后者带使能端gnd 接地input inputc 输入端口jkff jkffe 带低电平置位/清零的JK触发器,后者带使能端latch D锁存器nand12 nand2 nand3 nand4 nand6 nand8 与非门nor12 nor2 nor3 nor4 nor6 nor8 或非门not 反相器or12 or2 or3 or4 or6 or8 或门output outputc 输出端口param 参量srff srffe 带低电平置位/清零的RS触发器,后者带使能端tff tffe 带低电平置位/清零的t触发器,后者带使能端title 标题框tri 三态门vcc 正电源xnor xor 同或、异或c:\maxplus2\max2lib\mf161mux 16选1 * 81mux16cudslr 16cudslr 16位计数/移位16dmux 16ndux 4-16 译码器21mux 2选12x8mux 8位2选14count 4位计数器74系列电路的分类:“74”指的是商用器件,“54”是军用的,它们的适用温度范围不同,军用的范围大。

七段数码管的动态扫描显示实验报告

实验四七段数码管的动态扫描显示一、实验目的1.进一步熟悉QuartusII软件进行FPGA设计的流程;2.掌握利用宏功能模块进行常用的计数器, 译码器的设计;3.学习和了解动态扫描数码管的工作原理的程序设计方法;二、实验原理及过程实验板上面常用的4为联体的共阳极7段数码管。

其接口电路是把所有数码管的8个笔划段a-h同名端连接起来, 而每一个数码管由一个独立的公共极COM端控制。

对于这种结构的数码管, 采用动态显示的方法是最为广泛的一种显示方式之一。

在轮流点亮的过程中每位显示器的点亮时间都极为短暂, 但由于人的视觉暂留现象以及发光二极管的余晖效应, 尽管实际上每个显示器并非同时点亮, 但只要扫描的速度足够快(如达到30Hz以上), 给人的印象就是一组稳定的显示数据, 不会有闪烁感。

1、本次实验要求在实验板上实现显示00000000-99999999的十进制计数器。

使用的是宏模块产生一个16位的二进制计数器counter()作为4个数码管的显示数据;编写一个分频模块div, 其输出作为计数器counter()的时钟信号;编写数码管驱动模块segmain, 完成7段译码和扫描显示控制2、建立工程, 并建立顶层图。

3、设计计数时钟设计一分频器, 对50Mhz分频输出到计数器, 让计数器以较慢速度递增。

建立.v文件, 输入以下代码module int_div(clk,div_out);input clk;output reg div_out;reg[31:0] clk_div;parameter CLK_FREQ='D50_000_000;parameter DCLK_FREQ='D10;always@(posedge clk)beginif(clk_div<CLK_FREQ/DCLK_FREQ)clk_div<=clk_div+1;elsebeginclk_div<=0;div_out=~div_out;endendendmodule输入完成后, 将该文件设为顶层文件, 并分析该设计文件, 用于检查设计错误。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《电子设计基础》课程报告设计题目:4\7进制计数器学生班级:****学生学号:****学生姓名:****指导教师:****时间:****西南科技大学信息工程学院课程设计报告评分表实验二EDA软件简介一、实验目的1.了解电子电路仿真软件Multisim的基本应用;2.了解电子电路设计软件Protel的电路图编辑基本应用;3.了解电子电路设计软件Protel的PCB编辑基本应用。

二、实验内容三、1、使用Multisim对LED闪烁灯电路进行仿真2、使用Altium Designer对LED闪烁灯电路原理图进行编辑3、使用Altium Designer对LED闪烁灯电路的PCB进行编辑Multisim进行仿真时的原理图的设计以及元器件的放置、仿真时各个数据的记录方式以及示波器、万用表的使用,数据的测量方法。

在用Altium Designer进行原理图的编辑,元器件的放置以及线路的连接以及主要必须总线的放置以及网络标号的合理利用使得原理图看起来更加简洁清晰。

实验小结初步了解了Multisim软件的使用仍需要大量的实际操作才能熟练应用软件进行仿真。

AD对原理图的放置只了解了大概,使用AD制作PCB板时仍然不能熟练的布线实验日期:实验三焊接训练一、实验目的1.了解电子焊接的基本知识;2.初步掌握手工焊接的基本方法和技术。

二、实验内容1、了解PCB板的制作过程,弄懂PCB板上的点、线、面、层、字符的功能和含义。

2、辨认普通的小功率碳膜电阻、独石电容(无极性)、电解电容(有极性)、二极管、三极管和它们的外引线极性,辨认简单的集成电路芯片及其管脚排序方式;3、记录实验中“直接标注法”和“色码标志法”小功率碳膜电阻的标称值,用数字式万用表测量电阻并和标称值进行比较;4、记录实验中电解电容(直接标注法)和独石电容(数码表示法)的标称值(各两个)。

5、将电烙铁插头插入实验桌电源插座,加热电烙铁。

电源位置的选择应以电源线不影响焊接操作为准。

6、对要焊接的插脚式元件的外引线进行去氧化层、镀锡处理(如果是插脚没有氧化的新元件则不需要做此处理),并根据焊点的距离将元器件插脚定型。

7、按焊接技术要求将元件焊接到PCB板上,注意各元件位置和它们的标志朝向要有一致性,以方便辨读。

焊接完成后用斜口钳将多余的外引线剪除。

8、在通用PCB板上首先焊接电阻六个焊接时我们应注意握拿电烙铁的姿势和焊丝拿法,电烙铁头给PCB板焊盘和元件管脚要同时加温,要边加温边给锡,要控制好给锡量,不要抹焊,要让它自行流满焊盘,焊点饱满而不多,焊点光亮而没有沙眼气孔,不能有虚焊,不能有裂纹,也不能有桥接和拉尖,更不能有短路。

良好的焊点的结合面要显弯月型三、实验总结第一次进行焊接试验了解了基本的焊接原理,初次接触了焊接工具进行了最基本的焊接操作,为以后的学习PCB板的制作打下了基础实验日期:实验四小电路装焊与调测一、实验目的1.初步掌握电路装配的基本方法和要求;2.熟悉焊接工艺;3.掌握电路调试的基本步骤与技巧。

二、实验内容1使用已经制作好的PCB板按照试验原理图进行焊接2器材:PCB板发光二极管4.7μF电容器9014三极管电阻130Ω,130kΩ3个27kΩ130kΩ电压U=4.99VI max=13mA,I min=0mA变化渐亮至渐暗频率ʄ=1Hz三、实验总结使用已经制作好的PCB板和现成的原理图制作PCB板,更加直观的了解了PCB板的制作过程,将原理图与PCB板更加有效地结合在一起,熟悉焊接的过程,并且了解了其与原件的辨别与使用实验日期:实验五EDA软件应用一、实验目的1.初步掌握基于Multisim软件的仿真方法;2.初步掌握基于Altium Designer软件的电路图编辑方法;3.初步掌握基于Altium Designer软件的PCB编辑方法。

二、实验内容LED闪烁灯电路的Multisim原理图仿真LED闪烁灯电路的Altium Designer原理图LED闪烁灯电路的Altium Designer PCB图纸丝印层底层顶层1.电路中,有些元器件安装有方向性,请问如何确定这些元器件的方向?答:对于电解电容,正极的一边有一点平的一侧,对于三极管9014,平的一面和圆的一面在PCB板上有标注,对于LM358,接有缺口的一边和有小圆点的一侧,LED长脚的为正极。

2.U1A及其外围元件构成何种电路单元?答:积分电路。

3.U1B及其外围元件构成何种电路单元?答:滞回比较器。

4.R1和R2的作用是什么?答:R1和R2的作用是分压5.T1的作用是什么?答:放大电路6.R6的作用是什么?可以省去不用吗?答:R6是一个保护电阻,防止LED灯因电压过大被烧毁,可以省去7.C2、C3和C4的作用是什么?答:提供稳定的电压,减小输入电源电压的波动对电路的影响8.J1连线的作用是什么?答:J1为电源连接端口,引脚1接电源正极,引脚2接电源负极。

9.若T1的基极改接到U1B的输出端U1-7,电路的工作状态有什么改变?答:电路的工作状态将会变化,由放大器变为运算器。

10.若要改变LED的闪烁频率,可调整哪些元件参数?怎样调整?答:可以调整电容容量,改变电阻阻值。

若要使闪烁频率加快,就增加电容容量,减小电阻阻值。

三,实验总结通过本次实验,对于Multisim 软件,已经AD软件都有了初次的学习已经认识,两者之间联系的应用也让我对于电子技术的认识有了比较大的进步,但也明显的看到了自己的不足,还需要提高的地方。

在应用软件的过程中,尤其感觉到对于知识的掌握熟练程度的不够,在软件的各个细节方面的认识,也不具备科学的严谨态度,这也是自己需要反复练习的,最后,希望自己再拥有知识的前提下,不断创新应用,巩固提高,在老师的教学指导下,一定能有长足的进步,并把我的课程设计做好,在以后的学习中,只是一次非常难得的宝贵的经验。

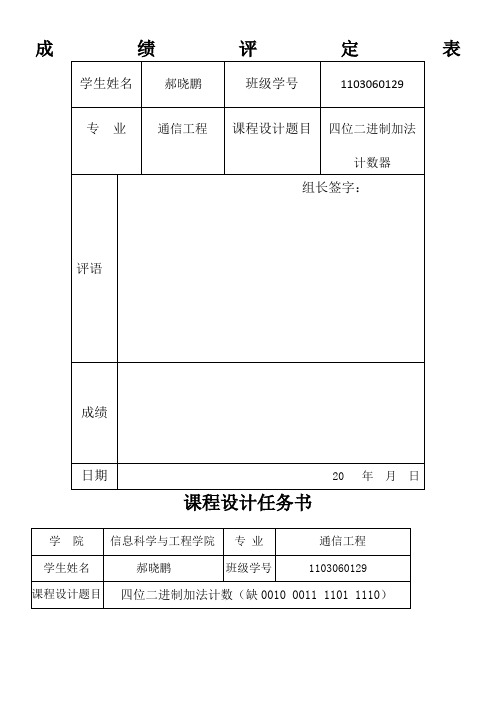

实验日期:课程设计报告一、设计任务及要求1、题目:4/7进制计数器设计:数码管显示,用开关切换两种进制(采用4516)2、要求:a、数码管显示计数状态b、用开关对两种进制进行转换c、计数脉冲由外部提供二、设计内容1、课题分析由题目及其要求分析可知,需要采用4516BD来进行设计4进制和7进制,用开关来转换两种进制可以用一个单刀双掷开关来进行实现,计数状态用数码管显示需要使用七段式数字显示器,来进行显示时需要译码器进行译码,为了方便,采用COMS系列的4511BD来进行译码。

在进行计数之前,为了方便进行计数,采用置数法,使计数器从0开始计数。

2、系统方案选择在进行计数器的设计时,4进制计数器有4个状态,而4516BD在计数的过程中有16个状态,因此要设法跳过多余的12个状态,而7进制计数器只有7个状态,也有9个多余的状态,然而由于4516BD有一个异步主复位端口MR,因此采用反馈清零法可以较方便的实现去除多余的状态。

在进行反馈清零时还需要用到组合逻辑电路,可用74LS20来实现。

3、电路的设计与计算(1)主要元器件功能及参数A、二进制加\减计数器45164516BD是一个边沿触发同步上升/下降4位二进制计数器的时钟输入(CP),向上/向下计数控制输入(UP / DN),低有效计数使能输入(CE),异步高电平并行负载输入(PL),四个并行输入(P0以P3),四并行输出(O0到O3),低电平有效终端数输出(TC),和压倒一切的异步主复位输入(MR)。

4516BD 引脚图4516BD 功能图沿B、7段锁存译码驱动器45117段锁存译码驱动器4511是在同一单片结构上由COS\MOS逻辑器件和N-P-N双极型晶体管器件构成,这些器件的组合使4511具有低静态耗散和高抗干扰及源电流高达25mA 的性能。

当使用外部转换电路时,七段显示器译码器把输入的BCD码,翻译成驱动七段LED数码管各对应段所需的电平,可多路转换盒显示不同的信号4511引脚图4511功能表4511动态工作条件(T=25 C)C、七段式数字显示器七段式数码显示器是目前使用最广泛的一种数码显示器。

这种数码显示器有分布在同一平面的七段可发光的线段组成,可用来显示数字、文字、符号。

最常用的七段数码显示器有半导体数码管和液晶显示器两种。

根据发光二极管的连接形式不同,分为共阴极显示器和共阳极显示器(如图)。

共阴极显示器将七个发光二极管的阴极连接在一起,作为公共端。

在电路中,将公共端接于低电平,将某段二极管的阳极为高电平时,相应段发光。

共阳极的显示方式和共阴极相反。

D、74LS2074LS20为双四输入与非门Y1=A1B1C1D1,Y2=A2B2C2D274LS20逻辑图74LS20动态参数(T=25 C )(2)电路的设计A 、利用4516通过反馈清零法来进行4进制电路设计 4进制计数器状态图0000 0001 01000011 0010由上图可知0100为过渡状态,即0100这个状态会在极短的瞬间出现,在主循环中未加粗表示,由上面介绍4516时可知,MR 为高电平时复位,因此,直接可通过其输出端O 2产生的信号为反馈信号到MR 端来进行清零。

B 、利用4516通过反馈清零法来进行7进制电路设计 7进制计数器状态图0000 0001 0010 0011011101100101 0100由上图可知0111为过渡状态,即0111这个状态会在极短的瞬间出现,在主循环中未加粗表示,由上面介绍4516时可知,MR 为高电平时复位,因此,直接可通过其输出端O 0、O 1、O 2产生的信号为反馈信号到MR 端来进行清零。

由于其清零时需要三个信号同时作用,故采用组合逻辑电路来实现。

则控制信号为Y= O 2O 1O 0当使用74LS00时会产生竞争冒险现象,故采用74LS20一个芯片来实现组合逻辑电路。

组合逻辑电路原理图74LS40D74LS40DO2C 、通过置数法来设置计数时的初始的0状态由4516有置数端PL ,可由一个开关控制初始状态,接到PL 端,输入端全部接地,用来使计数器初始状态为0。

开关闭合,计数器归零,停止计数,开关打开,计数器从零开始计数。

D 、4\7进制可由一个单刀双掷开关来进行转换,控制信号接到4516的MR 端如上图所示,由一个单刀双掷开关来进行4\7进制的转换。

如上图所示,将计数的结果由7段的数码管显示,数码管的每个端口串接330欧姆的电阻用来保护数码管。

4进制状态MR4、仿真及结果分析选择一个方波信号发生器作为输入信号源;CP由Multisim仿真,得到实验波形初始置0开关闭合,未进行计数上图为4进制的脉冲信号及输出端的波形图,从上图可以看出,在20ms以前,置0开关关闭,虽然有脉冲信号,但是并没有进行计数,从20ms后,开关打开开始计数,为第一个状态0000,后面的三个状态依次为0001、0010、0011,形成了0~3四个状态的转换,构成了一个4进制计数器。