高效除法器verilog实现

Verilog除法器设计(包含单步设计和流水线设计)

Verilog除法器设计(包含单步设计和流水线设计)1.单步设计:单步设计是最简单的一种除法器设计,其原理是将被除数和除数逐位进行比较和计算,直到得到商和余数。

首先,需要定义Verilog模块的输入和输出端口。

输入包括被除数(dividend)和除数(divisor),输出包括商(quotient)和余数(remainder)。

同时,还需要定义一些辅助信号,如计数器和比较器。

```verilogmodule Dividerinput [N-1:0] dividend,input [N-1:0] divisor,output [N-1:0] quotient,output [N-1:0] remainder```在单步设计中,使用一个循环进行逐位比较和计算,直到得到商和余数。

在每一步循环中,被除数向左移动一位,并与除数进行比较。

如果被除数大于或等于除数,则商的对应位为1,否则为0。

然后,将商的对应位赋值给商,并从被除数中减去除数的相应部分。

最后,余数更新为被除数。

```verilogreg [N-1:0] temp_dividend;reg [N-1:0] temp_remainder;reg [N-1:0] temp_quotient;integer i;temp_dividend = dividend;temp_remainder = {N{1'b0}};temp_quotient = {N{1'b0}};for (i = 0; i < N; i = i+1) begintemp_remainder = temp_dividend;if (temp_remainder >= divisor) begin temp_quotient[i] = 1'b1;temp_dividend = temp_remainder - divisor; endtemp_dividend = temp_dividend << 1;endquotient = temp_quotient;remainder = temp_dividend;endendmodule```以上就是单步设计的Verilog除法器代码。

基于verilog的除法器

module divider(quotient,remainder,ready,error,word1,word2,start,clock,reset); parameter L_divn=8,L_divr=4,S_idle=0,S_adivr=1,S_adivn=2,S_div=3,S_err=4,L_state=3,L_cnt=4,Max_cnt=L_divn-L_divr;output [L_divn-1:0] quotient,remainder;output ready,error;input [L_divn-1:0] word1;//dividendinput [L_divr-1:0] word2;//divisorinput start,clock,reset;//0,start,1,resetreg [L_state-1:0] state,next_state;reg Load_words,Subtract,Shift_dividend,Shift_divisor;reg [L_divn-1:0] quotient;reg [L_divn:0] dividend;reg [L_divr-1:0] divisor;reg [L_cnt-1:0] num_Shift_dividend,num_Shift_divisor;reg [L_divr:0] comparison;wire MSB_divr=divisor[L_divr-1];wire ready=((state==S_idle)&&reset);wire error=(state==S_err);wire Max=(num_Shift_dividend==Max_cnt+num_Shift_divisor);wire sign_bit=comparison[L_divr];assign remainder=(dividend[L_divn-1:L_divn-L_divr])>num_Shift_divisor;/////////always @(state or dividend or divisor or MSB_divr)case(state)S_adivr: if(MSB_divr==0)comparison=dividend[L_divn:L_divn-L_divr]+{1'b1,~(divisor<<1)}+1'b1;elsecomparison=dividend[L_divn:L_divn-L_divr]+{1'b1,~divisor[L_divr-1:0]}+1'b1;default:comparison=dividend[L_divn:L_divn-L_divr]+{1'b1,~divisor[L_divr-1:0]}+1'b1;endcasealways @(posedge clock or negedge reset)if(!reset) state<=S_idle; else state<=next_state;always @(state or word1 or word2 or start or comparison or sign_bit or Max)beginLoad_words=0;Subtract=0;Shift_dividend=0;Shift_divisor=0;case(state)S_idle: case(!start)0: next_state=S_idle;1: if(word2==0) next_state=S_err;else if(word1) begin next_state=S_adivr;Load_words=1; endelse next_state=S_idle;endcaseS_adivr: case(MSB_divr)0: if(sign_bit==0) begin next_state=S_adivr;Shift_divisor=1; endelse if(sign_bit==1) next_state=S_adivn;1: next_state=S_div;endcaseS_adivn: case({Max,sign_bit})2'b00: next_state=S_div;2'b01: begin next_state=S_adivn;Shift_dividend=1; end2'b10: begin next_state=S_idle;Subtract=1; end2'b11: next_state=S_idle;endcaseS_div: case({Max,sign_bit})2'b00: begin next_state=S_div;Subtract=1; end2'b01: next_state=S_adivn;2'b10: begin next_state=S_div;Subtract=1; end2'b11: begin next_state=S_div;Shift_dividend=1; endendcasedefault: next_state=S_err;endcaseendalways @(posedge clock or negedge reset)beginif(!reset)begindivisor<=0;dividend<=0;quotient<=0;num_Shift_dividend<=0;num_Shift_divisor<=0;endelse if(Load_words==1)begindividend<=word1;divisor<=word2;quotient<=0;num_Shift_dividend<=0;num_Shift_divisor<=0;endelse if(Shift_divisor)begindivisor<=divisor<<1;num_Shift_divisor<=num_Shift_divisor+1;endelse if(Shift_dividend)begindividend<=dividend<<1;quotient<=quotient<<1;num_Shift_dividend<=num_Shift_dividend+1;endelse if(Subtract)begindividend[L_divn:L_divn-L_divr]<=comparison;quotient[0]<=1;endendendmodule。

高速硬件除法器设计

高速硬件除法器设计一、实验目得 :了解与掌握硬件除法器得结构与工作原理,分析除法器得仿真波形与工作时序。

二、实验原理 :除法器算法得思路与手写除法基本一致。

假设除法a/b,a、b 就是输入得两个位数都为 n 得二进制数。

如果位数小于n, 可以在位数较少得数得前面添加0 来满足这种位数要求。

商与余数就是n 位标准矢量类型得二进制数。

在过程中, 算法也就是按顺序执行得 , 但就是综合后系统将会由组合逻辑电路组成, 进程中得每一步都与系统构建得不同级别得逻辑电路相对应。

首先 , 从输入信号中创建变量 A 与 B,A=a,B=b, 其中 a,b 都就是 n 位二进制数。

如果 A 大于等于 B, 则商为 1 , 余数为 A-B, 否则商为 0, 余数为 A。

这就是算法开始得第一次循环, 如果小于 B, 结果商位就是 0,A得值不做变化并保留其值。

否则 , 结果商位为 1, 则把相减后得余数插入变量 A 中。

不管比较结果如何, 变量 A 都要右移一位 ( 左边添加 0),接着开始下一次循环。

循环 n 次之后 ,n 位结果赋给商 , 最后 A剩余得值就就是余数。

三、实验任务 :用VerilogHDL设计除法器。

除法器得参考程序如下:module DIV16(input CLK,input[15:0] A,B,output reg[15:0] QU,RE);reg[15:0] AT,BT,P,Q; integer i;always (posedge CLK) beginAT=A; BT=B; P=16'H0000;Q=16'H0000;for(i=15;i>=0;i=i-1)beginP={P[14:0],AT[15]};AT={AT[14:0],1'B0}; P=P-BT;if (P[15]==1) begin Q[i]=0; P=P+BT; endelse Q[i]=1;endendalways (*) begin QU=Q;RE=P; endendmodule, 输出结果分成两其中 A 与 B 就是除法器输入端得两个 16 位数据 , 它们分别为被除数与除数部分 :QU 就是商 ,RE 就是余数。

verilog代码乘法除法编写

Verilog代码乘法除法1. 引言Verilog是一种硬件描述语言,用于设计和建模数字电路。

在数字电路中,乘法和除法是常见的运算操作。

本文将介绍如何使用Verilog编写乘法和除法的代码,并提供一些示例来帮助读者更好地理解。

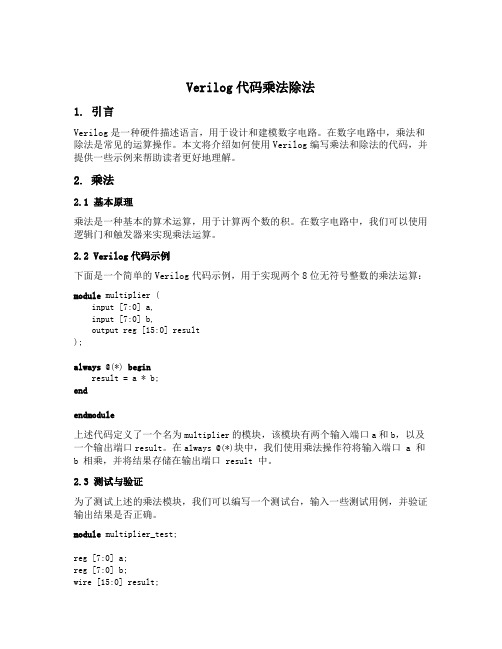

2. 乘法2.1 基本原理乘法是一种基本的算术运算,用于计算两个数的积。

在数字电路中,我们可以使用逻辑门和触发器来实现乘法运算。

2.2 Verilog代码示例下面是一个简单的Verilog代码示例,用于实现两个8位无符号整数的乘法运算:module multiplier (input [7:0] a,input [7:0] b,output reg [15:0] result);always @(*) beginresult = a * b;endendmodule上述代码定义了一个名为multiplier的模块,该模块有两个输入端口a和b,以及一个输出端口result。

在always @(*)块中,我们使用乘法操作符将输入端口a和b相乘,并将结果存储在输出端口result中。

2.3 测试与验证为了测试上述的乘法模块,我们可以编写一个测试台,输入一些测试用例,并验证输出结果是否正确。

module multiplier_test;reg [7:0] a;reg [7:0] b;wire [15:0] result;multiplier dut(.a(a),.b(b),.result(result));initial begin// Test case 1: a = 5, b = 3a = 5;b = 3;#10; // Wait for 10 time unitsif (result !== 15)$display("Test case 1 failed");// Test case 2: a = 10, b = 0a = 10;b = 0;#10; // Wait for 10 time unitsif (result !== 0)$display("Test case 2 failed");// Add more test cases here...endendmodule上述代码定义了一个名为multiplier_test的测试台模块。

verilog除法器 srt算法

verilog除法器srt算法Verilog实现SRT除法器算法在数字电路设计中,除法是一种常见的数值运算。

在Verilog中,可以使用SRT (Sweeney-Robertson-Tocher)算法来实现除法器。

SRT算法是一种用于计算除法的算法,它可以实现高精度和高效率的除法运算。

本文将详细介绍如何使用Verilog实现SRT除法器算法,以及该算法的原理和实现步骤。

SRT除法器算法的原理SRT除法器算法是一种通过连续的减法和移位操作来计算除法的算法。

它采用了一种逐位比较的策略,可以在不考虑余数的情况下,实现整数除法的计算。

SRT 算法的核心思想是将被除数和除数进行比较,并根据比较结果来进行减法和移位操作,以得到商数。

SRT算法的步骤如下:1. 将被除数和除数进行比较,得到初始估计商数。

2. 进行减法运算,得到余数。

3. 对余数进行移位操作,得到新的估计商数。

4. 重复步骤2和3,直到得到最终的商数。

SRT算法的优点是可以实现高精度和高效率的除法运算,适用于多种除法场景。

Verilog实现SRT除法器算法的步骤接下来,我们将详细介绍如何使用Verilog实现SRT除法器算法。

第一步:定义模块和端口首先,我们需要在Verilog中定义SRT除法器的模块和端口。

模块包括被除数、除数和商数等参数,端口包括输入端口和输出端口。

定义模块和端口的代码如下:verilogmodule srt_divider (input [N-1:0] dividend, 被除数(N位)input [N-1:0] divisor, 除数(N位)output reg [2*N-1:0] quotient, 商数(2N位)output reg [N-1:0] remainder 余数(N位));在上面的代码中,我们定义了一个包括被除数、除数、商数和余数的SRT除法器模块,并设置了相应的输入端口和输出端口。

第二步:实现SRT算法的核心逻辑接下来,我们需要在Verilog中实现SRT算法的核心逻辑。

verilog除法的近似计算

Verilog 除法的近似计算1. 引言Verilog 语言是一种硬件描述语言,广泛应用于数字电路设计和硬件描述。

在数字电路设计中,除法运算是一个常见的运算,在一些特定的硬件评台上,除法运算可能需要进行近似计算。

本文将深入探讨Verilog 除法的近似计算方法。

2. Verilog 除法的原理在Verilog 中,除法运算通常是通过硬件电路来实现的。

但是,在一些资源受限的硬件评台上,完全实现除法运算可能会占用过多的资源。

需要一种近似计算的方法来实现除法运算。

3. 近似计算方法有很多种方法可以用来实现Verilog 中的除法运算的近似计算。

其中一种方法是通过使用查找表来进行近似计算。

通过预先计算出一定范围内的除法结果,并存储在查找表中,然后根据输入的除数和被除数,在查找表中查找对应的近似结果。

这种方法可以大大节省硬件资源,但会牺牲一定的计算精度。

4. 优缺点分析通过近似计算方法来实现Verilog 中的除法运算,可以在节省硬件资源的实现较为准确的计算结果。

但是这种方法也有一定的局限性,因为近似计算可能会引入一定的误差,对于一些对计算精度要求较高的应用场景可能不够适用。

5. 个人观点和理解在数字电路设计和Verilog 编程中,除法运算是一个常见但又具有挑战性的问题。

通过近似计算方法来实现Verilog 中的除法运算,可以在一定程度上解决资源占用的问题,但是也需要在计算精度和误差控制方面进行权衡。

我个人认为,对于不同的应用场景,需要根据具体的需求来选择合适的近似计算方法。

6. 总结通过本文的深入探讨,我们对Verilog 除法的近似计算有了更深入的了解。

近似计算方法在数字电路设计中具有一定的应用前景,但也需要在计算精度和资源占用上进行综合考量。

在今后的实践中,希望我们能够灵活运用近似计算方法,实现更加高效和灵活的数字电路设计。

以上是根据您提供的主题“verilog除法的近似计算”撰写的文章,希望能够对您有所帮助。

quartus中除法器的用法

quartus中除法器的用法

在Quartus中,除法器通常用于实现数字电路中的除法运算。

Quartus是一款由英特尔公司开发的集成电路设计软件,用于设计和验证数字电路。

下面我将从不同角度来介绍Quartus中除法器的用法。

首先,Quartus中的除法器可以通过硬件描述语言(如Verilog 或VHDL)来实现。

在Verilog中,可以使用“/”操作符来表示除法运算,而在VHDL中可以使用除法函数来实现。

这样可以在设计中直接使用除法运算,而无需手动实现除法器的逻辑。

其次,Quartus中的除法器还可以通过IP核的方式进行使用。

IP核是一种预先设计好的可重用模块,其中包含了除法器的逻辑实现。

在Quartus中,可以通过IP Catalog来选择合适的IP核,并将其实例化到设计中,从而实现除法运算。

此外,Quartus还提供了丰富的仿真和验证工具,可以用于验证除法器的功能和性能。

可以使用ModelSim等仿真工具对设计进行仿真,以验证除法器的正确性。

同时,Quartus还提供了时序分析工具,可以用于分析除法器的时序性能。

总的来说,Quartus中的除法器可以通过硬件描述语言实现,也可以通过IP核进行使用,并且可以借助Quartus提供的仿真和验证工具进行验证。

这些方法可以帮助工程师在数字电路设计中高效地实现除法运算功能。

verilog hdl除法

verilog hdl除法

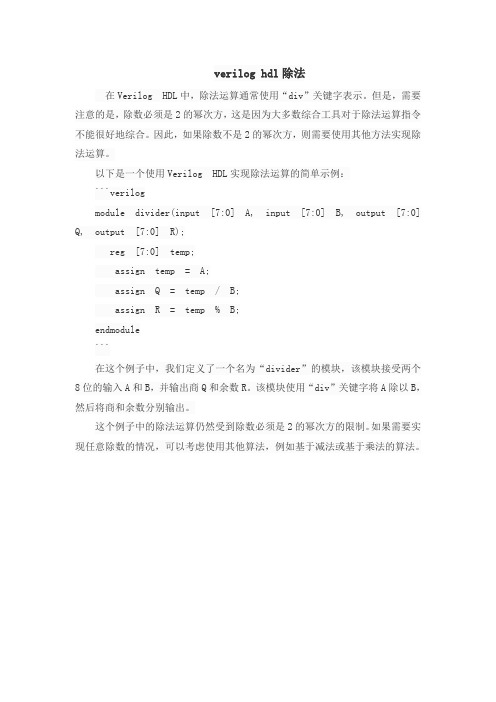

在Verilog HDL中,除法运算通常使用“div”关键字表示。

但是,需要注意的是,除数必须是2的幂次方,这是因为大多数综合工具对于除法运算指令不能很好地综合。

因此,如果除数不是2的幂次方,则需要使用其他方法实现除法运算。

以下是一个使用Verilog HDL实现除法运算的简单示例:

```verilog

module divider(input [7:0] A, input [7:0] B, output [7:0] Q, output [7:0] R);

reg [7:0] temp;

assign temp = A;

assign Q = temp / B;

assign R = temp % B;

endmodule

```

在这个例子中,我们定义了一个名为“divider”的模块,该模块接受两个8位的输入A和B,并输出商Q和余数R。

该模块使用“div”关键字将A除以B,然后将商和余数分别输出。

这个例子中的除法运算仍然受到除数必须是2的幂次方的限制。

如果需要实现任意除数的情况,可以考虑使用其他算法,例如基于减法或基于乘法的算法。

verilog HDL语言的循环整数除法器

循环整数除法器******学院**级***系姓名:***学号:********指导老师:****目录一、除法器的基本原理与改进第1页二,程序源代码及QuartusII仿真第4页三,测试代码及Modelsim仿真第8页四,DC综合部分第11页五.Astro版图及解释第14页一,除法器的基本原理与改进本设计是基于传统的除法器的基础上改进而来的。

传统除法器的设计:一、先取除数和被除数的正负关系,然后正值化被除数。

传统除法器因为需要递减的关系,所以除数就取负值的补码,方便操作。

二、被除数递减除数,每一次的递减,商数递增。

三、直到被除数小于除数,递减过程剩下的是余数。

四、输出的结果根据除数和被除数的正负关系。

例如:10除以3其操作流程就是:1,10-3 余7>3;2,7-3 余4>3;3,4-3 余1<3。

即经过三次的运算比较,得出10÷3=3并且余1。

此次运算需要三个时钟周期来进行比较运算,显然,随着被除数的增大,其所需的时钟周期会呈递增趋势,加入,被除数过大的话,其过多的时钟消耗将会减慢运算速度。

改进的循环型除法器循环型的除法器,就是位操作的除法器。

循环型的除法器是典型的除法器,假设除数和被除数的位宽为N位,那么除法器就会循环N次的除法操作。

这样时钟消耗就不会随着被除数的增加而增加了,提高了计算的速度。

假设被除数A = 7(0111),除数B = 2 ( 0010 ),它们均为4位位宽。

那么操作空间就是 temp 就是 2 * Width。

temp[ Width - 1 : 0 ]是用来填充被除数,temp[ Width * 2 - 1:Width -1 ] 是用与除数递减操作。

为了方便操作,我们建立 5位位宽的s空间用来寄存除数B的负值补码形式。

此外还要考虑同步操作,temp[ Width * 2 - 1:Width -1 ] 和除数B的递减操作应该发生别的空间,亦即diff空间。

verilog 乘法 除法

verilog 乘法除法Verilog是一种硬件描述语言,广泛应用于数字电路设计和验证。

本文将介绍Verilog中的乘法和除法原理及其在实际应用中的实现。

一、Verilog乘法器原理与实现1.原理Verilog乘法器的原理是基于位级运算。

输入的两个二进制数按位进行与运算,得到乘积的位级表示。

然后通过移位和加法运算,将位级乘积转换为最终的整数乘积。

2.实现Verilog乘法器的实现主要分为三个部分:全加器、位级乘法器和移位器。

全加器用于处理乘数和被乘数的各位与运算结果;位级乘法器用于计算乘数和被乘数的各位与运算;移位器用于调整位级乘积的位数。

3.实例以下是一个简单的Verilog乘法器实例:```module multiplier(input [7:0] a, b [7:0], output [15:0] result);wire [15:0] partial_product;wire [15:0] temp_result;// 位级乘法器wire [15:0] product [7:0];genvar i;generatefor (i = 0; i < 8; i = i + 1) beginassign product[i] = a * b[i];endendgenerate// 移位器assign partial_product = {product[7], product[6:0]};// 全加器assign temp_result = partial_product + result;assign result = temp_result;endmodule```二、Verilog除法器原理与实现1.原理Verilog除法器的原理是采用迭代算法,将除法问题转化为加法和减法问题。

除数和被除数按位进行与运算,得到余数的位级表示。

然后通过循环移位和加法运算,将余级表示转换为最终的整数商和余数。

加减交替阵列除法器的设计与仿真实现

加减交替阵列除法器的设计与仿真实现一、引言随着数字电路的发展,除法器在计算机和通信系统中的应用越来越广泛。

加减交替阵列除法器是一种高效的除法器,具有运算速度快、面积小等优点。

本文将详细介绍加减交替阵列除法器的设计与仿真实现。

二、加减交替阵列除法器原理加减交替阵列除法器是一种基于移位和加减运算的快速除法器。

其主要原理如下:1. 将被除数左移n位,得到一个n+1位的数(其中最高位为0)。

2. 对于每个n+1位的数,采用加减交替的方式进行运算。

3. 在第n步时,判断商是否已经求出。

4. 如果商未求出,则返回第1步。

三、加减交替阵列除法器设计1. 系统框图加减交替阵列除法器由以下模块组成:被除数寄存器、商寄存器、余数寄存器、控制单元、计算单元和状态机。

系统框图如下所示:2. 系统模块设计(1)被除数寄存器被除数寄存器用于存储待处理的被除数。

它由一个n位的寄存器和一个移位器组成,可以将被除数左移n位。

(2)商寄存器商寄存器用于存储计算得到的商。

它由一个n位的寄存器和一个移位器组成,可以将商左移1位。

(3)余数寄存器余数寄存器用于存储计算得到的余数。

它由一个n+1位的寄存器和一个移位器组成,可以将余数左移1位。

(4)控制单元控制单元用于控制整个系统的运行。

它根据状态机的输出信号来控制各个模块之间的数据传输和运算。

(5)计算单元计算单元是加减交替阵列除法器最核心的部分,用于进行加减运算。

它由若干个加法器和减法器组成,每个加法器或减法器都能够进行一次加或减运算。

(6)状态机状态机用于控制控制单元的工作状态,并输出相应的信号。

它有以下三种状态:a. 初始化状态:在这个状态下,被除数、商、余数等变量都被初始化。

b. 运行状态:在这个状态下,加减交替阵列除法器按照原理进行运算。

c. 结束状态:在这个状态下,商已经求出,整个系统停止工作。

四、加减交替阵列除法器仿真实现1. 系统仿真为了验证加减交替阵列除法器的正确性,需要对其进行仿真。

高效除法器

一、实验目的及要求用verilog实现一个被除数为8位,除数为4位的高效除法器。

二、实验设备(环境)及要求实验室计算机及modelsim仿真软件,最后用synplify进行综合仿真得到图形。

三、实验内容与步骤1.实验总体设计思路1、先定义被除数为dividend,除数为divisor,商为Rtient,余数为Qainer,举个例子假如被除数与除数分别为1111与0100。

2、将被除数赋给寄存器变量Q=1111,再将除数赋给变量Dr=0100,设置商的变量R 初始值为 4’b0000,则{R,Q}为{00001111}。

3、首先将{R,Q}左移一位,即{00011110},现在R=0001,Q=1110;4、比较R与除数Dr的大小,如果R>Dr,则R=R-Dr,并且{R,Q}再左移一位并且Q[0]=1,反之{R,Q}左移一位Q[0]=0。

5、继续上述过程,循环4次{R,Q}={00111100},{01111000},{01110001},{01100011}。

6、此时商Rtient=Q,而余数Qainer=(R>>1)(即余数等于R向右移一位),所以此例结果为Rtient=0011,Qainer=0011。

检验:对应于十进制,是15除以4,商为3,余数为3.2.系统结构和模块划分,关键子模块之间的接口实现定义。

输入端口:Clk,Rst,dividend,divisor;输出端口:quotient,remainer;寄存器变量:R,Q,Dr;Verilog 代码如下:module chufa(dividend,divisor,Clk,Rst,quotient,remainer); //端口定义input [7:0] dividend; //定义被除数input [7:0] divisor ; //定义除数input Clk; //时钟信号input Rst; //复位信号output [7:0] quotient; //定义商数output [7:0] remainer; //定义余数reg [7:0]Q;reg [7:0]R;reg [7:0]Dr; //定义寄存器变量wire [7:0]quotient;wire [7:0]remainer;integer i;parameter SIZE = 8;always@(posedge Clk or negedge Rst)beginif(!Rst) //复位信号为0时置0。

fpga小数除法 -回复

fpga小数除法-回复FPGA(现场可编程门阵列)是一种集成电路技术,可以实现可编程硬件逻辑的实时处理。

它在各种领域中得到广泛应用,包括图像处理、数据通信以及数字信号处理等。

在这篇文章中,我们将讨论FPGA 的小数除法功能及其实现。

小数除法是一项基本的数学运算,但在计算机中实现它是具有挑战性的。

传统的微处理器和硬件并不直接支持小数除法,所以通常需要额外的软件算法来实现。

然而,FPGA 具有高度可编程的特性,可以用硬件逻辑直接实现小数除法功能,从而提供更高的计算性能。

下面是实现FPGA 小数除法的基本步骤:1. 确定使用的数据格式:在开始实现小数除法之前,需要确定所使用的数据格式。

常用的格式包括浮点数和定点数。

浮点数用于表示较大的范围和更高的精度,而定点数适用于精确的小数计算。

2. 设计除法器的数据路径:在FPGA 中实现小数除法的关键是设计一个合适的数据路径。

数据路径是各种逻辑电路组件的连接,用于执行特定的计算任务。

在小数除法器的数据路径中,通常包括寄存器、加减器、比较器和移位器等。

3. 实现除法运算步骤:小数除法通常通过迭代运算来实现,其中每个迭代步骤都将部分商和余数逐渐逼近最终结果。

每个步骤的核心操作是将当前余数乘以基数,然后与除数进行比较和运算。

这个过程将一直进行到达到所需的精度。

4. 处理异常情况:在小数除法的实现过程中,需要考虑可能的异常情况。

例如,如果被除数或除数为零,就会引发除以零的错误。

为了确保计算的正确性和稳定性,需要在硬件逻辑中加入异常处理机制。

5. 优化设计:在实现小数除法器后,可以通过优化设计来提高其性能和效率。

一种常见的方法是使用流水线技术,将整个除法过程分为多个阶段,并同时处理多个数据。

这样可以提高整个计算过程的并行性和速度。

需要注意的是,FPGA 小数除法的实现并不是一项简单的任务。

它需要对数字电路和计算机体系结构有深入的了解,并且需要使用专门的设计工具和语言,如VHDL或Verilog。

高性能CPU中除法器的设计与实现

同济大学硕士学位论文高性能CPU中除法器的设计与实现姓名:石松华申请学位级别:硕士专业:电子科学与技术指导教师:林正浩20050301摘要摘要在CPtJ的发展过程中,由于对运算精度的要求不断提高,浮点运算单元成为构成CPU的不呵缺少的部件之一。

除法相对于加法、减法和乘法来说,是属于较少用到的运算,但因为运算较复杂,使得其延迟时间比其他运算长,其性能优劣将直接影响CPU的整体处理能力,因此,设计高性能的浮点除法单元成为提高CPU性能的关键。

本文首先介绍了浮点数的标准和运算规则,在此基础上分析了浮点除法的基本原理,然后介绍了目前流行的基于减法和基于乘法的经典浮点除算法,在比较几种算法优劣的基础上选择了基4SRT算法作为本设计的算法。

接下来应用基4SRT算法设计了浮点除法器的体系结构,对此结构中的关键部件进行了分析与选择。

在此基础上通过VerilogHDL编码和综合优化给出了该除法器的基于.1Sum工艺库的门级网表。

本文的主要工作集中在浮点除法器的算法选择、体系结构设计和综合优化。

难点是算法选择,各种算法各有优缺点,需综合考虑,进行取舍。

重点是体系结构设计。

创新点是综合优化,在不改变源代码的前提下,应用不同的优化策略较之标准编译过程可以有效地提高设计的性能。

关键词:浮点除法SRTVerilog综合优化AbstracfABSTRACTTherequirementofcomputationalprecisionisrisinginthedevelopmentofCPU,sothefloating—pointunitespeciallythefloating—pointdividerunitbecomesoneofthenecessarybasicpartofCPU.Divisionistheleastusedoperationascomparetoaddition,subtractionandmultiplication.Butdivisionoperationismorecomplex,itstime—delayislongerthanotheroperation,theperformanceoffloating—pointdividerunithasadirecteffectonCPU,Soahi曲performancefloating—pointdividerunitiscriticaltothedesignofCPU.Inthisarticle,standardandcomputingruleareintroducedfirst.Onthisbase,theoryoffloating—pointdivisionisanalyzed.Thensomepopularfloating-pointdivisionarithmeticisintroduced.Basedonthecomparisonofdifferentarithmetic,Radix.4SRTarithmeticischosentorealizethisdesign.Thenarchitectureoffloating—pointdivisionbasedonradix-4arithmeticisdesigned.OnthisbasebyVerilogHDLcodingandsynthesisoptimization,netlistbasedon.18urntechnologylibraryisprovided.Finallylow—powerdesignisdiscussed.Themainworkofthisarticlefocusesonchoosingoffloating-pointdivisionarithmetic,architecturedesignandsynthesisoptimization.Thedifficultyischoosingoffloating-pointdivisionarithmetic,eacharithmetichasitsOWnadvantageandisdisadvantage,choosingisdependedonwholeconsideration.Thekeypointarchitecturedesign.Theinnovationalpartissynthesisoptimization.Applicationofdifferentoptimizationstrategycaneffectivelyenhancetheperformanceofdesignascomparetostandardcompileprocess.KeyWords:floating-pointdivisionSRTVerilogSynthesisOptimization】I学位论文版权使用授权书本人完全了解同济大学关于收集、保存、使用学位论文的规定,同意如下各项内容:按照学校要求提交学位论文的印刷本和电子版本;学校有权保存学位论文的印刷本和电子版,并采用影印、缩印、扫描、数字化或其它手段保存论文;学校有权提供目录检索以及提供本学位论文全文或者部分的阅览服务;学校有权按有关规定向国家有关部门或者机构送交论文的复印件和电子版;在不以赢利为目的的前提下,学校可以适当复制论文的部分或全部内容用于学术活动。

verilog移位除法

verilog移位除法Verilog中的移位除法可以通过逻辑移位操作实现。

以下是一个使用移位除法计算两个无符号整数相除的例子:```verilogmodule shift_divider (input [31:0] dividend, // 被除数input [31:0] divisor, // 除数input clk, // 时钟信号input reset, // 复位信号output reg [31:0] quotient, // 商output reg [31:0] remainder, // 余数output reg done // 运算完成信号);reg [31:0] count; // 移位计数器reg [31:0] shifted_divisor; // 移位后的除数always@(posedge clk or posedge reset) beginif (reset) begincount <= 0;shifted_divisor <= divisor;quotient <= 0;remainder <= 0;done <= 0;end else beginif (count < 32) beginif (dividend >= shifted_divisor) beginquotient[count] <= 1;remainder <= dividend - shifted_divisor;end else beginquotient[count] <= 0;remainder <= dividend;endshifted_divisor <= shifted_divisor >> 1;count <= count + 1;end else begindone <= 1;endendendendmodule```在这个例子中,首先定义了一个移位计数器`count`和一个移位后的除数`shifted_divisor`。

高效除法器verilog实现

整理文本西北工业大学《 FPGA 技术实验》实验报告二(高效除法器 )学院:软件与微电子学院学号:姓名:专业:微电子学实验时间:2011.10.12实验地点:毅字楼 335指导教师:王少熙西北工业大学2010年 10 月一、实验目的及要求实验目的 : 1.进一步了解熟悉verilog 语句语法掌握条件语句在简单建模中的应用,学会建模仿真综合 .2.熟练运用 modelsim进行调试模拟仿真 .3.初步学会运用综合工具进行综合,熟悉 synplify.实验要求 :用verilog实现一个被除数为8 位,除数为 4 位的高效除法器 .二、实验设备(环境)及要求ModelSim SE 6.2b及 Synplify Pro 9.6.2三、实验内容与步骤1.实验总体设计思路由于只有加法器 ,除法在计算机中是通过部分余数左移加除数补码或 0 实现 ,我们由此可以得到启示 ,也按照如此的思路进行 .整体思路是先将八位 (本来余数是四位的但是我们这里的余数不仅仅充当余数 ,还当中间变量把被除数从最高位一位一位的移到余数里 )余数清零 ,然后把被除数的最高位拼接到余数后面 ,此时余数与除数比较 , 若余数大于除数 ,则把他们俩的差作为新的余数 ,且把对应的商值为记 1; 若余数小于除数 ,则把对应位的商值记 0;进行下一步之前把被除数的第二高位继续拼接到余数后面 ,如此进行 ,循环八次即可 .最后结果是得到商和余数的形式 .其算法流图如下所示 :Start余数 rem=0;商 quo=0; i=7rem={rem[6:0],did[i]}是否rem>disquo[i]=1;i=i-1;quo[i]=0;rem=rem-dis;rem=rem;i=i-1;i<0否是得到 quo,rem.是 4 位,除数 (dis)是 2 位,商(quo)是 4 位 ,余数 (rem)是 4 位,设 did=0110,dis=10,我们来看看是怎么执行的.首先余数和商都清零 ,即 rem=0,quo=0;把被除数的最高位0 拼接到 rem的最低位 ,此时 rem=0000B,由于 rem 小于除数 dis=10,则商 quo[3]=0;下面进行第二次计算,把 did[2]拼接到 rem 最低位 ,此时 rem=0001,dis=10>rem,故 quo[2]=0;继续计算 , 把 did[1]拼接到 rem 最低位 ,此时 rem=0011,dis=10<rem,故quo[1]=1,rem=rem-quo=0011-10=0001;进行最后一轮运算 , 把 did[0]拼接到 rem 最低位 ,此时 rem=0010,dis=10=rem,因此 quo[0]=1,rem=rem-dis=0010-10=0000,至此我们已计算完毕商quo=0011,余数 rem=0000;计算简单快速 .2.测试平台设计模块设计`timescale 1ns/1nsmodule divider_8_4(did,// Divident被除数dis,// Divisor除数quo,// Quotient商rem,// Remainder 余数error//错误,如果除数为0.则error置1);parameter M=7;//被除数,余数,商的位数parameter N=3;//除数的位数input [M:0] did;input [N:0] dis;output [M:0] quo;output [M:0] rem;output error;reg [M:0] quo;reg [M:0] rem;reg error;integer i;//整数,用于计数always @(did or dis)//被除数,除数beginquo=0;rem=0;//开始余数和商清零if(dis==0)error=1;//若除数为0则显示错误else if(did<dis)//为了提高效率,在被除数小于除数时begin//商0,余数为除数rem=dis;quo=0;error=0;endelsebeginerror=0;for (i=8;i>0;i=i-1) //循环8次beginrem={rem[M-1:0],did[i-1]}; //把did[i-1]连接到rem后quo=quo<<1;//商左移一位if(rem>=dis)//若拼接后rem>=除数disbeginquo=quo+1; //商值自加1rem=rem-dis; //新余数变为旧余数减除数endendendend//结束endmoduleTesebench如下 :`timescale 1ns/1nsmodule divider_bench;reg [7:0] did;reg [3:0] dis;wire [7:0] quo;wire [7:0] rem;integer i;//整数,用于控制被除数变化integer j;//整数,用于控制除数变化divider_8_4 d1(did,dis,quo,rem,error); //实例化initialbeginfor(i=0;i<=255;i=i+1)//被除数从0到255begindid=i;for(j=0;j<=15;j=j+1)//除数从0到15变化#1 dis=j;endendinitialbegin$monitor($time,"divident=% divisor=%d quotient=%dremainder=%d",did,dis,quo,rem) ;endinitialbegin#1000 $finish;// 1000ns 时停止仿真endendmodule四、实验结果与数据处理1.Modelsim 仿真结果,波形图,代码覆盖率图等为了严谨 ,把所有的数值都测了一遍 (did 从 0 到 255,dis 从 0 到 15),从modeldim 仿真结果看到程序的正确性 ,鉴于数据较多这里只选择几组数据给予展示 :上图中从上到下一次代表被除数,除数 ,错误 ,商和余数 ,当被除数是 4.除数分别是 9,10,11,12,13,14,15时商为 0,余数分别 9,10,11,12,13,14,15.当被除数为 147,除数分别为 1,2,3,4,5,6,7时 ,商分别为 147,73,49,36,29,24,21,余数分别为 0,1,0,3,2,3,0结.果正确 .由上图可见代码覆盖率已达100%,非常好 .2.综合结果,布局布线结果,关键路径,资源利用率等。

verilog除法计算方法

基于Veri log计算精度可调的整数除法器的设计时间:2009-05-07 10:32:52 来源:现代电子技术作者:贵州省光电子技术及应用重点实验室叶显阳,张海勇,皮代军,秦0 引言除法器是电子技术领域的基础模块,在电子电路设计中得到广泛应用。

目前,实现除法器的方法有硬件实现和软件实现两种方法。

硬件实现的方法主要是以硬件的消耗为代价,从而有实现速度快的特点。

用硬件的方法来实现除法器的研究很多,如利用微处理器实现快速乘除法运算,FPGA实现二进制除法运算,模拟除法器等;而通过软件实现的除法器算法,可以大大提高器件的工作频率和设计的灵活性,可以从总体上提高设计性能,而设计高效实用的算法是除法器的关键,故除法器的算法研究成为现今热点。

目前,软件方面主要是通过减法算法来实现除法运算,把被除数作为被减数,除数作为减数,作减法,直到被减数小于减数为止,记录能够相减的次数即得到商的整数部分。

将所得的余数乘以10作为被减数,除数作为减数,作减法,差重新置入被减数,反复相减,直到被减数小于减数为止,记录能够相减的次数即得到商的十分位数值。

依此继续下去,可得到商的百分位数值,千分位数值,……,要精确到哪一位,就依次做到哪一位。

此方法的缺点是速度慢,而且最后一位的精度不高,为了克服以上的缺点,这里设计一种算法在软件上改进了除法器运算的准确性和处理速度。

1 设计方法对于任意给定的两个整数fenzi和fenm u,设fenzi为被除数,fenmu为除数。

为了得到两个数相除的十进制结果,本设计主要通过下面的算法来实现,假如要保留小数点后面的n 位有效数字,首先把fen zi乘以10的n次方,赋值给寄存器变量dat aO;接着把fen mu分别乘以10的(n+m),(n+m一1),(n+m一2),…,1,O次方分别赋值给(n+m+1)个不同的变量data(n+m+1),data(n+m),…,datal,其中m是fe nzi和f enmu的位数之差(当fenzi 的位数多于fenmu时,m为正,否则为负);先求出商的最高位的值,如果data O大于da ta(n+m+1),则计数器自动加1,再把data O和dat a(n+m+1)的差值赋给d ata0,再相减直到d ata0的值小于da ta(n+m+1),此时计数器的计数值就是最高位的值;依此用同样的方法继续下去,就可得到各个位上的值。

verilog参数除法

Verilog参数除法1. 引言Verilog是一种硬件描述语言,用于设计和验证数字电路。

它广泛应用于FPGA和ASIC设计中。

本文将讨论在Verilog中实现参数除法的方法。

2. 参数除法的需求在数字电路设计中,除法运算是非常常见的操作。

然而,由于除法运算的复杂性,Verilog中并没有内置的除法运算符。

因此,需要使用其他方法来实现参数除法。

3. 方法一:利用乘法和移位运算一种实现参数除法的方法是利用乘法和移位运算。

该方法基于以下原理:除法可以通过连续减法来实现,而连续减法可以通过乘法和移位运算来实现。

3.1 算法描述以下是参数除法的算法描述:1.将被除数和除数加载到两个寄存器中。

2.判断被除数是否为0,如果是,则结果为0。

3.通过乘法和移位运算将除数左移,直到它大于被除数。

4.将除数右移一位,并将结果累加到商中。

5.重复步骤3和4,直到除数小于被除数。

6.返回商作为结果。

3.2 Verilog实现以下是使用Verilog实现参数除法的代码示例:module param_divider (input [31:0] dividend,input [31:0] divisor,output [31:0] quotient);reg [31:0] dividend_reg;reg [31:0] divisor_reg;reg [31:0] quotient_reg;reg [31:0] remainder_reg;reg [31:0] shift_reg;always @(*) begindividend_reg = dividend;divisor_reg = divisor;quotient_reg = 0;remainder_reg = 0;shift_reg = 0;if (dividend_reg == 0) beginquotient_reg = 0;end else if (divisor_reg == 0) beginquotient_reg = 0;end else beginwhile (divisor_reg >= dividend_reg) begindivisor_reg = divisor_reg >> 1;shift_reg = shift_reg + 1;endwhile (shift_reg > 0) beginif (dividend_reg >= divisor_reg) begindividend_reg = dividend_reg - divisor_reg;quotient_reg = quotient_reg + (1 << (shift_reg - 1));enddivisor_reg = divisor_reg >> 1;shift_reg = shift_reg - 1;endendquotient = quotient_reg;endendmodule4. 方法二:利用查找表另一种实现参数除法的方法是利用查找表。

VERILOG除法计算方法

1 设计方法

对于任意给定的两个整数fenzi和fenmu,设fenzi为被除数,fenmu为除数。为了得到两个数相除的十进制结果,本设计主要通过下面的算法来实现,假如要保留小数点后面的n位有效数字,首先把fenzi乘以10的n次方,赋值给寄存器变量dataO;接着把fenmu分别乘以10的(n+m),(n+m一1),(n+m一2),…,1,O次方分别赋值给(n+m+1)个不同的变量data(n+m+1),data(n+m),…,datal,其中m是fenzi和fenmu的位数之差(当fenzi的位数多于fenmu时,m为正,否则为负);先求出商的最高位的值,如果dataO大于data(n+m+1),则计数器自动加1,再把dataO和data(n+m+1)的差值赋给data0,再相减直到data0的值小于data(n+m+1),此时计数器的计数值就是最高位的值;依此用同样的方法继续下去,就可得到各个位上的值。对最后一位进行四舍五入处理,当相减后的

dataO<datal时,再通过比较dataO*2是否大于datal,如果大于datal,则最后一位计数器的值加1,否则不变,最后把得到的整体值除以10的n次方,也就是小数点往左移动n位。传统除法算法由于采用多次相减的过程来实现,相减的过程耗费了大量时钟脉冲,而且对运算结果的最后一位没有进行处理;而本设计是通过采用位扩展使除数和被除数位数相同,进而对每一位进行分开处理,减少了做减法运算的次数,从而提高运算速度;同时采用四舍五入的方法对运算结果进行处理,提高准确性。上面算法是一种顺序方式,用Verilog硬件描述语言很容易实现,图1为流程图,其中假定fenzi为3位的整数,fenmu为2位的整数,

verilog负数除法

Verilog负数除法介绍在Verilog中实现负数除法是一个常见的应用,尤其在数字信号处理领域。

负数除法是指对两个负数进行除法运算,得到一个带符号的结果。

本文将介绍如何在Verilog中实现负数除法的基本原理和具体实现方法。

负数除法的原理负数除法是通过将被除数和除数转换为二进制补码表示形式来实现的。

具体步骤如下: 1. 将被除数和除数转换为二进制补码。

2. 对转换后的数进行除法运算。

3. 如果最高位为1,表示结果为负数,则将结果转换为十进制补码形式。

Verilog实现负数除法的方法步骤1:将被除数和除数转换为二进制补码为了对负数进行运算,首先需要将负数转换为二进制补码形式。

转换的方法如下:1. 将负数的绝对值转换为二进制形式。

2. 反转二进制数的每一位,即0变为1,1变为0。

3. 对反转后的二进制数加1,得到二进制补码。

步骤2:进行除法运算在Verilog中,除法运算可以通过被除数与除数的乘法逆运算来实现。

具体步骤如下: 1. 将被除数与除数转换为二进制补码形式。

2. 对转换后的数进行乘法运算。

3. 得到乘法运算的结果,即商。

4. 如果最高位为1,表示结果为负数,则将结果转换为十进制补码形式。

步骤3:转换结果为十进制补码形式在Verilog中,负数的结果通常使用十进制补码形式表示。

转换的方法如下: 1. 如果最高位为1,表示结果为负数。

2. 反转结果的每一位,即0变为1,1变为0。

3. 对反转后的二进制数加1,得到负数的十进制补码形式。

Verilog负数除法的代码实现下面是一个用Verilog实现负数除法的简单示例代码:module negative_division (input signed [7:0] dividend,input signed [7:0] divisor,output signed [7:0] quotient);assign quotient = dividend / divisor;endmodule总结通过本文的介绍,我们了解了在Verilog中实现负数除法的原理和具体方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

西北工业大学 《FPGA 技术实验》

实验报告二 (高效除法器)

微电子学 2011.10.12 毅字楼335

西北工业大学

学 院 学 号 姓 名 专 业 实验时间 实验地点 指导教师

软件与微电子学院

Start

为了能清楚的展示以上算法我们看下面例子:为了简单期间我们假设被除数

(did)是4位,除数(dis)是2位,商(quo)是4位,余数(rem)是4位,设did=0110,dis=10,我们来看看是怎么执行的•首先余数和商都清零,即rem=0,quo=0;把被除数的最高位0拼接到rem的最低位,此时rem=0000B,由于rem小于除数dis=10,则商quo[3]=0;下面进行第二次计算,把did[2]拼接到rem 最低位,此时rem=0001,dis=10>rem,故

quo[2]=0;继续计算,把did[1]拼接到rem 最低位,此时rem=0011,dis=10<rem,故

quo[1]=1,rem=rem-quo=0011-10=0001; 进行最后一轮运算,把did[0] 拼接至U rem 最低位,此时rem=0010,dis=10=rem.

因此quo[0]=1,rem=rem-dis=0010-10=0000,至此我们已计算元毕商quo=0011, 余数rem=0000;计算简单快速.

2. 测试平台设计

模块设计

'timescale 1ns/1ns

module divider_8_4(did.

dis,

quo, // Quotie nt

rem, // Rema inder

error //

);

parameter M=7;

parameter N=3; //

in put [M:0] did;

in put [N:0] dis;

output [M:0] quo;

output [M:0] rem;

output error;

reg [M:0] quo;

reg [M:0] rem;

reg error;

in teger i;

always (did or dis) // // Divide nt 被除数

// Divisor 除数

商

余数

错误,如果除数为0.则error置1

// 被除数,余数,商的位数

除数的位数

// 整数,用于计数

被除数,除数

beg in

quo=0;

rem=O; // 开始余数和商清零

if(dis==O)

error=1; // 若除数为0则显示错误else if(did<dis) // 为了提高效率,在被除数小于除数时beg in // 商0,余数为除数

rem=dis;

quo=0;

error=0;

end

else

beg in

error=O;

for (i=8;i>0;i=i-1) // 循环8次

beg in

rem={rem[M-1:0],did[i-1]}; //把did[i-1] 连接到rem后

quo=quo<<1; // 商左移一位

if(rem>=dis) // 若拼接后rem>=除数dis

beg in

quo=quo+1; // 商值自加1

rem=rem-dis; // 新余数变为旧余数减除数

end

end

end

end // 结束en dmodule

Tesebench 如下:

'timescale 1ns/1ns

module divider_be nch;

reg [7:0] did;

reg [3:0] dis;

wire [7:0] quo;

wire [7:0] rem;

in teger i; //

in teger j; // divider_8_4 d1(did,dis,quo,rem,error); // 整数,用于控制被除数变化整数,用于控制除数变化实例化

in

itial beg in

for(i=0;i<=255;i=i+1) beg in

did=i;

for(j=0;j<=15;j=j+1)

#1 dis=j;

// 被除数从0到255

// 除数从0到15变化

end

end in itial

beg in

$mon itor($time,"divide nt=% divisor=%d quotie nt=%d remai nder=%d",did,dis,quo,rem);

end

in itial

beg in

#1000 $fini sh; // 1000ns 时停止仿真

end

en dmodule

四、实验结果与数据处理

1. Modelsim仿真结果,波形图,代码覆盖率图等

为了严谨,把所有的数值都测了一遍(did从0到255,dis从0到15),从modeldim仿真结果看到程序的正确性,鉴于数据较多这里只选择几组数据给予

展示

:

上图中从上到下一次代表被除数,除数,错误,商和余数,当被除数是4.除数分别是9,10,11,12,13,14,15 时商为0,余数分别9,10,11,12,13,14,15.

wave -

default

当被除数为147,除数分别为123,4,5,6,7

时,商分别为

147,73,49,36,29,24,21, 余数分别为 0,1,0,3,2,3,0.

结果正确.

啊血

^TB_bndi

I EE I Medic

4«t=liT (r

+ J JI Modi 'To 如

4 NMTklf 血由如1则Fhtts-

由上图可见代码覆盖率已达100%,非常好.

2.综合结果,布局布线结果,关键路径,资源利用率等。

由于过程简单,布局和布线基本用到很少,,关键路径主要在testbench 中开 始赋初值的时间和除数被除数的正确输入,程序简单明了资源利用率较高。

五、分析与讨论

1.电路的功能是否正确,仿真是否充分,如何进一步提高代码覆盖率

/dMdef bench/dkj

上 * /dividef berwh/dis

O /dividei_bench/erroi 2;;^

7divi£ler_bench/quo +;

'J -

147 147

0 (o :

1

立

3 14

!

5

16

1__I!

1

a

(0

147

173

4S I3E

29

124

:2i r

(0

0 13

;

2 13

阳耶帅口阡剳片 初tmiri 扫广円沁勿齢£刑々刘jipr B 咐av 电划计诞 駅时临那師吩9 Mr 列唧1

•局惟。