数字低频倍频器的设计与实现

数字低频滤波器的设计与仿真

【4】伍小芹,王萍,易家傅.基于DSP-TMS320C5402的FIR数字 滤波嚣设计及实现【J】.海南大学学报(自然科学版),2007(04).

【5】陈敏歌.基于窗函数法的FIR数字滤波嚣的设计【J】.陕西师范 大学学报(自然科学版),2007(¥2).

【6】廖晓辉,秦毅男.基于ActiveX技术的数字滤波器设计【J】.微 计算机信息,2007(34).

频率特性作某种近似的基础上的。这些方法有窗函数法、频 率抽样法以及最佳一致逼近法。

本文主要介绍窗函数设计法。它的基本原理是用一定宽 度窗函数截取无限冲激响应序列以获得有限长的脉冲响应 序列,主要设计步骤为:通过傅里叶逆变换获得理想滤波器 的单位脉冲响应hd(n);由性能指标确定窗函数w(n)和窗口 长度N;求得实际滤波器的单位脉冲响h(n),h(n)即为所设 计FIR滤波器系数向量b(n);检验滤波器性能。

2.数字滤波器的设计方法

数字滤波器是一种用来过滤时间离散信号的数字系统, 它是通过对抽样数据进行数学处理来达到频域滤波的目 的。数字滤波器可以用软件或设计专用的数字处理硬件两 . 种方式来实现。用软件来实现数字滤波器优点是:随着滤波 器参数的改变,很容易改变滤波器的性能。

目前,FIR DF的设计方法主要是建立在对理想滤波器

m

y(nt)=乞h(nT)x(nT--kT)

k=0

(o.6)

由公式(1.6)得到的FIR滤波器的输出为有限长度的在 单位抽样响应作用下过去输入与当前输入的加权和。由有6

个分支的FIR结构计算,使用以下关系式:

y(n)=x(n)h(0)+x(n--1)h(1)+……x(n--5)h(5) (0.7) 图3显示了具有6个分支的直接型FIR滤波器的网络

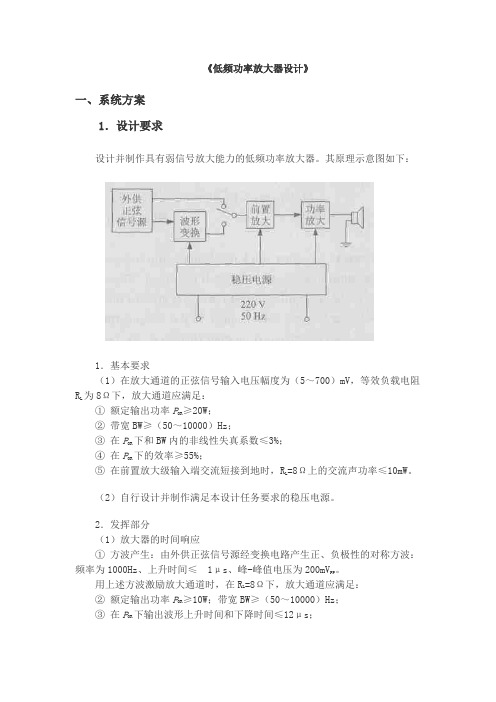

《低频功率放大器设计》

《低频功率放大器设计》一、系统方案1.设计要求设计并制作具有弱信号放大能力的低频功率放大器。

其原理示意图如下:1.基本要求(1)在放大通道的正弦信号输入电压幅度为(5~700)mV,等效负载电阻为8Ω下,放大通道应满足:RL①额定输出功率P OR≥20W;②带宽BW≥(50~10000)Hz;③在P OR下和BW内的非线性失真系数≤3%;④在P OR下的效率≥55%;=8Ω上的交流声功率≤10mW。

⑤在前置放大级输入端交流短接到地时,RL(2)自行设计并制作满足本设计任务要求的稳压电源。

2.发挥部分(1)放大器的时间响应①方波产生:由外供正弦信号源经变换电路产生正、负极性的对称方波:。

频率为1000Hz、上升时间≤1μs、峰-峰值电压为200mVpp用上述方波激励放大通道时,在R=8Ω下,放大通道应满足:L②额定输出功率P OR≥10W;带宽BW≥(50~10000)Hz;③在P OR下输出波形上升时间和下降时间≤12μs;④在P OR下输出波形顶部斜降≤2%;⑤在P OR下输出波形过冲量≤5%。

(2)放大通道性能指标的提高和实用功能的扩展(例如提高效率、减小非线性失真等)。

2、主要电路的设计与计算1.功率放大级电路设计当功率放大器以的满功率不失真输出时,输出电压的幅度为为留有充分的余地,取.由此可以计算功率放大器的总电压增益,即用分贝表示,功率放大级电路可直接选用集成功率放大器,也可以选用分离元件来组成,但是由于集成功率放大级的调节往往达不到目的,故选用由分离元件晶体管组成的功率放大电路,电路图如下所示:其中、组成差分放大器,如果电路的参数完全对称则电路具有很高的共模抑制比,可以克服由温度变化引起的静态工作点的漂移。

晶体管组成电压放大器,为末级功率放大电路提供驱动电压。

晶体管、、、组成末级功率放大电路,输出端为互补对称的OCL电路。

这3级之间采用直流耦合,并引入直流负反馈,电压增益为反馈电阻决定,即。

低频数字信号发生器的设计

低频数字信号发生器的设计学校:昆明理工大学专业:电子信息工程姓名:指导教师单位:昆明理工大学指导教师姓名:指导教师职称:讲师The Design of Digital SignalGenerator of Low FrequencyUniversity: Kunming University of Science and Technology Major: Electronic Information EngineeringName:Name of Advisor:Unit of Advisor: Kunming University of Science and Technology Professional Title: Lectorate目录摘要 (I)Abstract (II)第1章绪论 (1)1.1 概述 (1)1.2 设计要求 (2)第2章设计的整体构思 (3)2.1 输入输出电路的构思 (3)2.3 软件设计的构思 (4)2.3.1 幅度控制 (4)2.3.2 频率控制 (4)2.3.3 波形的产生 (5)2.4 本章小结 (5)第3章硬件电路设计 (6)3.1 系统总体电路图 (6)3.2 单片机最小系统 (8)3.3 单片机与DAC0832的接口技术 (10)3.3.1 DAC0832简介 (10)3.3.2 LM324功能 (13)3.3.3 DAC0832和MCS-51的接口 (14)3.4 按键及显示电路设计 (16)3.4.1 按键的设计 (16)3.4.2 显示电路的设计 (16)3.5 本章小结 (17)第4章软件部分的设计 (18)4.1 软件总体流程 (18)4.2各部分软件设计 (19)4.2.1键盘显示模块设计 (19)4.2.2波形产生模块的设计 (21)4.3 本章小结 (26)第5章系统的安装与调试 (27)5.1 系统设计的安装与调试 (27)5.2 系统的各部分调试 (27)5.2.1系统硬件调试 (27)5.2.2系统软件调试 (28)5.3 在调试过程中遇到的问题 (28)5.4 本章小结 (29)结论 (30)总结与体会 (31)致谢 (32)参考文献 (33)附一:英文翻译 (34)摘要各种各样的信号是通信领域的重要组成部分,其中正弦波、锯齿波和方波等是较为常见的信号。

单片数字锁相倍频电路的设计与实现

= Tin N

=

M N

ççèæ

12 f clk

÷÷øö

刘俊丰:硕士研究生

(3) 利用定时器 T1 实现倍频方波信号输出:置定

电 话 :010-62132436 ,62192616(T/F ) 《 嵌入式系统应用精选 200 例》

中国自控网:http://www.a utocontrol.cn

邮局订阅号:82-946 120 元 / 年 - 153 -

INT0 上升沿到来之际,启动定时器 T0 开始对内部时 钟(振荡频率的 1/12)进行计数,在下一个 INT0 上升 沿到来之后,关闭定时器 T0,读取计数值 M,并启动下 一次定时过程。输入信号周期为:

Tin

=

M ççèæ

12 f clk

÷÷øö

(2) 确定倍频输出信号周期,设倍频数为 N,则

Tout

(投稿日期:2004.12.20) (修稿日期:2004.12.28)

欢迎订阅 欢迎刊登广告

中国自控网:http://www.a utocontrol.com.cn

- 154 - 120 元 / 年 邮局订阅号:82-946

电 话 :010-62132436 ,62192616(T/F ) 《 P LC 技术应用 200 例》

上述过程循环执行,不断测量当前输入信号周 期,及时更新倍频定时器 T1 的计数初值,即可实现倍 频输出信号频率随输入信号频率的变化而相应变化, 但保持倍频数不变。为了保证倍频的正确实现,系统 振荡频率 fclk、输入信号频率 fin 和分频数 N 之间应满足 下式关系:

10 £ fclk ´ 1 £ 256 fin 2N

(西安理工大学)刘 俊 丰 同 向 前

数字式低频信号发生器的软件设计

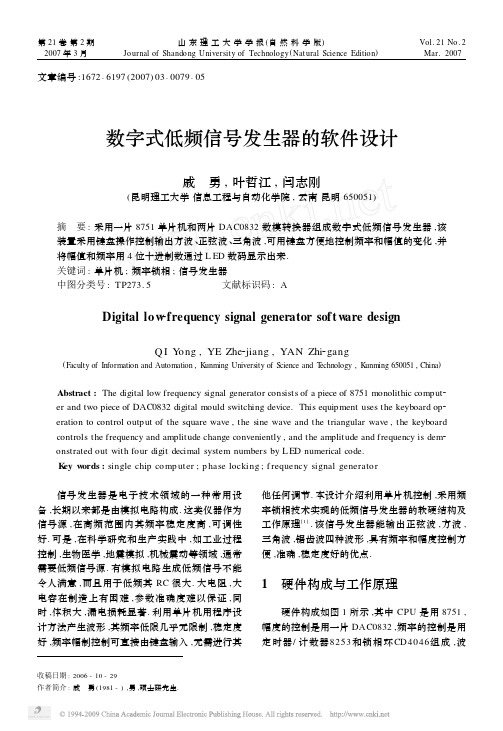

第21卷第2期2007年3月山东理工大学学报(自然科学版)Journal of Shandong University of Technology(Natural Science Edition)Vol.21No.2Mar.2007文章编号:1672-6197(2007)03-0079-05数字式低频信号发生器的软件设计戚 勇,叶哲江,闫志刚(昆明理工大学信息工程与自动化学院,云南昆明650051)摘 要:采用一片8751单片机和两片DAC0832数模转换器组成数字式低频信号发生器,该装置采用键盘操作控制输出方波、正弦波、三角波,可用键盘方便地控制频率和幅值的变化,并将幅值和频率用4位十进制数通过L ED数码显示出来.关键词:单片机;频率锁相;信号发生器中图分类号:TP273.5文献标识码:ADigital low2frequency signal generator soft w are designQ I Y ong,YE Zhe2jiang,YAN Zhi2gang(Faculty of Information and Automation,Kunming University of Science and T echnology,K unming650051,China)Abstract:The digital low frequency signal generator consists of a piece of8751monolithic comput2 er and two piece of DAC0832digital mould switching device.This equipment uses the keyboard op2 eration to control output of the square wave,the sine wave and the triangular wave,the keyboard controls the frequency and amplitude change conveniently,and the amplitude and frequency is dem2 onstrated out with four digit decimal system numbers by L ED numerical code.K ey w ords:single chip comp uter;p hase locking;f requency signal generator 信号发生器是电子技术领域的一种常用设备,长期以来都是由模拟电路构成.这类仪器作为信号源,在高频范围内其频率稳定度高,可调性好.可是,在科学研究和生产实践中,如工业过程控制,生物医学,地震模拟,机械震动等领域,通常需要低频信号源.有模拟电路生成低频信号不能令人满意,而且用于低频其RC很大.大电阻,大电容在制造上有困难,参数准确度难以保证,同时,体积大,漏电损耗显著.利用单片机用程序设计方法产生波形,其频率低限几乎无限制,稳定度好,频率幅制控制可直接由键盘输入,无需进行其他任何调节.本设计介绍利用单片机控制,采用频率锁相技术实现的低频信号发生器的软硬结构及工作原理[1].该信号发生器能输出正弦波,方波,三角波,锯齿波四种波形,具有频率和幅度控制方便,准确,稳定度好的优点.1 硬件构成与工作原理硬件构成如图1所示,其中CPU是用8751,幅度的控制是用一片DAC0832,频率的控制是用定时器/计数器8253和锁相环CD4046组成,波收稿日期:2006-10-29作者简介:戚 勇(1981-),男,硕士研究生.形控制是用EPROM 的函数变换功能,用键盘和显示电路控制其所需数值的大小.图1 信号发生器的硬件构成1.1 信号发生器核心部分低频信号发生器的核心部分是由两片74L S161,一片2764,和一片DAC0832(U8)构成的波形发生器[2].两片74L S161接成八位二进制加法计数器,在CP 信号的作用下,从全0到全1作加1循环计数,使2764低八位地址从00H 到FF H 循环变化,从而依次选中EPROM 中256个波形参数单元,并将单元中内容及波形参数送到始终处于转换状态的DAC0832(U8)中进行D/A 转换.当CP 脉冲每达到256个时,U8便输出一个周期的完整的信号波形.显然,输出信号的周期等于CP 脉冲周期的256倍.因此,输出信号的频率f 0与CP 脉冲频率f cp 有如下关系:f 0=f cp /256(1)2764作为波形参数存储器,依次放着正弦波、方波、三角波,锯齿波4种波形量化后的参数(根据需要还可以放任意周期性波形量化后的参数).量化时,将每种波形的一个周期均按256个等间隔点进行量化.量化后的参数各占256个存储单元.各种波形的量化参数在2764中的地址单元分配如下:0000H -00FF H :正弦波波形参数;0100H -01FF H :方波波形参数;0200H -02FF H :三角波波形参数;0300H -03FF H :锯齿波波形参数[3].DAC0832是含有双输入数据锁存器的D/A 数模转换器,其内部的L E 为寄存命令,当L E 为1时,寄存器的输出数据随输入变化;当L E 为0时,数据被锁存在寄存器中,而不再随数据总线上的数据变化而变化.1.2 波形控制硬件2764的地址高三位A12,A11,A10接成000,而A9,A8作为波形选择控制线由8751控制.当8751的P11,P10分别置为00,01,10,11时,信号发生器输出的分别是周期性的正弦波,方波,三角波或锯齿波.1.3 频率控制硬件频率是信号发生器最重要的性能指标,频率的控制是信号发生器的关键所在.为使信号发生器的频率准确,稳定又易于控制,频率的控制由频率锁相环电路来实现[4].频率的控制部分由8253,CD4046等构成.1.4 幅度的控制及双极性信号输出幅度控制电路由DAC0832(U3)完成,因为DAC0832输出电压与输入数字量有如下关系:V0=-(Dn/2n )×V REF ,Dn 为输入数字量,V REF 为参考电压.显然,对于波形发生器DAC0832(U8)输出的信号,其幅值等于-V REF.所以,只要改变U8的参考电压VREF ,即可以改变输出信号的幅度.由于U8的参考电压是由U3转换成的模拟电压V02提供的,所以只要改变U3输入数字量即可得到不同的输入电压值,从而改变波形发生器U8的参考电压值,实现输出波形的幅度控制.因此,对于要求输出的幅值,通过由8751的P0口的U3写入对应的数字量,即可达到控制的目的.由于A1输出到U8的基准电压V2为负值,所以A2将输出正极形波形V1.为达到输出双极性波形V0的目的,可对V1作波形变换.V0与V01的变换关系为V0=2V1-|V2|=2V1+V2.波形的变换可用运算放大器完成.1.5 按键及串行显示电路本电路设计用4个按键,分别用移位键接P3.2控制移位,用加一键接P3.3控制加一,用波形键接P3.4控制波形,用频率和幅度键接P3.5控制频率和幅度.显示电路采用4个共阴极数码管,4块74L S164集成电路和若干限流电阻组成.单片机利用串行口的0工作方式就可以将笔行码输入到4块74L S164中.由于是共阴极数码管,故74L S164的输出电平为0时,对应笔画码熄灭,为1时发光,只要输出00H 就会熄灭整个数码管.由于串行口接到数码显示的最高位,在更新显示内容时,按个位,十位,百位,千位的顺序依次输出.2 软件设计软件主要由以下几个功能模块组成:自检,初08山东理工大学学报(自然科学版)2007年 始化,判断处理及显示,幅度控制,频率控制及定时器/计数器0中断服务程序.软件的设计采用顺序设计的方法.2.1 主程序的设计在对低频信号发生器软件执行设计中,把自检初始化,判键,功能模块,执行显示等都放在主程序中,利用定时中断产生256HZ 的频率.按键的分配:P3.2用于控制移位;P3.3用于控制修改位加;P3.4波形选择控制主程序流程图如图2所示.图2 主程序流程图2.2 自检程序设计主要是一段显示程序,用以检测单片机系统是否正常工作.自检就是利用事先编好的检测程序对仪器的主要部件进行自动检测.自检中如果没发现问题,就进入测量程序,如果发现问题,则及时报警,以避免仪器带病工作.设对应四个数码管RAM 开辟四个字节显示缓冲区,用来存放四位显示内容,定义5CH ,5DH ,5EH ,5FH 存放千位,百位,十位,个位,然后从个位到千位依次输出0000-9999.2.3 初始化程序设计主要用于产成256Hz 的方波信号,包括设定中断存储器的内容以允许定时器/计数器0溢出中断,设置定时器/计数器0工作方式,预置定时器/计数器0的初值等.另外,初始化程序还要进行8253工作方式的设置.由于选用定时器/计数器0,产生256Hz 的方波即3906μs 的定时,所以送方式控制寄存器为40H ,送高八位加法计数器T H0为10H ,送低五位加法计数器为B EH .8253的地址为FBFF H ,选用8253计数器0的工作方式3,读/写两个字节,按二-十进制计数,所以送37H 到8253的地址.2.4 加一和移位功能的实现移位和加一功能,用P3.2和P3.3分别控制.移位用30H ,31H ,32H ,33H 存放千位,百位,十位,个位.移位功能:当移位键按一下时,通过对P3.2编程使数码管的位数移动一位,先用指令判断是否要移位操作,如果按下就使所加位闪烁以示所加位的位置,在调加一程序使所加位加到所需值.如果需灭零就熄灭数码管,最后调整闪烁标志位.20H.0-20H.3用于移位闪烁位标志.先设定20H.3和20H.7为1,每闪烁依次便右移一位,然后判断标志位是否设定,如果设定就使设定位闪烁.进行闪烁处理的基本方法是:一段时间正常显示,一段时间熄灭显示,相互交替就产生了闪烁的效果.因为用的是共阴极的数码管,所以先送0FF H 到所需闪烁位,然后延时一段时间,再熄灭,如此循环就可形成闪烁.移位功能流程图如图3所示.图3 移位功能流程图18第2期 戚 勇,等:数字式低频信号发生器的软件设计加1键控制:判断加一键是否按下,如果按下就延时去抖,再使所加位内容加至所需值.加1键控制流程图见图4.图4 加1键控制流程图2.5 波形控制设计A9,A8作为波形选择控制线由8751控制.当8751的P11,P10分别置为00,01,10,11时,信号发生器输出的分别是周期性的正弦波,方波,三角波或锯齿波.用50H 单元存放送往P1口的内容,开始默认为正弦波,并送00H 到P1口,当键P3.4按一次便加一送往P1口,使波形变化.波形用P3.4键控制,依次输出正弦波,方波,三角波,锯齿波.波形控制流程图如图5所示.图5 波形控制流程图2.6 幅度控制和频率控制设计根据键盘输入的幅度值,计算出对应的数字量,输出到U3并启动D/A 转换,实现对幅度的控制.将键盘输入的频率值N 作为初值写入8253,实现对频率的控制.其控制用P3.5控制.当P3.5键按奇数下时是幅度控制,并用标志位7F H =1表示,按偶数下时是频率控制,用7F H =0表示.幅度和频率的显示用个位小数点区别,即2A H.0存放其内容.用24H.0存放修改标志位.幅度控制和频率控制总流程图如图6所示.图6 幅度控制和频率控制总流程图幅度控制幅度控制方法是根据公式D n =V 0/5×255编程先使输入的幅值和51转换为16进制,然后相乘.再把乘后的16进制转化为BCD 码,小数点左移3位,再转化为16进制,最后输出.可以看出这种方法比较麻烦,所以采用简单的近似方法.最大幅度为5000mv ,转化后的数字量为D n =V 0/5000×255≈(V 0/10)/2.因为DAC0832的分辨度为19.5mv ,输入的数值单位是V ,所以以mv 为单位个位就无意义,只需取所得键盘写入的BCD 码高三位转化为16进制存于原地址,然后右移一次,最后把转化的数字量由DAC0832输出就可以控制幅度.输入的双字节BCD 存于60H 和61H .因为最大为5V ,存在的16进制不会超过一个字节,所以最后压缩到62H 输出.幅度控制流程图如图7所示.频率控制频率是信号发生器中最重要的指标,频率的控制是信号发生器的关键所在.为使频率准确,稳28山东理工大学学报(自然科学版)2007年 图7 幅度控制流程图定又易于控制,频率的控制由锁相环来实现.由硬件原理可知,在CP 脉冲的作用下,两片74L S164接成八位地址从全0到全1做加一循环计数,从而2764从低八位地址从00H 到FF H 循环变化.每当CP 脉冲到256个时便输出一个完整的信号波形.依次,输出信号的频率f 0与CP 脉冲频率f cp 有如下关系:f 0=f cp /256(1)通过CD4046锁定频率后,CD4046压控振荡器的输出频率为:f vout =256×N (2),由于CD4046压控振荡器的输出是作为波形发生器中同步八位二进制计数器的CP 信号.所以,由(1),(2)二式可得信号发生器的输出脉冲频率为f 0=N ,又因为8253在此处做除N 分频器,N 为可编程预置分频数,即由单片机写入8253的计数常数[4].频率控制流程图如图8所示.2.7 定时器/计数器0中断服务程序执行重赋定时器/计数器0的操作,并对P12取反,以实现在P1.2引脚输出256HZ 的方波信号.图8 频率控制流程图3 结论本设计采用一片8751单片机和两片DAC0832数模转换器做成的数字式低频信号发生器,它的特点是价格低、性能高,在低频范围稳定性好、操作方便、体积小、耗电少等.该装置采用键盘操作控制输出方波、正弦波、三角波,可用键盘方便地控制频率和幅值的变化,并将幅值和频率用四位十进制数通过L ED 数码显示出来[5].参考文献:[1]黎国栋.信号发生器专业基础知识问答[J ].上海计量测试,2004,(5):72274.[2]蒋 宏,赵志宏,郭 志.基于C8051F 系列单片机信号发生器设计[J ].现代电子技术,2006,(23):80283.[3]张 震,张山钟.存储器在函数发生器中的应用[J ].郑州大学学报(工学报),2002,23(4):50253.[4]杨志国.脉冲销相技术及其应用[J ].无线电通信技术,2002,(4):47248.[5]沈红卫.单片机应用系统设计实例与分析[M ].北京:北京航空航天大学出版社,2003.38第2期 戚 勇,等:数字式低频信号发生器的软件设计。

低频小信号放大器电路设计.

摘要低频小信号放大器电路设计摘要实用性低频小信号放大器电路设计,它主要用于使用前置放大器的低频小信号的电压经过集成块LM358的放大使其增益二十几倍,达到信号放大的作用,本文介绍了其基本原理,内容,与低频放大微弱信号放大能力的技术路线,设计电路图方案等。

本系统是基于(IC)LM358设计而成的一种低频小信号放大器,整个电路主要由稳压电源,前置放大电路,波形变换电路3部分。

电源主要是为前置放大器提供稳定的直流电源。

前置放大器主要是由ML358一级放大电路和ML358二级放大电路组成,第一级可以将电压放大5倍,第二级可以放大1-5倍,总增益20-25倍,接通电源后,信号发生器产生信号,示波器用于变换的波形显示。

通过波形的数据变化,计算出增益效果,是否满足设计需求。

该设计的电路结构简单,实用,充分利用了集成功放的优良性能。

实验结果表明,前置放大器的带宽,失真,效率等方面具有较好的指标,具有较高的实用性,为小信号放大器的设计是一个广泛的思考。

关键词:低频小信号,电压放大,前置放大级电路,集成块LM358AbstractDesign of low frequencysmall signal amplifierAbstract:The utility of low frequency small signal amplifier circuit design, it is mainly used for voltage low frequency small signal using a pre amplifier after amplification integrated block LM358 has gain 20 times, achieve signal amplification effect, this paper introduces the basic principle, content, and low frequency amplification technology route of weak signal amplification ability, circuit design scheme.The system is based on (IC) a low frequency small signal amplifier LM358 designed, the whole circuit is mainly composed of a regulated power supply, preamplifier circuit, a waveform transform circuit 3 parts. The power supply is mainly to provide a stable DC power for the preamplifier. The preamplifier is mainly composed of ML358 amplifier and ML358 two stage amplifier circuit, the first stage of the voltage can be magnified 5 times, second can be magnified 1-5 times, 20-25 times of the total gain, power, signal generator generates a signal, oscilloscope is used to transform the waveform display. By the waveform data changes, calculated the gain effect, whether meet the design requirements.The design of the circuit structure is simple, practical, make full use of the excellent performance of the integrated amplifier. The experimental results show that, the pre amplifier bandwidth, distortion, has better efficiency indicators, and has higher practicability, designed for small signal amplifier is a broad thinking.Keywords:Lowfrequency smalsignal,voltage amplification,preamplifiercircuit,Integrated block LM358常州工学院延陵学院毕业设计说明书目录第1章绪论 (1)前言 (3)1.1课题研究背景 (3)1.2课题主要研究内容 (4)第2章设计方案分析 (5)2.1设计任务 (6)2.2设计分析 (7)2.2.1设计技术指标 (7)2.2.2集成块LM358的介绍 (8)2.3 LM358概述 (9)2.3.1 LM358的原理与应用 (9)2.3.2 LM358行情介绍 (10)第3章前置放大器的设置原理描述 (10)3.1总体方框图设计 (11)3.2方案设计与论证 (12)3.3前置放大电路设计 (13)3.4电压跟随器电路设计 (16)第4章软件介绍......................................................................... (17)4.1 proteus仿真软件概述 (19)第5章系统的软硬件调试 (22)5.1实验电路功能的测试 (23)5.2硬件调试 (23)5.2.1上电前的调试 (23)5.2.2 上电调试 (24)5.3各模块调试 (24)5.4整机调试 (25)第6章详细元器件清单 (25)6.1电路图汇总 (26)6.2实验仪器清单 (26)6.3实验元器件清单如下表 (27)结论 (27)致谢 (28)参考文献 (31)附录 (32)第1章绪论前言在科学研究和工程实践中,经常遇到的微伏级信号的检测有问题,如材料分析的地震波速度,测定,测量卫星信号接收器的荧光强度,红外检测的生物信号测量等。

一种0~20Hz超低频信号发生器的设计与实现.

一种0~20Hz超低频信号发生器的设计与实现1 引言雷达的天线控制系统是一个自动调整系统,其任务是使天线自动跟踪目标。

目标(例如:飞机等)在空间瞬时坐标的倍息,就是雷达天线控制系统的输入量。

要实现对雷达天线控制系统的性能测试,必须对目标信息进行模拟,为此,我们设计了一种单片机控制下的超低频信号发生器,用其产生频率和幅度都能改变的正弦信号模拟不同的目标信息。

该超低频信号发生器采用了主一从式双CPU结构,通过串行通信方式将两个CPU联系起来。

从CPU控制产生0~20Hz频率变化的正弦信号,主CPU控制所产生信号的幅度,并且充分地利用了单片机强大的程序控制和计算功能,采用查表的方法利用软件生成了正弦信号,从而大大地节省了硬件开销,动态地实现了目标信息的模拟。

2 超低频信号发生器硬件组成及工作过程超低频信号发生器的硬件结构框图如图1所示。

三要由以下部分组成:①双机通信部分:实现主从CPU的串行通信。

②D/A转换电路;把8031从单片机送来的正弦二进制数码变成正弦电压,其幅度由D/A转换器2所输出的参考电压控制。

③正弦信号的幅度控制电路:在8031主单片机控制的控制下产生一定幅度范围内的参考电压。

④功率放大z把D/A变换送来的正弦电压进行功率放大,驱动雷达天线转动。

其工作过程是:由从CPU查询频率存储单元(存放信号频率值),并开始执行信号生成程序,通过D/A转换器1和两级运算放大器,将数字量变成模拟量,从而得到超低频的正弦信号,其正弦信号的幅度控制由主CPU控制D/A转换器l的参考电压,从而实现正弦信号幅度的控制,正弦信号的频率通过主一从CPU的串行通信由主CPU预置到从CPU的频率存储器单元。

3 超低频信号发生器的硬件电路设计3.1 双机通信部分超低频信号发生器由两个CPU控制,主、从CPU都以MCS一51系列单片机8031为核心,配以锁存器74LS373、和EPROM27128构成单片机最小系统。

从CPU主要是产生正弦信号,经过D/A转换和运算放大器,信号形成后经过一级功率放大送到雷达天控系统的相敏检波器,其正弦信号的幅度、频率均受主CPU 的控制。

低频数字频率计设计仿真电路图及报告

数字频率计设计报告一内容提要:数字频率计是一种用十进制数字显示被测信号频率的数字测量仪器.它的基本功能是测量正弦信号.方波信号,尖脉冲信号及其他各种单位时间内变化的物理量.本文粗略讲述了我在本次实习中的整个设计过程及收获。

二设计内容及要求:要求设计一个简易的数字频率计,其信号是给定的脉冲信号,是比较稳定的。

1.测量信号:方波;2.测量频率范围: 1Hz~999Hz ;3.显示方式: 3位十进制数显示;4.时基电路由 555 定时器产生;三设计思路及原理:数字频率计由四部分组成:时基电路、闸门电路、逻辑控制电路以及可控制的计数、译码、显示电路。

由555 定时器,分级分频系统及门控制电路得到具有固定宽度T的方波脉冲做门控制信号,时间基准T称为闸门时间.宽度为T的方波脉冲控制闸门的一个输入端B.被测信号频率为fx,周期Tx.到闸门另一输入端A.当门控制电路的信号到来后,闸门开启,周期为Tx的信号脉冲和周期为T的门控制信号结束时过闸门,于输出端 C 产生脉冲信号到计数器,计数器开始工作,直到门控信号结束,闸门关闭.单稳1的暂态送入锁存器的使能端,锁存器将计数结果锁存,计数器停止计数并被单稳2暂态清零. (简单地说就是:在时基电路脉冲的上升沿到来时闸门开启,计数器开始计数,在同一脉冲的下降沿到来时,闸门关闭,计数器停止计数.同时,锁存器产生一个锁存信号输送到锁存器的使能端将结果锁存,并把锁存结果输送到译码器来控制七段显示器,这样就可以得到被测信号的数字显示的频率.而在锁存信号的下降沿到来时逻辑控制电路产生一个清零信号将计数器清零,为下一次测量做准备,实现了可重复使用,避免两次测量结果相加使结果产生错误.) 若T=1s,计数器显示fx=N(T时间内的通过闸门信号脉冲个数) 若T=0.1s,通过闸门脉冲个数位N时,fx=10N,(闸门时间为0.1s时通过闸门的脉冲个数).也就是说,被测信号的频率计算公式是fx=N/T.由此可见,闸门时间决定量程,可以通过闸门时基选择开关,选择T大一些,测量准确度就高一些,T小一些,则测量准确度就低.根据被测频率选择闸门时间来控制量程.被测信号频率通过计数锁存可直接从计数显示器上读出.在整个电路中,时基电路是关键,闸门信号脉冲宽度是否精确直接决定了测量结果是否精确.因此,可得出数字频率计的原理框图如下:四:设计分析1.时基电路其基本电路图如左:I555定时器组成的振荡器(即脉冲产生电路),要求其产生1S高电平的脉冲.振荡器的频率计算公式为:T1=(R30+R31)*C*ln2,因此,我们可以计算出各个参数通过计算确定了R30取30k欧姆,R31取10k欧姆,电容取47uF.这样我们得到了比较稳定的一秒时基信号。

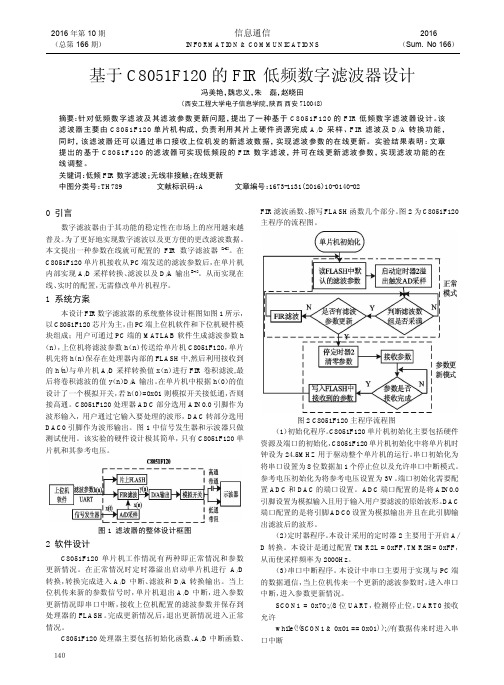

基于C8051F120的FIR低频数字滤波器设计

140基于C8051F120的FIR 低频数字滤波器设计冯美艳,魏忠义,朱磊,赵晓田(西安工程大学电子信息学院,陕西西安710048)摘要:针对低频数字滤波及其滤波参数更新问题,提出了一种基于C8051F120的FIR 低频数字滤波器设计。

该滤波器主要由C8051F120单片机构成,负责利用其片上硬件资源完成A/D 采样、FIR 滤波及D/A 转换功能,同时,该滤波器还可以通过串口接收上位机发的新滤波数据,实现滤波参数的在线更新。

实验结果表明:文章提出的基于C8051F120的滤波器可实现低频段的FIR 数字滤波,并可在线更新滤波参数,实现滤波功能的在线调整。

关键词:低频FIR 数字滤波;无线非接触;在线更新中图分类号:TH789文献标识码:A文章编号:1673-1131(2016)10-0140-020引言数字滤波器由于其功能的稳定性在市场上的应用越来越普及。

为了更好地实现数字滤波以及更方便的更改滤波数据。

本文提出一种参数在线就可配置的FIR 数字滤波器[1-2]。

在C8051F120单片机接收从PC 端发送的滤波参数后,在单片机内部实现A/D 采样转换、滤波以及D/A 输出[3-4]。

从而实现在线、实时的配置,无需修改单片机程序。

1系统方案本设计FIR 数字滤波器的系统整体设计框图如图1所示,以C8051F120芯片为主,由PC 端上位机软件和下位机硬件模块组成;用户可通过PC 端的MATLAB 软件生成滤波参数h (n ),上位机将滤波参数h (n )传送给单片机C8051F120,单片机先将h (n )保存在处理器内部的FLASH 中,然后利用接收到的h (n )与单片机A/D 采样转换值x (n )进行FIR 卷积滤波,最后将卷积滤波的值y (n )D/A 输出。

在单片机中根据h (0)的值设计了一个模拟开关,若h (0)=0x01则模拟开关接低通,否则接高通。

C8051F120处理器ADC 部分选用AIN0.0引脚作为波形输入,用户通过它输入要处理的波形,DAC 转部分选用DAC0引脚作为波形输出。

数电课程设计低频频率计

武夷学院课程设计(论文) 低频数字频率计的设计院系:武夷学院电子工程系专业(班级):09级电信(2)姓名:刘惠学号: 20094082025指导教师:范有机职称:讲师完成日期:2011 年6 月3 日武夷学院教务处制摘要《数字电子技术基础》课程设计是实践环节课程。

其目的是训练我们运用学过的数字电路的基本知识,独立设计比较复杂的数字电路的能力。

频率计是一种用十进制数字显示被测信号频率的数字测量仪器,其基本功能是测量正弦信号,方波信号,尖脉冲信号以及其他各种单位时间内变化的物理量。

而且数字频率计是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器。

它已经成为电路设计的常用原器件之一,有它不可取代的地位。

本课题要设计的是低频数字频率计,使其频率值以十进制的数在数码管上显示出来,从而可以直接的看出频率值,相对比较直观,而且误差相对较小(误差约为1%)。

本设计的数字频率计的测量范围是1HZ~9999HZ,显示的数值N是0001~9999。

关键字:整形;锁存;清零;计数;译码显示器。

目录1 概述 (4)2 设计任务及要求 (4)2.1 测量信号范围 (4)2.2 最大读数 (4)2.3 电路具有启、停控制 (4)3 系统框图及简要说明 (5)4 单元电路设计 (5)4.1 放大整形电路 (5)4.2 闸门电路 (6)4.3 时基电路 (6)4.4 逻辑控制电路 (7)4.5 计数,译码,锁存,显示电路 (7)5 安装与调试 (8)5.1 放大整形电路调试 (8)5.2 时基电路调试 (9)5.3 逻辑控制电路调试 (10)5.4 计数,译码,锁存,显示电路调试 (10)5.5 整体测试 (10)6 心得体会 (11)7 结论 (11)附录A 整机逻辑电路图 (12)附录B 元件清单 (14)附录C 参考文献 (15)低频数字频率计的设计1 概述通过信号放大与整形电路使被测频率Fx产生一个CP脉冲(闸门信号),通过时基电路产生高电平时间长度为1s低电平时间长度为0.25s方波信号。

低频功率放大器的设计与制作——功放部分

摘要 (1)英文摘要 (1)引言 (2)1 系统方案设计 (3)1.1 系统框图 (3)1.2 前置运放设计方案 (3)1.3 功率放大器设计方案 (8)2 硬件电路设计 (10)2.1 前置放大电路设计 (10)2.2 放大电路设计 (11)2.3 功率放大电路设计 (12)2.4 带阻滤波电路设计 (12)2.5 电源电路设计 (14)2.6 低频功率放大器总图 (15)3 元器件选配 (16)4 硬件电路的制作 (17)4.1 前置放大电路PCB的制作 (17)4.2 功率放大电路PCB的制作 (17)4.3 电源电路PCB的制作 (18)5 调试 (19)5.1 调试与测试所用仪器 (19)5.2 测试内容 (19)5.3 测试步骤 (19)结论与谢辞 (24)参考文献 (25)附件一原理图 (26)附件二 PCB 图 (28)附件三实物图 (29)低频功率放大器的设计与制作——功放部分信息工程学院通信网络与设备专业余国斌摘要:设计并制作一个频率信号功率放大器,它主要由前置放大电路、功率推动电路、功率放大电路、及电源电路等部分组成。

前置放大电路采用NE5532为主要芯片,功率推动级同样采用了NE5532,功率放大电路采用了场效应管IRF530/IRF530,通频带部分采用NE5532作为主体芯片。

制作出来的低频功率放大器具有输入阻抗高、失真度小、放大倍数大、输出稳定性高等特点。

关键词:放大功率运放场效应管Design and Manufacture of Low-FrequencyPower Amplifier——Amplifier Section (Major of Communication Network and Equipment,Information and Engineering College,JinHua College of Vocation And Technology, Yu Guobin)Abstract:Design and production of a frequency signal power amplifier, which is mainly from the preamplifier circuit, the power to promote the circuit, power amplifier circuit, and power circuit components. NE5532 preamplifier circuit used as the main chip, the power to promote the same level using NE5532, power amplifier circuit using FET IRF530/IRF530, pass band as the main part is NE5532 chip. Produced low-frequency power amplifier with high input impedance, distortion is small, the magnification large, and high output stability. Keywords:Zoom power FET op amp引言近年来,现代电子技术的飞速发展和家庭影院需求档次的不断提高, 人们已基本上不满足于普通的家用音响所能够提供的音质音效了,需要音质更纯正、立体声音效更佳、高低音的频率响应丰满、功能更佳智能化的影音系统。

直接数字频率合成低频信号源的设计与实现

难 以集 成 化 且 成 本 高 。间 接 合 成 法 的 核 心是 锁 相 环 技

修 改 稿 收 到 日期 :0 0—0 21 6—2 9。

第一作 者邹 尔宁 , ,9 6年 生 ,9 8年毕 业 于北京航 空 学 院分 院 自 女 15 17

术 , 了合 成 所 需 要 的频 率 , 要 采用 多种 形 式 的锁 相 为 需

Abta t Drc dgt rq ec y tei D S)fa rsa v nae f ih rslt n,p aecniuu p nf q ec w t igad sr c: i t iilf u n ysnhss( DF e a e et e d a t so g eoui u g h o h s o t o su o r un ys i hn n n e c

+ [

丑一 ,

图 1 DDF S原 理 图

Fi 1 Prncp e o g. i il fDDFS

高于其他频段 的频率 覆 盖系数 , 一般 的 R C振 荡器 或 L c振荡器都无法达到… 。随着计算机技术 的发 展 , 数

字技 术 已广 泛 应 用 于 各 类 电 子 测 量 仪 表 , 接 数 字 频 直

正 弦样本 , 需要 一 个容 量 为 2的 计 数器 , 还 以此 得 到 2

低频小信号放大器的设计

1. 设计任务及要求1.1 设计任务:运用放大器原理等知识,设计一个低频小信号放大器。

1.2 设计要求:1)放大倍数≥1000(60db);2)共模抑制比KCMR≥60db;3)输入阻抗Ri≥10M;4)频带范围0~100HZ;5)信噪比SNR≥40db;2. 方案设计2.1.1同相放大电路输入电压u i接至同相输入端,输出电压u o通过电阻R F仍接到反相输入端。

R 2的阻值应为R2=R1//RF.根据虚短和虚断的特点,可知I-=I+=0,则有oFuRRRu⋅+=-11且 u-=u+=ui,可得:ioFuuRRR=⋅+111Fiouf RR1uuA+==同相比例运算电路输入电阻为:∞==iiif iuR输出电阻: Rof=0因此选择同相放大电路满足输入阻抗足够大2.1.2 差分放大电路差动输入比例运算(即减法运算)在差动放大电路中,有两个输入端,当在这两个端子上分别输入大小相等、相位相反的信号,(这是有用的信号)放大器能产生很大的放大倍数,我们把这种信号叫做差模信号,这时的放大倍数叫做差模放大倍数。

如果在两个输入端分别输入大小相等,相位相同的信号,(这实际是上一级由于温度变化而产生的信号,是一种有害的东西),我们把这种信号叫做共模信号,这时的放大倍数叫做共模放大倍数。

由差模放大倍数和共模放大倍数可求差模增益Avd 和共模增益Acd,共模抑制比KCMR =20log(Avd/Acd)2.1.3 仪表放大器图5是仪用放大器的结构,是分离和集成仪表放大器最常选的结构。

整个增益的传输函数很复杂,当R1=R2=R3=R4时,传输函数可以简化为R5和R6设置为相同值(通常在10~50kΩ)。

简单地调节RG的值,电路的整个增益可由单位值调至任意高的值。

因此选择三运放仪用放大器满足电路的增益要求。

2.2 方案确定2.2.1 主要器件选择芯片:OP07供电电压:+12V直流稳压电源供电滤波电路:0.1uF,10u电容反馈电路电阻:10K,1K调节增益电阻:1M滑动变阻器安捷伦示波器数字万用表信号发生器2.2.1 最终电路选择使用两个运放同相输入组成第一级差分放大电路,使用第三个运放组成第二级差分放大电路,即两级共同构成了仪用放大器,在第二级接入滑动变阻器改变电路总增益。

超低频数字频率计设计与制作

摘要频率检测是电子测量领域的最基本也是最重要的测量之一。

频率信号抗干扰能力强、易于传输,可以获得较高的测量精度,所以测频率方法的研究越来越受到重视。

本课题的等精度数字频率计设计,采用当今电子设计领域流行的EDA 技术,以CPLD为核心,配合AT89C51单片机,采用多周期同步测频原理,实现了0. 1Hz-50MHz信号频率的等精度频率测量,此外,该系统还可以测方波信号宽度及高、低电平的占空比。

设计中用一块复杂可编程逻辑器件CPLD(Complex Programmable Logic Device)芯片EPM7128SLC84-15完成各种时序逻辑控制、计数功能。

在Quartus II平台上,用VHDL语言编程完成了CPLD 的软件设计、编译、调试、仿真和下载。

用AT89C51单片机作为系统的主控部件,实现整个电路的测试信号控制、数据运算处理、键盘扫描和控制数码管的显示输出。

系统将单片机AT89C51的控制灵活性及CPLD芯片的现场可编程性相结合,不但大大缩短了开发研制周期,而且使本系统具有结构紧凑、体积小,可靠性高,测频范围宽、精度高等优点。

采用常规数字电路设计数字频率计,所用的器件较多、连线比较复杂,而且存在延时较大、测量误差较大、可靠恻氏的缺点。

采用复杂可编程逻辑器件,以EDA工具为开发手段、运用VHDL语言编程进行数字频率计的设计,将在使系统大大简化的同时,提高仪器整体的性能和可靠性。

本文介绍的用FPGA实现的数字频率计,采用VHDL语言编程,用Maxplus II集成开发环境进行波形仿真、编译,并下载到FPGA中。

经测试,该系统性能可靠、测量精确,详细论述了系统自上而下的设计方法及各部分硬件电路组成及单片机、CPLD的软件编程设计。

使用以GW48-CK EDA实验开发系统为主的实验环境下进行了仿真和硬件验证,达到了较高的测量精度和测量速度。

关键词: 超低频;数字频率计;设计;;制作;AbstractFrequency detection is the most basic electronic measurement is one of the most important measurement. Frequency signal interference capability, easy to transport, access to high accuracy, so the frequency method of measuring more and more attention. The issue of equal precision digital frequency meter design, the use of today's popular electronic design EDA technology to CPLD as its core, with AT89C51 microcontroller, a multi-period synchronous frequency principle, to achieve the 0. 1Hz-50MHz frequency of Equal Frequency measurement, in addition, the system can also measure the width of the square wave signal and the high, low duty cycle. Design using a complex programmable logic device CPLD (Complex Programmable Logic Device) chip EPM7128SLC84-15 to complete a variety of temporal logic control, counting function. In the Quartus II platform, complete with VHDL, CPLD programming software design, coding, debugging, simulation, and download. With AT89C51 microcontroller as the main control system components, to achieve the test signal control circuit, data processing operations, the keyboard scanning and control of digital control of display output. AT89C51 the monolithic control system flexibility and field-programmable CPLD chip combining, the development will not only greatly reduce the development period, and Shiben system has a compact structure, small size, high reliability, frequency measurement range, high precision . Conventional digital circuit design digital frequency meter, a device used in more complicated connection, but there is a greater delay, measurement error is large, reliable and sad's shortcomings. Use complex programmable logic devices to develop means of EDA tools, VHDL language programming using a digital frequency meter design, will greatly simplify the system at the same time, improve the equipment overall performance and reliability. This article describes the use of FPGA implementation of digital frequency meter, using VHDL language programming, withMaxplus II integrated development environment for wave simulation, compiled, and downloaded to the FPGA. After testing, the system is reliable, accurate measurement is discussed in detail the system and the part of top-down design of hardware circuit and the MCU, CPLD design software programming. Use of GW48-CK EDA experimental development system-based experimental environment simulation and hardware verification, to achieve a high measurement accuracy and measurement speed.Key words: ultra-low frequency; digital frequency meter; design;; production;目录摘要 ........................................................................................................................................... - 1 - Abstract ........................................................................................................................................ - 2 - 目录 ........................................................................................................................................... - 4 - 第1章绪论................................................................................................................................ - 6 -1.1选题背景....................................................................................................................... - 6 -1.2研究内容及相关技术................................................................................................... - 7 -1.3数字频率计的硬件结构与设计思想........................................................................... - 8 - 第二章数字频率计设计原理.................................................................................................... - 9 -2.1数字频率计原理........................................................................................................... - 9 -2.2系统设计指标............................................................................................................. - 13 - 第三章硬件电路设计.............................................................................................................. - 14 -3.1系统顶层电路设计..................................................................................................... - 14 -3.1.1 CPLD的结构与功能介绍............................................................................... - 15 -3.1.2 CPLD测频专用模块逻辑设计....................................................................... - 17 -3.2单片机主控模块......................................................................................................... - 20 -3.2.1 AT89C51单片机性能..................................................................................... - 20 -3.2.2单片机控制电路............................................................................................. - 21 -3.3外围电路设计............................................................................................................. - 23 - 第四章软件设计...................................................................................................................... - 25 -4.1 Quartus II概述..................................................................................................... - 25 -4.2 Quartus 使用VHDL实现系统功能的全过程........................................................ - 26 -4.2.1电子系统的设计方法..................................................................................... - 26 -4.2.2“自顶向下”与“自底向上”的设计方法.................................................. - 27 -4.2.3 VHDL语言简介........................................................................................... - 29 -4.2.4键盘扫描、时间值输入及计数值计算子程序............................................. - 31 -第五章实验测试及误差分析.................................................................................................. - 34 -5.1实验测试的方法......................................................................................................... - 34 -5.2误差分析..................................................................................................................... - 35 - 结论 ....................................................................................................................................... - 37 - 致谢 ....................................................................................................................................... - 38 - 参考文献.................................................................................................................................... - 39 -第1章绪论1.1选题背景近年来,在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得更为重要.在电子系统非常广泛应用领域内,到处可见到处理离散信息的数字电路。

一种低成本小型化倍频组件的设计

一种低成本小型化倍频组件的设计尹红波【摘要】This paper introduces the design of a frequency multiplication subassembly based on PIN diode HSMP 3822. The design reduces the requirements of subassembly inner to filter, which makes the designed subassembly have the advantages of low cost,small size and convenient application. Test results validate that the subassembly can satisfy all of technical index requirements and the performance is perfect.%介绍了一种基于PIN二极管HSMP-3822的倍频组件的设计,该设计降低了组件内部对滤波器的要求,使得设计出来的组件成本低、体积小、使用方便。

测试结果验证了该组件满足各项技术指标要求,性能较好。

【期刊名称】《舰船电子对抗》【年(卷),期】2012(035)003【总页数】3页(P101-103)【关键词】倍频器;滤波器;雷达模拟系统【作者】尹红波【作者单位】船舶重工集团公司723所,扬州225001【正文语种】中文【中图分类】TN7710 引言随着微波技术的发展,倍频器作为一个基本的电子部件,被广泛应用于雷达、通信、电子战、频率合成器等各种电子设备中。

本文的倍频组件是为满足某雷达模拟器系统需要而设计的,通过外部一个晶体振荡器的输入,得到多个成整数倍的高稳定度、低相位噪声的倍频频率。

此组件要求体积小、成本低、性能稳定可靠[1]。

1 倍频组件的设计方案本组件技术要求如下(见图1):(1)输入频率100 MHz,功率0±1 dBm,为晶体振荡器输入。