电子万年历时钟设计

基于单片机的电子万年历设计

基于单片机的电子万年历设计一、概述随着科技的快速发展和人们对生活品质的追求,电子设备在日常生活中扮演着越来越重要的角色。

电子万年历作为一种集日期、时间显示于一体的实用电子产品,已经深入到人们的日常生活和工作中。

传统的机械式日历已经无法满足现代人对时间精确性和功能多样性的需求,基于单片机的电子万年历设计应运而生,成为了当前研究的热点之一。

基于单片机的电子万年历设计,旨在利用单片机(如STC89CAT89C51等)的强大计算和控制能力,结合液晶显示屏(LCD)、按键输入等外设,实现时间的准确显示、日期的自动更新、闹钟提醒、温度显示等多样化功能。

该设计不仅具有高度的集成性和可靠性,而且能够通过编程实现各种定制化的功能,满足不同用户的需求。

本文将对基于单片机的电子万年历设计进行详细的介绍和分析,包括设计思路、硬件组成、软件编程等方面。

通过本文的阅读,读者可以了解电子万年历的基本原理和设计方法,掌握单片机在电子万年历设计中的应用技巧,为实际的开发工作提供有益的参考和借鉴。

1.1 研究背景与意义随着科技的不断进步,人们日常生活和工作中对于时间的精度和便捷性的要求日益提高。

传统的机械式日历和简单的电子时钟已经无法满足现代生活的需求。

电子万年历作为一种集时间显示、日历查询、定时提醒等多功能于一体的电子装置,在日常生活、工作乃至科研领域都具有广泛的应用价值。

基于单片机的电子万年历设计,不仅可以提供准确的时间显示,还能实现复杂的日期计算、农历显示、节假日提示等功能,极大地提高了时间管理的效率和便捷性。

单片机作为一种集成度高、功耗低、价格适中的微型计算机,非常适合用于小型化、智能化的电子产品设计,如电子万年历。

本研究的意义在于,通过对基于单片机的电子万年历的设计研究,可以推动微型计算机技术和电子时钟技术的融合发展,提升电子产品的智能化水平,满足人们日益增长的生活和工作需求。

同时,该研究还可以为相关领域的技术人员提供参考和借鉴,推动电子万年历产品的不断创新和优化。

电子设计多功能电子万年历

多功能电子万年历摘要本设计以单片机AT89s52和时钟芯片DS1302为核心,设计了一款多功能电子万年历。

不同于单片机提供的定时计数器,DS1302时钟芯片具有涓细电流充电功能,可以对年、月、日、周日、时、分、秒进行计时,还具有闰年补偿等多种功能。

最重要的是,相对于单片机的定时计数器,DS1302在时间的读写方面误差要小很多。

设计对多功能电子万年历采用LCD12864实现数字和文字的同步显示,可以显示年、月、日、星期、时、分、秒和温度等信息,与此同时通过内部程序指令还具有时间校准功能。

关键词:时钟电钟;DS1302;DS18B20;LCD12864;单片机~~~~~~目录~~~~~~一、设计要求与方案论证 (4)1.1 设计要求 (4)1.2 系统基本方案选择和论证 (4)1.2.1单片机芯片的选择方案和论证 (4)1.2.2 显示模块选择方案和论证 (4)1.2.3 时钟芯片的选择方案和论证 (4)1.2.4 温度传感器的选择方案与论证 (5)1.3 电路设计最终方案决定 (5)二.系统的硬件设计与实现 (5)2.1 电路设计框图 (5)2.2 系统硬件概述 (5)2.3 主要单元电路的设计 (6)2.3.1单片机主控制模块的设计 (6)2.3.2时钟电路模块的设计 (6)2.3.3温度采集模块设计 (7)2.3.4 电路原理及说明 (7)2.3.5 显示模块的设计 (9)三、系统的软件设计 (10)3.1程序流程框图 (10)3.2子程序的设计 (12)3.2.1 DS18B20温度子程序 (12)3.2.2 读/写DS1302子程序 (14)3.2.3 LCD12864显示子程序 (16)四. 指标测 (19)4.1 测试仪器 (19)4.2硬件测试 (20)4.3软件测试 (20)4.4测试结果分析与结论 (20)4.4.1 测试结果分析 (20)4.4.2 测试结论 (20)五、作品心得总结 (21)六、致谢词 (22)参考文献 (22)附录一:系统电路图 (23)附录二:系统使用说明书 (24)附录三:系统程序清单 (25)一、设计要求与方案论证1.1 设计要求:(1)能显示阳历年、月、日、星期、小时、分、秒,当年是闰年是会显示闰年。

电子万年历的设计

三、硬件设计

LED数码管动态 数码管动态 扫描显示模块 AT89S52 主控制 模块 温度采集模块 键盘模块

DS1302时钟模块 时钟模块

主控制系统图

键盘模块

日期和时间的修改由3 个按键构成。 键1为向右移; 键2为加1; 键3为减1。

DS1302的引脚图

返回

ds1302内部结构

温度采集模块

谢谢大家 欣赏

数字式温度传感器DS18B20, 它是数字式温度传感器, 具有测量精度高,电路连 接简单特点,此类传感器 仅需要一条数据线进行数 据传输,使用P0.7与 DS18B20的I/O口连接加一 个上拉电阻,Vcc接电源 ,Vss接地

I/O

vss

vcc

返回

LED动态扫描显示模块 动态扫描显示模块

系统电路图

一.设计要求

具有年、 具有年、月、日、星期、时、分、秒等功 星期、 能; 时间与阴、阳历能够自动关联; 时间与阴、阳历能够自动关联; 具备年、 星期、 具备年、月、日、星期、时、分、秒校准 功能; 功能; 具有温度计功能; 具有温度计功能;

二、基本方案

采用AT89S52作为主控制系统 作为主控制系统 采用 采用DS1302提供时钟 提供时钟 采用 采用数字式温度传感器DS18B20 采用数字式温度传感器 采用LED数码管动态扫描作为显示 数码管动态扫描作为显示 采用

1.

六、总结

通过此次毕业设计, 通过此次毕业设计,我 不仅把知识融会贯通, 不仅把知识融会贯通,而且 丰富了大脑, 丰富了大脑,同时在查找资 料的过程中也了解了许多课 外知识,开拓了视野, 外知识,开拓了视野,认识 了将来电子的发展方向, 了将来电子的发展方向,使 自己在专业知识方面和动手 能力方面有了质的飞跃。 能力方面有了质的飞跃。

万年历时钟电路设计报告word精品

阿坝师范学院万年历设计报告姓名:李朝林学号:20156045 班级:电子信息工程02班阿坝师范学院物理与电子科学系目录1•设计任务与要求 (2)2•主要器件讨论与选择 (2)3.设计原理 (3)4•单元电路设计 (3)4.1显示电路 (3)4.2时分秒设计............................................. .44.3星期天数设计 (5)4.4闰年平年判断电路 (6)4.5二月与大小月判断电路 (9)4.6天数置数信号 (10)4.7校正电路 (11)4.8秒脉冲电路 (11)5.完整的电路设计原理图 (12)6.电路调试过程与方法 (13)7.实验心得体会与总结 (13)1. 设计任务与要求用数字集成电路设计万年历电子钟逻辑电路指标如下:1)设计一个能直接显示“年”“月”“日”、“星期”、“时”、“分”、“秒”的十进制万年历时钟显示器。

2)具有校时的功能,可分别对“年”、“月”、“日”、“星期”、“时” “分” “秒”进行单独校时。

2. 主要器件讨论与选择主要器件中显示模块选用74SEG_BCD数码管显示8421bcd码,计数模块统一选用74LS160作为计数芯片;74LS160具有同步置数异步清零功能,同时在有时钟脉冲的情况下进行加计数,无论采用同步置数还是异步清零都可以实现60s、60m、24h置数清零功能。

因此2/ 13[在此处键入]数字电子技术万年历设计报告3/ 1374LS160是一个不错的选择。

本次仿真通过 74LS160作为时分秒年月 日星期置数,通过秒计数的置数信号作为分计时的脉冲 cp ,取反作 为分计时的使能端,依次向高位进位达到显示目的。

通过闰年、平年、大月、小月、二月的判断电路来控制天计数的 多少。

校时电路,校时选用74LS74触发器作为跳变信号;74LS244存储 信号。

起作用的只有一个,当校时有效时计时电路无效。

3. 设计原理原理图如下:万年加时种星示器框采禺P4. 单元电路设计4.1显示电路振荡器呈期廿数楼时电路・译码显示电路疋*千 百 十个阿坝师范学院物理与电子科学系4 13整个显示电路分为年、月、日、时、分、秒、星期几大模块。

万年历电子钟设计论文

目录摘要万年历电子钟是一种非常广泛的日常计时工具,在现代社会生活中越来越流行。

它可以对年、月、日、周、时、分、秒进行计时,还具有闰年补偿等多种功能。

万年历电子钟设计是基于单片机进行的,可以显示年、月、日、时、分、秒、周及温度信息,具有可调整日期和时间功能。

设计包含STC89C52单片机模块、LED数码管模块、键盘模块、DS1302时钟模块、闹钟控制模块。

STC89C52单片机作为核心,功耗小,能在3V的低压工作,电压可选用3~5V电压供电。

LED数码管动态扫描,对于显示数字最合适,价格适中,而且采用动态扫描法与单片机连接时,占用的单片机口线少。

DS1302的使用寿命长,误差小。

对于万年历电子钟采用直观的数字显示,可以同时显示年、月、日,周日,时、分、秒等信息,还具有时间校准,闹钟,闹钟状态校准等功能。

关键词:STC89C52,DS1302,74HC164,LED数码管一.设计要求与方案论证1.1 设计要求1.1.1基本要求(1)具有年、月、日、星期、时、分、秒等功能;(2)时间与阴、阳历能够自动关联;(3)具备年、月、日、星期、时、分、秒校准功能;2. 发挥部分:(1)增加闹钟二.电子万年历硬件设计与实现2.1 电子万年历系统设计2.1.1系统设计框图2.1.2 系统硬件概述本电路是由STC89C52单片机为控制核心,具有在线编程功能,低功耗,能在3V超低压工作;本源程序采用DS1302做专用的走时,停电后也可以正常走时90天以上;本源程序充分利用了STC89C51的新功能,设定的定时控制数据可以停电10年不丢失;本程序设计了误差自动校正,如果因为晶振的误差导致一天走时快1秒或者慢1秒的话,本程序每天都会在深夜自动校正后再在正确时间基础上计时;本程序还设计了快速走时摸拟运行状态(是正常走时的100倍以上);本程序还有6位数的阳历年月日显示,既可以当日历还可以当电子钟,也有6位数字显示时间。

2.2系统硬件各模块作用2.2.1单片机主控制模块功能特性描述STC89C52是一种低功耗、高性能CMOS8位微控制器,具有 8K 在系统可编程Flash 存储器。

单片机课程设计报告电子万年历

单片机课程设计报告电子万年历单片机课程设计报告:电子万年历一、设计简介在本次单片机课程设计中,我们选择了电子万年历作为设计主题。

电子万年历是一种结合了数字电路、单片机技术和实时时钟(RTC)技术的电子产品,它具有显示年份、月份、星期、日、时、分、秒的功能,还可以根据用户的需求进行定时、闹钟、报时等功能。

二、硬件设计我们采用了基于8051内核的单片机作为主控芯片。

该单片机具有丰富的I/O 端口,适于实现各种复杂的输入输出操作。

此外,它还内置了定时器和中断控制器,可以很方便地实现实时时钟功能。

1.显示模块:为了方便用户查看时间信息,我们选用了LCD显示屏作为显示设备。

LCD屏具有功耗低、体积小、显示内容丰富等优点。

2.实时时钟(RTC)模块:我们采用了常用的DS1302芯片作为实时时钟模块。

该芯片可以提供秒、分、时、日、星期、月、年的信息,而且还有可编程的报警功能。

3.按键模块:为了实现人机交互,我们设计了一组按键。

用户可以通过按键来调整时间、设置闹钟等。

4.电源模块:为了保证系统的稳定工作,我们采用了稳定的5V直流电源。

三、软件设计我们采用了C语言编写程序。

程序主要由以下几个部分组成:1.主程序:主程序主要负责读取RTC模块的时间信息,并控制LCD显示屏显示时间。

同时,主程序还要检测按键输入,根据用户的需求进行相应的操作。

2.RTC驱动程序:为了正确地读取和设置DS1302芯片的时间信息,我们编写了相应的驱动程序。

驱动程序包括初始化和读写寄存器两部分。

3.按键处理程序:按键处理程序用于检测按键输入,并根据按键值执行相应的操作。

比如,用户可以通过按键来增加或减少时间,设置闹钟等。

4.LCD显示程序:LCD显示程序用于控制LCD显示屏的显示内容。

在本设计中,我们使用了点阵字符库,将时间信息以字符的形式显示在LCD屏上。

四、测试与验证为了确保我们的电子万年历设计正确无误,我们进行了以下的测试和验证:1.硬件测试:首先,我们对硬件电路进行了测试,确保每个模块都能正常工作。

万年历电子钟设计论文

一、引言随着科技的不断进步,人们对电子产品的需求也愈发增加。

电子钟作为一种必需品,能够准确地显示时间和日期,被广泛应用于家庭、办公室、学校等场所。

然而,传统的电子钟只能显示当前的日期和时间,功能较为简单。

为了满足人们的需求,设计一种万年历电子钟是十分必要的。

二、设计方法1.硬件设计(1)主控芯片选择:根据万年历电子钟的功能需求,选择一款性能强大的主控芯片,例如ARM Cortex-M系列的芯片,具备强大的计算和控制能力。

(2)显示屏选择:选用高分辨率的液晶显示屏,能够清晰地显示日期和时间。

考虑到用户操作的便捷性,可以选择带有背光灯的显示屏。

(3)电源设计:采用直流电源供电,可以选择使用电池或者接入市电。

对于使用电池供电的设计,需加入节电模式,提高电池使用寿命。

2.软件设计(1)显示功能:通过主控芯片控制液晶显示屏,实现日期和时间的显示。

根据数据的变化,实时更新显示内容。

(2)时钟功能:使用定时器功能,实现时钟的计时功能。

利用时钟中断,每秒更新一次时钟。

(3)日期功能:通过读取实时时钟芯片的数据,获取当前的年份、月份、日期和星期。

根据每月的天数和闰年的规则,实现日期的显示和计算。

(4)闹钟功能:通过设置闹钟选项,设置闹钟的时间和铃声。

当闹钟的设定时间到达时,发出闹铃声。

三、设计结果经过软硬件设计的整合,实现了一款功能丰富的万年历电子钟。

通过液晶显示屏,能够准确地显示当前的年份、月份、日期、星期、小时和分钟。

通过定时器功能,实现了精准的时间计时功能。

通过读取实时时钟芯片的数据,实现了准确的日期显示和计算。

同时,通过设置闹钟功能,提醒用户重要的时间节点。

四、结论本文设计了一款功能强大的万年历电子钟,能够准确地显示日期和时间,并具有闹钟功能。

通过软硬件的整合,实现了高清晰度的显示和准确的日期计算。

该设备不仅满足了人们对时间和日期的需求,还具有提醒功能,对用户的生活起到了积极的作用。

值得注意的是,该设计只是一个初始的版本,仍可以进行优化和改进,使其更加符合用户需求。

毕业设计万年历功能电子时钟的设计

摘要单片机应用技术飞速发展,纵观我们现在生活的各个领域,从导弹的导航装置,到飞机上各种仪表的控制,从计算机的网络通讯与数据传输,到工业自动化过程的实时控制和数据处理,以及我们生活中广泛使用的各种智能IC卡等,这些都离不开单片机。

单片机是集CPU ,RAM ,ROM ,定时,计数和多种接口于一体的微控制器。

它体积小,成本低,功能强,广泛应用于智能产业和工业自动化上。

而51系列单片机是各单片机中最为典型和最有代表性的一种。

这次毕业设计通过对它的学习,应用,从而达到学习、设计、开发软、硬的能力。

本文以单片机为核心,采用串行时钟芯片DS1302。

过去多用并行接口的时钟芯片,如MC146818、DS12887 等。

它们已能完全满足单片机系统对实时时钟的要求,但是这些芯片与单片机接口复杂、占用地址, 数据总线接线多、芯片体积大占用空间多。

显示电路采用LED动态扫描方式,动态扫描方式节省外部接口资源。

本文通过对一个基于单片机的能实现万年历功能电子时钟的设计,从而达到学习、了解单片机相关指令在各方面的应用。

系统由主控制器A T89C52、时钟电路DS1302、显示电路、按键电路、和复位电路等部分构成,能实现时钟日历显示的功能,能进行年、月、日、时、分及星期的显示。

关键词:AT89C52芯片DS1302芯片C语言Keil软件LED动态显示;AbstractSCM rapid development of applied technology, we now live Looking at the various fields, from the missile's navigation devices, to the various instruments on the aircraft control, computer network communications and data transmission, industrial automation to the process of real-time control and data Processing, and we live in the extensive use of the smart IC cards, these are inseparable from the SCM. S CM is set CPU, RAM, ROM, timing, counting on one interface and a variety of microcontrollers. Its small size, low cost, feature strong, smart widely used in industry and industrial automation. And 51 of the SCM SCM is the most typical and most representative one. The graduation project through its study, and thereby to study, design, develop software and hardware capabilities.Based on SCM as the core, a serial clock chip DS1302. Past the use of parallel interface chip's clock, such as the MC146818, DS12887, and so on. They have been able to fully meet the SCM system to the requirements of real-time clock, but these chips and microcontroller interface complex, occupied address, data bus wiring, chip size of the space and more. LED display circuit using dynamic scan mode, dynamic scan mode external interface save resources.Based on a microcontroller based on the calendar function to achieve the design of electronic clock, so as to achieve learning and understanding of SCM related instructions in all aspect s of the application. System by the main controller AT89C52, clock circuit DS1302, show circuit, the circuit keys, and reset circuit, and other components, to achieve the clock showed that the calendar function, capable of year, month, day, hour, minute an d weeks of shows.Key W ords:AT89C52 Chip DS1302 Chip Keil C language software LED dynamic display;目录摘要 (I)Abstract (II)目录........................................................................................................... 错误!未定义书签。

「基于单片机的多功能电子万年历设计」

基于单片机的多功能电子万年历设计引言在现代社会中,计算机及其应用已经成为我们生活中不可或缺的一部分。

计算机科技的发展不仅使我们的生活更加便捷,还为我们提供了更多的娱乐和功能选择。

在这样一个科技高度发达的时代,电子万年历作为一种基于单片机技术的应用产品,正逐渐走进人们的生活。

而本文将着重对基于单片机的多功能电子万年历进行设计与实现。

一、设计目标本次设计主要是基于单片机的多功能电子万年历。

设计目标包括:1.显示日期、时间和星期几的功能。

2.具备日历计算功能,能够计算今天是该年的第几天,该周的第几天等信息。

3.具备闹钟和定时器功能。

二、设计思路基于单片机的多功能电子万年历的设计理念是通过单片机与LCD显示屏、温度传感器、按键等外设组合实现多种功能。

具体实现步骤如下:1. 使用单片机和RTC(Real-Time Clock)芯片实现时间的获取和处理。

RTC芯片可以提供准确的时钟信息,单片机可以通过与RTC芯片的通信来读取时钟信息,并进行相应的处理。

2.使用单片机与LCD显示屏进行通信,将获取的时间、日期和星期信息显示在LCD显示屏上。

3.设计按键接口,通过按键的触发实现切换功能或进行相应操作。

例如,通过按键的触发可以实现日期、时间的调整,以及闹钟和定时器的设置等。

4.使用单片机和温度传感器实现温度测量功能。

通过温度传感器读取当前温度信息,并将其显示在LCD屏幕上。

5.使用定时器功能实现闹钟和定时器的功能。

单片机可以通过定时器来控制闹钟和定时器的开启与关闭,并通过LCD屏幕上的显示提醒用户。

三、电路设计本次设计中需要使用的元器件主要包括单片机、RTC芯片、LCD显示屏、温度传感器和按键。

其中,单片机为本次设计的核心控制器,RTC芯片用于提供准确的时钟信息,LCD显示屏用于显示时间、日期和其他信息,温度传感器用于测量当前温度信息,按键用于触发相应的操作。

四、软件设计本次设计中需要编写相应的软件程序,用于读取RTC芯片提供的时钟信息,并将其显示在LCD屏幕上。

万年历电子设计报告

河北联合大学电子时钟设计方案——非专业组学院:以升创新教育基地年级: 09级机设专业成员:杨晓高涛侯明雷2011年 04月 22日一.设计名称:电子时钟设计二.内容描述使用该芯片对LED数码管进行显示控制,实现用单片机的端口控制数码管,时间、日期和温度循环显示,并能用按钮实现调时、设置闹钟和使用秒表,可以根据外界的光线自动调节数码管的亮暗。

要求选用定时器的工作方式,画出使用单片机控制LED数码管显示的电路图,并编程完成软件部分和软件流程图,最后调试可以实现时间、日期和温度循环显示,并且可以通过按键调节时、设置闹钟和使用秒表。

三、硬件设计蜂鸣器ATmega16按键控制信号74HC59574LS138四位LED 数码管段选位 选18B20总体硬件电路图硬件设计电路分解为Megal6单片机、晶体振荡器、LED数码管显示、18B20和蜂鸣器5个部分.其结构简单,经济实惠。

Megal6单片机外部晶体振荡器的外接电路由两个30 pF的电容c1和C2、晶体振荡器Y1(8MHz)构成。

按键复位电路,Megal6是低电平复位,故将按键一端接地另一端接RESET接口。

PA口接芯片74HC138和74HC595控制LED数码管的显示,PC口控制蜂鸣器和温度传感器18B20。

PD口接三个按键,PD0口按键表示功能键,按键选择秒表和要调整的月、日、时、分和闹钟,PD1口表示闹钟开、秒表的开始暂停和数字“-”,按一下则对应的数字减一,PD2口表示秒表的复位键和数字“+”,按一下则对应的数字加一。

数码管显示电路用74HC595实现8路并口输出的扩展,占用单片机的三个端口。

编写函数,程序控制数据线,将一字节由高位到低位,依次输入,将1字节的数据由低位到高位串行输入到74HC595中,则可控制在74HC595的输出端得到并行的8位数据,即七段数码管的段码值。

用74ls138实现6路并口输出的扩展,将位选的段码值依次打入74ls138,74ls138任一时刻只有一个输出口输出低电平,对应的一位数码管被选中,扫描6次后可以实现六位数码管的显示。

多功能电子万年历设计

多功能电子万年历设计一、本文概述本文旨在探讨多功能电子万年历设计的原理、方法及其在实际应用中的价值。

我们将对电子万年历的基本概念进行简要介绍,包括其发展历程、主要功能以及与传统日历的对比。

接着,我们将详细分析多功能电子万年历的设计要素,包括硬件选择、软件编程、用户界面设计等方面,以展示其独特的功能和设计理念。

在此基础上,我们将深入探讨多功能电子万年历设计的关键技术,如时间同步技术、多语言支持、日历算法优化等,以揭示其背后的技术原理和实现方法。

我们还将对多功能电子万年历的市场需求和应用前景进行分析,以展示其在现代社会中的重要作用。

本文将对多功能电子万年历设计的未来发展进行展望,探讨其在智能化、个性化、集成化等方面的趋势和挑战。

通过本文的阐述,读者可以对多功能电子万年历设计有一个全面、深入的了解,为其在实际应用中的开发和使用提供有益的参考。

二、电子万年历的设计原理电子万年历的设计原理主要基于时间计算、显示控制和数据存储三大核心部分。

在设计过程中,我们需要考虑如何精确计算时间,如何将时间信息以清晰易懂的方式显示出来,以及如何将这些时间数据存储和处理。

时间计算是电子万年历设计的基石。

它涉及到如何准确地计算年、月、日、时、分、秒等时间单位,并且要考虑闰年、闰月等复杂的时间规则。

这通常通过内置的时钟芯片实现,该芯片能够按照预设的算法进行时间计算,确保时间的准确性和连续性。

显示控制是电子万年历设计的关键。

显示控制的主要任务是将计算得到的时间信息转化为可视化的界面,供用户查看。

这包括选择适合的显示器件(如LCD屏幕、LED数码管等),并编写相应的显示驱动程序,以确保时间信息能够清晰、准确地呈现在用户面前。

数据存储是电子万年历设计的重要组成部分。

数据存储主要负责保存用户设置的时间、日期、闹钟等信息,以便在用户关机或断电后能够恢复。

通常,这些数据会存储在内置的存储芯片中,如EEPROM或Flash芯片,这些芯片具有非易失性,能够长期保存数据。

【完美升级版】多功能电子万年历设计_毕业论文设计

论文题目:多功能电子万年历的设计学院电气工程学院多功能电子万年历设计专业:自动化姓名:指导老师:摘要随着科学技术的快速发展,纵观太阳、摆钟到现在电子钟,人类不断研究,不断创新进步。

目前,单片机技术的应用产品已经走进了千家万户。

多功能电子万年历的出现给人们的生活带来了诸多方便。

此产品是基于STC89C52RC单片机的日历显示系统,它能显示公历年、月、日,以及时、分、秒、温度、星期等信息,而且还具有调整时间,温度采集,闹钟及个性化的闹铃等功能。

系统所用的时钟日历芯片DS1302具有高性能、低功耗、接口简单的特点,使本系统电路简化,编程方便,同时功能也很强。

采用STC89C52RC单片机的万年历系统可以很好的改善传统采用模拟电路引起的计时不准确,不可靠,一致性差等问题。

此系统计时精确,价格低廉,可以广泛应用在生活,学习和工作等任何领域,并且起到重要作用。

关键词:万年历,单片机,时钟芯片,温度芯片ABSTRACTAlong with the technical fast development, time passing, to from the view sun, the pendulum clock to the present electron clock, the humanity studies unceasingly, innovates unceasingly the record. At present, the monolithic integrated circuit technology's application product already entered everyone. The electronic ten thousand calendar's appearances have brought conveniently many for people's life.This design is one based on STC89C52RC single-chip microcomputer calendar display system, it can demonstrate years, the month, the date of the Gregorian calendar, and hour, minute, second, temperature, week and so on. Moreover it has also provided the lunar calendar information, adjustable time pattern, temperature sample, alarm system, individual quarter-bell and so on. The system clock calendar DS1302 with high performance, low power consumption and simple interface features Circuit enable the system to streamline programming convenience, but also highly functional. The problems of inaccurate, unreliable, and the uniform inferior can be come up when you use the analogous circuit. However, it can be improved when you use the clock system based on STC89C52RC single-chip microcomputer. The system time accurate, low cost and can be widely applied to the life, study and work in any field, and has played an important role.Key words:The Electronic Calendar Clock, Single-chip Microcomputer, The Time Calendar Clock, Temperature Chip目录ABSTRACT (3)1 绪论 (8)1.1多功能电子万年历的研究背景与意义 (8)1.2多功能电子万年历的发展现状 (9)1.3论文研究的内容 (9)1.4 本设计进行的主要工作 (10)1.5本多功能电子万年历系统主要要实现的功能 (10)2单片机的简介 (11)2.1单片机的介绍 (11)3 方案设计与论证 (13)3.1单片机芯片设计与论证 (13)3.2 电源模块设计与论证 (14)3.3 按键控制模块设计与论证 (14)3.4 时钟模块设计与论证 (15)3.5 温度采集模块的设计与论证 (15)3.6 显示模块设计与论证 (15)4 系统的硬件设计 (17)4.1 主控芯片STC89C52RC与复位电路和时钟振荡电路 (17)4.1.1 STC89C52RC的概述 (17)4.1.2复位电路和时钟振荡电路 (19)4.2 时钟芯片DS1302接口设计和性能分析 (20)4.2.1 DS1302性能简介 (20)4.2.2 DS1302接口电路设计 (21)4.3 温度芯片DS18B20接口设计和性能分析 (25)4.3.1 DS18B20的性能介绍 (25)4.3.2 DS18B20的接口电路设计 (26)4.4 闹钟模块系统设计于性能分析 (26)4.4.1 AT24C02器件分析 (27)4.4.2 接口电路的设计 (28)4.5 LCD显示模块 (28)4.5.1 LCM1602的特性及使用说明 (28)4.5.2 LCM1602与STC89C52RC单片机的接口电路 (30)4.6 按键模块设计 (31)4.7蜂鸣器设计 (32)5 软件设计 (34)5.1 软件总体部分的设计 (34)5.2 LCD驱动及液晶显示 (36)5.3 按键识别及处理 (36)5.4 温度数据采集 (36)5.5 时间数据采集 (38)5.6 闹钟程序 (40)6 系统的测试 (42)总结 (45)致谢 (46)参考文献 (47)附录 (48)1 绪论1.1多功能电子万年历的研究背景与意义伴随着单片机和电子技术的快速发展,人类不断研究,不断创新纪录。

数字电子万年历 时钟电路设计 毕业设计

摘要在当代繁忙的工作与生活中,时间与我们每一个人都有非常密切的关系,每个人都受到时间的影响。

为了更好的利用我们自己的时间,我们必须对时间有一个度量,因此产生了钟表。

钟表的发展是非常迅速的,从刚开始的机械式钟表到现在普遍用到的数字式钟表,即使现在钟表千奇百怪,但是它们都只是完成一种功能——计时功能,只是工作原理不同而已,在人们的使用过程中,逐渐发现了钟表的功能太单一,没有更大程度上的满足人们的需求。

因此在这里,我想能不能把一些辅助功能加入钟表中去。

在此设计中所设计的钟表不但具有普通钟表的功能,它还能实现一个额外的功能:温度测量。

且数字电子万年历采用直观的数字显示,可以同时显示年、月、日、周日、时、分、秒和温度等信息,还具有时间校准等功能。

该电路采用AT89C52单片机作为核心,功耗小,能在3V的低压工作,电压可选用3~5V电压供电.。

具有较高的实用性。

关键词:单片机AT89C52;万年历; DS18B20温度传感器;时钟芯片DS12C887AbstractIn contemporary work and busy life, time and every one of us has a very close relationship, each person affected by time. In order to better use of our own time, we must have a measure of time, resulting in a watch. Clocks is a very rapid development, from the beginning of the mechanical watches that is now widely used in digital watches, clocks, even though it is now unusual, but they are just completed a feature - a time function, working principle is different in people's use of the process, and gradually found a single watch function too, there is no greater demand to meet the people. So here, I would like to be able to watch a number of auxiliary functions to join in to.In the design of the watches designed not only has the general functionality of watches and clocks, it can achieve an additional function: temperature measurement. And digital electronic calendar using intuitive digital display, you can also display year, month, day, weekdays, hours, minutes, seconds and temperature information, but also time-calibration functions. AT89C52 single-chip microcomputer of the circuit as the core of power in small, low-pressure in the work of 3V, voltage can be selected 3 ~ 5V supply voltage.. Have a high relevance.Key words:single-chip microcomputer AT89C52; calendar; DS18B20 temperature sensor; clock chip DS12C887目录绪论 (1)1. 方案设计 (2)1.1 课题开发背景 (2)1.2 设计的目的 (2)1.3 设计的意义 (3)1.4 国内外发展 (3)1.5 总体方案论证与选择 (3)1.6 模块方案论证与选择 (4)1.6.1 时钟模块 (4)1.6.2 键盘模块 (4)1.6.3 显示模块 (5)1.6.4 温度传感器模块 (5)2. 系统总体设计 (6)2.1 电路设计框图 (6)2.2 系统硬件概述 (7)2.3 单片机AT89C52功能介绍 (7)2.4 时钟模块设计 (13)2.5 温度采集模块 (16)2.6 显示模块 (22)2.7 电源电路部分 (26)2.7.1 电路组成 (26)2.7.2 三端稳压集成电路7805 (27)2.8 键盘部分 (28)2.9 报警模块 (30)2.9.1 报警电路 (30)2.9.2 NE555芯片 (30)结论与展望 (32)结论 (32)单片机的发展趋势 (32)致谢 (33)参考文献 (34)附录一 (35)绪论电子钟已成为人们日常生活中必不可少的物品,广泛用于个人家庭以及车站、码头、剧院、办公室等公共场所,给人们的生活、学习、工作、娱乐带来极大的方便。

万年历 电子钟 毕业设计正文

1. 综述1.1 课题背景1.1.1 概述随着电子技术的迅速发展,特别是随着大规模集成电路的产生而出现的微型计算机,给人类生活带来了极大的方便。

走入家庭,从洗衣机、微波炉到音响、汽车,到处都可以见到单片机应用的踪影。

如果说微型计算机技术的出现使现代科学研究得到了质的飞跃,那么也可以毫不夸张的说:“单片机技术的出现则是给现代工业测控领域带来了一次新的工业革命”。

目前,单片机以其可靠性高和智能性等特点被广泛应用到工业控制系统、数据采集系统、智能化仪器仪表、办公自动化等领域中,并已经进入家庭,因此,单片机技术的开发和应用水平已经逐步成为一个国家自动化发展水平的标志之一。

本课题就是以单片机为主体与其它常用器件组合设计而成。

代表了单片机的主流发展方向。

本课题实现一个实用而又相对简单的电子万年历。

在市场上精致而且漂亮的万年历有很多,不过任何一个事物都不是完美的,都有可以进一步发展的余地。

本设计由51系列单片机和时钟芯片DS1302以及LED实现,功能齐全且实用。

1.1.2 单片机的发展历程单片机是微型计算机的一个重要分支,也是一种非常活跃和颇具生命力的机种,特别适用于工业控制领域。

1971年微处理器研制成功不久,就出现了单片机,但最早的单片机是1位的,处理能力有限。

单片机的发展共分四个阶段:第一阶段是初级阶段,功能非常简单;第二阶段是低性能阶段,以INTEL公司制造的MCS-48系列单片机为代表。

第三阶段为高性能单片机阶段,这个阶段推出的单片机普遍带有串行接口,多级中断系统,16位定时器/计数器,片内ROM、RAM容量加大,直到现在仍被广泛应用,是目前应用数量较多的单片机。

第四阶段是8位单片机巩固发展以及16位单片机、32位单片机推出阶段,以满足不同的用户需要。

纵观单片机几十年的发展历程,单片机的今后发展方向将向多功能、高性能、高速度、低功耗、低价格、外围电路内装化以及内存储器容量增加和FLASH存储器化方向发展。

电子万年历的设计制作

电子万年历1.1 功能要求电子万年历能显示阳历年、月、日、星期、[小]时、分、秒和阴历月、日、温度、节假日,在显示阴历时间时,能标明是否为闰年。

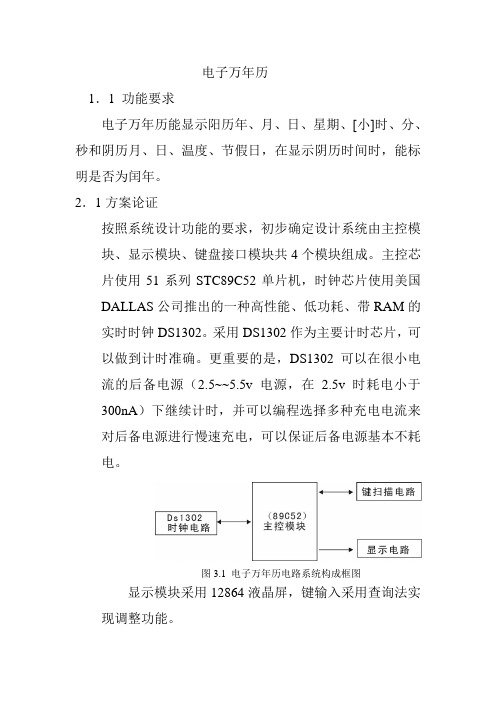

2.1方案论证按照系统设计功能的要求,初步确定设计系统由主控模块、显示模块、键盘接口模块共4个模块组成。

主控芯片使用51系列STC89C52单片机,时钟芯片使用美国DALLAS公司推出的一种高性能、低功耗、带RAM的实时时钟DS1302。

采用DS1302作为主要计时芯片,可以做到计时准确。

更重要的是,DS1302可以在很小电流的后备电源(2.5~~5.5v电源,在 2.5v时耗电小于300nA)下继续计时,并可以编程选择多种充电电流来对后备电源进行慢速充电,可以保证后备电源基本不耗电。

图3.1 电子万年历电路系统构成框图显示模块采用12864液晶屏,键输入采用查询法实现调整功能。

系统由主控制器STC89C52、时钟芯片DS1302、串口显示电路及键扫描电路组成。

2.2 主控制器STC89C52台湾宏晶公司生产的STC89(:52单片机采用高性能的静态80C51设计,由先进工艺制造,并带有非易失性Flash 程序存储器。

它是一种高性能、低功耗的8位CMOS微处理芯片,市场应用最多。

主要性能特点有:·8 KB Flash ROM,可以擦除1 000次以上,数据保存10年。

·256字节内部RAM。

·电源控制模式——时钟可停止和恢复;——空闲模式;——掉电模式。

·6个中断源。

·4个中断优先级。

·4个8位I/O口。

·全双工增强型UART。

·3个16位定时/计数器,TO、T1(标准80C51)和增加的T2(捕获和比较)。

·全静态工作方式:0~24 MHz。

2.3 时钟电路DSl3021.DSl302的性能特性·实时时钟,可对秒、分、时、日、周、月以及带闰年补偿的年进行计数;·用于高速数据暂存的31×8位RAM;·最少引脚的串行I/O;·2.5~5.5 V电压工作范围;·2.5 V时耗电小于300 nA;·用于时钟或RAM数据读/写的单字节或多字节(脉冲方式)数据传送方式;·简单的3线接口;·可选的慢速充电(至V CC1)的能力。

基于51单片机电子万年历设计

一、引言电子万年历是一种以数字形式实时显示日期、星期和时间等信息的电子设备。

在现代人日常生活中,万年历是一种常见的小型电子产品。

本文将基于51单片机设计一款简单实用的电子万年历。

二、设计原理1.时钟模块:采用DS1302实时时钟模块。

DS1302通过三线式串行接口与51单片机进行通信,可以实时获取日期、星期和时间等信息。

2.显示模块:使用数码管显示日期、星期和时间等信息。

共使用四块共阳数码管,采用数码管模块进行驱动,通过IO口进行数据传输。

3.按键模块:设计四个按键,分别为设置、上、下和确定。

通过按键来调整日期、星期和时间等信息。

4.闹钟功能:加入闹钟功能,可以设定闹钟时间,到达设定时间时,会有提示音。

5.温湿度传感器:加入温湿度传感器,可以实时监测环境温湿度,并在数码管上进行显示。

6.外部电源:由于51单片机工作电压较高,需要使用外部电源进行供电。

三、硬件设计1.电源电路:使用稳压电源芯片LM7805进行5V稳压,将稳压后的电压供给单片机和各个模块。

2.时钟模块:DS1302模块与单片机通过串行通信进行连接。

时钟模块上的时钟信号、数据信号和复位信号分别与单片机的IO口相连。

3.数码管显示模块:共有四块共阳数码管,通过595芯片进行驱动。

单片机的IO口与595芯片的串行、时钟和锁存引脚相连,595芯片的输出引脚与数码管的各段相连。

4.按键模块:通过电阻分压来实现按键功能,按下按键时,相应的IO口会被拉低。

5.闹钟功能:使用蜂鸣器来产生提示音,通过IO口与单片机相连。

6.温湿度传感器:使用DHT11温湿度传感器。

传感器的数据引脚通过IO口与单片机相连。

四、软件设计1.时钟显示:通过DS1302获取日期、星期和时间等信息,将其转化为数码管需要的编码格式,并通过595芯片进行显示。

2.按键操作:对按键进行扫描,根据按键的不同操作进行相应的处理。

例如按下设置键进行日期和时间的设置,按下上下键进行数值的变化,按下确定键进行数值的确认。

基于单片机的电子万年历的设计

基于单片机的电子万年历的设计摘要本文以AT89C2051单片机为主控芯片,采用美国DALLAS公司的涓细充电时钟芯片DS1302为时钟控制芯片,设计了一个电子万年历,能够显示年、月、日、时、分、秒、星期信息。

关键词实时显示 AT89C2051 单片机目录0、引言 (3)1、电子万年历的硬件电路设计 (3)2、主控制器AT89C2051 (3)3、DSl302时钟芯片的工作原理 (4)3.1 引脚功能 (4)3.2 DSl302的控制字节 (4)3.3 DSl302的复位特征和时钟控制要求 (4)3.4 数据输入输出I/O (5)3.5 DSl302的寄存器 (5)4、DS1302与微控制器的连接及软件控制 (5)4.1 DSl302与AT89C2051的连接 (5)4.2 软件控制 (6)4.3 根据在调试中出现的问题,作如下说明: (9)5、总结 (9)0、引言日常生活生产中有许多地方需要电子时钟和日历,比如家庭,办公室,以及一些智能化仪表。

目前的电子时钟日历系统多采用时钟芯片以简化系统的设计。

DSl302是众多时钟芯片中一款性价比较高的产品。

以AT89C2051单片机为主控芯片,采用美国DALLAS 公司的实时时钟芯片DSl302为时钟控制芯片,设计并实现的各种时钟控制电路,应用于各种家电、实验设备等。

其能够显示年、月、日、时、分、秒、星期。

并且可根据需要对各个位进行调节。

1、电子万年历的硬件电路设计硬件电路设计是电子时钟日历系统设计的第一步。

系统由主控模块,时钟芯片。

显示电路、键盘扫描电路共四个部分组成,电路构成,框图如图l所示。

图l 电子万年历系统的框架图主控芯片使用MCU-51系列的AT89C2051单片机,时钟芯片使用美国DALLAS公司推出的一种高性能、低功耗、带RAM的实时时钟DSl302。

采用DSl302作为主要计时芯片,可以作到计时准确。

更重要的是,DSl302可以在很小的后备电源(2.5-5.5V电源,在2.5V 时耗电小于300Na)下继续计时,并可编程选择多种充电电源来对后备电源进行慢速充电,可以保证后备电源基本不耗电。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于DS1302的数字时钟设计一、设计目的1、掌握电子时钟的基本工作方式。

2、进一步熟悉DS1302芯片的特性。

3、通过使用各基本指令,进一步熟练掌握单片机的编程和程序调试。

二、设计思路利用AT89C52的特点及DS1302的特点,设计一种基于DS1302单片机控制,再利用数码管静态显示的可调可定时数字钟。

本系统硬件利用AT89S52作为CPU 进行总体控制,通过DS1302时钟芯片获取准确详细的时间(年、月、日、周、日、时、分、秒准确时间),对时钟信号进行控制,同时利用数码管对时间进行准确显示年、月、日、周、日、时、分、秒。

三、设计过程3.1系统设计结构图图1系统设计结构图根据系统设计的要求和设计思路,确定该系统的系统设计结构图。

如图1所示。

硬件电路主要由MCU微处理控制器单元、DS1302时钟电路、储存器、复位电路、晶振电路、数码管显示模块构成。

3.2 MCU微控制器电路AT89S52作为系统的核心控制元件,只有它能正常工作后才能使其它的元件进入正常工作状态。

因此,下面对AT89S52进行必要的说明,AT89S52的管脚如图3所示。

图3 AT89S52的管脚1)VCC:40脚,供电电压,一般接+5V电压。

2)GND:20脚,接工作地。

3)P0口:1~8脚,P0口是一个8位漏极开路的双向I/O口。

作为输出口,每位能驱动8个TTL逻辑电平。

对P0端口写“1”时,引脚用作高阻抗输入。

当访问外部程序和数据存储器时,P0口也被作为低8位地址/数据复用。

在这种模式下,P0具有内部上电阻。

但是P0口在程序校验作为输出指令字节时,需要外部加上拉电阻,一般上拉电阻选4.7K~10K为宜。

本设计中用5.1K的排阻对P0口进行上拉电平。

4)P1口:32~39脚,P1口是一个内部具有上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4个TTL门电流。

P1端口写入“1”后,被内部上拉电阻把端口拉高,此时可以作为作输入口使用。

作为输入使用时,被外部拉低的引脚由于内部电阻的原因,将输出电流。

5)P2口:20~27脚,P2 口是一个具有内部上拉电阻的8 位双向I/O 口,P2 输出缓冲器能驱动4 个TTL 逻辑电平。

对P2 端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。

6)P3口:10~17脚,P3 口是一个具有内部上拉电阻的8 位双向I/O 口,P3 输出缓冲器能驱动4 个TTL 逻辑电平。

对P3 端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。

7)RESET:9脚,复位输入端。

当振荡器复位器件时,要保持RST脚两个机器周期的高电平时间。

8)ALE/P非:30脚,当访问外部存储器时,地址锁存允许的输出电平用于锁存地址的地位字节。

在FLASH编程期间,此引脚用于输入编程脉冲。

在平时,ALE 端以不变的频率周期输出正脉冲信号,此频率为振荡器频率的1/6。

因此它可用作对外部输出的脉冲或用于系统校验。

9)PSEN:29脚,外部程序存储器的选通信号。

10)RST非/VP:31脚,访问外部程序存储器控制信号。

当EA非为低电平时,读取外部程序存储器;当EA非端为高电平时,则读取内部程序存储器,设计中一般接高电平。

11)XTAL1:19脚,振荡器反相放大器和内部时钟发生电路的输入端。

如采用外部时钟源时,XTAL1为输入端。

12)XTAL2:18脚,振荡器反相放大器的输出端。

如采用外部时钟源时,XTAL2 应悬空不接。

3.3 数码管静态显示电路在Proteus仿真中,我用了带有译码器的单个数码管,实际中是没有带译码器的数码管的,这里有两种方法可以解决:○1在实际焊板子是要改变端口对应且要改变程序以适应实际的八脚数码管。

○2用7447芯片来转换。

采用74HC595芯片驱动数码管,有关74HC芯片的介绍如下:8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

1、特点8位串行输入8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率2、输出能力并行输出,总线驱动串行输出;标准中等规模集成电路3、应用串行到并行的数据转换4、描述595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE 时(为低电平),存储寄存器的数据输出到总线。

6、参考数据7、CPD决定动态的能耗,PD=CPD×VCC×f1+∑(CL×VCC2×f0)F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压8、引脚说明9、功能表H=高电平状态L=低电平状态↑=上升沿↓=下降沿Z=高阻NC=无变化×=无效图4 全位静态数码管显示电路图5 74HC595电路3.4实时时钟电路本设计使用的实时时钟电路芯片是美国DALLAS公司生产的一种高性能、低功耗、带RAM的实时时钟电路芯片DS1302。

VCC1为后备电源,VCC2为主电源。

在主电源关闭的情况下,也能保持时钟的连续运行。

DS1302由VCC1或VCC2两者中的较大者供电;当VCC2大于VCC1+0.2V时,VCC2给DS1302供电;当VCC2小于VCC1时,DS1302由VCC1供电。

X1和X2是振荡源,外接32.768kHz晶振。

RST非是复位/片选线,通过把RST非输入驱动置高电平来启动所有的数据传送。

3.5复位电路在AT89S52单片机中的振荡器运行时,RST非引脚上保持到少2个机器周期的高电平输入信号,复位过程即可完成。

根据此原理,本设计采用上电复位和按键复位嵌套在系统中,增强了系统的实用性。

3.6 晶振电路AT89S52在工作时需要外部提供时钟信号,因此,本设计选择在其18脚19脚之间接上12MHz的晶振,为单片机提供1μs的机器振荡周期。

其电路连接图如图所示。

在图中,电容器C3、C4起稳定振荡频率、快速起振的作用,其电容值一般在20~50pF。

四、系统调试与结果4.1系统调试过程用Proteus画仿真电路后,将程序烧入芯片中起初出现乱码及按键功能混乱等错误,之后经过多次调整程序并解决了问题成功仿真。

4.2系统调试结果图8 调试结果五、主要元器件与设备Protues软件、AT89C512芯片、DS1302芯片、74HC595芯片及各电路模块六、课程设计体会本设计利用单片机AT89C512控制串行实时时钟芯DS1302构成数字时钟电路,实现计时功能。

该电路使用简单的三线接口,为单片机节省大量的接口资源,时钟芯片带有后备电池。

该时钟功能强大,性能优越,能为很多领域,特别是对时钟工作的准确性和可靠性有较高要求。

通过对电子时钟的设计的设计与制作,让我了解了电子时钟模块的编程思想,也让我明白了电子时钟的基本原理与设计理念,要设计一个电路必须先编好程序,用仿真软件测试成功后再得出结论。

通过这次学习,让我对该软件有了更熟悉的了解,我们应该自己动手,实际操作,才会有更深刻的理解。

经过这次设计我学到很多很多的的东西,不仅巩固了以前所学过的知识,而且通过这次课程设计使我懂得了理论与实际相结合的重要性,同时也提高了自己的实际动手能力和独立思考的能力。

最后感谢老师的授课和教导!七、参考文献[1]张义和.例说51单片机[M].北京:人民邮电出版社,2010年[2] 阎石编著数字电子技术基础(第五版) 北京高等教育出版社]2006.1~550[3] 蔡明文冯先成主编单片机课程设计华中科技大学出版社 2007.3[4]陈明萤编著 8051单片机课程设计实训教材清华大学出版社 2004[5] 康华光编著模拟电子技术基础(第五版)高等教育出版社 2006[6 ]黄智伟编著全国大学生电子设计竞赛电路(第一版)航空航天大学出版社 2006.36附录源程序代码:#include<reg51.H>#include<intrins.h>//---------------------------------------------------------------------------------------------------------------#define uint unsigned int#define uchar unsigned char//---------------------------------------------------------------------------------------------------------------/*uchar code table[]={0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0x80,0x98,0x88,0x83,0xc6,0xa1,0x86,0x8e};//共阳极数码管代码 */uchar code xingqi[8]={0x00,0x07,0x01,0x02,0x03,0x04,0x05,0x06};//星期显示代码ucharmiao,shi,fen,date,month,day,year,year10,set,mun,set_shi,set_fen,time _flag; //全局定义uint year_data,t;//---------------------------------------------------------------------------------------------------------------sbit SCLK=P3^5; //DS1302通讯线定义sbit DIO=P3^6;sbit RST=P3^7;sbit speak=P0^0;sbit DS=P2^0; //串行数据输入sbit SH_CP=P2^1; //移位时钟脉冲端口sbit ST_CP1=P2^2; //锁存端口sbit ST_CP2=P2^3;sbit ST_CP3=P2^4;sbit ST_CP4=P2^5;sbit ST_CP5=P2^6;sbit ST_CP6=P2^7;sbit ST_CP7=P3^0;sbit ST_CP8=P3^1;sbit OE1=P1^0; //并行输出控制位sbit OE2=P1^1;sbit OE3=P1^2;sbit OE4=P1^3;sbit OE5=P1^4;sbit OE6=P1^5;sbit OE7=P1^6;sbit OE8=P1^7;sbit K1=P3^2; //按键接口定义sbit K2=P3^3;sbit K3=P3^4;sbit K4=P0^1;sbit K5=P0^2;//---------------------------------------------------------------------------------------------------------------void write_595(uchar temp) //写74HC595一个字节{uchar i;for(i=0;i<8;i++) //移8位输入一个字节{SH_CP=0;_nop_();_nop_();_nop_();if(temp&0x80) //?{DS=1;}else{DS=0;}_nop_();_nop_();_nop_();SH_CP=1; //产生一个时钟上升沿,使数据移位temp<<=1; // 数据移位}}//---------------------------------------------------------------------------------------------------------------void delay(uint z) //Nms延时{uint x,y;for(x=z;x>0;x--)for(y=112;y>0;y--);}//---------------------------------------------------------------------------------------------------------------void delaynus(uint z) //ums延时{uint x,y;for(x=z;x>0;x--)for(y=10;y>0;y--);}//---------------------------------------------------------------------------------------------------------------void write(uchar date) //写入DS1302一个字节{uchar i;RST=1;SCLK=0;for(i=0;i<8;i++){SCLK=0;if(date&0x01)DIO=1;elseDIO=0;SCLK=1;date>>=1;}}//---------------------------------------------------------------------------------------------------------------uchar read() //读出DS1302一个字节{uchar a,temp;RST=1;for(a=8;a>0;a--){temp>>=1;SCLK=1;_nop_();_nop_();_nop_();_nop_();_nop_();_nop_();_nop_();SCLK=0;if(DIO){temp=temp|0x80;}else{temp=temp|0x00;}}return (temp);}//---------------------------------------------------------------------------------------------------------------void write_1302(uchar add,uchar dat) //写DS1302数据{RST=0;SCLK=0;RST=1;write(add);write(dat);SCLK=1;RST=0;}//---------------------------------------------------------------------------------------------------------------uchar read_1302(uchar add) //读DS1302数据{uchar temp;RST=0;SCLK=0;RST=1;write(add);temp=read();SCLK=1;RST=0;return(temp);}//---------------------------------------------------------------------------------------------------------------void display() //显示子程序{miao=read_1302(0x81); //读秒fen=read_1302(0x83); //读分shi=read_1302(0x85)&0x3f; //读时date=read_1302(0x87); //读日month=read_1302(0x89); //读月year=read_1302(0x8d); //读年day=read_1302(0x8B); //读星期write_595(miao); //显示秒ST_CP1=0; //数据被传入存储寄存器ST_CP1=1;ST_CP1=0;delaynus(10);write_595(fen); //显示分ST_CP2=0;ST_CP2=1;ST_CP2=0;delaynus(10);write_595(shi); //显示时ST_CP3=0;ST_CP3=1;ST_CP3=0;delaynus(10);write_595(date); //显示日ST_CP4=0;ST_CP4=1;ST_CP4=0;delaynus(10);write_595(month); //显示月ST_CP5=0;ST_CP5=1;ST_CP5=0;delaynus(10);write_595(year); //显示年ST_CP6=0;ST_CP6=1;ST_CP6=0;delaynus(10);write_595(xingqi[day]); //显示星期ST_CP7=0;ST_CP7=1;ST_CP7=0;delaynus(10);}//---------------------------------------------------------------------------------------------------------------void ds1302_init() //1302初始化{RST=0;SCLK=0;/*write_1302(0x80,0x00);//设置初始SEC 我就不设初始值了write_1302(0x82,0x00);//设置初始MINwrite_1302(0x84,0x00);//设置初始HRwrite_1302(0x86,0x00);//设置初始DATEwrite_1302(0x88,0x00);//设置初始MONTHwrite_1302(0x8A,0x00);//设置初始DAYwrite_1302(0x8C,0x00);//设置初始值YEAR */}//---------------------------------------------------------------------------------------------------------------void PORT_INIT() //端口初始化{P0=0XFE;P1=0X00;P2=0X00;P3=0XFC;}void time_init() //定时器初始化{TMOD=0x11; //设置定时器0\1都为工作方式1 TH0=(65536-50000)/256; //装入初值TL0=(65536-50000)%256;TH1=(65536-10000)/256; //装入初值TL1=(65536-10000)%256;PT0=1; //T0定时器优先级最高EA=1 ; //开总中断ET0=1; //开定时器0中断ET1=1; //开定时器1中断TR0=1; //启动定时器0TR1=1; //启动定时器1}//---------------------------------------------------------------------------------------------------------------void main(void) //主程序{PORT_INIT();ds1302_init();time_init(); //初始化year=read_1302(0x8d); //读年数据year_data=0x2000|year; //取20 //至少我活不到3000年,就这么设计吧write_595(year_data>>8); //显示年的20字样ST_CP8=0;ST_CP8=1;ST_CP8=0;set_shi=0x08; //闹钟初始值设定set_fen=0x00;time_flag=0; //标志位set=0;while(1){switch(set){case 0: //设置秒{display(); //显示if((shi==set_shi)&&(fen==set_fen)&&(time_flag==0)) //闹钟设定只设定小时和分钟{speak=~speak;if((K2==0)&&(time_flag==0)) //按键K2停止闹钟响{P0&=0XFE;time_flag=1;}delay(10);}} break;}if(fen==set_fen+1) //当不按下闹钟停止按键,一分钟后自动停止闹钟{P0&=0XFE;time_flag=0;}}}//---------------------------------------------------------------------------------------------------------------void time0() interrupt 1 // 定时器0中断{TR0=0;TH0=(65536-50000)/256;TL0=(65536-50000)%256;mun++;if(mun==15){mun=0;switch(set){case 1: //设置秒闪烁{delay(300);OE1=0;} break;case 2: //设置分闪烁{OE2=1;delay(300);OE2=0;} break;case 3: //设置时闪烁{OE3=1;delay(300);OE3=0;} break;case 4: //设置日闪烁{OE4=1;delay(300);OE4=0;} break;case 5: //设置月闪烁{OE5=1;delay(300);OE5=0;} break;case 6: //设置年闪烁{OE6=1;OE8=1;delay(300);OE6=0;OE8=0;} break;case 7: //设置星期闪烁 {delay(200);OE7=0;} break;case 8: //设置闹钟闪烁{OE2=1;OE3=1;delay(200);OE2=0;OE3=0;} break;}}TR0=1; //}//---------------------------------------------------------------------------------------------------------------void time1() interrupt 3 // 定时器1中断{TR1=0; //先关定时器TH1=(65536-20000)/256;TL1=(65536-20000)%256;if(K1==0){delay(10);if(K1==0){set++;if(set==9){set=0;write_1302(0x80,miao); //设置初始值SECwrite_1302(0x82,fen); //设置初始值MINwrite_1302(0x84,shi); //设置初始值HRwrite_1302(0x86,date); //设置初始值DATEwrite_1302(0x88,month); //设置初始值MONTHwrite_1302(0x8A,day); //设置初始值DAYwrite_1302(0x8C,year_data); //设置初始值YEAR}t=50000;while((!K1)&&t){t--;}}}if(K2==0){delay(10);if(K2==0){switch(set){case 1:{miao++;if((miao&0x0f)>0x09){miao+=0x10; //十位进1miao&=0xf0; //个位清零}if(miao==0x60){miao=0x00;}write_595(miao); //重写一次ST_CP1=0;ST_CP1=1;ST_CP1=0;} break;case 2:{fen++;if((fen&0x0f)>0x09){fen+=0x10;fen&=0xf0;}if(fen==0x60){fen=0x00;}write_595(fen);ST_CP2=0;ST_CP2=1;ST_CP2=0;} break;case 3:{shi++;if((shi&0x0f)>0x09){shi+=0x10;shi&=0xf0;}if(shi==0x24) //24小时制{shi=0x00;}write_595(shi); //显示时ST_CP3=0;ST_CP3=1;ST_CP3=0;} break;case 4:{date++;if((date&0x0f)>0x09){date+=0x10;date&=0xf0;}if((date==0x32)&&((month==0x01)||(month==0x03)||(month==0x05)||(m onth==0x07)||(month==0x08)||(month==0x10)||(month==0x12))){date=0x01;}elseif((date==0x31)&&((month==0x04)||(month==0x06)||(month==0x09)||(mont h==0x11))){date=0x01;}elseif((date==0x29)&&(month==0x02)&&((year_data|read_1302(0x8d))%100!=0) &&((year_data|read_1302(0x8d))%400!=0)){date=0x01;}elseif((date==0x30)&&(month==0x02)&&((year_data|read_1302(0x8d))%100==0) &&((year_data|read_1302(0x8d))%400==0)){date=0x01;}write_595(date);ST_CP4=0;ST_CP4=1;ST_CP4=0;} break;case 5:{month++;if((month&0x0f)>0x09){month+=0x10;month&=0xf0;}if(month==0x13){month=0x01;}write_595(month);ST_CP5=0;ST_CP5=1;ST_CP5=0;} break;case 6:{year_data++;if((year_data&0x000f)==0x0a) //十进制{year_data+=0x0010;year_data&=0xfff0;}if((year_data&0x00ff)==0xa0){year_data+=0x0100; //向前进1year_data&=0xff00; //后面尾数归0}write_595(year_data);ST_CP6=0;ST_CP6=1;ST_CP6=0;write_595(year_data>>8);ST_CP8=0;ST_CP8=1;ST_CP8=0;} break;case 7:{day++;if((day&0x0f)==0x08){day=0x01;}write_595(xingqi[day]);ST_CP7=0;ST_CP7=1;ST_CP7=0;} break;}t=50000;while((!K2)&&t){t--;}}}//-----------------------------------------------------------------------------if(K3==0){delay(10);if(K3==0){switch(set){case 1:{miao--;if((miao&0x0f)==0x0F){miao&=0xf9; //减到0后,再减一次就归0,}if(miao==0xF9) //当全部减到00时,再减一次就为59{miao=0x59;}write_595(miao);ST_CP1=0;ST_CP1=1;ST_CP1=0;} break;case 2:{fen--;if((fen&0x0f)==0x0F){fen&=0xf9;}if(fen==0xF9){fen=0x59;}write_595(fen);ST_CP2=0;ST_CP2=1;ST_CP2=0;} break;case 3:{shi--;if((shi&0x0f)==0x0F){shi&=0xf9;}if(shi==0xF9) //24小时制{shi=0x23;}write_595(shi); //显示时ST_CP3=0;ST_CP3=1;ST_CP3=0;} break;case 4:{date--;if((date&0x0f)==0x0F){date&=0xf9;}if((date==0x00)&&((month==0x01)||(month==0x03)||(month==0x05)||(m onth==0x07)||(month==0x08)||(month==0x10)||(month==0x12))){date=0x31;}elseif((date==0x00)&&((month==0x04)||(month==0x06)||(month==0x09)||(mont h==0x11))){date=0x30;}elseif((date==0x00)&&(month==0x02)&&((year_data|read_1302(0x8d))%100!=0) &&((year_data|read_1302(0x8d))%400!=0)){date=0x28;}elseif((date==0x00)&&(month==0x02)&&((year_data|read_1302(0x8d))%100==0) &&((year_data|read_1302(0x8d))%400==0)){date=0x29;}write_595(date);ST_CP4=0;ST_CP4=1;ST_CP4=0;} break;case 5:{month--;if((month&0x0f)==0x0F){month&=0xf9;}if(month==0x00){month=0x12;}write_595(month);ST_CP5=0;ST_CP5=1;ST_CP5=0;} break;case 6:{year_data--;if((year_data&0x000f)==0x0F){year_data&=0xfff9;}if((year_data&0x00f0)==0xF0){year_data&=0xf999;}write_595(year_data);ST_CP6=0;ST_CP6=1;ST_CP6=0;write_595(year_data>>8);ST_CP8=0;ST_CP8=1;ST_CP8=0;} break;case 7:{day--;if((day&0x0f)==0x00){day=0x07;}write_595(xingqi[day]);ST_CP7=0;ST_CP7=1;ST_CP7=0;} break;}t=50000;while((!K3)&&t) //松手检测{t--;}}}//-----------------------------------------------------------------------------switch(set){case 8:{if(K4==0){delay(10);if(K4==0){set_shi++;if((set_shi&0x0f)>0x09){set_shi+=0x10;set_shi&=0xf0;}if(set_shi==0x24) //24小时制{set_shi=0x00;}write_595(set_shi); //显示闹钟的时ST_CP3=0;ST_CP3=1;ST_CP3=0;t=50000;while((!K4)&&t){t--;}}}if(K5==0){delay(10);if(K5==0){set_fen++;if((set_fen&0x0f)>0x09){set_fen+=0x10;set_fen&=0xf0;}if(set_fen==0x60){set_fen=0x00;}write_595(set_fen);ST_CP2=0;ST_CP2=1;ST_CP2=0;t=50000;while((!K5)&&t){t--;}}}}}if(((K4==0)||(K5==0))&&(set==0)){delay(10);if(((K4==0)||(K5==0))&&(set==0)){write_595(set_shi); //显示闹钟的时ST_CP3=0;ST_CP3=1;ST_CP3=0;write_595(set_fen); //显示闹钟的分ST_CP2=0;ST_CP2=1;ST_CP2=0;P1=0XF9;while((!K4)||(!K5));P1=0X00;}}TR1=1; //退出时开定时器}。