脉宽调制PWM的VHDL实现

相关主题

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

pwm_output : out std_logic ); end PWM;

architecture behav of PWM is

signal Triangle_data : std_logic_vector( 7 downto 0 ); 5/6

signal pwm_data : std_logic;

pwm_output <= pwm_data; end behav;

6/6

END SYN;

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; USE ieee.std_logic_unsigned.all;

entity PWM is port( clk : in std_logic; rst : in std_logic; ADC_data : in std_logic_vector ( 7 downto 0 ); --Triangle_data : in std_logic_vector ( 7 downto 0 );

一、实验原理

PWM 的设计

二、系统描述

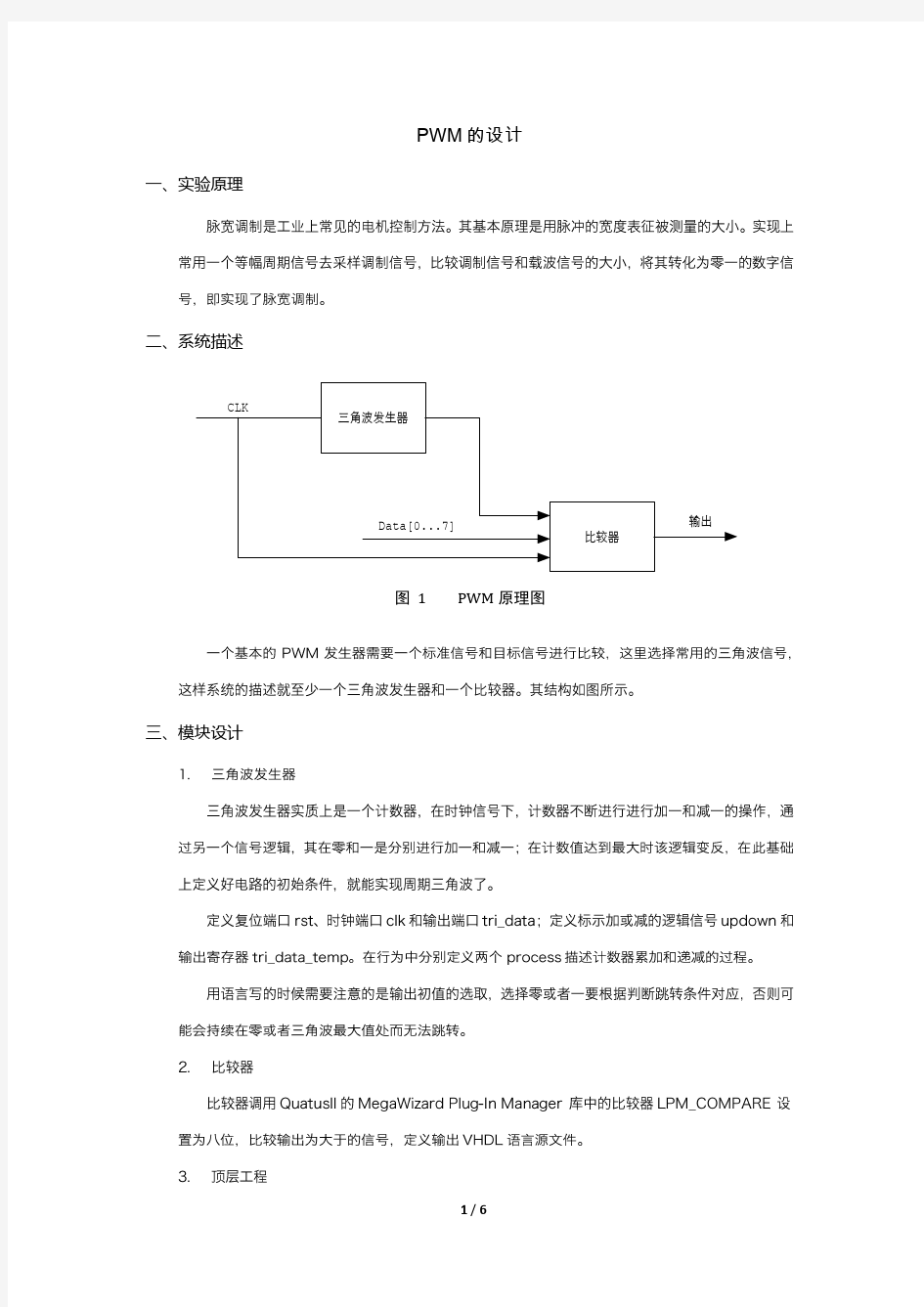

CLK

三角波发生器

Data[0...7]

输出 比较器

图 1 PWM 原理图

三、模块设计

1/6

四、实验结果

五、问题与展望

图 2 PWM 仿真波形图

2/6

附源代码

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; USE ieee.std_logic_unsigned.all;

component Triangle is port( rst : in std_logic; clk : in std_logic; tri_data : out std_logic_vector ( 7 downto 0 ) );

end component;

component Compare is port( dataa : in std_logic_vector( 7 downto 0 ); datab : in std_logic_vector( 7 downto 0 ); AgB : out std_logic );

COMPONENT lpm_compare

GENERIC (

lpm_representation

: STRING;

lpm_type

: STRING;

lpm_width

: NATURAL

4/6

); PORT (

dataa : IN STD_LOGIC_VECTOR (7 DOWNTO 0); datab : IN STD_LOGIC_VECTOR (7 DOWNTO 0); AgB : OUT STD_LOGIC ); END COMPONENT;

end if; --tri_data <= tri_data_temp; end process;

end behav;

LIBRARY ieee; USE ieee.std_logic_1164.all;

LIBRARY lpm; USE lpm.all;

ENTITY Compare IS

PORT

(

dataa

begin

process( rst, clk ) begin

if rst = '0' then updown <= up;

elsif clk'event and clk = '1' then case updown is when up => if tri_data_temp >= B"11111110" then updown <= down; end if; when down => if tri_data_temp <= B"00000001" then updown <= up; end if; when others => end case;

Leabharlann Baidu

BEGIN AgB

<= sub_wire0;

lpm_compare_component : lpm_compare GENERIC MAP (

lpm_representation => "UNSIGNED", lpm_type => "LPM_COMPARE", lpm_width => 8 ) PORT MAP ( dataa => dataa, datab => datab, AgB => sub_wire0 );

constant up : std_logic := '0'; --* rising slope *-constant down : std_logic := '1'; --* descending slope *-signal updown : std_logic; signal tri_data_temp : std_logic_vector(7 downto 0);

ENTITY Triangle IS

port(

rst

: in std_logic;

clk

: in std_logic;

tri_data: out std_logic_vector( 7 downto 0 )

);

end Triangle;

architecture behav of Triangle is

: IN STD_LOGIC_VECTOR (7 DOWNTO 0);

datab

: IN STD_LOGIC_VECTOR (7 DOWNTO 0);

AgB

: OUT STD_LOGIC

);

END Compare;

ARCHITECTURE SYN OF compare IS

SIGNAL sub_wire0 : STD_LOGIC ;

end component;

begin

Triangel_inst : Triangle port map( rst => rst, clk => clk, tri_data => Triangle_data );

Compare_inst : Compare port map( dataa => ADC_data, datab => Triangle_data, AgB => pwm_data );

end if; tri_data <= tri_data_temp; end process;

3/6

process ( rst, clk ) begin

if rst = '0' then tri_data_temp <= B"00000001";

elsif clk'event and clk = '1' then case updown is when up => tri_data_temp <= tri_data_temp + 1; when down => tri_data_temp <= tri_data_temp - 1; when others => end case;

architecture behav of PWM is

signal Triangle_data : std_logic_vector( 7 downto 0 ); 5/6

signal pwm_data : std_logic;

pwm_output <= pwm_data; end behav;

6/6

END SYN;

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; USE ieee.std_logic_unsigned.all;

entity PWM is port( clk : in std_logic; rst : in std_logic; ADC_data : in std_logic_vector ( 7 downto 0 ); --Triangle_data : in std_logic_vector ( 7 downto 0 );

一、实验原理

PWM 的设计

二、系统描述

CLK

三角波发生器

Data[0...7]

输出 比较器

图 1 PWM 原理图

三、模块设计

1/6

四、实验结果

五、问题与展望

图 2 PWM 仿真波形图

2/6

附源代码

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; USE ieee.std_logic_unsigned.all;

component Triangle is port( rst : in std_logic; clk : in std_logic; tri_data : out std_logic_vector ( 7 downto 0 ) );

end component;

component Compare is port( dataa : in std_logic_vector( 7 downto 0 ); datab : in std_logic_vector( 7 downto 0 ); AgB : out std_logic );

COMPONENT lpm_compare

GENERIC (

lpm_representation

: STRING;

lpm_type

: STRING;

lpm_width

: NATURAL

4/6

); PORT (

dataa : IN STD_LOGIC_VECTOR (7 DOWNTO 0); datab : IN STD_LOGIC_VECTOR (7 DOWNTO 0); AgB : OUT STD_LOGIC ); END COMPONENT;

end if; --tri_data <= tri_data_temp; end process;

end behav;

LIBRARY ieee; USE ieee.std_logic_1164.all;

LIBRARY lpm; USE lpm.all;

ENTITY Compare IS

PORT

(

dataa

begin

process( rst, clk ) begin

if rst = '0' then updown <= up;

elsif clk'event and clk = '1' then case updown is when up => if tri_data_temp >= B"11111110" then updown <= down; end if; when down => if tri_data_temp <= B"00000001" then updown <= up; end if; when others => end case;

Leabharlann Baidu

BEGIN AgB

<= sub_wire0;

lpm_compare_component : lpm_compare GENERIC MAP (

lpm_representation => "UNSIGNED", lpm_type => "LPM_COMPARE", lpm_width => 8 ) PORT MAP ( dataa => dataa, datab => datab, AgB => sub_wire0 );

constant up : std_logic := '0'; --* rising slope *-constant down : std_logic := '1'; --* descending slope *-signal updown : std_logic; signal tri_data_temp : std_logic_vector(7 downto 0);

ENTITY Triangle IS

port(

rst

: in std_logic;

clk

: in std_logic;

tri_data: out std_logic_vector( 7 downto 0 )

);

end Triangle;

architecture behav of Triangle is

: IN STD_LOGIC_VECTOR (7 DOWNTO 0);

datab

: IN STD_LOGIC_VECTOR (7 DOWNTO 0);

AgB

: OUT STD_LOGIC

);

END Compare;

ARCHITECTURE SYN OF compare IS

SIGNAL sub_wire0 : STD_LOGIC ;

end component;

begin

Triangel_inst : Triangle port map( rst => rst, clk => clk, tri_data => Triangle_data );

Compare_inst : Compare port map( dataa => ADC_data, datab => Triangle_data, AgB => pwm_data );

end if; tri_data <= tri_data_temp; end process;

3/6

process ( rst, clk ) begin

if rst = '0' then tri_data_temp <= B"00000001";

elsif clk'event and clk = '1' then case updown is when up => tri_data_temp <= tri_data_temp + 1; when down => tri_data_temp <= tri_data_temp - 1; when others => end case;