(完整版)中国科技大学微机原理与接口技术-周荷琴第4版ppt课件

微机原理与接口技术课件PPT

汇编语言的优点

汇编语言具有高效、可移植性、 可维护性等优点,适用于编写操 作系统、编译器等关键软件。

汇编语言的缺点

汇编语言编写复杂,容易出错, 且可移植性较差,需要针对不同 的计算机体系结构进行修改。

高级语言

01

高级语言的定义

高级语言是一种抽象程度更高的 编程语言,它使用更接近自然语 言的语法和语义。

实验提供参考。

THANKS FOR WATCHING

感谢您的观看

串行接口的数据传输速率比并行 接口慢,但只需要一根数据线, 因此成本较低。

03

串行接口的常见标准包括RS-232 、RS-422和USB。

04

中断控制器

中断控制器是微机中的一 种重要组件,它负责管理 计算机系统中断的处理。

中断控制器可以管理硬件 设备的中断请求,例如键 盘、鼠标和计时器等。

ABCD

并行接口通常用于连接打印机、磁盘驱动器等高速设备, 因为这些设备需要快速传输大量数据。

并行接口的常见标准包括ECP、EPP和USB。

串行接口

01

串行接口是一种数据传输方式, 它通过单个数据线逐位传输数据 。

02

串行接口通常用于连接鼠标、调 制解调器等低速设备,因为这些 设备不需要快速传输大量数据。

语音识别和图像处理

利用微机原理与接口技术,可以实现语音识 别和图像处理等功能,提高办公自动化水平 。

在家用电器中的应用

1 2 3

智能家居控制

微机原理与接口技术可以用于智能家居控制,实 现家用电器的远程控制和自动化控制。

电视和音响设备控制

通过微机原理与接口技术,可以实现电视和音响 设备的智能控制,提供更加便捷和智能的娱乐体 验。

微机原理与接口技术第四版微机复习课精品PPT课件

4、 移位指令

▪ 1、非循环移位指令

左移 SHL 补0 逻辑移位 右移 SHR 补0

算术移位 左移 SAL 补0

右移 SAR 补最高位

▪ 2、循环移位

左移 ROL 补最高位

循环移位

右移 ROR 补最低位

带进位循环移位 左移 RCL 带CF位循环 右移 RCR 带CF位循环

▪ 3、移位指令的格式

例:XXX CL,4

子程序控制指令

⑴ CALL调用指令 格式: CALL Lable 功能:把CALL下一条指令地址压入堆栈保护后,转向 目标地址处执行子程序。

⑵ RET返回指令 格式:RET 功能:过程执行完以后,通过该指令返回原调用程序 的返回处。

6、 串操作指令

要求:掌握串操作原理。

①串处理指令只能处理单个字节或字,应用中需要串重复 前缀配合使用。

② CX寄存器存放重复操作的次数。 ③一般源串存放在数据段DS中,偏移地址由SI指定。 ④目的串存放在附加段ES中,偏移地址由DI指定。 ⑤ 设置方向标志指令:CLD(DF=0)和STD(DF=1)来 设置SI、DI偏移地址在重复操作过程中的移动方向。

第四章 汇编语言程序设计

考点 伪指令与指令性指令

1、 数据传送指令

地址传送指令:LEA LEA —— 偏移地址送寄存器指令

LEA OPD,OPS 同功能指令 MOV OPD,OFFSET OPS

2、 算术运算指令

四种标准算术运算指令: 加、减、乘、除

3、 逻辑运算指令

AND — 逻辑与指令 作用:用来屏蔽掉一个数中某些位,以便对剩下的其它位进 行某些处理。 如:AND AL,0FH ;屏蔽AL高四位 OR — 逻辑或指令 作用:用来给某数中特定位置位,其它位不变。 如:OR AL,0FH ;置位AL低四位 XOR — 逻辑异或指令 作用:用来将某数中特定位取反,其它位不变。 如:XOR AL,0FH ;取反AL低四位

微型计算机原理与接口技术.

●第13章 32位微机基本工作原理概述

Page 2

第1章Байду номын сангаас绪 论

1.3 计算机数据格式

本章重点:

●微型计算机的发展历史

●微型计算机系统

●计算机中的数制与码制

●计算机的结构及其工作原理

Page 3

1.3.1 计算机中的数制 一、 计算机中的数制

1、无符号整数表示法及数制变换 1)四种常用进制数的表示方法 A)二进制-----------以B作后缀 B)八进制----------以Q作后缀 C)十六进制-------以H作后缀 D)十进制----------以D作后缀或省略

十六进制

3

4 5 6

00000011B

00000100B 00000101B 00000110B

03H

04H 05H 06H

7

8 9 16 32 64 128 256 1024 65536 1048576

00000111B

00001000B 00001001B 00010000B 00100000B 01000000B 10000000B 100000000B 1000000000B 10000000000000000B 100000000000000000000B

3、机器字长n=8, 求+0、+6、+127、-0、-6、-127补码。

00000000B、00000110B、01111111B、00000000B、11111010B、10000001B

1.6、对下列8位字长及16位字长数据,分别补码表示。 真实值 [37] [-37] 原码 反码 补码

7CA2H

Page 13

例题:

微机原理与接口技术-周荷琴第4版ppt课件

2、存储器

功能:存放程序和数据。

SRAM RAM DRAM

存储器

内存(主存) 外存(辅存)

ROM

ROM

EPROM E2PROM

软盘、U盘

硬盘(移动硬盘)

• AMD Athlon II X2 240/盒装 本周劲热排 行第3位

• 参考价格: ¥380(全国) • 接口类型:Socket AM3(938) • 生产工艺:45纳米 • 主频:2.8GHz • 二级缓存:L2=2×1M • 核心数量:双核

4、十六进制表示法 基数为16,用0 - 9 、A - F 十五个字符来数值,逢十六 进一。 各位的权值为 16i 。

二进制表示数值方法如下:

n NH= ± Ki * 16i

i=-m

其中:K = 0 - 9 、A - F i

例:(56D.3)H = 5 * 162 + 6 * 161 + 13 * 160 + 3 * 16-1

I/O设备

输入设备

输出设备

键盘 鼠标 扫描仪、数码相机

显示器 打印机 绘图仪

(2)、I/O接口:连接外设备和系统总线,完成信号 转换、数据缓冲、与CPU进行信号联络等工作。

显示器卡:完成显示器与总线的连接。 声卡:完成声音的输入/输出。 网卡:完成网络数据的转换。 扫描卡:连接扫描仪到计算机。 调制解调器卡:模拟信号与数字信号相互转换。 键盘接口、打印机接口等。 232接口:串行数据接口。

运算规则:

加法运算:

0+0 = 0 0+1 = 1 1+0 = 1 1+1 =10 (逢二进一) 减法运算:

0-0 = 0 10-1 =1 (借位) 1-0 = 1 乘法运算:

微机原理与接口技术 第四版

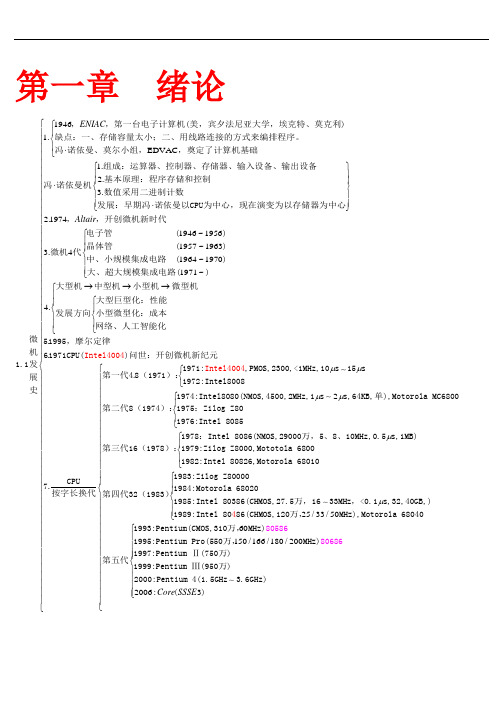

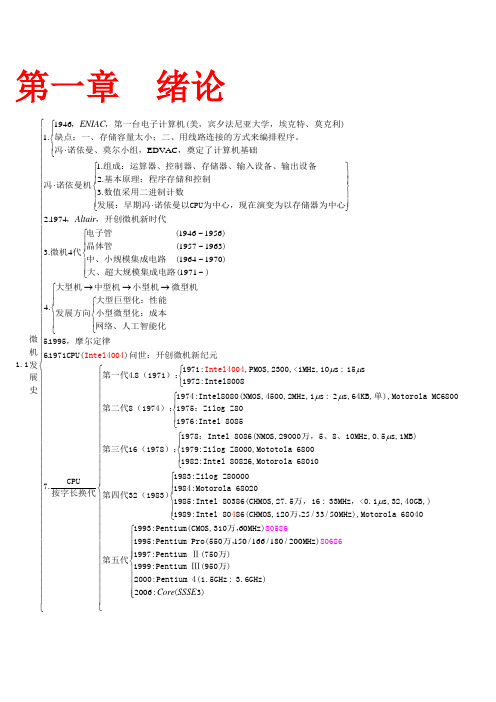

第一章 绪论19461.EDVAC 1.2.3.ENIAC ⎧⎪⎨⎪⋅⎩⎧⎪⎪⋅⎨⎪⎪⋅⎩,,第一台电子计算机(美,宾夕法尼亚大学,埃克特、莫克利)缺点:一、存储容量太小;二、用线路连接的方式来编排程序。

冯诺依曼、莫尔小组,,奠定了计算机基础组成:运算器、控制器、存储器、输入设备、输出设备基本原理:程序存储和控制冯诺依曼机数值采用二进制计数发展:早期冯诺依曼以CPU 为中心,现在演变为以存储器为中心微机1.1发展史 2.19741946~19561957~19633.41964~19701971~4..Altair ⎫⎪⎪⎬⎪⎪⎭⎧⎪⎪⎨⎪⎪⎩→→→⎧⎪⎧⎪⎨⎪⎨⎪⎪⎪⎩⎩,,开创微机新时代电子管 ()晶体管 ()微机代中、小规模集成电路 ()大、超大规模集成电路()大型机中型机小型机微型机大型巨型化:性能发展方向小型微型化:成本网络、人工智能化51995,..2μμμμ⎧⎨⎩摩尔定律61971CPU()问世:开创微机新纪元1971:,PMOS,2300,<1MHz,10s 15s 第一代48(1971):1972:Intel80081974:Intel8080(NMOS,4500,2MHz In ,1s s,64KB,单),Motorola MC6800第二代8(1974):1975:Zilog Z80CPU 7.按字长tel4004Intel4004换代μ⎧⎪⎨⎪⎩⎧⎪⎨⎪⎩1976:Intel 80851978:Intel 8086(NMOS,29000万,5、8、10MHz,0.5s,1MB)第三代16(1978):1979:Zilog Z8000,Mototola 68001982:Intel 80826,Motorola 680101983:Zilog Z800001984:Motorola 68020第四代32(1983)1985:In z 25/33/50z 60z 150/166/180/200z μ⎧⎪⎪⎨⎪⎪⎩tel 80386(CHMOS,27.5万,1633MH ,<0.1s,32,40GB,)1989:Intel 8086(CHMOS,120万,MH ),Motorola 680401993:Pentium(CMOS,310万,MH )1995:Pentium Pro(5450万,MH )8058680619978第五代6:Pen 2006:3Core SSSE ⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩⎪⎪⎩⎩tium Ⅱ(750万)1999:Pentium Ⅲ(950万)2000:Pentium 4(1.5GHz 3.6GHz)()1.2⎧⎧⎪⎪•⎨⎨⎪⎪⎩⎩基本结构:CPU(运算器、控制器)、存储器、输入/输出设备微机系统冯诺依曼工作原理:存储器存储程序控制的原理发展:早期冯诺依曼以CPU为中心,现在演变为以存储器为中心()=+CPU =+++I/O 1. 1.2.3./4...1.2.1CPU I O ⎧⎪⎪⎪⎪⎪⎪⎨⎪⎧⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎩⎩⎧⎨⎩核心,中央处理器微处理器运算器控制器微控制器运算器控制器存储器接口单片机从存储器中取指令,指令译码简单的算术逻辑运算任务在处理器和存储器或之间传送数据程序流向控制等随机存储器2存储器:分类存放程序和数据只读存储器微处理器RAM 3I/O 接口:外部设备与C 1 微机微ROM 型计算机.I/O I /O ⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎧⎪⎪⎪⎧⎪⎨⎪⎨⎪⎪⎪⎩⎪⎪⎩⎧⎧⎪⎨⎩⎪⎪⎨⎪⎪⎪⎩PU 或存储器连接交换信息连接CPU 、存储器、I/O 接口任务:CPU 与存储器、I/O 间传送地址、数据、控制信息系数据总线统4总分类地址总线线控制总线键盘、鼠标、扫描仪、数字化仪、输入设备条形码读入器、光笔、语音输入器5.输出设备:CRT 显示器、打印机、绘图仪设备公用设备:软盘机,硬盘机,光盘机CPU ⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩⎧⎪⎨⎪⎩⎧⎨组成:(主体)微机、I/O 设备、系统软件微机2输入设备:键盘、鼠标、扫描仪、数字化仪、条形码读入器系统输出设备:CRT 显示器、打印机、绘图仪算术逻辑部件ALU :算术、逻辑运算累加器和寄存器组指令指针寄存器IP (程序计数器):指向要执行的下一条指令的偏移地址3段寄存器:段地址与偏移地址组成20位物理地址对存储器寻址时序和控制部件内部总线{41234567⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩⎪⎪⎩微机性能指标主频字长内存容量存取周期运算速度内核数目高速缓冲4.⎧⎧⎪⎪⎧⎨⎪⎨⎪⎪→→⎩⎩⎪⎪⎧⎪⎪⎧⎪⎪⎨⎨⎪⎨⎪⎪⎪⎪⎪⎩⎩⎪⎧⎨⎩⎩半导体存储器随机读写,断电存储内容消失特点:容量大速度慢动态DRAM内存条MOS电路存储单元电容:漏电信息消失刷新特点:容量小速度高随机RAM双极型电路分类静态SRAM存储单元:触发器或不要刷新MOS电路断电不丢失数据内存非易失性随机读写存储器NVRAM分类SRAM实时读写功能与EEPROM可靠非易失功能综合存储器⎧⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎩⎪⎪⎧⎪⎪⎪⎧⎧⎪⎪⎪⎨⎪⇒⎪⎩⎪⎪⎨⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩⎩⎪⎪⎪⎩只读不写,非易失性原理:专有设备烧断芯片内二极管而存储二进制信息可编程PROM只能写一次,固化程序用只读ROM分类可擦除可编程EPROMEEPROM(电可擦除EPROM)高速缓冲存储器Cache:存储空间较小,速度较慢,位于CPU和主存之间lash⎧⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩⎪⎧⎪⎪⎪⎧⎪⎪⎪⎪⎪⇒⎨⎨⎪⎪⎪⎪⎩⎪⎪⎪⎩⎩磁记录:软盘、硬盘、磁带1只读光盘外存光盘存储器:2一次写入光盘大容量、标准化、重量轻、易保存、寿命长3可改写光盘F存储器:(优盘)将数据以电荷的形式储存在光栅电极上,集成度高,可靠性好,不易损坏74373742451.2.2/CPU LS LS I O 作用:(或存储器)与外设交换信息。

微机原理与接口技术课件PPT

9

CPU

A0~~A9 CS A0~~A9 CS A0~~A9 CS A0~~A9 CS

1KX4

WR D0~~D3 D4~~D7 D0~~D3 WE

1KX4

WE D4~~D7

1KX4

WE D0~~D3

1KX4

WE D4~~D7

第6章 存储器

按存取方式分类

随机存取存储器 (RAM) 半导体存储器 静态RAM(SRAM)

动态RAM(DRAM)

掩膜式ROM

可编程ROM(PROM)

只读存储器 (ROM)

可擦除PROM(EPROM) 电可擦除PROM(E2PROM)

说明

(1)随机存取存储器RAM 信息可以随时写入或读出 关闭电源后所存信息将全部丢失 静态RAM采用双稳电路存储信息,而动态RAM是以 电容上的电荷存储信息。 静态RAM速度更快,而动态RAM的集成度更高、功 耗和价格更低,动态RAM必须定时刷新。

3.存储芯片的选用和地址分配

存储芯片类型和芯片型号的选择因素 存放对象 存储容量 存取速度 结构 价格

6.4.2 存储器与地址总线的连接

存储器与地址总线的连接,本质上就是在地址分配的 基础上实现地址译码,保证 CPU 能对存储器中所有单 元正确寻址。 它包括两方面内容:一是高位地址线译码,用以选择 存储芯片;二是低位地址线连接,用以通过片内地址 译码器选择存储单元。

存储器与CPU接口的一般问题

–CPU总线的负载能力 –存储器与CPU之间的时序配合

–存储芯片的选用和地址分配

1.CPU总线的负载能力

通常 CPU 总线的负载能力是一个 TTL 器件或 20 个 MOS器件。 一般小型系统中, CPU 可直接与存储器芯片相连。 而在较大系统中,当总线负载数超过限定时应当 加接驱动器。 地址线、控制线时是单向的,故采用单向驱动器, 如74LS244,Intel8282等,而数据线是双向传动 的 , 故 采 用 双 向 驱 动 器 , 如 7 4 LS245、 Intel8286/8287等。

微机原理与接口技术中科大第四版ppt

伪指令用于指示汇编程序进行某些操作,如定义数据、分配存储空间、设置段寄存器等。常见的伪指令包括DB、 DW、DD、ORG、ASSUME等。

顺序程序设计方法举例

顺序结构

程序按照代码的顺序逐条执行,没有分支和循环。

举例

计算1+2+3+...+10的累加和,可以按照顺序结构依次将每个数加到累加器中。

计算机系统组成及工作原理

计算机系统组成

包括硬件系统和软件系统两大部分。硬件系统主要由中央处 理器、存储器、输入输出设备等组成;软件系统包括系统软 件和应用软件等。

计算机工作原理

基于存储程序控制原理,即程序和数据一样存放在存储器中 ,计算机能自动地、连续地执行存放在存储器中的程序,无 需人工干预。

数的表示与运算方法

算术运算和逻辑运算类指令

算术运算类指令

如ADD、SUB、MUL、DIV等,用于执行加、减、乘、除等算术运算。

逻辑运算类指令

如AND、OR、NOT等,用于执行与、或、非等逻辑运算。这些指令可以处理 二进制数,进行位操作和逻辑判断。

03

汇编语言程序设计基础

汇编语言源程序格式及伪指令

源程序格式

汇编语言源程序通常以文本形式存储,包含指令、伪指令、宏指令、数据定义和注释等元素。

应用举例

内存条、U盘、SSD等存储设备均采用半导体存储器技术, 具有体积小、容量大、速度快等优点。

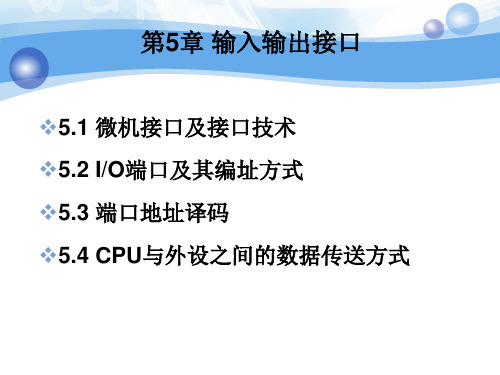

I/O接口基本概念及编址方式

I/O接口基本概念

连接CPU与外设之间的桥梁,实 现数据缓冲、电平转换、信息格 式转换等功能。

I/O接口编址方式

主要有统一编址和独立编址两种 方式。统一编址将I/O端口与内存 单元统一编址,通过访问内存指 令进行I/O操作;独立编址将I/O 端口单独编址,使用专门的I/O指 令进行操作。

微机原理和接口技术-1-1绪论-微机发展史zq-PPT课件

11

2015.9 Zuo

华中科技大学计算机学院

微机原理与接口技术 – 生物医学工程

Chapter1 绪论

世界上第一台电子数字计算机-电子数字积分计算机 ENIAC(Electronic Numerical Integrator And Computer), 由美国宾夕法尼亚大学于1946年研制成功并投入使用。

微机原理与接口技术 – 生物医学工程

Chapter1 绪论

第三代电子计算机—— IBM S/360

S/360极强的通用性适用于各方面的用户,它具有 “360度”全方位的特点,并因此得名。 开发S/360被称为“世纪豪赌”,IBM为此投入了 50亿美元的研发费用,远远超过制造原子弹的“曼 哈顿计划”的20亿美元。

计 算 兼 容 性

18

2015.9 Zuo

华中科技大学计算机学院

微机原理与接口技术 – 生物医学工程

Chapter1 绪论

第四代计算机

从1970年至今的计算机基本上都属于第四代计算机, 它们都采用大规模和超大规模集成电路。随着技术的 进展,计算机开始分化成通用大型机、巨型机、中型 机、小型机和微型机、单片机。 微型计算机(Microcomputer)与其他机型计算机的 区别:其中央处理器(CPU)采用了大规模、超大规 模集成电路技术,而其他类型计算机的CPU由相当多 的分离元件电路或集成电路所组成。称微型计算机的 CPU为微处理器(MPU:Micro Processing Unit)。

19

2015.9 Zuo

华中科技大学计算机学院

微机原理与接口技术 – 生物医学工程

Chapter1 绪论

1.2 微型计算机的发展概况

第一代(1971-1973年):4位和低档8位微处理器时代

微机原理与接口技术 第四版

第一章 绪论19461.EDVAC 1.2.3.ENIAC ⎧⎪⎨⎪⋅⎩⎧⎪⎪⋅⎨⎪⎪⋅⎩,,第一台电子计算机(美,宾夕法尼亚大学,埃克特、莫克利)缺点:一、存储容量太小;二、用线路连接的方式来编排程序。

冯诺依曼、莫尔小组,,奠定了计算机基础组成:运算器、控制器、存储器、输入设备、输出设备基本原理:程序存储和控制冯诺依曼机数值采用二进制计数发展:早期冯诺依曼以CPU 为中心,现在演变为以存储器为中心微机1.1发展史 2.19741946~19561957~19633.41964~19701971~4..Altair ⎫⎪⎪⎬⎪⎪⎭⎧⎪⎪⎨⎪⎪⎩→→→⎧⎪⎧⎪⎨⎪⎨⎪⎪⎪⎩⎩,,开创微机新时代电子管 ()晶体管 ()微机代中、小规模集成电路 ()大、超大规模集成电路()大型机中型机小型机微型机大型巨型化:性能发展方向小型微型化:成本网络、人工智能化51995,..2μμμμ⎧⎨⎩摩尔定律61971CPU()问世:开创微机新纪元1971:,PMOS,2300,<1MHz,10s 15s第一代48(1971):1972:Intel80081974:Intel8080(NMOS,4500,2MHz In ,1s s,64KB,单),Motorola MC6800第二代8(1974):1975:Zilog Z80CPU 7.按字长tel4004Intel4004换代μ⎧⎪⎨⎪⎩⎧⎪⎨⎪⎩1976:Intel 80851978:Intel 8086(NMOS,29000万,5、8、10MHz,0.5s,1MB)第三代16(1978):1979:Zilog Z8000,Mototola 68001982:Intel 80826,Motorola 680101983:Zilog Z800001984:Motorola 68020第四代32(1983)1985:In z 25/33/50z 60z 150/166/180/200z μ⎧⎪⎪⎨⎪⎪⎩tel 80386(CHMOS,27.5万,1633MH ,<0.1s,32,40GB,)1989:Intel 8086(CHMOS,120万,MH ),Motorola 680401993:Pentium(CMOS,310万,MH )1995:Pentium Pro(5450万,MH )8058680619978第五代6:Pen 2006:3Core SSSE ⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩⎪⎪⎩⎩tium Ⅱ(750万)1999:Pentium Ⅲ(950万)2000:Pentium 4(1.5GHz 3.6GHz)()1.2⎧⎧⎪⎪∙⎨⎨⎪⎪⎩⎩基本结构:CPU(运算器、控制器)、存储器、输入/输出设备微机系统冯诺依曼工作原理:存储器存储程序控制的原理发展:早期冯诺依曼以CPU为中心,现在演变为以存储器为中心()=+CPU =+++I/O 1. 1.2.3./4...1.2.1CPU I O ⎧⎪⎪⎪⎪⎪⎪⎨⎪⎧⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎩⎩⎧⎨⎩核心,中央处理器微处理器运算器控制器微控制器运算器控制器存储器接口单片机从存储器中取指令,指令译码简单的算术逻辑运算任务在处理器和存储器或之间传送数据程序流向控制等随机存储器2存储器:分类存放程序和数据只读存储器微处理器RAM 3I/O 接口:外部设备与C 1 微机微ROM 型计算机.I/O I /O ⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎧⎪⎪⎪⎧⎪⎨⎪⎨⎪⎪⎪⎩⎪⎪⎩⎧⎧⎪⎨⎩⎪⎪⎨⎪⎪⎪⎩PU 或存储器连接交换信息连接CPU 、存储器、I/O 接口任务:CPU 与存储器、I/O 间传送地址、数据、控制信息系数据总线统4总分类地址总线线控制总线键盘、鼠标、扫描仪、数字化仪、输入设备条形码读入器、光笔、语音输入器5.输出设备:CRT 显示器、打印机、绘图仪设备公用设备:软盘机,硬盘机,光盘机CPU ⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩⎧⎪⎨⎪⎩⎧⎨组成:(主体)微机、I/O 设备、系统软件微机2输入设备:键盘、鼠标、扫描仪、数字化仪、条形码读入器系统输出设备:CRT 显示器、打印机、绘图仪算术逻辑部件ALU :算术、逻辑运算累加器和寄存器组指令指针寄存器IP (程序计数器):指向要执行的下一条指令的偏移地址3段寄存器:段地址与偏移地址组成20位物理地址对存储器寻址时序和控制部件内部总线{41234567⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩⎪⎪⎩微机性能指标主频字长内存容量存取周期运算速度内核数目高速缓冲4.⎧⎧⎪⎪⎧⎨⎪⎨⎪⎪→→⎩⎩⎪⎪⎧⎪⎪⎧⎪⎪⎨⎨⎪⎨⎪⎪⎪⎪⎪⎩⎩⎪⎧⎨⎩⎩半导体存储器随机读写,断电存储内容消失特点:容量大速度慢动态DRAM内存条MOS电路存储单元电容:漏电信息消失刷新特点:容量小速度高随机RAM双极型电路分类静态SRAM存储单元:触发器或不要刷新MOS电路断电不丢失数据内存非易失性随机读写存储器NVRAM分类SRAM实时读写功能与EEPROM可靠非易失功能综合存储器⎧⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎩⎪⎪⎧⎪⎪⎪⎧⎧⎪⎪⎪⎨⎪⇒⎪⎩⎪⎪⎨⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩⎩⎪⎪⎪⎩只读不写,非易失性原理:专有设备烧断芯片内二极管而存储二进制信息可编程PROM只能写一次,固化程序用只读ROM分类可擦除可编程EPROMEEPROM(电可擦除EPROM)高速缓冲存储器Cache:存储空间较小,速度较慢,位于CPU和主存之间lash⎧⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩⎪⎧⎪⎪⎪⎧⎪⎪⎪⎪⎪⇒⎨⎨⎪⎪⎪⎪⎩⎪⎪⎪⎩⎩磁记录:软盘、硬盘、磁带1只读光盘外存光盘存储器:2一次写入光盘大容量、标准化、重量轻、易保存、寿命长3可改写光盘F存储器:(优盘)将数据以电荷的形式储存在光栅电极上,集成度高,可靠性好,不易损坏74373742451.2.2/CPULS LS I O 作用:(或存储器)与外设交换信息。

微型计算机原理与接口技术(中国科学技术大学出版社 第4版)第一章 课件

8086/8088/80286(1978-1982)

16位,2.9-13万个晶体管/1.5µm 时钟频率5-16MHz

80386/80486(1985-1989)

低档32位,27.5-120万个晶体管/1µm 时钟频率16-100MHz

第1章 绪论 3 / 69

课程要求

成绩组成

期末考试 50% 期中考试 20% 平时成绩 30%

(包括考勤、作业、大作业)

课件下载

课程中心网站 /

大平台课程 《微机原理及接口技术》 L.J.Zhu

第1章 绪论 4 / 69

课程内容

1 绪论

微型计算机的三个层次

运算器

控制器

微机系统 微机 微处理器

寄存器组

系统总线

RAM

ROM

I/O 接口

I/O 接口

系统软件

I/O 设备

I/O 设备

大平台课程 《微机原理及接口技术》 L.J.Zhu

第1章 绪论 30 / 69

微型计算机系统的构成

微型计算机系统

(µCS)

微型计算机

( µC )

微处理器

(µP)

大平台课程 《微机原理及接口技术》 L.J.Zhu

第1章 绪论 16 / 69

微处理器的发展

Pentium(1993)——奔腾:Intel的第五代 x86架构

64位,310-450万个晶体管/0.8µm/主频66-200MHz

Pentium Pro/Pentium MMX(1995-1996)

微型计算机

微型计算机

以微处理器为核心(也称CPU或中央处 理器),配上大规模集成电路的存储器 (ROM/RAM)、输入/输出接口电路 及系统总线等所组成的计算机

微机原理与接口技术第四版 第九章 可编程外围接口芯片8255及应用PPT课件

出端口。

I/O PC7~PC4

▪

端口A和端口B常作为独

立的输入或输出端口。

▪ 端口C可以作为输入端

I/O

PC3~PC0 口或输出端口,也可以

用来配合端口A和端口B

I/O PB7~PB0

的工作。在方式字的控 制下,端口C可以分成

两个4位的端口,分别

用来为端口A和端口B提

供控制和状态信息。

三、8255A的工作方式

D7 ~D0

INTEA

PA7 ~PA0

PC7

PC6

INTRA PC3

ACKA OBFA

外设响应信号 表示外设已经接收

到数据

输出缓冲器满信 号,表示CPU已 经输出了数据

中断请求信号 请求CPU再次输出数据

中断允许触发器 由PC6决定

B端口:

D7 ~D0

INTEB

PB7 ~PB0

PC2

PC1

INTRB PC0

③ CS:片选信号,低电平有效。该 信号来自译码器的输出,只有当CS 有效时,读信号RD和写信号WR才 对8255A有效。

④ RD:读信号,低电平有效。它 控制从8255A读出数据或状态信息

WR:写信号,低电平有效。它 控制把数据或控制命令字写入 8255A。

⑤ A1、A0:端口选择信号。8255A内部共有4

中断请求信号 请求CPU接收数据

中断允许触发器 由PC4决定

B端口:

D7 ~D0

INTEB

INTRB PC0

中断请求信号 请求CPU接收数据

PB7 ~PB0

PC2

PC1

STBB IBFB

数据选通信号 表示外设已经准备

好数据

输入缓冲器满信号, 表示B口已经接收 数据,但尚未被 CPU取走,通知外 设不能送新数据

微机原理与接口技术课件PPT

1 统一编址方式

从存储器空间划出一部分地址空间给I/O设备,把I/O 接口中的端口当作存储器单元一样进行访问,不设置 专门的I/O指令 优点: 访问I/O端口可实现输入/输出操作,还可以对端口内 容进行算术逻辑运算、移位等等; 能给端口有较大的编址空间,这对大型控制系统和 数据通信系统是很有意义的;

2.状态信息

CPU 在传送数据信息之前,经常需要先了解外 设当前的状态。如输入设备的数据是否准备好 、输出设备是否忙等。

用于表征外设工作状态的信息就叫做状态信息, 它总是由外设通过接口输入给CPU的。 状态信息的长度不定,可以是1个二进制位或 多个,含义也随外1 为什么要设置接口电路

CPU与外设两者的信号线不兼容,在信号线功能定义、逻 辑定义和时序关系上都不一致 两者的工作速度不兼容,CPU速度高,外设速度低

若不通过接口,而由CPU直接对外设的操作实施控制,就 会使CPU处于穷于应付与外设打交道之中,大大降低CPU的 效率 若外部设备直接由CPU控制,也会使外设的硬件结构依赖 于CPU,对外设本身的发展不利。

用来发布控制命令、控制外设工作的 信息,例如A/D转换器的启停信号。

控制信息总是CPU通过接口发出的。

返 回

5.1.3 接口的基本功能

1 . 2. 3. 4. 5. 6 . 7. 8. 数据缓冲功能 端口选择功能 信号转换功能 接收和执行CPU命令的功能 中断管理功能 可编程功能 返回外设状态的功能 数据宽度与数据格式转换的功能

I/O端口地址选用的原则

凡是被系统配置所占用了的地址一律不能使用 原则上讲,未被占用的地址,用户可以选用,但 对计算机厂家申明保留的地址,不要使用,否则 会发生I/O地址重叠和冲突,造成用户开发的产品 与系统不兼容而失去使用价值 一般,用户可使用300~31FH地址

微机原理与接口技术周荷琴第版ppt课件免费全文阅读

总线操作 总线读操作: CPU从存储器或外设读取数据。 总线写操作: CPU将数据写入存储器或外设 。 1 、最小模式下的总线读周期

总线周期包括:T1 、T2 、T3 、(TW) 、T4机器周期。

( 1)T1周期

•M//IO信号: 从存储器读还是从I/O设备中读数据; •AD15-AD0 、A19/S7-A16/S3:确定20位地址;

(5)T4状态

在T4状态 ,数据从数据总线上被撤除 ,各种控制信号 和状态信号进入无效状态 ,CPU完成了对存储器或 I/O设备的写操作。

3 、总线空操作(补充)

8086只有在CPU和存储器或外设要传送数据时 ,才能 执行上述的总线周期; 当指令队列已满 ,且EU未申 请访问存储器时 ,不执行总线周期 , 总线接口进入了 总线空闲周期。

SP------堆栈指针寄存器 BP------基址指针寄存器 DI------- 目的变址寄存器 SI------- 源变址寄存器

(3)标志寄存器 (4)算术逻辑单元ALU 完成8位或者16位二进制算术和逻辑运算 ,计算偏移量。

(6)标志寄存器 P25

16位寄存器 ,其中有7位未用。

D15 OF DF I F TFF SF ZF

•/DEN:变低电平 ,启动收发器8286 ,做好接收数据的 准备。

(3)T3状态

•若存储器或I/O端口已做好发送数据准备 ,则在T3状 态期间将数据放到数据总线上 ,在T3结束时 ,CPU从 AD15-AD0上读取数据。

(4)TW状态

•在T3状态 ,存储器或外设没有准备好数据 ,不能在T3 状态将数据放到总线上 ,使READY=0 ,则CPU在T3 和T4之间插入一个或几个TW状态 ,直到数据准备好

2 、执行部件 作用:

微机原理与接口技术课件PPT

例题

例3-45将首地址为SRC的源字符串传送到DEST 为首地址的内存区,字符串的长度为N个字节。 CLD ;DF=0,增量方向 LEA SI,SRC ;DS:SI←字符串首地址 LEA DI,ES:DEST ;ES:DI←目标地址 MOV CX,N ;字符串长度 REP MOVSB ;重复字符串传送

1.基本串操作指令

(1)串传送指令 MOVSB ;字节传送,ES:[DI]←DS:[SI], SI←SI±1,DI←DI±1 MOVSW ;字传送,ES:[DI]←DS:[SI], SI←SI±2,DI←DI ±2 DF=0,(SI)和(DI)增量;DF=1, ,(SI)和(DI)减量 不影响FR寄存器的值

5)串搜索指令 SCASB ;字节搜索,AL-ES:[DI],DI←[DI] ±1. SCASW ;字搜索, AX-ES:[DI],DI←[DI] ±2 DF=0,(SI)和(DI)增量;DF=1, (SI)和(DI)减量 影响FR寄存器的所有标志位

2.重复前缀指令

格式: REP ;无条件重复前缀指令 REPE/REPZ ;条件重复前缀指令 REPNE/REPNZ ;条件重复前缀指令

(3)存串指令 STOSB ;存字节,ES:[DI]←AL,DI←[DI] ±1 STOSW ;存字, ES:[DI]←AX,DI←[DI] ±2. DF=0,(DI)增量;DF=1, (DI)减量 不影响FR寄存器的值

例题2

使内存中0400H开始的256个单元清零 CLD LEA DI,[0400H] MOV CX, 0080H XOR AX ,AX REP STOSW

REP指令用在MOVS、STOS指令之前,每执行一次串 指令,CX←(CX)-1,直到CX=0,重复执行结束 REPE/REPZ指令用在CMPS、SCAS指令之前,每执 行一次串指令,CX←(CX)-1,并判断ZF标志位是否为 0;只要CX=0或ZF=0,则重复执行结束 REPNE/REPNZ指令用在CMPS、SCAS指令之前,每 执行一次串指令,CX←(CX)-1,并判断ZF标志位是否 为1;只要CX=0或ZF=1,则重复执行结束 LODS指令之前不能添加重复前缀

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、微处理器

微处理器(CPU)是大规模集成电路技术做成的芯片,芯 片内集成有控制器、运算器和寄存器等相关部件,完成对计算 机系统内各部件进行统一协调和控制。

2、存储器

功能:存放程序和数据。

SRAM RAM DRAM

存储器

内存(主存) 外存(辅存)

ROM

ROM

EPROM E2PROM

CPU 和 DMA 控制器。 被总线控制的部件(总线控制设备):

存储器 和 I/O设备。 总线的使用特点:

1、在某一时刻,只能由一个总线主控设备来控制总线, 其它总线主控设备此时必须放弃对总线的控制。

2、在连接系统的各个设备中,在某一时刻只能有一发 送者发送信号,但可以有多个设备从总线上同时获得 信号。

USB接口:通用串行接口。

4、系统总线

(1)、总线:传递信息的一组公用导线。 (2)、系统总线:从处理器引出的若干信号线,CPU通过它们 与存储器或I/O设备进行信息交换。系统总线分为: (A)、地址总线:传递地址信息的总线,即AB。CPU在地址 总线上输出将要访问的内存单元或I/O端口的地址,该总线为单 向总线。

2、主频 主频也叫做时钟频率,用来表示微处理器的运行

速度,主频越高表明微处理器运行越快,主频的单位 是MHz。现在一般用G表示。如P4 /2.8G

0.05

二 1974 8 8080

20

0.5

2-4

0.5

三

1978 1982

16

8086/8088 80286

2-3

四

1985 1989

32

80386 80486

1-2

2.9 13

27.5 120

4.77-10 8-20

12-33 25-66

<1 1-2

6-12 20-40

五 1993 32 Pentium 0.6-0.8

第一章 绪论

主要内容

• 微型计算机的组成 • 计算机中数制及其转换 • 符号数的表示及运算 • 数的定点与浮点表示

§1.1 概 述

一、电子计算机的发展:

• 电子管计算机(1946-1956) • 晶体管计算机(1957-1964) • 中小规模集成电路计算机(1965-1970) • 超大规模集成电路计算机(1971-今)

3、通过总线插槽来接口板连接。

四、微机主要性能指标

1、字长 字长是微处理器一次可以直接处理的二进制数码的 位数,它通常取决于微处理器内部通用寄存器的位 数和数据总线的宽度。微处理器的字长有4位、8位 、16位、32位和64位等等。 8088称为准16位微处理器,而80386SX称为准32位 微处理器。

• 参考价格: ¥740(全国) • 接口类型:Socket AM3(938) • 核心类型:Stars • 生产工艺:45纳米 • 主频:3.1GHz • 二级缓存:L2=2×512K • 三级缓存:L3=6M • 核心数量:双核

3、I/O设备和I/O接口 (1)、I/O设备:微机配备的输入/输出设备(外设)。 标准输入/输出设备(控制台):键盘和显示器(CRT)。

内存容量的计算:16条地址线可访问 216 = 64 KB。

20条地址线可访问 220 = 1 MB。

1K = 1024B 1M = 1024 KB 1G = 1024 MB

(B)、数据总线:传递数据信息的总线,即DB。

在CPU进行读操作时,内存或外设的数据通过数据总线送往 CPU;

在CPU进行写操作时,CPU数据通过数据总线送往内存或外设, 数据总线是双向总线。

330

60-200

100-200

1995 1996 六 1997 1999 2001

七

2002 ?

P/Pro

P/MMX 32 PII

PIII

P4

64

Itanium ?

0.6 0.6 0.35 .25-.13 .18-.13

0.08

550 450 750 850 3000

133-200 166-233 233-450 450-1200 1300-3000

二、电子计算机按其性能分类:

• 大中型计算机/巨型计算机(Mainframe Computer)

• 小型计算机(Minicomputer) • 微型计算机(Microcomputer) • 单片计算机(Single-Chip Microcomputer)

• 微型计算机的发展是以微处理器的发展 来表征的

软盘、U盘

硬盘(移动硬盘)

• AMD Athlon II X2 240/盒装 本周劲热排 行第3位

• 参考价格: ¥380(全国) • 接口类型:Socket AM3(938) • 生产工艺:45纳米 • 主频:2.8GHz • 二级缓存:L2=2×1M • 核心数量:双核

AMD Phenom II X2 550/黑盒

(C)、控制总线:传递控制信息的总线,即CB。

控制总线的方向:

一部分是从CPU输出:通过对指令的译码,由CPU内部产生, 由CPU送到存储器、输入/输出接口电路和其它部件。如时钟信 号、控制信号等。

另一部分是由系统中的部件产生,送往CPU,如:中断请求信 号、总线请求信号、状态信号。

控制总线的部件(总线主控设备):

I/O设备

输入设备

输出设备

键盘 鼠标 扫描仪、数码相机

显:连接外设备和系统总线,完成信号 转换、数据缓冲、与CPU进行信号联络等工作。

显示器卡:完成显示器与总线的连接。 声卡:完成声音的输入/输出。 网卡:完成网络数据的转换。 扫描卡:连接扫描仪到计算机。 调制解调器卡:模拟信号与数字信号相互转换。 键盘接口、打印机接口等。 232接口:串行数据接口。

CPU:2.5K 800(20条指令/ Cache:30K 时钟周期)

>300 >3000

三、微型计算机的组成

CPU

运算器 控制器

AB 地址总线 DB 数据总线 CB 控制总线

内存 RAM ROM

I/O接口

8255、8250(8251) 8253、8259

I/O设备

键盘、打印机 显示器、软硬盘

• 微处理器的集成度每隔18-24个月就会翻 一番,芯片的性能也随之提高一倍 ------摩尔定律

Intel CPU的发展见下页表

代

发表 年份

字长

(bits)

型号

线宽 (m)

晶体管数 (万个)

时钟频率 (MHz)

速度 (MIPS)

一

1971 1972

4 4004 8 8008

50

0.2 0.3

<1