64M 闪速存贮器K9K1208UOM 及其应用

NAND FLASH存储器K9WBG08U1M在视频记录器中的应用

NAND FLASH存储器K9WBG08U1M在视频记录器中的应用潘璠;曹玉东;秦国栋;秦刚【期刊名称】《现代电子技术》【年(卷),期】2013(000)018【摘要】A new video recorder was designed according to the characteristics of large amount of digital video data to im- prove the real-time performance and stability of video recorder. The design method based on the FPGA+DSP architecture was adopted for the interface of this video recorder. The read- write time sequence of K9WBG08U1M memory array was designed. The real-time read-write of the K9WBG08U1M array was realized. The continuous record and display of the images from infrared imaging system and CCD images were carried out with this video recorder in the experiment. The experiment results indicate that the video recorder composed of 16 pieces of K9WBG08U1M memories can realize successive video real-time record and play- back in 2.5 h. The video recorder satisfies the real-time requirement of image,and has perfect robustness.%为提高视频记录器的实时性和稳定性,并结合数字视频数据量较大的特点,在此设计了一种新型视频记录器。

K9F1G08UOM数据手册

m A 5 5 15 15 1 10 10 20 20 1 µA 10 50 10 50

页 编 ICC2 程 擦除 ICC3 ISB1 等待状态电流 (TTL) 等待状态电流 (CMOS) 输入开漏电流 输出开漏电流

ISB2

IL1 IL0

-

-

±10 ±10

-

-

±10 ±10 VCC V +0.3 0.8 -

6. 命令/地址/ 数据复用端口: 7. 硬件数据保护:编程/擦除操作在电源转换时关闭。 8. 可靠的 CMOS 浮置门技术: --保证:100K 编程/ 擦除次数。 --数据保持时间: 10 年。 9. 命令寄存器操作 10. 为高速编程设置的缓冲编程操作。 11. 通电自动读操作。 12. 智能复制拷贝操作。 13.为防盗版而设置的唯一的 ID 保护。 14. 封装。 - K9F1GXXX0M-YCB0/YIB0 48 - Pin TSOP I (12 x 20 / 0.5 mm pitch) - K9F1G08U0M-VCB0/VIB0 48 - Pin WSOP I (12X17X0.7mm)

器件描述

三星 K9F1GXXX0M 提供了 128M*8Bit/64M*16Bit 的存储容量,另外还有 32 M 的空闲存储器,它是采用 NAND 技术的大容量、高可靠的 Flash 存储器。 它对 2112 字节一页(*8device )或者 1056 字(*16device)一页的写操作。典型 时间是 300 微秒。对 128 字节/64K 字一块的擦除时间是 50 纳秒。输出引脚可 以作为数据/地址/命令复用。每一页的数据读出时间也很快,平均每个字节只 需 50 纳秒。片内的写控制器,可以自动执行写操作和擦除功能,包括必要的脉 冲产生器,内部校验和冗余数据。 K9F1G08 提供了实时映像算法的纠错码,写 操作系统可以利用 K9F1G08U0M 扩展的 100K 编程/ 擦除。K9F1G08U0M 为大 容量存储,新型电可擦写的非易失性半导体存储器,提供了最优方案。

闪速存储器在图像采集系统中的应用

闪速存储器在图像采集系统中的应用文章作者:长春理工大学刘智薛旭东文章出处:单片机及嵌入式系统应用摘要:闪速存储器具有结构简单、控制灵活、编程可靠、擦除快捷的优点,而且集成度可以做得很高,因此获得了较广泛的应用。

本文详细介绍Samsung公司生产的64M×8位闪速存储器K9F1208UOM的主特性、应用方法和接口技术;介绍采用K9F1208UOM作为图像存储介质的图像采集记录系统的组成原理和具体实现方法。

关键词:闪速存储器 K9F1208UOM 图像采集图像存储引言图像的保存和恢复是一个图像采集系统所不可或缺的功能之一。

保存图像信息所用的介质或设备有很多种,如常用的电影胶片、胶卷、硬盘、软盘、光盘、各种静态和动态RAM、ROM以及固态存储器件等。

其中,Flash ROM以其内容掉电不消失、价格低廉、控制方法灵活、与微处理器接口方便等特点,越来越多地应用在图像采集与存储系统中,如常见的数码像机。

因此,研究Flash ROM在图像采集记录系统中的应用技术有着重要的意义。

1 闪速存储器的分类和发展现状目前常见的图像采集记录系统如数码像机、数码摄像机中,通常采用半导体存储器作为其记忆部分。

半导体存储器通常可分为随机存储器(RAM)和只读存储器(ROM_。

RAM的内容可以随时刷新,访问速度快,但是掉电后其存储的信息会丢失;ROM 则具有掉电不丢失数据的特性。

通常ROM又可分为固定ROM、PROM、EPROM和EEPROM。

图1 K9F1208UOM引脚定义闪速存储器(Flash ROM)属于半导体存储器的一种,属于非易失性存储器NVM(Non-Volatile Memory)。

它采用类似于EPROM的单管叠栅结构的存储单元揣怕,是新一代用电信号擦除的可编程ROM;它既吸收了EPROM结构简单、编程可靠的优点,又具有EPROM用随道效应擦除的快捷特性,集成度可做得很高,因而在便携式数据存储和各种图像采集记录系统中得到了广泛的应用。

超大容量存储器K9F2G08U0M及其在管道通径仪中的应用

3.4 页复制页复制操作用来快速有效地实现页间数据移动,这是由于省去了比较费时的与片外设备之间的读写操作。这一特性的优势在块替换操作用于页间数据复制时体现尤为明显。其实该操作是按页读与页编程操作的复合,页复制读命令35H将页中数据移至数据寄存器中,而页复制写命令85H将数据复制到目标页中。页复制流程图。

闪存(Flash Memory)是一种可以进行电擦写并且掉电后信息不丢失(非易失,Non-Volatile)的存储器,具有功耗低、擦写速度快等特点,被广泛应用于外部存储领域。管道运输作为当前油气资源的主要输送手段,其运行安全性受到越来越多的重视。由于不同的要求使得铺设的管道直径不尽相同,并且管道在长期运行过程中也会存在各种变形,这对管道缺陷检测器的运行有相当大的影响,容易造成卡死等后果。通径仪就是鉴于此研制的记录管径变动情况的仪器。一般情况下,通径仪连续运行几百公里,相应记录的数据将达到上百兆字节。32MB、64MB的闪存已经不能满足需求。因此选用了Samsung公司开发的K9F2G08U0M,其单片容量高达264MB,可满足工程需求。本文将介绍该存储器的主要性能及其在管道通径仪中的应用。1 K9F2G08U0M存储器简介从接口角度看,虽然K9F2G08U0M的容量和寻址范围远远超过常见单片机的容量和寻址范围,但由于芯片上的写控制器能自动控制所有编程和擦除功能,提供必要的重复脉冲、内部确认和数据空间,而且只通过I/OI/O接口接收单片机的命令和数据而不需要地址线,因此实际操作起来非常方便。另外芯片是通过“与非”单元结构增大容量,所以没有因此而削弱自身性能;芯片具有独立的1页大小的数据存储器和缓存存储器,因此可以在0.2ms内完成2112B的页编程操作,在2ms内完成128KB的块擦除操作,同时数据区内的数据能以30ns/B的速度读出。整个存储区被分为2 048个相互独立的块,可从逻辑上和物理上对块的组织结构分类。图1为块的逻辑结构,每个块分为64页,每页为2 112B(2 048B+额外存储区的64B)。芯片通过页地址和页内字节地址访问每一个字节。通常页地址称为行地址行地址,而页内字节地址称为列地址,即264MB=2048块×64页/块×2112字节/页=217行×2112列。因此,行地址需要3个字节,列地址2个字节,输入顺序如表1所示。

最新-闪速存储器芯片K9F642019系列的典型应用 精品

闪速存储器芯片K9F6408系列的典型应用摘要96408系列是8×8的型闪速存储器。

它以其快速读写循环,数据硬件保护,可擦除,口命令地址数据线复用和接口便利等特点,正成为大型数据如语音、数字图像、文件等系统数据的载体。

本文给出了9640800与单片机8752的硬件连接电路及闪速存储器操作的软件应用程序。

关键词存储器;扇区;操作;应用程序1、概述存储器是计算机外围产品的重要组成部分,在经历了,和和如今已到了闪速存储器的时代。

存储器以其低成本,高可靠性的读写,非易失性,可擦写性和操作简便而成为一系列程序代码应用软件和数据用户文件存储的理想媒体,从而受到到嵌入式系统开发者的欢迎。

存储器的应用范围极广,从现代计算机优盘到嵌入式系统中取代的地位,可谓占尽风流。

正因为的应用广泛,了解和掌握的相关操作和管理技术就极为重要。

大致说来操作包括检错对内部坏扇区的检测、写操作写入数据、读操作从中读出数据、空间管理和擦除操作。

在系统中我们选用8752单片机,它有24个口,其中8个作为有特殊功能的口,因此只剩16个口可供一般的输入输出使用。

我们选用9640800闪存的主要原因是它能节约口,即它的地址线和数据线可复用。

而其他许多闪存的地址线和数据线是分开使用的。

因此,本文以公司的9640800为例,介绍的操作技术。

2、9640800芯片的性能特点·供电电压27~36·该芯片容量为66,由1024块组成,每块又由16页组成,一页共有512+16×8。

使用64,另外还有2的闲置储存空间。

·写和读以页为单位,而擦除以块为单位。

读、写和擦除操作均通过命令完成,非常方便。

参见图3·此芯片可擦写1百万次,掉电数据不丢失,数据可保存十年。

·有8位串行口,且可复用,既可作为地址和数据的输入输出引脚,又可作命令的输入引脚,根据时序采用分时循环。

见时序图5·写入每页的时间为200,平均每写一个字节约400,即约20。

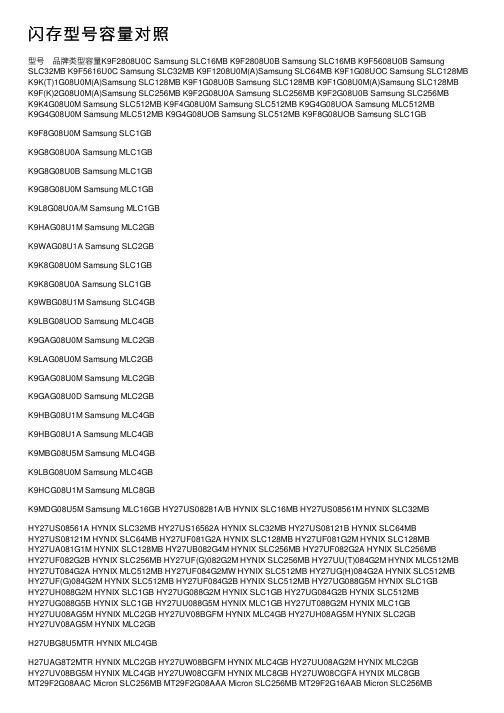

闪存型号容量对照

K9GAG08U0M Samsung MLC2GB

K9GAG08U0D Samsung MLC2GB

K9HBG08U1M Samsung MLC4GB

K9HBG08U1A Samsung MLC4GB

K9MBG08U5M Samsung MLC4GB

K9F8G08U0M Samsung SLC1GB

K9G8G08U0A Samsung MLC1GB

K9amsung MLC1GB

K9L8G08U0A/M Samsung MLC1GB

K9HAG08U1M Samsung MLC2GB

MT29F2G08X Micron SLC256MB MT29F2G08AAB Micron SLC256MB MT29F4G08MAA Micron MLC512MB MT29F4G08AAA Micron SLC512MB

MT29F4G08AAA(1)Micron SLC512MB MT29F8G08FAB Micron SLC1GB MT29F8G08DAA Micron SLC1GB MT29F8G08QAA Micron MLC1GB MT29F8G16MAA Micron MLC1GB MT29F128G08CJWAAAWC Micron MLC16GB MT29F8G08MAD Micron MLC1GB MT29F8G08BAA Micron SLC1GB MT29F8G08MAA Micron MLC1GB MT29F16G08FAA Micron SLC2GB MT29F16G08QAA Micron MLC2GB MT29F16G08MAA Micron MLC2GB MT29F16G08TAA Micron MLC2GB MT29F32G08QAA Micron MLC4GB MT29F32G08CBAAAWP Micron MLC4GB MT29F32G09CFAAA Micron MLC8GB MT29F32G08TAA Micron MLC4GB MT29F32G08FAA Micron SLC4GB MT29F32G08TAA1Micron MLC4GB MT29F64G08TAA Micron MLC8GB MT29F64G08MAA Micron MLC8GB JS29F02G08AAA intel SLC256MB JS29F04G08FANB3intel MLC512MB JS29F8G08CANCI intel MLC1GB JS29F16G08CANCI intel MLC2GB JS29F16G08CANC2intel MLC2GB JS29F08G08CANC1intel MLC1GB JS29F08G08AAMB2intel MLC1GB JS29F16G08CAMB2intel SLC2GB JS29F16G08AAMC1intel MLC2GB JS29F32G08CAMC1intel MLC4GB JS29F32G08FAMB2intel MLC4GB JS29F32G08AAMDB intel MLC4GB JS29F32G08AAMD2intel MLC4GB JS29F64G08CAMDB intel MLC8GB JS29F64G08CAMD1intel MLC8GB JS29F128G08FAMC1intel MLC16GB TC58128(A)FT Toshiba SLC16MB TC58256(A)FT Toshiba SLC32MB TC58DVM82A1FT Toshiba SLC32MB TC58512(A)FT Toshiba SLC64MB TC58DVM92A1FT Toshiba SLC64MB

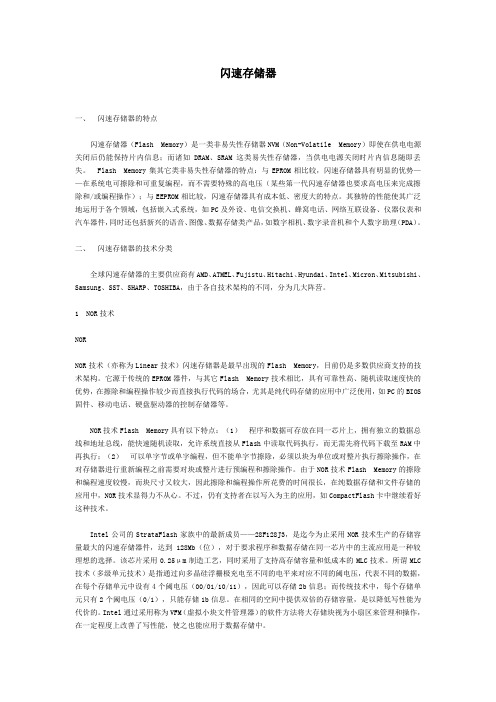

闪速存储器

闪速存储器一、闪速存储器的特点闪速存储器(Flash Memory)是一类非易失性存储器NVM(Non-Volatile Memory)即使在供电电源关闭后仍能保持片内信息;而诸如DRAM、SRAM这类易失性存储器,当供电电源关闭时片内信息随即丢失。

Flash Memory集其它类非易失性存储器的特点:与EPROM相比较,闪速存储器具有明显的优势——在系统电可擦除和可重复编程,而不需要特殊的高电压(某些第一代闪速存储器也要求高电压来完成擦除和/或编程操作);与EEPROM相比较,闪速存储器具有成本低、密度大的特点。

其独特的性能使其广泛地运用于各个领域,包括嵌入式系统,如PC及外设、电信交换机、蜂窝电话、网络互联设备、仪器仪表和汽车器件,同时还包括新兴的语音、图像、数据存储类产品,如数字相机、数字录音机和个人数字助理(PDA)。

二、闪速存储器的技术分类全球闪速存储器的主要供应商有AMD、ATMEL、Fujistu、Hitachi、Hyundai、Intel、Micron、Mitsubishi、Samsung、SST、SHARP、TOSHIBA,由于各自技术架构的不同,分为几大阵营。

1 NOR技术NORNOR技术(亦称为Linear技术)闪速存储器是最早出现的Flash Memory,目前仍是多数供应商支持的技术架构。

它源于传统的EPROM器件,与其它Flash Memory技术相比,具有可靠性高、随机读取速度快的优势,在擦除和编程操作较少而直接执行代码的场合,尤其是纯代码存储的应用中广泛使用,如PC的BIOS 固件、移动电话、硬盘驱动器的控制存储器等。

NOR技术Flash Memory具有以下特点:(1)程序和数据可存放在同一芯片上,拥有独立的数据总线和地址总线,能快速随机读取,允许系统直接从Flash中读取代码执行,而无需先将代码下载至RAM中再执行;(2)可以单字节或单字编程,但不能单字节擦除,必须以块为单位或对整片执行擦除操作,在对存储器进行重新编程之前需要对块或整片进行预编程和擦除操作。

Nand flash工作原理

Nand flash芯片工作原理------------------------------------Nand flash芯片型号为Samsung K9F1208U0B,数据存储容量为64MB,采用块页式存储管理。

8个I/O引脚充当数据、地址、命令的复用端口。

芯片内部存储布局及存储操作特点:一片Nand flash为一个设备(device), 其数据存储分层为:1 (Device) = 4096 (Blocks)1 (Block) -= 32 (Pages/Rows) 页与行是相同的意思,叫法不一样1 (Page) = 528 (Bytes) = 数据块大小(512Bytes) + OOB 块大小(16Bytes)在每一页中,最后16个字节(又称OOB)用于Nand Flash命令执行完后设置状态用,剩余512个字节又分为前半部分和后半部分。

可以通过Nand Flash命令00h/01h/50h分别对前半部、后半部、OOB进行定位通过Nand Flash内置的指针指向各自的首地址。

存储操作特点:1. 擦除操作的最小单位是块。

2. Nand Flash芯片每一位(bit)只能从1变为0,而不能从0变为1,所以在对其进行写入操作之前要一定将相应块擦除(擦除即是将相应块得位全部变为1).3. OOB部分的第六字节(即517字节)标志是否是坏块,如果不是坏块该值为FF,否则为坏块。

(转载注:应该是每块的第一页的第六个字节。

)4. 除OOB第六字节外,通常至少把OOB的前3个字节存放Nand Flash硬件ECC码NAND FLASH的工作原理- to beginner2007-04-23 23:43NAND FLASH 是一种大容量、高速的存储技术。

其接口较为简单,如果没有专门的nand flash控制器,甚至可以用io口与之对接。

其编程也相对简单,只要了解如下关键概念就可以:1.nand flash内部有管理单元,管理单元负责对nand flash的实际单元的操作。

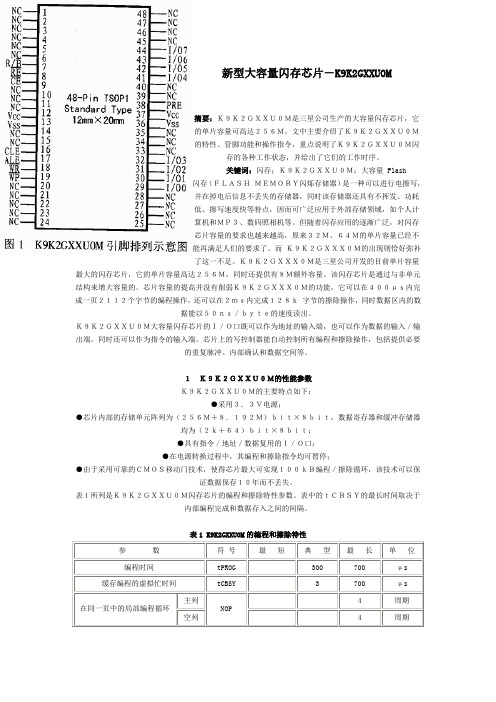

新型大容量闪存芯片K9K2GXXU0M

新型大容量闪存芯片-K9K2GXXU0M摘要:K9K2GXXU0M是三星公司生产的大容量闪存芯片,它的单片容量可高达256M。

文中主要介绍了K9K2GXXU0M的特性、管脚功能和操作指令,重点说明了K9K2GXXU0M闪存的各种工作状态,并给出了它们的工作时序。

关键词:闪存;K9K2GXXU0M;大容量 Flash闪存(FLASHMEMORY闪烁存储器)是一种可以进行电擦写,并在掉电后信息不丢失的存储器,同时该存储器还具有不挥发、功耗低、擦写速度快等特点,因而可广泛应用于外部存储领域,如个人计算机和MP3、数码照相机等。

但随着闪存应用的逐渐广泛,对闪存芯片容量的要求也越来越高,原来32M、64M的单片容量已经不能再满足人们的要求了。

而K9K2GXXX0M的出现则恰好弥补了这一不足。

K9K2GXXX0M是三星公司开发的目前单片容量最大的闪存芯片,它的单片容量高达256M,同时还提供有8M额外容量。

该闪存芯片是通过与非单元结构来增大容量的。

芯片容量的提高并没有削弱K9K2GXXX0M的功能,它可以在400μs内完成一页2112个字节的编程操作,还可以在2ms内完成128k字节的擦除操作,同时数据区内的数据能以50ns/byte的速度读出。

K9K2GXXU0M大容量闪存芯片的I/O口既可以作为地址的输入端,也可以作为数据的输入/输出端,同时还可以作为指令的输入端。

芯片上的写控制器能自动控制所有编程和擦除操作,包括提供必要的重复脉冲、内部确认和数据空间等。

1K9K2GXXU0M的性能参数K9K2GXXU0M的主要特点如下:●采用3.3V电源;●芯片内部的存储单元阵列为(256M+8.192M)bit×8bit,数据寄存器和缓冲存储器均为(2k+64)bit×8bit;●具有指令/地址/数据复用的I/O口;●在电源转换过程中,其编程和擦除指令均可暂停;●由于采用可靠的CMOS移动门技术,使得芯片最大可实现100kB编程/擦除循环,该技术可以保证数据保存10年而不丢失。

大容量NAND Flash K9T1G08UOM在网络存储中的应用

N N ls A D Fah器件 K T G 8 0 及 其编程 特 点 ,并 讨论 了网络 存储应 用 的存储 策略 和数 据 可靠性 9 10U M 方 面的考虑 , 设计 并 实现 了网络数据 流 的 N N l h存储 A D Fa s

关 键 词 : A D Fah 9 1 0 U M: 网络 存 储 : 无 效 块 处 理 N N l ;K T G 8 0 s

维普资讯

一ቤተ መጻሕፍቲ ባይዱ

6一 4

《 国外 电子元器件}0 7 20 年第 1 期 20 0 07年 1 0月

●主 题 论 文

大 容 量 N D ls T G0 U M AN F ah K9 1 8 0

在 网络存储 中的应 用

郭 宝 清 ,黄光 明

1 引 言

随着嵌 入式 系 统 广泛应 用 , 入 式 系统 中的数 嵌 据存储 和数据 管理 则成 为设计人 员考 虑 的重点 。在

许 多现 场 不 可 达 数据 采 集 应 用 中采 用 分 布式 数 据

基于 大 容量 N N ah的 网络存 储 系统 ,该 系统 A DF s l 具有 速 度快 、 全 可靠 、 扩展 、 震 和抗 干扰 能力 安 易 抗 强 、 用 温 度 范 围宽 等 特点 , 方 便 的用 于 安 全 监 使 可 控、 生产 数 据记 录 、 航行 数 据记 录等 方 面 , 具有 广 阔

都存 在 抗 震 和 抗 电磁 干扰 能 力 差 、使 用 温 度 范 围

构 如 图 1 示 , 中 5 2列 至 5 7列 间是 备 用 区 。 所 其 1 2

Abs r c : mi g a h tr g e u r me tf re e d d s se t a tAi n tt e so a e r q ie n o mb d e y t m,a so a e s h me b s d o r a a t r g c e a e n g e tc - p ct a i NAND F a h s p o o e n t i a e . e NAND a h K9 8 M n i p o r mmi g y l s i r p s d i h s p p rTh Fls - T1 G0 UO a d t r g a s n c a a t rsi r nto u e Th tae y fr a lc to fn t r tr g a d t e d t e ib lt r h r ce itc a e i r d c d. e sr t g pp ia i n o ewo k so a e, n h aa r l iiy a e o a d s u s d he so a e o ic s e .T tr g n NAND a h fr n t r t te m sd sg e Fl s ewo k daa sr a i e in d. o Ke r : NAND l s ; K9 y wo ds Fa h T1 G08 UOM; n t r tr g ; ma a e n fi a i l c e wo k so a e n g me to nv ld b o k

K9F2G08U0M中文资料

2

元器件交易网

K9F2G08Q0M K9F2G16Q0M K9F2G08U0M K9F2G16U0M

Preliminary FLASH MEMORY

256M x 8 Bit / 128M x 16 Bit NAND Flash Memory

PRODUCT LIST

Part Number K9F2G08Q0M-Y,P K9F2G16Q0M-Y,P K9F2G08U0M-Y,P K9F2G16U0M-Y,P 2.7 ~ 3.6V Vcc Range 1.70 ~ 1.95V Organization X8 X16 X8 X16 TSOP1 PKG Type

FEATURES

• Voltage Supply -1.8V device(K9F2GXXQ0M): 1.70V~1.95V -3.3V device(K9F2GXXU0M): 2.7 V ~3.6 V • Organization - Memory Cell Array -X8 device(K9F2G08X0M) : (256M + 8,192K)bit x 8bit -X16 device(K9F2G16X0M) : (128M + 4,096K)bit x 16bit - Data Register -X8 device(K9F2G08X0M): (2K + 64)bit x8bit -X16 device(K9F2G16X0M): (1K + 32)bit x16bit - Cache Register -X8 device(K9F2G08X0M) : (2K + 64)bit x8bit -X16 device(K9F2G16X0M) : (1K + 32)bit x16bit • Automatic Program and Erase - Page Program -X8 device(K9F2G08X0M) : (2K + 64)Byte -X16 device(K9F2G16X0M) : (1K + 32)Word - Block Erase -X8 device(K9F2G08X0M) : (128K + 4K)Byte -X16 device(K9F2G16X0M) : (64K + 2K)Word • Page Read Operation - Page Size - X8 device(K9F2G08X0M) : 2K-Byte - X16 device(K9F2G16X0M) : 1K-Word - Random Read : 25µs(Max.) - Serial Access : 50ns(Min.) 30ns(Min., K9F2G08U0M only) • Fast Write Cycle Time - Page Program time : 300µs(Typ.) - Block Erase Time : 2ms(Typ.) • Command/Address/Data Multiplexed I/O Port • Hardware Data Protection - Program/Erase Lockout During Power Transitions • Reliable CMOS Floating-Gate Technology - Endurance : 100K Program/Erase Cycles - Data Retention : 10 Years • Command Register Operation • Cache Program Operation for High Performance Program • Power-On Auto-Read Operation • Intelligent Copy-Back Operation • Unique ID for Copyright Protection • Package : - K9F2GXXX0M-YCB0/YIB0 48 - Pin TSOP I (12 x 20 / 0.5 mm pitch) - K9F2GXXX0M-PCB0/PIB0 : Pb-FREE PACKAGE 48 - Pin TSOP I (12 x 20 / 0.5 mm pitch)

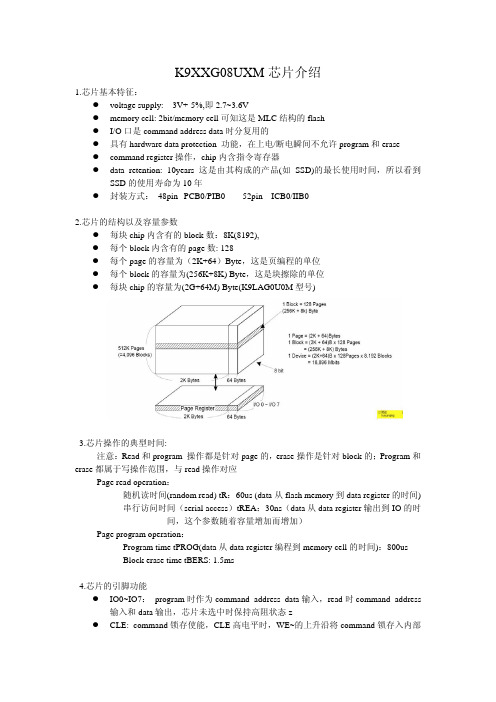

K9LAG08U0M芯片手册读后感(huyunqing)

K9XXG08UXM芯片介绍1.芯片基本特征:z voltage supply: 3V+-5%,即2.7~3.6Vz memory cell: 2bit/memory cell可知这是MLC结构的flashz I/O口是command address data时分复用的z具有hardware data protection 功能,在上电/断电瞬间不允许program和erasez command register操作,chip内含指令寄存器z data retention: 10years 这是由其构成的产品(如SSD)的最长使用时间,所以看到SSD的使用寿命为10年z封装方式: 48pin--PCB0/PIB0 52pin—ICB0/IIB02.芯片的结构以及容量参数z每块chip内含有的block数:8K(8192),z每个block内含有的page数: 128z每个page的容量为(2K+64)Byte,这是页编程的单位z每个block的容量为(256K+8K) Byte,这是块擦除的单位z每块chip的容量为(2G+64M) Byte(K9LAG0U0M型号)3.芯片操作的典型时间:注意:Read和program 操作都是针对page的,erase操作是针对block的;Program和erase都属于写操作范围,与read操作对应Page read operation:随机读时间(random read) tR:60us (data从flash memory到data register的时间)串行访问时间(serial access)tREA:30ns(data从data register输出到IO的时间,这个参数随着容量增加而增加)Page program operation:Program time tPROG(data从data register编程到memory cell的时间):800usBlock erase time tBERS: 1.5ms4.芯片的引脚功能z IO0~IO7: program时作为command address data输入,read时command address 输入和data输出,芯片未选中时保持高阻状态zz CLE: command锁存使能,CLE高电平时,WE~的上升沿将command锁存入内部command registerz ALE:address锁存使能,ALE高电平时,WE~的上升沿将address锁存入内部address register,因address长度的不同所需地址周期也不同z RE~:使得在data register中的data输出,RE下降沿tREA时间后输出有效(这是serial access time),并将自动增加内部page的column地址计数器(能够连续读取data)z WE~:WE上升沿时可以写入command address dataz WP~:写保护端,在上电/断电瞬间有效,有效时将禁止program/erase操作z R/B~:高时表明flash芯片准备好待操作,低时表明正在进行program/erase/ random read 操作;random read operation是data从memory cell到data register的这段操作,random write是data从data register到memory cell这一段操作;当data在memory cell和data register之间交换时(包括随机读和随机写)RB~出现低电平表z Vcc:powerz Vss:groundz NC:not connect5. 芯片操作时的寻址周期:z A0~A11: column address 访问范围2K(一个page)z A12~A31: row address 访问chip中的8K个block 及block中的128个page地址(13+7)z每个cycle传送8位address, column address和row address不能在同一个cycle里传送,不足的address位接低电平0z可知传送一个完整地址需要2个column寻址周期+3个row寻址周期,一共5个周期z Block erase只需要3个rom 寻址周期(为何不是2个?)z每个page的Spare 64Byte 的访问是column address的最后64(2048~2111)6. 指令执行所需周期数Block erase, page program, page read等指令需要2周期(但并不连续,一般是在第一个命令周期内发送寻址命令,第二个命令周期内发送数据传送命令)reset, status read等指令只需要一个周期7. flash芯片操作指令一览8.read flow、program flow、erase flow注意program flow, erase flow依靠R/B~ 和IO0来判断过程是否完成,read flow通过校验ECC来判断过程是否完成14.关于芯片的坏块z Flash芯片出厂时可能含有少量坏块(invalid block)z坏块数量会随使用时间的增加而增加z一个坏块不会影响其他好块,这与结构有关z三星公司保证每块flash芯片的第一个block是好块z三星公司保证坏块的最后一个page中没有FFh数据(address:2048),这也是检测坏块的方法(在K9WBG08U0M芯片中块定义不同)15.flash芯片的interleave 操作Interleave操作允许同时操作一个chip中的两个die,以interleave page program为例:阶段A:die1进入编程阶段,R/B~1显示忙,此时可以继续向die2发送命令阶段B:die1和die2都进入编程阶段,R/B~1和R/B~2都显示忙阶段C:die1已经完成编程,die2仍在编程中阶段D:die1和die2都完成编程,R/B~显示空闲,可以再次进行interleave操作HYQ2009-3-27。

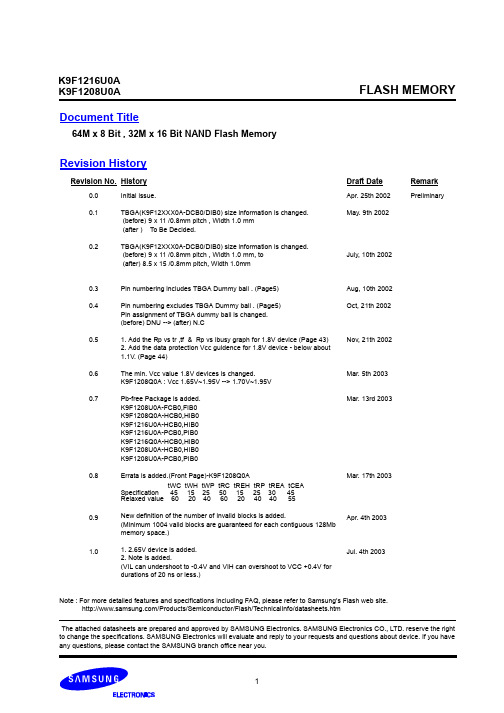

K9F1208U0A芯片资料_SAMSUNG_

FLASH MEMORYK9F1208U0AK9F1216U0A Document Title64M x 8 Bit , 32M x 16 Bit NAND Flash MemoryRevision HistoryThe attached datasheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the rightto change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you have Revision No.0.00.10.20.30.40.50.60.70.80.91.0RemarkPreliminaryHistoryInitial issue.TBGA(K9F12XXX0A-DCB0/DIB0) size information is changed. (before) 9 x 11 /0.8mm pitch , Width 1.0 mm (after ) To Be Decided.TBGA(K9F12XXX0A-DCB0/DIB0) size information is changed. (before) 9 x 11 /0.8mm pitch , Width 1.0 mm, to (after) 8.5 x 15 /0.8mm pitch, Width 1.0mmPin numbering includes TBGA Dummy ball . (Page5)Pin numbering excludes TBGA Dummy ball . (Page5)Pin assignment of TBGA dummy ball is changed.(before) DNU --> (after) N.C1. Add the Rp vs tr ,tf & Rp vs ibusy graph for 1.8V device (Page 43)2. Add the data protection Vcc guidence for 1.8V device - below about 1.1V. (Page 44)The min. Vcc value 1.8V devices is changed.K9F1208Q0A : Vcc 1.65V~1.95V --> 1.70V~1.95V Pb-free Package is added.K9F1208U0A-FCB0,FIB0K9F1208Q0A-HCB0,HIB0K9F1216U0A-HCB0,HIB0K9F1216U0A-PCB0,PIB0K9F1216Q0A-HCB0,HIB0K9F1208U0A-HCB0,HIB0K9F1208U0A-PCB0,PIB0Errata is added.(Front Page)-K9F1208Q0AtWC tWH tWP tRC tREH tRP tREA tCEA Specification 45 15 25 50 15 25 30 45Relaxed value 60 20 40 60 20 40 40 55New definition of the number of invalid blocks is added.(Minimum 1004 valid blocks are guaranteed for each contiguous 128Mb memory space.)1. 2.65V device is added.2. Note is added.(VIL can undershoot to -0.4V and VIH can overshoot to VCC +0.4V for durations of 20 ns or less.)Draft DateApr. 25th 2002May. 9th 2002July, 10th 2002Aug, 10th 2002Oct, 21th 2002Nov, 21th 2002Mar. 5th 2003Mar. 13rd 2003Mar. 17th 2003Apr. 4th 2003Jul. 4th 2003Note : For more detailed features and specifications including FAQ, please refer to Samsung’s Flash web site. /Products/Semiconductor/Flash/TechnicalInfo/datasheets.htmFLASH MEMORYK9F1208U0AK9F1216U0A Document Title64M x 8 Bit , 32M x 16 Bit NAND Flash MemoryRevision HistoryThe attached datasheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the rightto change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you have Revision No.1.11.21.31.41.5RemarkHistoryErrata is deleted.AC parameters are changed.-K9F1208Q0AtWC tWH tWP tRC tREH tRP tREA tCEA Before 45 15 25 50 15 25 30 45After 60 20 40 60 20 40 40 551. K9F1208Q0A-DC(I)B0,K9F1216Q0A-DC(I)B0, K9F1208D0A-DC(I)B0, K9F1216D0A-DC(I)B0,K9F1208U0A-DC(I)B0, K9F1216U0A-DC(I)B0 are deleted.1. Add the Protrusion/Burr value in WSOP1 PKG Diagram .1. PKG(TSOP1, WSOP1) Dimension Change 1. NAND Flash Technical Notes is changed.-Invalid block -> initial invalid block ( page 16 ) -Error in write or read operation ( page 17 ) -Program Flow Chart ( page 17 )Draft DateAug. 1st 2003Oct. 14th 2003Apr. 24th 2004May. 24th 2004Oct. 25th. 2004Note : For more detailed features and specifications including FAQ, please refer to Samsung’s Flash web site. /Products/Semiconductor/Flash/TechnicalInfo/datasheets.htmFLASH MEMORYK9F1208U0AK9F1216U0A GENERAL DESCRIPTIONFEATURES• Voltage Supply -2.7 ~ 3.6 V • Organization- Memory Cell Array- X8 device(K9F1208U0A) : (64M + 2048K)bit x 8 bit - X16 device(K9F1216U0A) : (32M + 1024K)bit x 16bit - Data Register- X8 device(K9F1208U0A) : (512 + 16)bit x 8bit - X16 device(K9F1216U0A) : (256 + 8)bit x16bit • Automatic Program and Erase - Page Program- X8 device(K9F1208U0A) : (512 + 16)Byte - X16 device(K9F1216U0A) : (256 + 8)Word - Block Erase :- X8 device(K9F1208U0A) : (16K + 512)Byte - X16 device(K9F1216U0A) : ( 8K + 256)Word • Page Read Operation - Page Size- X8 device(K9F1208U0A) : (512 + 16)Byte - X16 device(K9F1216U0A) : (256 + 8)Word - Random Access : 12µs(Max.) - Serial Page Access : 50ns(Min.)• Fast Write Cycle Time- Program time : 200µs(Typ.) - Block Erase Time : 2ms(Typ.)64M x 8 Bit / 32M x 16 Bit NAND Flash Memory• Command/Address/Data Multiplexed I/O Port • Hardware Data Protection- Program/Erase Lockout During Power Transitions • Reliable CMOS Floating-Gate Technology- Endurance : 100K Program/Erase Cycles - Data Retention : 10 Years • Command Register Operation • Intelligent Copy-Back• Unique ID for Copyright Protection • Package- K9F12XXU0A-YCB0/YIB048 - Pin TSOP I (12 x 20 / 0.5 mm pitch) - K9F1208U0A-VCB0/VIB048 - Pin WSOP I (12X17X0.7mm) - K9F12XXU0A-PCB0/PIB048 - Pin TSOP I (12 x 20 / 0.5 mm pitch)- Pb-free Package - K9F1208U0A-FCB0/FIB048 - Pin WSOP I (12X17X0.7mm)- Pb-free Package * K9F1208U0A-V,F(WSOPI ) is the same device as K9F1208U0A-Y ,P(TSOP1) except package type.Offered in 64Mx8bit or 32Mx16bit, the K9F12XXU0A is 512M bit with spare 16M bit capacity. The device is offered in 3.3V Vcc. Its NAND cell provides the most cost-effective solutIon for the solid state mass storage market. A program operation can be performed in typical 200µs on the 528-byte(X8 device) or 264-word(X16 device) page and an erase operation can be performed in typical 2ms on a 16K-byte(X8 device) or 8K-word(X16 device) block. Data in the page can be read out at 50ns cycle time per byte(X8 device) or word(X16 device). The I/O pins serve as the ports for address and data input/output as well as command input. The on-chip write con-trol automates all program and erase functions including pulse repetition, where required, and internal verification and margining of data. Even the write-intensive systems can take advantage of the K9F12XXU0A ′s extended reliability of 100K program/erase cycles by providing ECC(Error Correcting Code) with real time mapping-out algorithm. The K9F12XXU0A is an optimum solution for large nonvolatile storage applications such as solid state file storage and other portable applications requiring non-volatility.PRODUCT LISTPart Number Vcc RangeOrganizationPKG Type K9F1208U0A-Y ,P 2.7 ~ 3.6V X8TSOP1K9F1208U0A-V,F WSOP1K9F1216U0A-Y ,PX16TSOP1FLASH MEMORYK9F1208U0AK9F1216U0A PIN CONFIGURATION (TSOP1)K9F12XXU0A-YCB0,PCB0/YIB0,PIB0N.C N.C N.C N.C N.C N.C R/B RE CE N.C N.C Vcc Vss N.C N.C CLE ALE WE WP N.C N.C N.C N.C N.CVss I/O15I/O7I/O14I/O6I/O13I/O5I/O12I/O4N.C N.C Vcc N.C N.C N.C I/O11I/O3I/O10I/O2I/O9I/O1I/O8I/O0Vss123456789101112131415161718192021222324484746454443424140393837363534333231302928272625N.C N.C N.C N.C N.C N.C R/B RE CE N.C N.C Vcc Vss N.C N.C CLE ALE WE WP N.C N.C N.C N.C N.CN.C N.C N.C N.C I/O7I/O6I/O5I/O4N.C N.C N.C Vcc Vss N.C N.C N.C I/O3I/O2I/O1I/O0N.C N.C N.C N.CX8X16X16X8PACKAGE DIMENSIONS48-PIN LEAD/LEAD FREE PLASTIC THIN SMALL OUT-LINE PACKAGE TYPE(I)48 - TSOP1 - 1220FUnit :mm/Inch0.787±0.00820.00±0.20#1#240.16+0.07-0.030.008+0.003-0.0010.500.0197#48#250.48812.40M A X12.000.4720.10 0.004M A X 0.250.010()0.039±0.0021.00±0.050.0020.05MIN0.0471.20MAX0.45~0.750.018~0.0300.724±0.00418.40±0.100~8°0.0100.25T Y P0.125+0.0750.0350.005+0.003-0.0010.500.020()0.20+0.07-0.03FLASH MEMORYK9F1208U0AK9F1216U0A PIN DESCRIPTIONNOTE : Connect all V CC and V SS pins of each device to common power supply outputs.Do not leave V CC or V SS disconnected.Pin Name Pin FunctionI/O 0 ~ I/O 7(K9F1208X0A)I/O 0 ~ I/O 15(K9F1216X0A)DATA INPUTS/OUTPUTSThe I/O pins are used to input command, address and data, and to output data during read operations. The I/O pins float to high-z when the chip is deselected or when the outputs are disabled.I/O8 ~ I/O15 are used only in X16 organization device. Since command input and address input are x8 oper-ation, I/O8 ~ I/O15 are not used to input command & address. I/O8 ~ I/O15 are used only for data input and output.CLECOMMAND LATCH ENABLEThe CLE input controls the activating path for commands sent to the command register. When active high, commands are latched into the command register through the I/O ports on the rising edge of the WE signal.ALEADDRESS LATCH ENABLEThe ALE input controls the activating path for address to the internal address registers. Addresses are latched on the rising edge of WE with ALE high.CECHIP ENABLEThe CE input is the device selection control. When the device is in the Busy state, CE high is ignored, and the device does not return to standby mode in program or erase operation. Regarding CE control during read operation, refer to ’Page read’ section of Device operation .REREAD ENABLEThe RE input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid tREA after the falling edge of RE which also increments the internal column address counter by one.WEWRITE ENABLEThe WE input controls writes to the I/O port. Commands, address and data are latched on the rising edge of the WE pulse.WPWRITE PROTECTThe WP pin provides inadvertent write/erase protection during power transitions. The internal high voltage generator is reset when the WP pin is active low.R/BREADY/BUSY OUTPUTThe R/B output indicates the status of the device operation. When low, it indicates that a program, erase or random read operation is in process and returns to high state upon completion. It is an open drain output and does not float to high-z condition when the chip is deselected or when outputs are disabled.Vcc QOUTPUT BUFFER POWERVcc Q is the power supply for Output Buffer.Vcc Q is internally connected to Vcc, thus should be biased to Vcc.Vcc POWERV CC is the power supply for device. Vss GROUNDN.C NO CONNECTIONLead is not internally connected.DNUDO NOT USELeave it disconnected.FLASH MEMORYK9F1208U0AK9F1216U0A Product IntroductionThe K9F1208X0A is a 528Mbit(553,648,218 bit) memory organized as 131,072 rows(pages) by 528 columns. Spare sixteen columns are located from column address of 512 to 527. A 528-byte(x8 device), 264word(x16 device) data register is connected to memory cell arrays accommodating data transfer between the I/O buffers and memory during page read and page program operations. The memory array is made up of 16 cells that are serially connected to form a NAND structure. Each of the 16 cells resides in a different page. A block consists of two NAND structured strings. A NAND structure consists of 16 cells. Total 135168 NAND cells reside in a block. The array organization is shown in Figure 2. The program and read operations are executed on a page basis, while the erase operation is executed on a block basis. The memory array consists of 4,096 separately erasable 16K-byte blocks. It indicates that the bit by bit erase operation is prohibited on the K9F1208X0A.The K9F1208X0A has addresses multiplexed into 8 I/O's. This scheme dramatically reduces pin counts and allows systems upgrades to future densities by maintaining consistency in system board design. Command, address and data are all written through I/O's by bringing WE to low while CE is low. Data is latched on the rising edge of WE. Command Latch Enable(CLE) and Address Latch Enable(ALE) are used to multiplex command and address respectively, via the I/O pins. The 64M byte physical space requires 26addresses(X8 device) or 25 addresses(X16 device), thereby requiring four cycles for byte-level addressing: column address, low row address and high row address, in that order. Page Read and Page Program need the same four address cycles following the required command input. In Block Erase operation, however, only the three row address cycles are used. Device operations are selected by writing specific commands into the command register. Table 1 defines the specific commands of the K9F1208X0A.The device provides simultaneous program/erase capability up to four pages/blocks. By dividing the memory array into four 128Mbit separate planes, simultaneous multi-plane operation dramatically increases program/erase performance by 4X while still maintaining the conventional 512 byte(X8 device) or 256 word(X16 device) structure.The extended pass/fail status for multi-plane program/erase allows system software to quickly identify the failing page/block out of selected multiple pages/blocks. Usage of multi-plane operations will be described further throughout this document.In addition to the enhanced architecture and interface, the device incorporates copy-back program feature from one page to another of the same plane without the need for transporting the data to and from the external buffer memory. Since the time-consuming burst-reading and data-input cycles are removed, system performance for solid-state disk application is significantly increased.The device includes one block sized OTP(One Time Programmable), which can be used to increase system security or to provide identification capabilities. Detailed information can be obtained by contact with Samsung.Table 1. Command SetsNOTE : 1. The 00h command defines starting address of the 1st half of registers.The 01h command defines starting address of the 2nd half of registers.After data access on the 2nd half of register by the 01h command, the status pointer is automatically moved to the 1st half register(00h) on the next cycle.2. Page Program(True) and Copy-Back Program(True) are available on 1 plane operation.Page Program(Dummy) and Copy-Back Program(Dummy) are available on the 2nd,3rd,4th plane of multi plane operation. 3. The 71h command should be used for read status of Multi Plane operation.Caution : Any undefined command inputs are prohibited except for above command set of Table 1.Function1st. Cycle 2nd. Cycle3rd. CycleAcceptable Commandduring BusyRead 100h/01h (1)--Read 250h --Read ID 90h --ResetFFh --OPage Program (True)(2)80h 10h -Page Program (Dummy)(2)80h 11h -Copy-Back Program(True)(2)00h 8Ah 10h Copy-Back Program(Dummy)(2)03h 8Ah 11h Block Erase60h D0h -Multi-Plane Block Erase 60h----60hD0h -Read Status70h --O Read Multi-Plane Status71h (3)--OFLASH MEMORYK9F1208U0AK9F1216U0A RECOMMENDED OPERATING CONDITIONS(Voltage reference to GND, K9F12XXU0A-XCB0 :T A =0 to 70°C, K9F12XXU0A-XIB0:T A =-40 to 85°C)ParameterSymbol Min Typ.Max Unit Supply Voltage V CC 2.7 3.3 3.6V Supply Voltage V CCQ 2.7 3.3 3.6V Supply VoltageV SSVABSOLUTE MAXIMUM RATINGSNOTE :1. Minimum DC voltage is -0.6V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <30ns. Maximum DC voltage on input/output pins is V CC,+0.3V which, during transitions, may overshoot to V CC +2.0V for periods <20ns.2. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect reliability.ParameterSymbol Rating Unit Voltage on any pin relative to V SSV IN/OUT -0.6 to + 4.6VV CC -0.6 to + 4.6V CCQ-0.6 to + 4.6Temperature Under Bias K9F12XXU0A-XCB0T BIAS -10 to +125°C K9F12XXU0A-XIB0-40 to +125Storage Temperature K9F12XXU0A-XCB0T STG -65 to +150°C K9F12XXU0A-XIB0Short Circuit CurrentIos5mAFLASH MEMORYK9F1208U0AK9F1216U0A DC AND OPERATING CHARACTERISTICS (Recommended operating conditions otherwise noted.)NOTE : VIL can undershoot to -0.4V and VIH can overshoot to VCC +0.4V for durations of 20 ns or less.ParameterSymbol Test ConditionsMin Typ Max Min Typ Max UnitOperating CurrentSequential Read I CC 1tRC=50ns, CE=V IL I OUT =0mA-1020-1020mA ProgramI CC 2--1020-1020EraseI CC 3--1020-1020Stand-by Current(TTL)I SB 1CE=V IH , WP=0V/V CC --1--1Stand-by Current(CMOS)I SB 2CE=V CC -0.2, WP=0V/V CC -1050-1050µA Input Leakage Current I LI V IN =0 to Vcc(max)--±10--±10Output Leakage CurrentI LOV OUT =0 to Vcc(max)--±10--±10Input High Voltage V IH*I/O pinsV CCQ -0.4-V CCQ +0.3 2.0-V CCQ +0.3V Except I/O pinsV CC -0.4-V CC +0.3 2.0-V CC +0.3Input Low Voltage, All inputs V IL*--0.3-0.5-0.3-0.8Output High Voltage Level V OH I OH =-400µA V CCQ -0.4-- 2.4--Output Low Voltage Level V OLI OL =2.1mA--0.4--0.4Output Low Current(R/B)I OL (R/B)V OL =0.4V34-810-mAFLASH MEMORYK9F1208U0AK9F1216U0A CAPACITANCE (T A =25°C, V CC =3.3V, f=1.0MHz)NOTE : Capacitance is periodically sampled and not 100% tested.ItemSymbol Test ConditionMin Max Unit Input/Output Capacitance C I/O V IL =0V -10pF Input CapacitanceC INV IN =0V-10pFVALID BLOCKNOTE :1. The device may include invalid blocks when first shipped. Additional invalid blocks may develop while being used. The number of valid blocks is pre-sented with both cases of invalid blocks considered. Invalid blocks are defined as blocks that contain one or more bad bits . Do not erase or program factory-marked bad blocks. Refer to the attached technical notes for a appropriate management of invalid blocks.2. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block, does not require Error Correction up to 1K Program/Erase cycles.3. Minimum 1004 valid blocks are guaranteed for each contiguous 128Mb memory space.ParameterSymbol Min Typ.Max Unit Valid Block NumberN VB4,026-4,096BlocksAC TEST CONDITION(K9F12XXU0A-XCB0 :TA=0 to 70°C, K9F12XXU0A-XIB0:TA=-40 to 85°C, K9F12XXU0A : Vcc=2.7V~3.6V unless otherwise noted)ParameterK9F12XXU0A Input Pulse Levels 0.4V to 2.4VInput Rise and Fall Times 5ns Input and Output Timing Levels1.5VK9F12XXU0A:Output Load (Vcc Q :3.0V +/-10%) 1 TTL GATE and CL=50pF K9F12XXU0A:Output Load (Vcc Q :3.3V +/-10%)1 TTL GATE and CL=100pFMODE SELECTIONNOTE : 1. X can be V IL or V IH.2. WP should be biased to CMOS high or CMOS low for standby.CLE ALE CE WERE WP ModeH L L H X Read Mode Command Input L H L H X Address Input(4clock)H L L H H Write Mode Command Input L H L H H Address Input(4clock)L L L HH Data Input L L L H X Data OutputL L L H H X During Read(Busy) on K9F1208U0A-Y ,P ,V,FX X X X H X During Read(Busy) on the devices except K9F1208U0A-Y ,P ,V,F X X X X X H During Program(Busy)X X X X X H During Erase(Busy)X X (1)X X X LWrite ProtectXXHXX0V/V CC (2) Stand-byFLASH MEMORYK9F1208U0AK9F1216U0A AC TIMING CHARACTERISTICS FOR COMMAND / ADDRESS / DATA INPUTNOTE : 1. If tCS is set less than 10ns, tWP must be minimum 35ns, otherwise, tWP may be minimum 25ns.ParameterSymbol Min Max Unit CLE setup Time t CLS 0-ns CLE Hold Time t CLH 10-ns CE setup Time t CS 0-ns CE Hold Time t CH 10-ns WE Pulse Width t WP 25(1)-ns ALE setup Time t ALS 0-ns ALE Hold Time t ALH 10-ns Data setup Time t DS 20-ns Data Hold Time t DH 10-ns Write Cycle Time t WC 50-ns WE High Hold Timet WH15-nsPROGRAM / ERASE CHARACTERISTICSNOTE : 1. Typical program time is defined as the time within which more than 50% of the whole pages are programmed at Vcc of 3.3V and temperature of 25°C.ParameterSymbol Min Typ Max Unit Program Time t PROG -200500µs Dummy Busy Time for Multi Plane Program t DBSY 110µs Number of Partial Program Cycles in the Same Page Main Array Nop --1cycle Spare Array--2cycles Block Erase Timet BERS-23msFLASH MEMORYK9F1208U0AK9F1216U0A AC CHARACTERISTICS FOR OPERATIONNOTE : 1. If reset command(FFh) is written at Ready state, the device goes into Busy for maximum 5us. 2. To break the sequential read cycle, CE must be held high for longer time than tCEH. 3. The time to Ready depends on the value of the pull-up resistor tied R/B pin.ParameterSymbol Min Max Unit Data Transfer from Cell to Register t R -12µs ALE to RE Delay t AR 10-ns CLE to RE Delay t CLR 10-ns Ready to RE Low t RR 20-ns RE Pulse Width t RP 25-ns WE High to Busy t WB -100ns Read Cycle Time t RC 50-ns RE Access Time t REA -30ns CE Access Time t CEA -45ns RE High to Output Hi-Z t RHZ -30ns CE High to Output Hi-Z t CHZ -20ns RE or CE High to Output hold t OH 15-ns RE High Hold Time t REH 15-ns Output Hi-Z to RE Low t IR 0-ns WE High to RE Lowt WHR 60-ns Device resetting time(Read/Program/Erase)t RST-5/10/500(1)µsParameterSymbol Min Max Unit K9F1208U0A-Y ,P ,V,F or K9F1208D0A-Y ,P onlyLast RE High to Busy(at sequential read)t RB -100ns CE High to Ready(in case of interception by CE at read)t CRY -50 +tr(R/B)(3)ns CE High Hold Time(at the last serial read)(2)t CEH100-nsFLASH MEMORYK9F1208U0AK9F1216U0A NAND Flash Technical NotesIdentifying Initial Invalid Block(s)Initial Invalid Block(s)Initial invalid blocks are defined as blocks that contain one or more initial invalid bits whose reliability is not guaranteed by Samsung.The information regarding the initial invalid block(s) is so called as the initial invalid block information. Devices with initial invalid block(s) have the same quality level as devices with all valid blocks and have the same AC and DC characteristics. An initial invalid block(s) does not affect the performance of valid block(s) because it is isolated from the bit line and the common source line by a select transistor. The system design must be able to mask out the initial invalid block(s) via address mapping. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block, does not require Error Correction up to 1K program/erase cycles.All device locations are erased(FFh) except locations where the initial invalid block(s) information is written prior to shipping. The initial invalid block(s) status is defined by the 6th byte(X8 device) or 1st word(X16 device) in the spare area. Samsung makes sure that either the 1st or 2nd page of every initial invalid block has non-FFh(X8 device) or non-FFFFh(X16 device) data at the column address of 517(X8 device) or 256 and 261(X16 device). Since the initial invalid block information is also erasable in most cases, it is impossible to recover the information once it has been erased. Therefore, the system must be able to recognize the initial invalid block(s) based on the initial invalid block information and create the initial invalid block table via the following suggested flow chart(Figure 4). Any intentional erasure of the initial invalid block information is prohibited.*Check "FFh" at the column addressFigure 4. Flow chart to create initial invalid block table.StartSet Block Address = 0Check "FFh" ?Increment Block AddressLast Block ?EndNoYesYesCreate (or update)NoInitialof the 1st and 2nd page in the block517(X8 device) or 256 and 261(X16 device) Invalid Block(s) TableFLASH MEMORYK9F1208U0AK9F1216U0A NAND Flash Technical Notes (Continued)Program Flow ChartStartI/O 6 = 1 ?I/O 0 = 0 ?No*Write 80hWrite AddressWrite DataWrite 10hRead Status RegisterProgram Completedor R/B = 1 ?Program ErrorYesNoYesError in write or read operationWithin its life time, the additional invalid blocks may develop with NAND Flash memory. Refer to the qualification report for the actual data.The following possible failure modes should be considered to implement a highly reliable system. In the case of status read fail-ure after erase or program, block replacement should be done. Because program status fail during a page program does not affect the data of the other pages in the same block, block replacement can be executed with a page-sized buffer by finding an erased empty block and reprogramming the current target data and copying the rest of the replaced block. In case of Read, ECC must be employed. To improve the efficiency of memory space, it is recommended that the read or verification failure due to single bit error be reclaimed by ECC without any block replacement. The said additional block failure rate does not include those reclaimed blocks.Failure ModeDetection and Countermeasure sequenceWrite Erase Failure Status Read after Erase --> Block Replacement Program Failure Status Read after Program --> Block Replacement ReadSingle Bit FailureVerify ECC -> ECC CorrectionECC: Error Correcting Code --> Hamming Code etc. Example) 1bit correction & 2bit detection: If program operation results in an error, map out the block including the page in error and copy the*target data to another block.FLASH MEMORYK9F1208U0AK9F1216U0A Samsung NAND Flash has three address pointer commands as a substitute for the two most significant column addresses. ’00h’command sets the pointer to ’A’ area(0~255byte), ’01h’ command sets the pointer to ’B’ area(256~511byte), and ’50h’ command sets the pointer to ’C’ area(512~527byte). With these commands, the starting column address can be set to any of a whole page(0~527byte). ’00h’ or ’50h’ is sustained until another address pointer command is inputted. ’01h’ command, however, is effective only for one operation. After any operation of Read, Program, Erase, Reset, Power_Up is executed once with ’01h’ command, the address pointer returns to ’A’ area by itself. To program data starting from ’A’ or ’C’ area, ’00h’ or ’50h’ command must be inputted before ’80h’ command is written. A complete read operation prior to ’80h’ command is not necessary. To program data starting from ’B’ area, ’01h’ command must be inputted right before ’80h’ command is written.00h(1) Command input sequence for programming ’A’ areaAddress / Data input80h10h00h80h10hAddress / Data inputThe address pointer is set to ’A’ area(0~255), and sustained01h(2) Command input sequence for programming ’B’ areaAddress / Data input80h10h01h80h10hAddress / Data input’B’, ’C’ area can be programmed.It depends on how many data are inputted.’01h’ command must be rewritten before every program operationThe address pointer is set to ’B’ area(256~511), and will be reset to ’A’ area after every program operation is executed.50h(3) Command input sequence for programming ’C’ areaAddress / Data input80h10h50h80h10hAddress / Data inputOnly ’C’ area can be programmed.’50h’ command can be omitted.The address pointer is set to ’C’ area(512~527), and sustained’00h’ command can be omitted.It depends on how many data are inputted.’A’,’B’,’C’ area can be programmed.Pointer Operation of K9F1208X0A(X8)Table 2. Destination of the pointerCommandPointer position Area 00h 01h 50h0 ~ 255 byte 256 ~ 511 byte 512 ~ 527 byte1st half array(A)2nd half array(B)spare array(C)"A" area 256 Byte(00h plane)"B" area (01h plane)"C" area (50h plane)256 Byte16 Byte"A""B""C"Internal Page RegisterPointer select commnad(00h, 01h, 50h)PointerFigure 5. Block Diagram of Pointer OperationFLASH MEMORYK9F1208U0AK9F1216U0A Samsung NAND Flash has two address pointer commands as a substitute for the most significant column address. ’00h’ command sets the pointer to ’A’ area(0~255word), and ’50h’ command sets the pointer to ’B’ area(256~263word). With these commands, the starting column address can be set to any of a whole page(0~263word). ’00h’ or ’50h’ is sustained until another address pointer com-mand is inputted. To program data starting from ’A’ or ’B’ area, ’00h’ or ’50h’ command must be inputted before ’80h’ command is writ-ten. A complete read operation prior to ’80h’ command is not necessary.00h(1) Command input sequence for programming ’A’ areaAddress / Data input80h10h00h80h10hAddress / Data inputThe address pointer is set to ’A’ area(0~255), and sustained50h(2) Command input sequence for programming ’B’ areaAddress / Data input80h10h50h80h10hAddress / Data inputOnly ’B’ area can be programmed.’50h’ command can be omitted.The address pointer is set to ’B’ area(256~263), and sustained’00h’ command can be omitted.It depends on how many data are inputted.’A’,’B’ area can be programmed.Pointer Operation of K9F1216X0A(X16)Table 3. Destination of the pointerCommandPointer position Area 00h 50h0 ~ 255 word 256 ~ 263 wordmain array(A)spare array(B)"A" area 256 Word(00h plane)"B" area (50h plane)8 Word"A""B"Internal Page RegisterPointer select command (00h, 50h)PointerFigure 6. Block Diagram of Pointer Operation。

K9F1208中文资料

NAND Flash芯片K9F1208资料一 NAND FlaSh和NOR Flash闪存(Flash Memory)由于其具有非易失性、电可擦除性、可重复编程以及高密度、低功耗等特点,被广泛地应用于手机、MP3、数码相机、笔记本电脑等数据存储设备中。

NAND Flash和NOR Flash是目前市场上两种主要的非易失闪存芯片。

与NOR Flash相比,NAND Flash 在容量、功耗、使用寿命等方面的优势使其成为高数据存储密度的理想解决方案。

NOR Flash的传输效率很高,但写入和擦除速度较低;而NAND Flash以容量大、写速度快、芯片面积小、单元密度高、擦除速度快、成本低等特点,在非易失性类存储设备中显现出强劲的市场竞争力。

结构:NOR Flash为并行,NAND Flash为串行。

总线:NOR Flash为分离的地址线和数据线,而NANDFlash为复用的。

尺寸:典型的NAND Flash尺寸为NOR Flash尺寸的1/8。

坏块:NAND器件中的坏块是随机分布的,需要对介质进行初始化扫描以发现坏块,并将坏块标记为不可用。

位交换:NAND Flash中发生的次数要比NOR Flash多,建议使用NAND闪存时,同时使用EDC/ECC算法。

使用方法:NOR Flash是可在芯片内执行(XIP,eXecute In Place),应用程序可以直接在FIash闪存内运行,不必再把代码读到系统RAM 中;而NAND Flash则需I/O接口,因此使用时需要写入驱动程序。

通过以上的分析和比较,NAND Flash更适合于大容量数据存储的嵌入式系统。

本设计选用Samsung公司生产的NAND Flash存储器芯片K9F1208作为存储介质,并应用在基于uPSD3234A增强型8051单片机的嵌入式系统中。

二K9F1208介绍K9F1208是Samsung公司生产的512 Mb(64M×8位)NAND Flash 存储器。

flash 存储器分类

flash 存储器分类全球闪速存储器的技术主要掌握在AMD、ATMEL、Fujistu、Hitachi、Hyundai、Intel、Micron、Mitsubishi、Samsung、SST、SHARP、TOSHIBA,由于各自技术架构的不同,分为几大阵营。

1. NOR技术NORNOR技术(亦称为Linear技术)闪速存储器是最早出现的Flash Memory,目前仍是多数供应商支持的技术架构。

它源于传统的EPROM器件,与其它Flash Memory技术相比,具有可靠性高、随机读取速度快的优势,在擦除和编程操作较少而直接执行代码的场合,尤其是纯代码存储的应用中广泛使用,如PC的BIOS固件、移动电话、硬盘驱动器的控制存储器等。

NOR技术Flash Memory具有以下特点:(1) 程序和数据可存放在同一芯片上,拥有独立的数据总线和地址总线,能快速随机读取,允许系统直接从Flash中读取代码执行,而无需先将代码下载至RAM中再执行;(2)可以单字节或单字编程,但不能单字节擦除,必须以块为单位或对整片执行擦除操作,在对存储器进行重新编程之前需要对块或整片进行预编程和擦除操作。

由于NOR技术Flash Memory的擦除和编程速度较慢,而块尺寸又较大,因此擦除和编程操作所花费的时间很长,在纯数据存储和文件存储的应用中,NOR技术显得力不从心。

不过,仍有支持者在以写入为主的应用,如CompactFlash卡中继续看好这种技术。

Intel公司的StrataFlash家族中的最新成员——28F128J3,是迄今为止采用NOR技术生产的存储容量最大的闪速存储器件,达到128Mb(位),对于要求程序和数据存储在同一芯片中的主流应用是一种较理想的选择。

该芯片采用0.25μm制造工艺,同时采用了支持高存储容量和低成本的MLC技术。

所谓MLC技术(多级单元技术)是指通过向多晶硅浮栅极充电至不同的电平来对应不同的阈电压,代表不同的数据,在每个存储单元中设有4个阈电压(00/01/10/11),因此可以存储2b信息;而传统技术中,每个存储单元只有2个阈电压(0/1),只能存储1b信息。

K9F2G08U0A 中文数据手册

8

K9F2G08R0A K9F2G08U0A

图1. K9F2G08X0A 功能框图

VCC VSS

A12 - A28(地址) A0 - A11(地址)

X-Buffers Latches & Decoders

(行地址锁存缓存区&译码)

Y-Buffers Latches & Decoders

(列地址锁存缓存区&译码)

63-∅0.45±0.05

∅ 0.20 M A B

底视图

#A1 索引标记(可选)

10.00±0.10 0.80 x 9= 7.20 0.80 x 5= 4.00

0.80 654321

A B

0.80

0.25(最小) 1.00(最大)

侧视图

13.00±0.10

2.00 0.45±0.05

0.80 x 7= 5.60 0.80 x 11= 8.80

13.00±0.10

6

K9F2G08R0A K9F2G08U0A

引脚配置 (ULGA封装)

7 6 5 4 3 2 1

K9F2G08U0A-ICB0/IIB0

A B C DE FG HJ K L M N

NC

NC

NC

NC

NC

NC

NC

/RE

NC

NC

NC

NC

NC

Vcc

NC

Vss

IO7

IO5

Vcc

/CE

NC

3

K9F2G08R0A K9F2G08U0A

引脚配置 (TSOP1封装)

K9F2G08U0A-PCB0/PIB0

N.C N.C

1 2

NAND Flash芯片K9F1208在uPSD3234A上的应用

总 线 : O l h为分 离 的地 址线 和数 据 线 , N N N R Fa s 而 A D

F ah为 复用 的 。 ls

尺 寸 : 型 的 NA l h尺 寸 为 N R Fah尺 寸 典 ND Fa s O l s

术 与 应 用 实 例 [ .北 京 : 民 邮 电 出 版社 ,0 5 M] 人 20. [ ]盛 群 半 导 体 股 份 有 限 公 司 .HT— D 30 3 I E 0 0使 用 手 册 ,0 4 20. [ ]广州 周 立功单 片机 发展 有 限公 司.Z G 0 4 L 50读卡 模块 应 用 文档 ,

系统 中。

性、 可重复编程 以及高密度 、 低功耗等特点 , 被广泛地应用

于手 机 、 3 数 码相 机 、 记 本 电脑 等 数 据 存 储 设 备 中 。 MP 、 笔 NA l h和 N R Fah是 目前 市 场 上 两 种 主 要 的非 NDFa s 0 l s

易失 闪 存 芯 片 。与 NOR Fls a h相 比 , NAND ls Fa h在 容

维普资讯

N F h芯 片 K 8 AN s D l a 9 1 0 F2 在 u S 3 3 A上 的应 用 P D 24

■ 武 汉 工 程 大 学 刘 芳 赵 振 华

以 S ms n a u g NAND F a h器 件 K9 1 0 ls F 2 8为 例 , 比 NAND ls 对 Fa h和 NOR Fa h的 异 同 ; 绍 大 容 量 ls 介

量 、 耗 、 用 寿 命 等 方 面 的优 势 使 其 成 为 高 数 据 存 储 密 功 使 度 的理 想 解 决 方 案 。NO l h的 传 输 效 率 很 高 , 写 入 R Fa s 但

嵌入式系统中Nand-Flash的原理及应用

嵌入式系统中Nand-Flash的原理及应用当前各类嵌入式系统开发设计中,存储模块是不可或缺的重要方面。

NOR 和NAND 是目前市场上两种主要的非易失闪存技术。

Nor-flash 存储器的容量较小、写入速度较慢,但因其随机读取速度快,因此在嵌入式系统中,常应用在程序代码的存储中。

Nor-flash 存储器的内部结构决定它不适合朝大容量发展; 而Nand-flash 存储器结构则能提供极高的单元密度,可以达到很大的存储容量,并且写入和擦除的速度也很快。

Nand-flash 存储器是flash 存储器的-种,其内部采用非线性宏单元模式,为固态大容量存储器的实现提供了廉价有效的解决方案。

Nand-flash 存储器具有容量较大,改写速度快,适用于大量资料的存储,因而在业界得到了越来越广泛的应用,如嵌入式产品中包括数码相机、MP3 随身听记忆卡、体积小巧的U 盘等。

本文以三星公司的K9F1208UOB 芯片为例,介绍Nand-flash 存储器芯片的读写流程和时序。

1 Nand-Flash 存储器的工作原理1.1 Nand-Flash 存储器的组成结构及指令集K9F1208UOB 的容量为64Mb,存储空间按128K 个页(行)、每页中528 个字节(列)的组成方式构成。

备用的16 列,位于列地址的512-527。

K9F1208UOB 还将存储空间分为块(block),每1 块由32 个页构成。

因此K9F1208UOB 中一共有4096 个块。

这种“块-页”结构,恰好能满足文件系统中划分簇和扇区的结构要求。

K9F1208UOB 的内部结构如图1 所示。

图1 K9F1208UOB 的内部结构K9F1208UOB 的读和写都以页为单位,擦除则以块为单位进行操作。

K9F1208UOB 的地址通过8 位端口传送,有效地节省了引脚的数量,并能够保持不同密度器件引脚的一致性,系统可以在电路不作改动的情况下升级为高容量存储器件。

Flash闪速存储器--(NAND和NOR比较)

Flash闪速存储器--(NAND和NOR比较)一、闪速存储器的特点闪速存储器(FlashMemory)是一类非易失性存储器NVM(Non-VolatileMemory)即使在供电电源关闭后仍能保持片内信息;而诸如DRAM、SRAM这类易失性存储器,当供电电源关闭时片内信息随即丢失。

FlashMemory集其它类非易失性存储器的特点:与EPROM相比较,闪速存储器具有明显的优势——在系统电可擦除和可重复编程,而不需要特殊的高电压(某些第一代闪速存储器也要求高电压来完成擦除和/或编程操作);与EEPROM相比较,闪速存储器具有成本低、密度大的特点。

其独特的性能使其广泛地运用于各个领域,包括嵌入式系统,如PC及外设、电信交换机、蜂窝电话、网络互联设备、仪器仪表和汽车器件,同时还包括新兴的语音、图像、数据存储类产品,如数字相机、数字录音机和个人数字助理(PDA)。

Flash的技术特点如下:(1)区块存储单元:在物理结构上分成若干个被称为区块的存储单元,不同区块之间相互独立,每个区块几KB~几十KB。

(2)先擦后写:任何flash器件的写入操作只能在空或已擦除的单元内进行,所以大多数情况下,在进行写入操作之前必须先执行擦除。

(3)位交换:有时一个比特位会发生反转,就是位交换。

(4)区块损坏:使用过程中,某些区块可能会被损坏,区块损坏后就不可修复。

二、闪速存储器的技术分类全球闪速存储器的主要供应商有AMD、ATMEL、Fujistu、Hitachi、Hyundai、Intel、Micron、Mitsubishi、Samsung、SST、SHARP、TOSHIBA,由于各自技术架构的不同,分为几大阵营。

1 NOR技术NOR技术(亦称为Linear技术)闪速存储器是最早出现的FlashMemory,目前仍是多数供应商支持的技术架构。

它源于传统的EPROM器件,与其它FlashMemory技术相比,具有可靠性高、随机读取速度快的优势,在擦除和编程操作较少而直接执行代码的场合,尤其是纯代码存储的应用中广泛使用,如PC 的BIOS固件、移动电话、硬盘驱动器的控制存储器等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

64M闪速存贮器K9K1208UOM及其应用作者:南华大学现代教育技术中心李松来源:《国外电子元器件》摘要:K9K1208UOM是SAMSUNG2公司生产的大容量非易失性闪速存贮器,本文介绍了K9K1208UOM的性能、结构、工作原理,并重点介绍了该闪速存储器的使用方法。

最后给出了K9K1208UOM的各状态寄存器的定义和命令集。

关键词:闪速存贮器页读页编程块擦除 K9K1208UOM1 引言非易失性闪速存贮器K9K1208UOM是SAMSUNG公司采用CMOS浮置门技术和与非存贮结构生产的大容量、高可靠存贮器件。

该器件所提供的片内控制器、状态寄存器和专用命令集使其可以灵活应用于各种存储系统电路,其8位I/O端口可以方便地实现地址、数据和命令的多路复用,这样不但大规模降低了引脚数,而且便于系统倔后扩充存贮容量而不需改变系统板结构设计。

对于诸如固态文件存储,声间和音频信号处理,便携式智能设备等要求大容量非易失存贮的应用场合,K9K1208UOM提供了一种极佳的解决方案。

2 基本性能和引脚功能2.1 基本特性K9K1208UOM非易失性闪速存贮器的基本特征如下:●工作电压:2.7~3.6V;●结构:存贮单元阵列:(64M+2047k)字节;数据寄存器:(512+16)×8位;●可自动编程与擦除;页编程:(512+16)字节;块擦除:(16k+512)字节。

●可进行528字节/页读操作:随机读:10µs;连续页读:60ns;●快写周期时间:编程时间为200µs(典型值);块擦除时间为2ms(典型值);●具有硬件数据保护功能;●使用寿命达100k次编程/擦除;●数据可保存10年。

2.2 引脚说明K9K1208UOM采用48脚TSOP封装,各引脚的功能如下:I/O0~I/O7:数据输入输出端,芯片未选中时为高阻态。

CLE:输入端,命令锁存使能。

ALE:输入端,地址锁存使能。

CE:输入端,芯片选择控制。

RE:输入端,数据输出控制,有效时数据送到I/O总线上。

WE:输入端,写I/O口控制、命令、地址或数据时在上升沿锁存。

SE:输入端,访问备用存贮区控制。

R/B:输出端,指示器件的操作状态。

Vcc:电源端。

Vss:地。

其它引脚为未用引脚。

3 器件结构与工作原理K9K1208UOM的528M位存贮单元可组成131072行(页)、528列的存贮阵列。

64M字节主存贮区按低位列地址(0~255字节)和高位列地址(256~511字节)分成两个半区,16列2048k字节备用存贮区位于列地址的512~527字节。

主存贮区每512字节和备用存贮区16字节工528字节组成一页。

共有131072页,每32页构成一个块,总共4096个块。

一个528字节的数据寄存器在与存贮阵列相连时,可在页读出和页写入过程中用I/O缓冲器和存贮器之间地数据传输。

K9K1208UOM的内部结构如图1所示。

K9K1208UOM的地址、数据和命令信号输入都使用8位I/O口,当CE为低时,命令、地址和数据在WE变低时由I/O写入,并在WE的上升沿锁存。

通过命令锁存信号CLE和地址锁存信号ALE可使命令和地址实现对I/O口的复用。

除了块擦除周期需要两个总线周期(擦除建立和擦除执行)外,其他命令均可在一个总线周期内完成。

由于64M字节物理为间需要26根地址线,因此,按字节需要4个地址周期,依次为列地址、行地址低位和行地址高位。

页读和页编程在相应命令后需要4个地址周期。

然而,块擦除只需要3个列地址周期。

可以通过向命令寄存器写入相应的命令来选择器件的工作方式,K9K1208UOM的专用命令如表1所列。

表1 K9K 1208UOM的专用命令功能命令功能第个周期第二周期Read 1 00 h 01hRead 2 50 h -Read ID 90 h -h -Reset FFPage Program 80 h 10hBlack 60 h D 0hRead Status 70 h -利用K9K1208UOM的专用命令,可用3年方式设定目标地址指针:“00H”命令可使指针指向主存储区的低位列地址0~255字节区,“01H”命令指向主存储区的高位列地址256~511字节区,“50H”命令则指向备用存储区(512~527字节区)。

4 使用方法4.1 页读器件在上电后的初始状态即为READ1模式,也可与4个地址周期一起向命令寄存器写入“00H”来初始化。

命令锁存后,后续的页读操作不用再写。

读操作有3种类型:随机读、连续页读和顺序页读。

页地址在改变时激活随机读模式,所选择页的528字节数据将在10µs内传送到数据寄存器,系统控制器可根据R/B引脚的状态来判断传送是否结束。

数据传送到数据寄存器后,可由随后的RE信号在60ns内读出。

当最后一列数据读出后,自动选择下一页地址以备顺序读,等待10µs后可再读后续页。

使引脚CE变高可结束顺序读操作。

读命令READ1和READ2就象一个指针,用于选择主存贮区或备用存贮区。

当CE引脚为低时,写入读命令READ2可以访问备用存贮区512~527字节。

在操作过程中,禁止触发SE,可用A0~A3来设置备用区首地址,而A4~A7的状态可以任意。

在READ1操作中,除非操作被取消,否则页地址总是自动增加以备顺序读,而且每一页的备用区16个字节也将随后读出。

用READ1命令可以把指针移加主存贮区。

READ1的操作时序如图2所示。

4.2 页编程器件编程以页为基础,但在一个页编程周期内,也允许对页的部分区域编程,部分区域可以一个字节到多至528个连续字节。

对于同一页内编程的部分区域数,在主存贮区一般不超过两个,备用存贮区不超过3个,且中间不能插入擦除操作。

在一个块内,可按任何随机方式寻址,一个页编程周期由一系列数据装入周期组成,其间可把528字节数据装入页寄存器,在其后跟随的一个非易失写入周期内,可再把装入的数据写入相应的存贮单元内,通过移动指针,还可从高位列地址区启动连续数据装入操作。

输入连续数据装入命令80H,可在其后跟随4个地址周期,以开始连续数据的装入过程,再输入页编程确认命令10H即可开始编程过程。

单独输入10H而没有输入前面的数据则不会启动编程过程。

器件内部写控制器可自动执行编程和校验所需的算法和定时,然后释放系统控制器执行其他任务。

编程过程开始后,在引脚RE和CE为低情况下,可以输入读状态命令以读取状态寄存器,系统控制器可通过监视R/B输出信号或状态寄存器的状态位(I/O6)来检测编程周期是否结束。

在编程过程中,只有读状态命令和复位命令有效。

页编程结束时,可以检查写状态位I/O0,内部写校验只检查那些未能成功地编程为“0”的“1”错误。

直至另一个有效命令写入命令寄存器之前,命令寄存器一直保持读状态命令,编程和读状态操作时序如图3所示。

4.3 块擦除块擦除操作将由一个块擦除法启动命令(60H)开始,并在其后三个周期内输入块地址,地址中只有A14~A25有效,A9~A13不起作用。

块地址装入后,输入擦除确认命令(D0H)即可启动内部擦除过程。

采用两步设定才开始执行命令主要是为了防止存贮器内容被外部噪音意外擦除。

在擦除确认命令输入后的WE上升沿,内部写控制器控制进行擦除和擦除校验,擦除过程结束时检查写状态位(I/O0)。

块擦除与校验过程时序如图4所示。

4.4 其他操作a.读状态芯片内有一个状态寄存器可提供编程或擦除是否完成、编程和擦除是否成功等信息。

把命令70H写入命令寄存器后,状态寄存器内的信息将在CE或RE的下降沿被输出到I/O端口上,状态寄存器的各位定义如表2所列。

表2 状态寄存器定义I/O号状态I/O 0 编程/擦除状态指示,为0时,表示连接编程/擦除,为1表示编程/擦除错误I/O 1 待用I/O 2 待用I/O 3 待用I/O 4 待用I/O 5 待用I/O 6 器件操作状态指示,为0表示忙,为1表示准备好I/O 7 写保持状态,为0表示写保护,为1表示未写保护b.复位将命令FFH写入命令寄存器可使器件复位,在随机读、编程或擦除过程中,复位命令将取消这些操作,正在改变的存贮单元的内容也不再有效,因为它位可能已部分被编程或被擦除。

c.READY/BUSY信号K9K1208UOM中的输出可用于指示页编程、擦除和随机读是否完成,R/B引脚是漏极开路驱动器,使用时可以将多个R/B引脚相连,但需要接一个适当的上拉电阻。

d.数据保护该器件还提供了保护功能,以防止电源过渡过程中发生任何偶然的编程/擦除动作。

当Vcc<2.2V 时,内部电源擦测器将封锁所有功能。

WP引脚可用来提供硬件保护,在上电和关机过程中,建议将其保持为低电平。

而编程和擦除两级命令序列的软件保护则另外提供。

5 结束语K9K1208UOM器件与系统的接口十分简单,操作灵活方便,器件从硬件到软件均有多种保护,数据可靠性高,使用寿命长。

为大容量固态存贮器市场提供了最具成本效益的解决方案,因而在各种大容量非易失存贮器应用领域具有广阔的应用前景。