计算机组成原理习题答案3解析

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

`

第3章习题参考答案

1、设有一个具有20位地址和32位字长的存储器,问 (1) 该存储器能存储多少字节的信息

(2) 如果存储器由512K ×8位SRAM 芯片组成,需要多少片 (3) 需要多少位地址作芯片选择 解:

(1) 该存储器能存储:字节4M 8

32

220=⨯

{

(2) 需要

片88

232

28512322192020=⨯⨯=⨯⨯K (3) 用512K 8位的芯片构成字长为32位的存储器,则需要每4片为一组进行

字长的位数扩展,然后再由2组进行存储器容量的扩展。所以只需一位最高位地址进行芯片选择。

2、已知某64位机主存采用半导体存储器,其地址码为26位,若使用4M ×8位的DRAM 芯片组成该机所允许的最大主存空间,并选用内存条结构形式,问; (1) 若每个内存条为16M ×64位,共需几个内存条? (2) 每个内存条内共有多少DRAM 芯片?

(3) 主存共需多少DRAM 芯片 CPU 如何选择各内存条 解:

(1) 共需

条464

1664

226=⨯⨯M 内存条 (2) 每个内存条内共有

328

464

16=⨯⨯M M 个芯片

(3) 主存共需多少

1288

464

648464226=⨯⨯=⨯⨯M M M 个RAM 芯片, 共有4个内存条,故CPU 选择内存条用最高两位地址A 24和A 25通过2:4译码器实现;其余的24根地

址线用于内存条内部单元的选择。

*

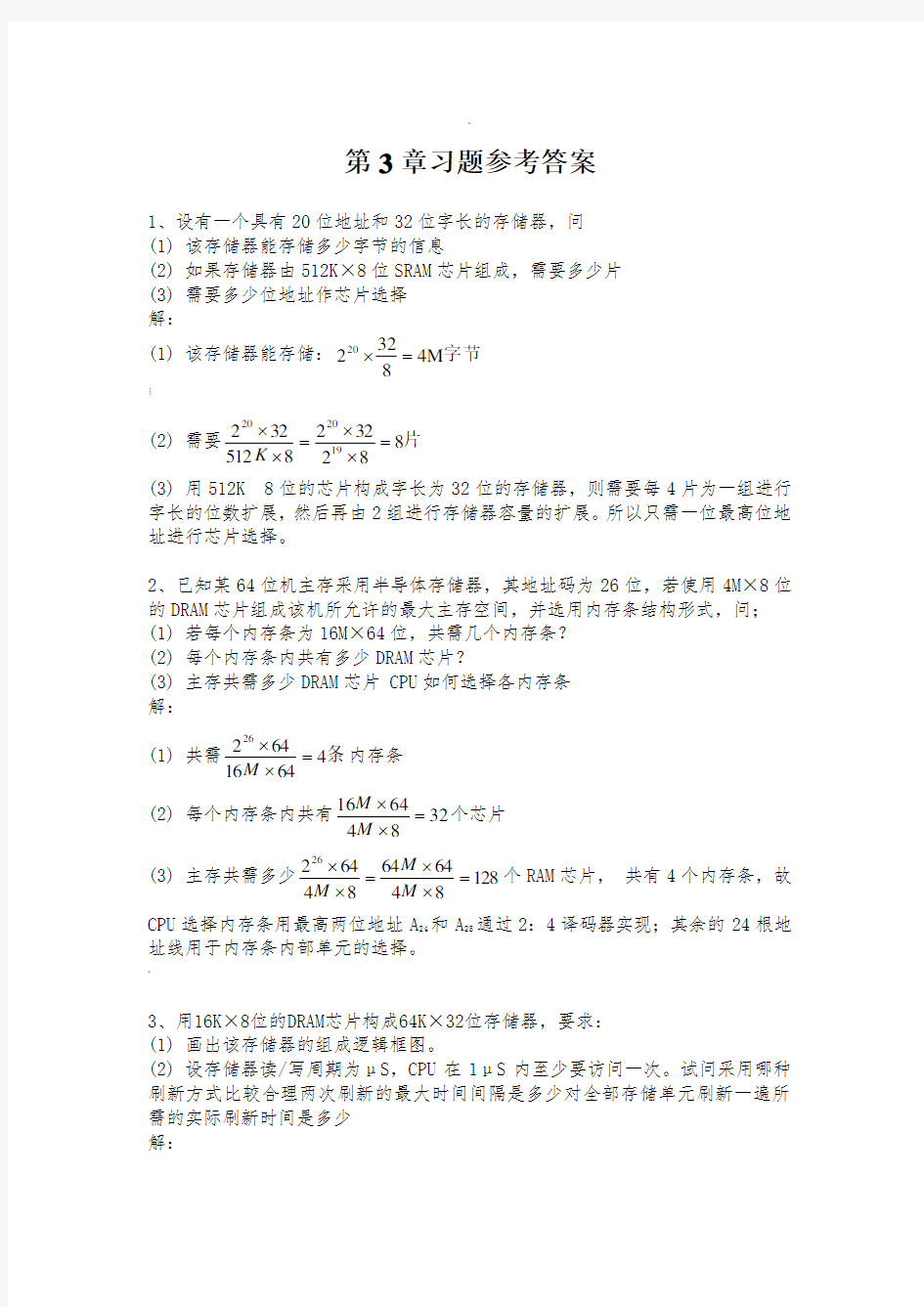

3、用16K ×8位的DRAM 芯片构成64K ×32位存储器,要求: (1) 画出该存储器的组成逻辑框图。

(2) 设存储器读/写周期为μS ,CPU 在1μS 内至少要访问一次。试问采用哪种刷新方式比较合理两次刷新的最大时间间隔是多少对全部存储单元刷新一遍所需的实际刷新时间是多少 解:

(1) 用16K ×8位的DRAM 芯片构成64K ×32位存储器,需要用

16

448

1632

64=⨯=⨯⨯K K 个芯片,其中每4片为一组构成16K ×32位——进行字长位数扩展(一组内的4个芯片只有数据信号线不互连——分别接D 0D 7、D 8D 15、D 16D 23和D 24D 31,其余同名引脚互连),需要低14位地址(A 0A 13)作为模块内各个芯片的内部单元地址——分成行、列地址两次由A 0A 6引脚输入;然后再由4组进行存储器容量扩展,用高两位地址A 14、A 15通过2:4译码器实现4组中选择一组。画出逻辑框图如下。

(1) (2) (3) (4)

(5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) CPU

D 0~D 31

RAS 0

RAS 1

RAS 2

RAS 3

A 0~A 13

A 14 A 15

A 0~A 6

A 0~A 6 A 0~A 6 A 0~A 6 WE WE

2-4 译码

RAS

D 0~7 D 8~15 D 16~23 D 24~31

D 0~7 D 8~15 D 16~23 D 24~31

D 0~7 D 8~15 D 16~23 D 24~31

D 0~7 D 8~15 D 16~23 D 24~31

WE

WE

WE

RAS

RAS

RAS

%

(2) 设刷新周期为2ms ,并设16K 8位的DRAM 结构是1281288存储阵列,则对所有单元全部刷新一遍需要128次(每次刷新一行,共128行)

若采用集中式刷新,则每2ms 中的最后128s=64s 为集中刷新时间,不能进行正常读写,即存在64s 的死时间

若采用分散式刷新,则每1s 只能访问一次主存,而题目要求CPU 在1μS 内至少要访问一次,也就是说访问主存的时间间隔越短越好,故此方法也不是最适合的

比较适合采用异步式刷新:

采用异步刷新方式,则两次刷新操作的最大时间间隔为s ms

μ625.15128

2=,可取

s ;对全部存储单元刷新一遍所需的实际刷新时间为:s 128=;采用这种方式,每s 中有s 用于刷新,其余的时间用于访存(大部分时间中1s 可以访问两次内存)。

4、有一个1024K ×32位的存储器,由128K ×8位的DRAM 芯片构成。问: (1) 总共需要多少DRAM 芯片 …

(2) 设计此存储体组成框图。

(3) 采用异步刷新方式,如单元刷新间隔不超过8ms ,则刷新信号周期是多少 解:

(1) 需要32488

12832

1024=⨯=⨯⨯K K 片,每4片为一组,共需8组

(2) 设计此存储体组成框图如下所示。

(1) (2) (3) (4)

(5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) CPU

D 0~D 31

RAS 0 A 0~A 16

A 17 A 18 A 0~A 8

WE WE

3-8 译码

RAS

D 0~7 D 8~15 D 16~23 D 24~31

D 0~7 D 8~15 D 16~23 D 24~31

D 0~7 D 8~15 D 16~23 D 24~31

D 0~7 D 8~15 D 16~23 D 24~31

WE

WE

WE

(17)

(18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) CPU

A 0~A 16

WE

D 0~7 D 8~15 D 16~23 D 24~31

D 0~7 D 8~15 D 16~23 D 24~31

D 0~7 D 8~15 D 16~23 D 24~31

D 0~7 D 8~15 D 16~23 D 24~31

A 19

RAS 0

RAS 1

RAS 2

RAS 3

RAS 4

RAS 5

RAS 6

RAS 7

RAS 1 RAS 2 RAS 3 RAS 4 RAS 5 RAS 6 RAS 7

WE

(3) 设该128K 8位的DRAM 芯片的存储阵列为5122568结构,则如果选择一个行地址进行刷新,刷新地址为A 0A 8,那么该行上的2048个存储元同时进行刷新,要求单元刷新间隔不超过8ms ,即要在8ms 内进行512次刷新操作。采

用异步刷新方式时需要每隔s ms

μ625.15512

8=进行一次,可取刷新信号周期为s 。

#

5、要求用256K×l6位SRAM 芯片设计1024K×32位的存储器。SRAM 芯片有两个控制端:当CS 有效时,该片选中。当W/R =1时执行读操作,当W/R=0时执行写操作。

解:

片82416

25632

1024=⨯=⨯⨯K K ,共需8片,分为4组,每组2片

即所设计的存储器单元数为1M ,字长为32,故地址长度为20位(A 19~A 0),所用