EDA技术与应用作业版

EDA 技术实用教程 课后作业答案

作业3-6module Mux3_1(a1,a2,a3,s0,s1,outy); input a1,a2,a3,s0,s1;output outy;reg outy;reg temp;always @(a2,a3,s0)beginif(s0 == 1'b0)temp = a2;elsetemp = a3;endalways @(a1, temp,s1)beginif(s1 == 1'b0)outy = a1;elseouty = temp;endendmodule作业3-7 半减器module H_suber(x,y,diff,s_out);input x,y;output diff,s_out;reg s_out;wire diff;assign diff = x ^ y;always @(x,y)beginif(x < y)s_out = 1'b1;elses_out = 1'b0;endendmodule全减器module F_suber(x,y,sub_in,diffr,sub_out); input x,y,sub_in;output diffr,sub_out;wire diffr,sub_out;wire H_diff,H_sout,s_out;assign sub_out = s_out || H_sout;H_suber U1 (.x(x),.y(y),.diff(H_diff),.s_out(H_sout));H_suber U2 (.x(H_diff),.y(sub_in),.diff(diffr),.s_out(s_out));Endmodule8位全减器module Bit8_suber(X,Y,Sub_in,Diff,Sub_out);input[7:0] X,Y;input Sub_in;output[7:0] Diff;output Sub_out;wire[7:0] Diff;wire Sub_out;wire[6:0] sub_out;F_suber U1(.x(X[0]),.y(Y[0]),.sub_in(Sub_in),.diffr(Diff[0]),.sub_out(sub_out[0]));F_suber U2(.x(X[1]),.y(Y[1]),.sub_in(sub_out[0]),.diffr(Diff[1]),.sub_out(sub_out[1])); F_suber U3(.x(X[2]),.y(Y[2]),.sub_in(sub_out[1]),.diffr(Diff[2]),.sub_out(sub_out[2])); F_suber U4(.x(X[3]),.y(Y[3]),.sub_in(sub_out[2]),.diffr(Diff[3]),.sub_out(sub_out[3])); F_suber U5(.x(X[4]),.y(Y[4]),.sub_in(sub_out[3]),.diffr(Diff[4]),.sub_out(sub_out[4])); F_suber U6(.x(X[5]),.y(Y[5]),.sub_in(sub_out[4]),.diffr(Diff[5]),.sub_out(sub_out[5])); F_suber U7(.x(X[6]),.y(Y[6]),.sub_in(sub_out[5]),.diffr(Diff[6]),.sub_out(sub_out[6])); F_suber U8(.x(X[7]),.y(Y[7]),.sub_in(sub_out[6]),.diffr(Diff[7]),.sub_out(Sub_out)); Endmodule作业3-13Amodule DFF_A(D,EN,CLK,RST,Q,Q1);input D,EN,CLK,RST;output Q,Q1;reg Q;wire Q1;wire D_temp;assign D_temp = D && EN;assign Q1 = (~D_temp)||RST;always @(negedge RST or posedge CLK)beginif(!RST)Q <= 1'b0;elseif(EN)Q <= D;elseQ <= Q;endmoduleBmodule DFF_B (A,B,C,D,Y);input A,B,C,D;output Y;reg Y;wire temp1,temp2,temp3;assign temp1 = A || B;assign temp2 = C && D;assign temp3 = temp1 ^ temp2; always @(A,temp1,temp3)beginif(temp1)Y = temp3;elseY = A;endendmoduleCmodule DFF_C(RST,D,CLK,Q,DOUT); input RST,D,CLK;output Q,DOUT;reg Q,DOUT;reg D_temp1;wire D_temp2;assign D_temp2 = D ^ D_temp1; always @(RST,D)beginif(RST)D_temp1 = 1'b0;elseD_temp1 = D;endalways @(posedge CLK)beginQ <= D_temp1;DOUT <= D_temp2;endmoduleDmodule DFF_D(SET,D,CLK,EN,RESET,Q);input SET,D,CLK,EN,RESET;output Q;reg Q;wire SET_temp;assign SET_temp = (~RESET) && SET;always @(posedge CLK or posedge RESET or posedge SET_temp) beginif(RESET)Q <= 1'b0;elseif(SET_temp)Q <= 1'b1;elseif(EN)Q <= D;elseQ <= Q;endendmodule8-2.用Mealy机类型,写出控制ADC0809采样的状态机。

eda技术及应用考试及答案

eda技术及应用考试及答案一、单选题(每题2分,共20分)1. EDA技术的核心是()。

A. 电子设计自动化B. 电子制造自动化C. 电子测试自动化D. 电子组装自动化答案:A2. 在EDA技术中,HDL指的是()。

A. 高级设计语言B. 硬件描述语言C. 硬件描述逻辑D. 高级描述语言答案:B3. 以下哪个不是EDA软件的主要功能()。

A. 逻辑综合B. 电路仿真C. 布线D. 机械加工答案:D4. 在EDA技术中,FPGA指的是()。

A. 现场可编程门阵列B. 固定可编程门阵列C. 现场可配置逻辑阵列D. 固定可配置逻辑阵列答案:A5. 以下哪个不是EDA技术中常用的仿真工具()。

A. ModelSimB. QuartusC. MATLABD. ISE答案:C6. 在EDA技术中,ASIC指的是()。

A. 应用特定集成电路B. 应用通用集成电路C. 应用特定逻辑阵列D. 应用通用逻辑阵列答案:A7. 在EDA技术中,以下哪个不是硬件描述语言()。

A. VHDLB. VerilogC. C语言D. SystemVerilog答案:C8. 在EDA技术中,以下哪个不是逻辑综合的主要任务()。

A. 优化逻辑B. 布局C. 布线D. 时序分析答案:C9. 在EDA技术中,以下哪个不是FPGA的主要优点()。

A. 可重构性B. 可编程性C. 低成本D. 高性能答案:C10. 在EDA技术中,以下哪个不是ASIC的主要优点()。

A. 高性能B. 低成本C. 低功耗D. 高可靠性答案:B二、多选题(每题3分,共15分)11. EDA技术的主要应用领域包括()。

A. 通信B. 计算机C. 消费电子D. 军事答案:ABCD12. 在EDA技术中,以下哪些是硬件描述语言的特点()。

A. 层次性B. 并行性C. 抽象性D. 可读性答案:ABC13. 在EDA技术中,以下哪些是FPGA的主要缺点()。

A. 成本高B. 速度慢C. 功耗大D. 灵活性差答案:ABC14. 在EDA技术中,以下哪些是ASIC的主要缺点()。

eda作业

eda一、如图1所示,电路为二级电压串联负反馈的放大电路,其中Vs为V AC/SOURCE,其属性设置为默许值。

三极管Q2N3904的模型参数为默许值。

试用EWB软件作如下的分析:(1)求直流工作点;(2)求无负反馈(即无电阻Rf)时的输入电阻、输出电阻、电压增益和上限截止频率;(3)当电阻Rf别离为6.2kΩ、15kΩ和30kΩ时的反馈深度,并总结反馈深度对放大电路性能的阻碍。

(25分)Re1300Rb420kRs 200Rf6.2kVcc12VdcCe210uCe110uR55kQ2Q2N3904Cb22.2uRb3300kVoutQ1Q2N3904Vs1Vac 0VdcCb12.2uVinRe2680Rb1300kCb32.2u Re3820Rc15.1kR2b20kRc25.1kIb=1.11uA, Ic=126.121uA, Uce=11.242;图二Ui=986.856mV, Ii=77.076uA, Uo=3.118V; Ri=Ui/Ii=986.856mV/77.076uA=12.8K。

Uo1=5.193V;Ro=(Uo1/Uo-1)*R5=3.4KA=Uo/Ui=3.118V/986.856mV=3.15;Af=2.462V/987.371mV=2.5Af=2.803V/987.371mV=2.8Af=2.947V/986.945mV=3反馈深度1+AF=A/Af;由上可得:Af减小二级电压串联负反馈:Ri=Ri/(1+Af);Ro=Ro*(1+Af);使的Ri减小Ro增大;二、设计题。

设计一个水温操纵系统。

(40分)大体要求:一升水由1kW的电炉加热,要求水温能够在必然范围内由人工设定,并能在环境温度降低时实现自动调整,以维持设定的温度大体不变。

达到的性能指标:①温度设定范围:40~90℃,最小区分度为1℃;②操纵精度:温度操纵的静态误差≤1℃;③用十进制数码显示实际水温;④能打印实测水温值;⑤具有通信能力,可接收其他数据设备发来的命令,或将结果传送到其他数据设备。

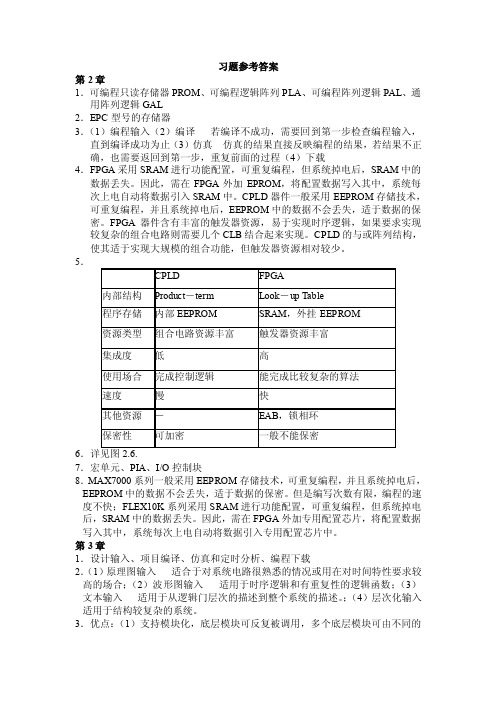

EDA技术及应用习题参考答案

习题参考答案第2章1.可编程只读存储器PROM、可编程逻辑阵列PLA、可编程阵列逻辑PAL、通用阵列逻辑GAL2.EPC型号的存储器3.(1)编程输入(2)编译若编译不成功,需要回到第一步检查编程输入,直到编译成功为止(3)仿真仿真的结果直接反映编程的结果,若结果不正确,也需要返回到第一步,重复前面的过程(4)下载4.FPGA采用SRAM进行功能配置,可重复编程,但系统掉电后,SRAM中的数据丢失。

因此,需在FPGA外加EPROM,将配置数据写入其中,系统每次上电自动将数据引入SRAM中。

CPLD器件一般采用EEPROM存储技术,可重复编程,并且系统掉电后,EEPROM中的数据不会丢失,适于数据的保密。

FPGA器件含有丰富的触发器资源,易于实现时序逻辑,如果要求实现较复杂的组合电路则需要几个CLB结合起来实现。

CPLD的与或阵列结构,使其适于实现大规模的组合功能,但触发器资源相对较少。

5.67.宏单元、PIA、I/O控制块8.MAX7000系列一般采用EEPROM存储技术,可重复编程,并且系统掉电后,EEPROM中的数据不会丢失,适于数据的保密。

但是编写次数有限,编程的速度不快;FLEX10K系列采用SRAM进行功能配置,可重复编程,但系统掉电后,SRAM中的数据丢失。

因此,需在FPGA外加专用配置芯片,将配置数据写入其中,系统每次上电自动将数据引入专用配置芯片中。

第3章1.设计输入、项目编译、仿真和定时分析、编程下载2.(1)原理图输入适合于对系统电路很熟悉的情况或用在对时间特性要求较高的场合;(2)波形图输入适用于时序逻辑和有重复性的逻辑函数;(3)文本输入适用于从逻辑门层次的描述到整个系统的描述。

;(4)层次化输入适用于结构较复杂的系统。

3.优点:(1)支持模块化,底层模块可反复被调用,多个底层模块可由不同的设计者同时使用,提高了设计效率;(2)设计方法比较自由;(3)团队之间的合作方便灵活。

EDA技术与应用课后习题答案(6)

EDA技术与应⽤课后习题答案(6)EDA技术与应⽤课后习题答案 CLK: IN STD_LOGIC; --状态机⼯作时钟 EOC: IN STD_LOGIC; --转换状态指⽰,低电平表⽰正在转换 ALE:OUT STD_LOGIC; --8个模拟信号通道地址锁存信号 START:OUT STD_LOGIC; --转换开始信号 OE:OUT STD_LOGIC; --数据输出三态控制信号 ADDA:OUT STD_LOGIC; --信号通道最低位控制信号 LOCK0:OUT STD_LOGIC; --观察数据锁存时钟 Q:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); --8位数据输出 END ADCINT; ARCHITECTURE behav OF ADCINT IS TYPE states IS(st0,st1,St2,st3,st4); --定义各状态⼦类型 SIGNAL current_state,next_state: states:=st0; SIGNAL REGL: STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL LOCK: STD_LOGIC;--转换后数据输出锁存时钟信号 BEGIN ADDA<='1';--当ADDA<='0',模拟信号进⼊通道IN0;当ADDA<='1',则进⼊通道INI Q<=REGL;LOCK0<=LOCK; COM: PROCESS(current_state,EOC) BEGIN --规定各状态转换⽅式 CASE current_state IS WHEN st0=> ALE<='0';START<='0';LOCK<='0';OE<='0'; next_state<=st1; --0809初始化 WHEN st1=> ALE<='1';START<='1';LOCK<='0';OE<='0'; next_state<=st2 ;--启动采样 WHEN st2=> ALE<='0';START<='0';LOCK<='0'; OE<='0'; IF(EOC='1') THEN next_state<=st3;--EOC=1表明转换结束 ELSE next_state<=st2; END IF; --转换未结束,继续等待 WHEN st3=> ALE<='0';START<='0';LOCK<='0';OE<='1'; next_state<=st4;--开启OE,输出转换好的数据 WHEN st4=> ALE<='0';START<='0';LOCK<='1';OE<='1';next_state<=st0; WHEN OTHERS=>next_state<=st0; END CASE; END PROCESS COM; REG:PROCESS(CLK) BEGIN IF(CLK'EVENT AND CLK='1') THEN current_state<=next_state; END IF; END PROCESS REG; --由信号current_state将当前状态值带出此进程:REG LATCH1: PROCESS(LOCK) --此进程中,在LOCK的上升沿,将转换好的数据锁⼊ BEGIN IF LOCK='1' AND LOCK'EVENT THEN REGL<=D; END IF; END PROCESS LATCH1; END behav; 8-5在不改变原代码功能的条件下⽤两种⽅法改写例8-2,使其输出的控制信号(ALE、START、OE、LOCK)没有⽑刺。

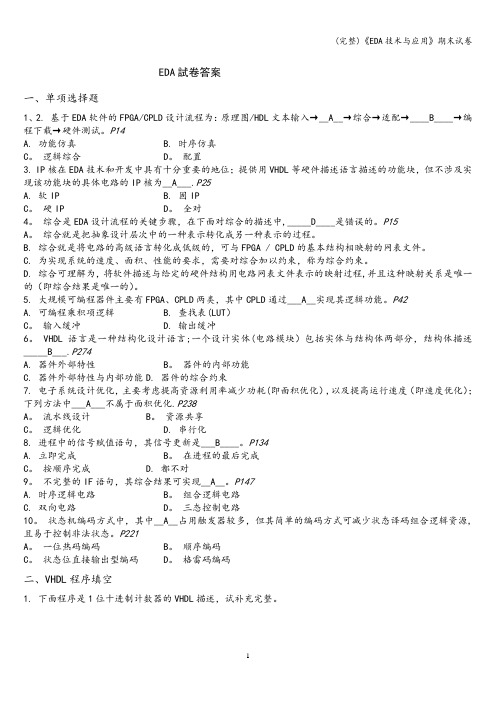

(完整)《EDA技术与应用》期末试卷

EDA試卷答案一、单项选择题1、2. 基于EDA软件的FPGA/CPLD设计流程为:原理图/HDL文本输入→__A__→综合→适配→____B____→编程下载→硬件测试。

P14A. 功能仿真B. 时序仿真C。

逻辑综合D。

配置3. IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为__A___.P25A. 软IPB. 固IPC。

硬IP D。

全对4。

综合是EDA设计流程的关键步骤,在下面对综合的描述中,_____D____是错误的。

P15A。

综合就是把抽象设计层次中的一种表示转化成另一种表示的过程。

B. 综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件。

C. 为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束。

D. 综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的(即综合结果是唯一的)。

5. 大规模可编程器件主要有FPGA、CPLD两类,其中CPLD通过___A__实现其逻辑功能。

P42A. 可编程乘积项逻辑B. 查找表(LUT)C。

输入缓冲 D. 输出缓冲6。

VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述_____B___.P274A. 器件外部特性B。

器件的内部功能C. 器件外部特性与内部功能D. 器件的综合约束7. 电子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);下列方法中___A___不属于面积优化.P238A。

流水线设计B。

资源共享C。

逻辑优化 D. 串行化8. 进程中的信号赋值语句,其信号更新是___B____。

P134A. 立即完成B。

在进程的最后完成C。

按顺序完成 D. 都不对9。

不完整的IF语句,其综合结果可实现__A__。

EDA技术与应用智慧树知到课后章节答案2023年下山东科技大学

EDA技术与应用智慧树知到课后章节答案2023年下山东科技大学山东科技大学第一章测试1.硬件描述语言主要有哪些?()答案:SystemVerilog;Verilog;AHDL;VHDL第二章测试1.下列不属于Verilog HDL算数运算符的是()答案:=2.在verilog语言中,a=4b'1011,那么&a=()答案:null3.5’b10011>>2等于()答案:5’b001004.{4{a}}等于()答案:{a,a,a,a}5.下列关于阻塞赋值运算(如b=a;)说法错误的是()答案:在“always”模块中的reg型信号都采用此赋值方式第三章测试1.假设design为TOP.v,顶层模块名为TOP;TestBench为TOP_TB.v,顶层模块名为TOP_TB,则完整写出Modelsim仿真该设计所用命令为vlibmywork()答案:错2.常见的数字仿真器有()答案:Modelsim;Iverilog;IUS;VCS3.Modelsim中,为禁用其优化,可以在命令行上添加-novopt选项。

()答案:对4.vsim仿真时,是从物理库开始查找模块。

()答案:错5.目前modelsim可以在包含中文的路径中正常执行。

()答案:错第四章测试1.EPF10K20TC144-4具有()个管脚答案:1442.FPGA结构一般分为三部分:可编程逻辑块(CLB)、可编程I/O模块和可编程内部连线。

()答案:对3.FPGA基于SRAM结构,每次上电后需要一次配置。

()答案:对4.大规模可编程器件主要有FPGA、CPLD两类,其中CPLD通过()实现其逻辑功能。

答案:查找表(LUT)5.CPLD的可编程是主要基于什么结构()。

答案:与或阵列可编程第五章测试1.IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为()答案:软IP2.综合是EDA设计流程的关键步骤,在下面对综合的描述中,()是错误的。

EDA技术课程大作业

2。

篇幅在3000-4000字

3.系统中要求有硬件框图、软件框图、EDA片内框图

题目A:2005年全国大学生电子设计竞赛试题A题。

要求产生的信号源用DDS方式使用FPGA芯片来产生。

题目B:基于FPGA的步进电机细分控制器的设计

要求使用FPGA芯片来产生步进电机细分控制器所需要的PWM信号;步进电机(6相,每相的电流为4A,工作电压为50V)的驱动电路;总的系统硬件图。

题目C:视频信号采集系统的设计

1.视频信号的规格为VCD像素数为352X288 ( PAL 制

式)

2.视频信号的采样精度为8bit,采样深度50帧。

题目D:高速公路车辆超速监测系统的设计

1.汽车的速度上限为120/小时。

2.采用FPGA芯片作为主控器件来测速。

简易无线供电系统

数字式电参数测量仪。

《EDA技术与应用》A卷及答案

《EDA技术与应用》A卷及答案汕头大学成人教育学院二0一0年春季学期期末考试试卷试卷编号:A卷闭卷课程名称:《EDA技术与应用》班级专业:姓名:学号:一、填空题(20分,每小题1分)1.VHDL的中文名称是__超高速集成电路硬件描述语言_____________。

2.用EDA技术进行电子系统设计的目标是最终完成asic________ 的设计与实现。

3.可编程器件分为 fpga__ 和 _cpld______ 。

4.标准逻辑位数据类型常用的数值有 _1__ 、 __0_ 、 _z__ 等。

5.在VHDL语言中可以使用的数据类型有:_位____ 、__标准逻辑位__________、___布尔_____。

6.完整的条件语句将产生_组合_______ 电路,不完整的条件语句将产生 __时序______电路。

7.信号的赋值符号为 <= ___ 变量的赋值符号为 =___ 。

8.随着EDA技术的不断完善与成熟, ___自顶向下______的设计方法更多的被应用于VHDL设计当中。

9.EDA设计过程中的仿真有三种,它们是___行为_____ 仿真、 _逻辑______ 仿真和 __时序____ 仿真。

10.目前国际上较大的PLD器件制造公司有__altera________ 和___xilinx______ 公司。

二、简答题(20分,每小题4分)1、与HDL文本输入法相比较,原理图输入法有何优点?2、写出结构体的一般语言格式并说明其作用3、信号和变量的区别?4、写出PROCESS语句结构的一般表达格式。

5、写出五种以上的VHDL的预定义数据类型。

三、程序注解(20分,每空1分)library ieee; __________ use ieee.std_logic_1164.all; _____________ ENTITY aa1 is ________ __ port(a,b,s:in bit; _______________________________end aa1; ___________________________ architecture one of aa1 is _________ y<=a when s='0' else b; ____________________ end one; _____ ________________________________ 逻辑功能:____________________________signal s1 : bit ; _________________________ begin ________________________________ process (clk,d) _______________________ beginif (clk = ‘1’) _____________________________ then ______________________________________ s1 <= d; ________________________________ end if; _________________________________ q <= s1 ; _____________________________ end process; ___________________________ end bo; __________________________ 逻辑功能: __________________四、VHDL语言编程题(1、2小题10分,3小题20分)1、编写一个D触发器的硬件描述语言程序,要求实现上升沿触发。

EDA技术与应用课后习题答案(2)

EDA技术与应用课后习题答案(2)END IF;END PROCESS;PR02:PROCESS(s1)BEGINIF s1=”0” THEN outy<=a1;ELSE outy<=tmp;END IF;END PROCESS;END ARCHITECTURE ONE;END CASE;4-4.下图是一个含有上升沿触发的D触发器的时序电路,试写出此电路的VHDL设计文件。

4-4.答案LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MULTI ISPORT(CL:IN STD_LOGIC; --输入选择信号CLK0:IN STD_LOGIC; --输入信号OUT1:OUT STD_LOGIC);--输出端END ENTITY;ARCHITECTURE ONE OF MULTI ISSIGNAL Q : STD_LOGIC;BEGINPR01: PROCESS(CLK0)BEGINIF CLK ‘EVENT AND CLK=’1’THEN Q<=NOT(CL OR Q);ELSEEND IF;END PROCESS;PR02: PROCESS(CLK0)BEGINOUT1<=Q;END PROCESS;END ARCHITECTURE ONE;END PROCESS;4-5.给出1位全减器的VHDL描述。

要求:(1) 首先设计1位半减器,然后用例化语句将它们连接起来,图3-32中h_suber是半减器,diff是输出差,s_out是借位输出,sub_in 是借位输入。

(2) 以1位全减器为基本硬件,构成串行借位的8位减法器,要求用例化语句来完成此项设计(减法运算是 x – y - sun_in = diffr) 4-5.答案底层文件1:or2a.VHD实现或门操作LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY or2a ISPORT(a,b:IN STD_LOGIC;c:OUT STD_LOGIC);END ENTITY or2a;ARCHITECTURE one OF or2a ISBEGINc <= a OR b;END ARCHITECTURE one;底层文件2:h_subber.VHD实现一位半减器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY h_subber ISPORT(x,y:IN STD_LOGIC;diff,s_out::OUT STD_LOGIC);END ENTITY h_subber;ARCHITECTURE ONE OF h_subber ISSIGNAL xyz: STD_LOGIC_VECTOR(1 DOWNTO 0); BEGINxyz <= x & y;PROCESS(xyz)BEGINCASE xyz ISWHEN "00" => diff<='0';s_out<='0';WHEN "01" => diff<='1';s_out<='1';WHEN "10" => diff<='1';s_out<='0';WHEN "11" => diff<='0';s_out<='0';WHEN OTHERS => NULL;END CASE;END PROCESS;END ARCHITECTURE ONE;顶层文件:f_subber.VHD实现一位全减器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY f_subber ISPORT(x,y,sub_in:IN STD_LOGIC;diffr,sub_out:OUT STD_LOGIC);END ENTITY f_subber;ARCHITECTURE ONE OF f_subber IS COMPONENT h_subberPORT(x,y:IN STD_LOGIC;diff,S_out:OUT STD_LOGIC);END COMPONENT;COMPONENT or2aPORT(a,b:IN STD_LOGIC;c:OUT STD_LOGIC);END COMPONENT;SIGNAL d,e,f: STD_LOGIC;BEGINu1: h_subber PORT MAP(x=>x,y=>y,diff=>d,s_out=>e);u2: h_subber PORT MAP(x=>d,y=>sub_in,diff=>diffr,s_out=>f);u3: or2a PORT MAP(a=>f,b=>e,c=>sub_out);END ARCHITECTURE ONE;END ARCHITECTURE ART;4-6.根据下图,写出顶层文件MX3256.VHD的VHDL设计文件。

eda技术应用实训报告

eda技术应用实训报告《eda技术应用实训报告》那天,阳光透过窗户洒在实验室的桌子上,我和我的小伙伴们就像一群即将踏上神秘冒险之旅的探险家,站在eda技术应用实训的大门前。

“嘿,你说这eda技术到底像啥呀?”小明挠着头,眼睛里满是疑惑。

我嘿嘿一笑,说道:“我觉得呀,这eda技术就像是一个超级魔法盒,能把我们那些天马行空的想法变成实实在在的电路设计呢。

”一开始,面对那些密密麻麻的线路图和各种各样的工具软件,我们就像迷失在森林里的小鹿,有些不知所措。

但是,我们知道,既然选择了这个冒险,就不能轻易退缩。

我坐在电脑前,眼睛紧紧盯着屏幕,手指在鼠标和键盘上小心翼翼地操作着。

每一次点击,每一次输入命令,都像是在和这个神秘的eda世界对话。

我心里不停地念叨着:“可别出岔子啊,小宝贝。

”这时候,老师就像一位经验丰富的老船长,在我们这片迷茫的海域里为我们指引方向。

“你们看,这里的模块就像是一个个小零件,要把它们巧妙地组合起来,就像搭积木一样。

”老师的话让我们豁然开朗。

我旁边的小红是个急性子,她在操作的时候出了点小差错,线路图变得一团糟。

她着急得脸都红了,就像一个熟透的苹果。

“哎呀,这可怎么办呀?”她嘟着嘴,眼睛里都快泛起泪花了。

我拍拍她的肩膀,安慰道:“别怕,小红。

这就像是不小心弄乱了的拼图,我们一块一块重新拼好就行啦。

”于是,我们一起仔细检查每一个连接点,每一个参数设置。

这个过程就像是在给受伤的小机器人做修复手术,必须要精准细致。

在实训的过程中,我们也有很多有趣的发现。

当我们成功地让一个简单的电路实现预期功能的时候,那种感觉就像是自己亲手创造了一个小世界。

灯光闪烁的那一刻,我们激动得欢呼起来,仿佛我们是发现了新大陆的哥伦布。

随着实训的深入,我们开始挑战更复杂的项目。

那些复杂的逻辑关系就像是一个个难解的谜题,在考验着我们的智慧。

有时候,我们为了一个小小的错误,要在几百行的代码里反复查找,就像大海捞针一样。

但是,每一次找到错误并且修正它的时候,我们都有一种成就感油然而生。

福建师范大学2021年8月《EDA技术》作业考核试题及答案参考2

福建师范大学2021年8月《EDA技术》作业考核试题及答案(参考)1. Excel工作簿只能有1至255个工作表。

( )此题为判断题(对,错)。

参考答案:正确2. 在多文件结构的程序中,通常把含有 main( )函数的文件称为( )。

A. 主文件B. 实现文件C. 程序文件D. 头文件参考答案:A3. 以下外设中,既可作为输入设备又可作为输出设备的是( )A.绘图仪B.键盘C.磁盘驱动器D.激光打印机参考答案:C4. 电容器可分为固定电容、可变电容和电解电容。

其中电解电容有正负极之分。

( )电容器可分为固定电容、可变电容和电解电容。

其中电解电容有正负极之分。

( )正确5. 正弦相量与复数有否区别?正弦相量与复数有否区别?正弦相量是时间t的函数;复数是一个数,不是时间t的函数;复数与正弦相量是两个完全不同的数学概念。

为表示正弦相量与复数的区别,在正弦相量上加“·”,以示与复数和有效值的区别。

正弦相量虽然是时间t的函数,但仅表示了正弦量三要素中的二个要素,未表达出其角频率要素。

用相量或复数表示正弦量,仅是表示而已。

主要是借助其运算方法,便于解决正弦量之间的加减乘除问题。

6. 信息资源备份应按下列项目进行:( )。

A.全盘备份B.增量备份C.关键项目备份D.后备媒体信息资源备份应按下列项目进行:( )。

A.全盘备份B.增量备份答案:ABCD7. 下列8位二进制数的补码,最大的是( )A.10001000B.11111111C.00000000D.00000001 下列8位二进制数的补码,最大的是( )A.10001000B.11111111C.00000000D.00000001正确答案:D8. CAE是Computer Aided Engineering,计算机辅助工程的缩写。

( )A.正确B.错误参考答案:A9. 数据链路层的数据传输单元( )A、数据帧B、比特流C、分组D、报文参考答案A10. SPLD器件分为几类( )。

EDA作业题及解答

v(1)、对其进行灵敏度分析(2)、→查找拓扑的得概念:拓扑就是一种结构,过去,拓扑被认为是一种空间数据结构,主要用于保证相互关联的数据能够形成一种一致简洁的结构。

由于面向对象的GIS的发展,人们对拓扑有了新的认识。

地理数据库支持对综合不同要素类型的地理问题进行建模,也支持不同类型的主要关系。

在这种情况下,拓扑就是一个规则和关系的集合,再加上一系列的编辑工具和技术,就能够支持地理数据库更为精确地模拟世界上发现的几何关系。

从要素行为角度考虑理解的拓扑,比从数据结构角度理解的拓扑,能支持更为灵活的几何关系。

它甚至可以支持要素数据集中更多离散类型的要素之间存在拓扑关系。

从这种角度看,拓扑可能仍被用于确保数据形成一个简洁、一致的拓扑结构;此外,它更广泛地是用于确保要素能服从用来定义要素在数据库的作用的关键几何规则。

→在数字电路中冒险和竞争的性质和概念:在组合电路中都是按理想情况进行讨论的,实际上,信号通过门电路甚至是导线,都会产生时延。

其结果是在输出端可能出现不正确的干扰信号,是电路产生错误的输出,这种现象称为“竞争冒险”或“过度噪声”竞争: 在组合逻辑电路中,某个输入变量通过两条或两条以上的途径传到输出端,由于每条途径延迟时间不同,到达输出门的时间就有先有后,这种现象称为竞争。

把不会产生错误输出的竞争的现象称为非临界竞争。

把产生暂时性的或永久性错误输出的竞争现象称为临界竞争。

冒险:是指数字电路中某个瞬间出现了非预期信号的现象。

“1”冒险是由一个变量的原变量和反变量同时加到与门输入端造成的。

“0”冒险是由一个变量的原变量和反变量同时加到一个或门输入端造成的。

在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。

产生毛刺叫冒险。

如果布尔式中有相反的信号则可能产生竞争和冒险现象。

解决方法:一是添加布尔式的消去项,二是在芯片外部加电容。

EDA技术与应用作业版

EDA技术与应用作业1.5 什么叫“综合”?一般综合包含哪些过程?答:将多个模块化设计文件合并为一个网表文件,并使层次设计平面化(即展平);对VHDL或Verilog HDL进行分析处理,并将其转换成电路结构或模块,对实际现实目标器件的结构进行优化,并使之满足各种条件约束,优化关键路径。

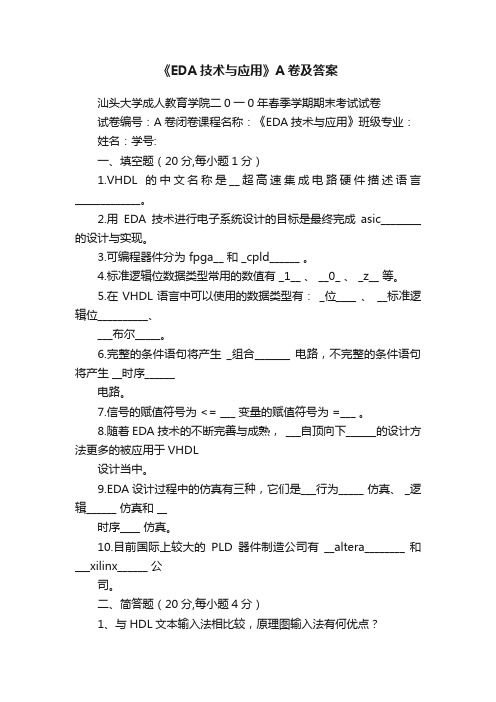

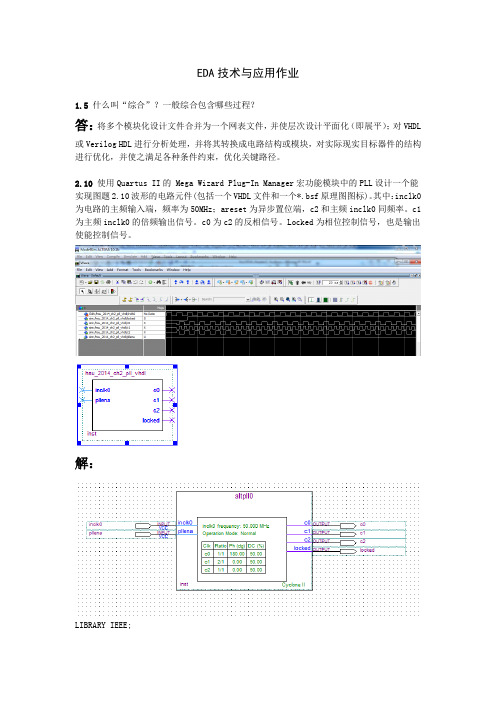

2.10使用Quartus II的 Mega Wizard Plug-In Manager宏功能模块中的PLL设计一个能实现图题2.10波形的电路元件(包括一个VHDL文件和一个*.bsf原理图图标)。

其中:inclk0为电路的主频输入端,频率为50MHz;areset为异步置位端,c2和主频inclk0同频率。

c1为主频inclk0的倍频输出信号。

c0为c2的反相信号。

Locked为相位控制信号,也是输出使能控制信号。

解:LIBRARY IEEE;USE ieee.std_logic_1164.all;LIBRARY altera_mf;USE altera_mf.all;ENTITY whyy ISPORT(inclk0:IN STD_LOGIC := '0';pllena:IN STD_LOGIC := '1';c0:OUT STD_LOGIC ;c1:OUT STD_LOGIC ;c2:OUT STD_LOGIC ;locked:OUT STD_LOGIC);END whyy;ARCHITECTURE SYN OF whyy ISSIGNAL sub_wire0 : STD_LOGIC_VECTOR (5 DOWNTO 0);SIGNAL sub_wire1 : STD_LOGIC ;SIGNAL sub_wire2 : STD_LOGIC ;SIGNAL sub_wire3 : STD_LOGIC ;SIGNAL sub_wire4 : STD_LOGIC ;SIGNAL sub_wire5 : STD_LOGIC ;SIGNAL sub_wire6 : STD_LOGIC_VECTOR (1 DOWNTO 0);SIGNAL sub_wire7_bv : BIT_VECTOR (0 DOWNTO 0);SIGNAL sub_wire7 : STD_LOGIC_VECTOR (0 DOWNTO 0);COMPONENT altpllGENERIC (clk0_divide_by : NATURAL;clk0_duty_cycle : NATURAL;clk0_multiply_by : NATURAL;clk0_phase_shift : STRING;clk1_divide_by : NATURAL;clk1_duty_cycle : NATURAL;clk1_multiply_by : NATURAL;clk1_phase_shift : STRING;clk2_divide_by : NATURAL;clk2_duty_cycle : NATURAL;clk2_multiply_by : NATURAL;clk2_phase_shift : STRING;compensate_clock : STRING;gate_lock_signal : STRING;inclk0_input_frequency : NATURAL; intended_device_family : STRING; invalid_lock_multiplier : NATURAL; lpm_hint : STRING;lpm_type : STRING;operation_mode : STRING;port_activeclock : STRING;port_areset : STRING;port_clkbad0 : STRING;port_clkbad1 : STRING;port_clkloss : STRING;port_clkswitch : STRING;port_configupdate : STRING;port_fbin : STRING;port_inclk0 : STRING;port_inclk1 : STRING;port_locked : STRING;port_pfdena : STRING;port_phasecounterselect : STRING; port_phasedone : STRING;port_phasestep : STRING;port_phaseupdown : STRING;port_pllena : STRING;port_scanaclr : STRING;port_scanclk : STRING;port_scanclkena : STRING;port_scandata : STRING;port_scandataout : STRING;port_scandone : STRING;port_scanread : STRING;port_scanwrite : STRING;port_clk0 : STRING;port_clk1 : STRING;port_clk2 : STRING;port_clk3 : STRING;port_clk4 : STRING;port_clk5 : STRING;port_clkena0 : STRING;port_clkena1 : STRING;port_clkena2 : STRING;port_clkena3 : STRING;port_clkena4 : STRING;port_clkena5 : STRING;port_extclk0 : STRING;port_extclk1 : STRING;port_extclk2 : STRING;port_extclk3 : STRING;valid_lock_multiplier : NATURAL );PORT (clk : OUT STD_LOGIC_VECTOR (5 DOWNTO 0);inclk : IN STD_LOGIC_VECTOR (1 DOWNTO 0);locked : OUT STD_LOGIC ;pllena : IN STD_LOGIC);END COMPONENT;BEGINsub_wire7_bv(0 DOWNTO 0) <= "0";sub_wire7 <= To_stdlogicvector(sub_wire7_bv);sub_wire4 <= sub_wire0(2);sub_wire3 <= sub_wire0(0);sub_wire1 <= sub_wire0(1);c1 <= sub_wire1;locked <= sub_wire2;c0 <= sub_wire3;c2 <= sub_wire4;sub_wire5 <= inclk0;sub_wire6 <= sub_wire7(0 DOWNTO 0) & sub_wire5;altpll_component : altpllGENERIC MAP (clk0_divide_by => 1,clk0_duty_cycle => 50,clk0_multiply_by => 1,clk0_phase_shift => "10000",clk1_divide_by => 1,clk1_duty_cycle => 50,clk1_multiply_by => 2,clk1_phase_shift => "0",clk2_divide_by => 1,clk2_duty_cycle => 50,clk2_multiply_by => 1,clk2_phase_shift => "0",compensate_clock => "CLK0",gate_lock_signal => "NO",inclk0_input_frequency => 20000,intended_device_family => "Cyclone II",invalid_lock_multiplier => 5,lpm_hint => "CBX_MODULE_PREFIX=hsu_2014_ch2_pll_vhdl", lpm_type => "altpll",operation_mode => "NORMAL",port_activeclock => "PORT_UNUSED",port_areset => "PORT_UNUSED",port_clkbad0 => "PORT_UNUSED",port_clkbad1 => "PORT_UNUSED",port_clkloss => "PORT_UNUSED",port_clkswitch => "PORT_UNUSED",port_configupdate => "PORT_UNUSED",port_fbin => "PORT_UNUSED",port_inclk0 => "PORT_USED",port_inclk1 => "PORT_UNUSED",port_locked => "PORT_USED",port_pfdena => "PORT_UNUSED",port_phasecounterselect => "PORT_UNUSED",port_phasedone => "PORT_UNUSED",port_phasestep => "PORT_UNUSED",port_phaseupdown => "PORT_UNUSED",port_pllena => "PORT_USED",port_scanaclr => "PORT_UNUSED",port_scanclk => "PORT_UNUSED",port_scanclkena => "PORT_UNUSED",port_scandata => "PORT_UNUSED",port_scandataout => "PORT_UNUSED",port_scandone => "PORT_UNUSED",port_scanread => "PORT_UNUSED",port_scanwrite => "PORT_UNUSED",port_clk0 => "PORT_USED",port_clk1 => "PORT_USED",port_clk2 => "PORT_USED",port_clk3 => "PORT_UNUSED",port_clk4 => "PORT_UNUSED",port_clk5 => "PORT_UNUSED",port_clkena0 => "PORT_UNUSED",port_clkena1 => "PORT_UNUSED",port_clkena2 => "PORT_UNUSED",port_clkena3 => "PORT_UNUSED",port_clkena4 => "PORT_UNUSED",port_clkena5 => "PORT_UNUSED",port_extclk0 => "PORT_UNUSED",port_extclk1 => "PORT_UNUSED",port_extclk2 => "PORT_UNUSED",port_extclk3 => "PORT_UNUSED",valid_lock_multiplier => 1)PORT MAP (inclk => sub_wire6,pllena => pllena,clk => sub_wire0,locked => sub_wire2);END SYN;3.20试用VHDL 语言设计一个曼彻斯特编码器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA技术与应用作业1.5什么叫“综合”?一般综合包含哪些过程?答:将多个模块化设计文件合并为一个网表文件,并使层次设计平面化(即展平);对VHDL 或Verilog HDL进行分析处理,并将其转换成电路结构或模块,对实际现实目标器件的结构进行优化,并使之满足各种条件约束,优化关键路径。

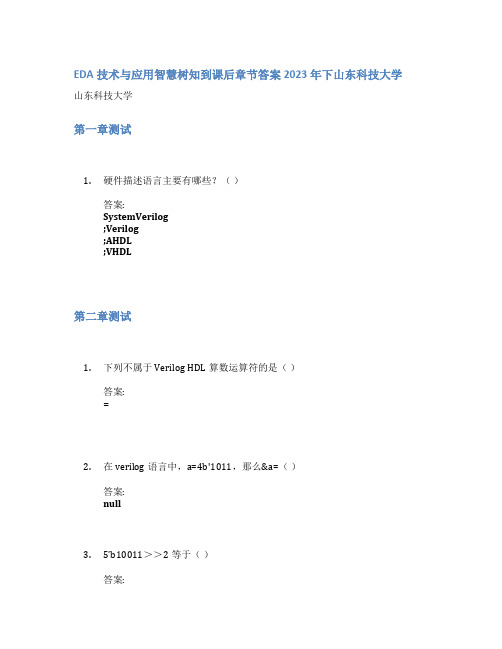

2.10 使用Quartus II 的Mega Wizard Plug-In Manager 宏功能模块中的PLL设计一个能实现图题2.10波形的电路元件(包括一个VHDL文件和一个*.bsf原理图图标)。

其中:inclk0 为电路的主频输入端,频率为50MHz areset为异步置位端,c2和主频inclk0 同频率。

c1为主频inclk0的倍频输出信号。

c0为c2的反相信号。

Locked为相位控制信号,也是输出使能控制信号。

]A I > I II f A 11 JtftlI粤*电・・■■嶂]]审越购劭电* 4- t[:■: i M:吐"赳匚|划n亡底昼% :1=吐_解:allpllOc^>iC2r-c2IbtrkEdlLIBRARY IEEE;0 iKikO 梓一pl宦na■- ■"〜=:©Q■ ■忆:-匸1二1•二:::G2Ala Edi hriau ■fcdd locdii Bock rm view Win^m HdqpIM紂Dlleirafre^uErcy: &3.O30 VHz2>perat»cm htode: HGrrr-slUSE ieee.std_logic_1164.all; LIBRARY altera_mf;USE altera_mf.all;ENTITY whyy ISPORT(inclk0:IN STD_LOGIC := '0';pllena:IN STD_LOGIC := '1';c0:OUT STD_LOGIC ;c1:OUT STD_LOGIC ;c2:OUT STD_LOGIC ;locked:OUT STD_LOGIC ); END whyy;ARCHITECTURE SYN OF whyy ISSIGNAL sub_wire0 SIGNAL sub_wire1 SIGNAL sub_wire2 SIGNAL sub_wire3 SIGNAL sub_wire4 SIGNAL sub_wire5 SIGNAL sub_wire6 STD_LOGIC_VECTOR (5 DOWNTO 0); STD_LOGIC ;STD_LOGIC ;STD_LOGIC ;STD_LOGIC ;STD_LOGIC ;STD_LOGIC_VECTOR (1 DOWNTO 0);SIGNAL sub_wire7_bv : BIT_VECTOR (0 DOWNTO 0);SIGNAL sub_wire7 : STD_LOGIC_VECTOR (0 DOWNTO 0);COMPONENT altpllGENERIC (clk0_divide_by clk0_duty_cycle clk0_multiply_by clk0_phase_shift clk1_divide_by clk1_duty_cycle clk1_multiply_by clk1_phase_shift clk2_divide_by clk2_duty_cycle clk2_multiply_by clk2_phase_shift : NATURAL;: NATURAL;: NATURAL;: STRING; : NATURAL;: NATURAL;: NATURAL;: STRING; : NATURAL;: NATURAL;: NATURAL;: STRING;compensate_clock : STRING;gate_lock_signal : STRING;inclk0_input_frequency : NATURAL; intended_device_family : STRING; invalid_lock_multiplier : NATURAL; lpm_hint : STRING;lpm_type : STRING;operation_mode STRING;port_activeclock : STRING;port_areset : STRING;port_clkbad0 STRING;port_clkbad1 STRING;port_clkloss STRING;port_clkswitch STRING;port_configupdate : STRING;port_fbin : STRING;port_inclk0 : STRING;port_inclk1 : STRING;port_locked : STRING;port_pfdena : STRING;port_phasecounterselect : STRING; port_phasedone STRING;port_phasestep STRING;port_phaseupdown : STRING;port_pllena : STRING;port_scanaclr STRING;port_scanclk STRING;port_scanclkena STRING;port_scandata STRING;port_scandataout : STRING;port_scandone STRING;port_scanread STRING;port_scanwrite STRING;port_clk0 : STRING;port_clk1 : STRING;port_clk2 : STRING;port_clk3 : STRING;port_clk4 : STRING;port_clk5 : STRING;port_clkena0 STRING;port_clkena1 STRING;port_clkena2 STRING;port_clkena3 STRING;port_clkena4 STRING;);PORT (clk : OUT STD_LOGIC_VECTOR (5 DOWNTO 0); inclk: IN STD_LOGIC_VECTOR (1 DOWNTO 0);locked : OUT STD_LOGIC ; pllena : IN STD_LOGIC);END COMPONENT; BEGINsub_wire7_bv(0 DOWNTO 0) <= "0"; sub_wire7 <=To_stdlogicvector(sub_wire7_bv); sub_wire4 <= sub_wire0(2); sub_wire3 <= sub_wire0(0); sub_wire1 <= sub_wire0(1); c1 <= sub_wire1; locked <= sub_wire2; c0 <= sub_wire3; c2 <= sub_wire4;sub_wire5 <= inclk0; sub_wire6 <= sub_wire7(0 DOWNTO 0) & sub_wire5;altpll_component : altpllGENERIC MAP ( clk0_divide_by => 1, clk0_duty_cycle => 50,clk0_multiply_by => 1, clk0_phase_shift => "10000",clk1_divide_by => 1, clk1_duty_cycle => 50, clk1_multiply_by => 2, clk1_phase_shift => "0", clk2_divide_by => 1, clk2_duty_cycle => 50, clk2_multiply_by => 1,clk2_phase_shift => "0", compensate_clock => "CLK0", gate_lock_signal => "NO", inclk0_input_frequency => 20000, intended_device_family => "Cyclone II", invalid_lock_multiplier => 5, lpm_hint =>"CBX_MODULE_PREFIX=hsu_2014_ch2_pll_vhdl", lpm_type => "altpll", operation_mode => "NORMAL", port_activeclock => "PORT_UNUSED", port_areset => "PORT_UNUSED", port_clkbad0 => "PORT_UNUSED", port_clkbad1 => "PORT_UNUSED", port_clkloss => "PORT_UNUSED", port_clkswitch => "PORT_UNUSED", port_configupdate => "PORT_UNUSED", port_fbin => "PORT_UNUSED", port_inclk0 => "PORT_USED", port_inclk1 => "PORT_UNUSED", port_locked => "PORT_USED",port_pfdena => "PORT_UNUSED", port_phasecounterselect => "PORT_UNUSED", port_phasedone => "PORT_UNUSED",port_clkena5 port_extclk0 port_extclk1 port_extclk2 port_extclk3STRING; STRING; STRING; STRING; STRING;valid_lock_multiplier : NATURALport_phasestep => "PORT_UNUSED", port_phaseupdown => "PORT_UNUSED", port_pllena => "PORT_USED",port_scanaclr => "PORT_UNUSED", port_scanclk => "PORT_UNUSED", port_scanclkena => "PORT_UNUSED", port_scandata => "PORT_UNUSED", port_scandataout => "PORT_UNUSED", port_scandone => "PORT_UNUSED", port_scanread => "PORT_UNUSED", port_scanwrite => "PORT_UNUSED", port_clk0 => "PORT_USED", port_clk1 => "PORT_USED", port_clk2 => "PORT_USED", port_clk3 => "PORT_UNUSED", port_clk4 => "PORT_UNUSED", port_clk5 => "PORT_UNUSED", port_clkena0 => "PORT_UNUSED", port_clkena1 => "PORT_UNUSED", port_clkena2 => "PORT_UNUSED", port_clkena3 => "PORT_UNUSED",port_clkena4 => "PORT_UNUSED", port_clkena5 => "PORT_UNUSED", port_extclk0 => "PORT_UNUSED",port_extclk1 => "PORT_UNUSED", port_extclk2 =>"PORT_UNUSED", port_extclk3 => "PORT_UNUSED",valid_lock_multiplier => 1)PORT MAP (inclk => sub_wire6, plle na => plle na, clk => sub_wire0, locked=> sub_wire2);clkclk_d clk_ix clk_lo n.me ode_oiu.£3.20试用VHDL语言设计一个曼彻斯特编码器。