PN(伪随机码)码发生器的设计

伪随机码发生器研究与设计

伪随机码发生器的研究与设计Pseudo-random code generator Research and Design摘要伪随机序列产生技术是集数学、计算机科学、电子与通信等诸多学科于一身的技术,其产生技术自上世纪末至今一直是国内外的研究热点并取得了不少的成果。

伪随机码越来越受到人们的重视,被广泛应用于导弹、卫星、飞船轨道测量和跟踪、雷达、导航、移动通信、保密通信和通信系统性能的测量以及数字信息处理系统中。

目前国内外均有项目研究提高伪随机序列发生器可靠性、状态利用率等问题。

本课题介绍了伪随机码的应用和研究概况,研究了伪随机码的产生方式和产生原理,并以此为基础阐述了一种基于移位寄存器的m序列伪随机码发生器的设计与实现的方法。

最终在使用集成电路的前提下,先分析由移位寄存器电路构成的伪随机序列发生器的设计方法,分步设计了移位寄存器电路和同步复位信号发生电路;再通过一系列的误差和可靠性调整设计,最终用小规模集成电路和外加时钟信号设计实现了线性反馈移位寄存器产生周期P=15的m序列,并且给出了完整的实现电路和时序分析结果。

关键词:伪随机码,绕码,m序列,移位寄存器ABSTRACTPseudo-random sequence generation technique is a mathematics, computer science, electronics and communication, and many other subjects in one of the technology, its production technology since the end of the century has been the research focus at home and abroad and made a lot of results.Pseudo-random code more and more attention, is widely used in missiles, satellites, spacecraft orbit measurement and tracking, radar, navigation, mobile communications, secure communications and communication system performance measurement and digital information processing system. Research projects at home and abroad are pseudo-random sequence generator to improve reliability, availability status and other issues.This topic describes the application of pseudo-random code and research overview of the pseudo-random code generation means and generating principle, and described as the basis for an m-sequence shift register based pseudo-random code generator of the design and implementation Approach. Final premise in the use of integrated circuits, the first shift register circuits of the pseudo-random sequence generator design, step by step design of the shift register circuit and the synchronous reset signal circuit; then through a series of errors and reliable Adjustment design, end-users and small-scale integrated circuit design of the clock signal applied to achieve a linear feedback shift register generating cycle P = 15 m-sequence and provides a complete implementation of the circuit and timing analysis. Key words:Pseudo-random code,Around the code, m sequence,Shift register目录摘要 (Ⅰ)ABSTRACT (Ⅱ)目录 (Ⅲ)1 绪论 (1)1.1 伪随机序列的研究概况 (1)1.2 伪随机序列的应用领域及其意义 (1)1.3 课题研究内容与难点 (2)2 伪随机序列发生器 (3)2.1 伪随机序列的定义及其特点 (3)2.2 伪随机序列的产生 (3)2.3 伪随机序列反馈函数 (4)3伪随机码发生器电路设计 (7)3.1 移位寄存器电路设计 (7)3.2置数功能电路设计 (7)3.3可靠性附加电路设计 (8)3.4元器件选型 (10)3.5整体电路图 (10)4电路时序分析 (12)4.1移位寄存器电路时序分析 (12)4.2完整电路时序分析 (12)结束语 (14)参考文献 (15)附录芯片逻辑引脚图及各型号性能对比 (16)致谢 (17)1 绪论1.1 伪随机码的研究概况伪随机码又称伪随机序列或伪噪声序列。

M序列发生器

M 序列发生器M 序列(即De Bruijn 序列)又叫做伪随机序列、伪噪声(PN)码或伪随机码。

可以预先确定并且可以重复实现的序列称为确定序列;既不能预先确定又不能重复实现的序列称随机序列;不能预先确定但可以重复产生的序列称伪随机序列。

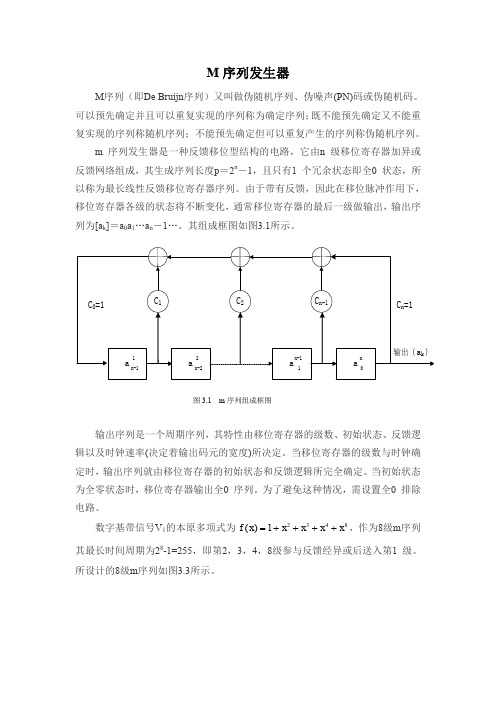

m 序列发生器是一种反馈移位型结构的电路,它由n 级移位寄存器加异或反馈网络组成,其生成序列长度p =2n -1,且只有1 个冗余状态即全0 状态,所以称为最长线性反馈移位寄存器序列。

由于带有反馈,因此在移位脉冲作用下,移位寄存器各级的状态将不断变化,通常移位寄存器的最后一级做输出,输出序列为[a k ]=a 0a 1…a n -1…。

其组成框图如图3.1所示。

输出序列是一个周期序列,其特性由移位寄存器的级数、初始状态、反馈逻辑以及时钟速率(决定着输出码元的宽度)所决定。

当移位寄存器的级数与时钟确定时,输出序列就由移位寄存器的初始状态和反馈逻辑所完全确定。

当初始状态为全零状态时,移位寄存器输出全0 序列。

为了避免这种情况,需设置全0 排除电路。

数字基带信号V 1的本原多项式为84321)(x x x x x f ++++=,作为8级m 序列其最长时间周期为28-1=255,即第2,3,4,8级参与反馈经异或后送入第1 级。

所设计的8级m 序列如图3.3所示。

图3.1 m 序列组成框图a n-11a n-22a 1n-1a 0n C 1C 2C n-1C n =1C 0=1输出{a k }依据上图原理,设计了一种通过手动置数产生M 序列的电路,其电路设计如图3.4所示,该图由Protel SE99绘制,再根据该图搭建硬件电路,图中的单刀开关可以用拨码开关代替。

电路分析:全0状态时,采用此方法设计的m 序列发生器不具有自启动特性。

为了使电路启动,可以断开开关S 1,将74LS194 的工作方式控制端S 1置高电平,这时S 1和S 0均为高电平,即S 1S 0=11,74LS194 处于置数状态,把输入端的初始状态10000000 置到输出端。

伪随机码产生器实验

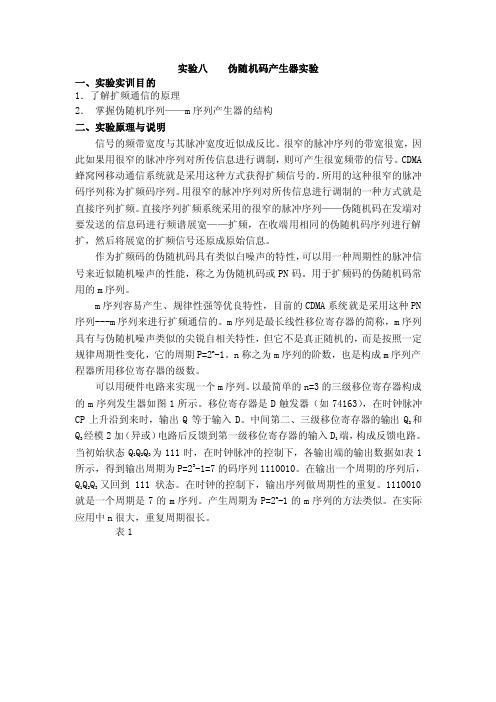

实验八伪随机码产生器实验一、实验实训目的1.了解扩频通信的原理2.掌握伪随机序列——m序列产生器的结构二、实验原理与说明信号的频带宽度与其脉冲宽度近似成反比。

很窄的脉冲序列的带宽很宽,因此如果用很窄的脉冲序列对所传信息进行调制,则可产生很宽频带的信号。

CDMA 蜂窝网移动通信系统就是采用这种方式获得扩频信号的。

所用的这种很窄的脉冲码序列称为扩频码序列。

用很窄的脉冲序列对所传信息进行调制的一种方式就是直接序列扩频。

直接序列扩频系统采用的很窄的脉冲序列——伪随机码在发端对要发送的信息码进行频谱展宽——扩频,在收端用相同的伪随机码序列进行解扩,然后将展宽的扩频信号还原成原始信息。

作为扩频码的伪随机码具有类似白噪声的特性,可以用一种周期性的脉冲信号来近似随机噪声的性能,称之为伪随机码或PN码。

用于扩频码的伪随机码常用的m序列。

m序列容易产生、规律性强等优良特性,目前的CDMA系统就是采用这种PN 序列---m序列来进行扩频通信的。

m序列是最长线性移位寄存器的简称,m序列具有与伪随机噪声类似的尖锐自相关特性,但它不是真正随机的,而是按照一定规律周期性变化,它的周期P=2n-1。

n称之为m序列的阶数,也是构成m序列产程器所用移位寄存器的级数。

可以用硬件电路来实现一个m序列。

以最简单的n=3的三级移位寄存器构成的m序列发生器如图1所示。

移位寄存器是D触发器(如74163),在时钟脉冲CP上升沿到来时,输出Q等于输入D。

中间第二、三级移位寄存器的输出Q2和Q3经模2加(异或)电路后反馈到第一级移位寄存器的输入D1端,构成反馈电路。

当初始状态Q1Q2Q3为111时,在时钟脉冲的控制下,各输出端的输出数据如表1所示,得到输出周期为P=23-1=7的码序列1110010。

在输出一个周期的序列后,Q1Q2Q3又回到111状态。

在时钟的控制下,输出序列做周期性的重复。

1110010就是一个周期是7的m序列。

产生周期为P=2n-1的m序列的方法类似。

PN(伪随机码)码发生器的设计

通信系统专业课程设计一.课题名称:PN(伪随机码)码发生器的设计二.设计目的:1、巩固加深对电子线路的基本知识,提高综合运用专业知识的能力;2、培养学生查阅参考文献,独立思考、设计、钻研专业知识相关问题的能力;3、通过实际制作安装电子线路,学会单元电路以及整机电路的调试与分析方法;4、掌握相关电子线路工程技术规范以及常规电子元器件的性能技术指标;5、了解电气图国家标准以及电气制图国家标准,并利用电子CAD正确绘制电路图;6、培养严肃认真的工作作风与科学态度,建立严谨的工程技术观念;7、培养工程实践能力、创新能力和综合设计能力。

三.设计要求:1、通信系统的原理框图,说明系统中各主要组成部分的功能;2、根据选用的软件编好用于系统仿真的测试文件;3、拟采用的实验芯片的型号可选89c51、TSC 5402、5416、2407及ALTERA的EPM7128CPLD或EP1K30进行硬件验证;4、独立完成课程设计报告,严禁报告内容雷同;5、电路图中的图形符号必须符合国家或国际标准。

四.所用仪器设备:Altera的MAX 7000S系列芯片;方正文祥电脑。

五.设计内容:1、伪随机序列产生原理及作用:随着通信理论的发展,早在20世纪40年代,香农就曾指出,在某些情况下,为了实现最有效的通信,应采用具有白噪声的统计特性的信号。

另外,为了实现高可靠的保密通信,也希望利用随机噪声。

然而,利用随机噪声最大困难是它难以重复产生和处理。

直到60年代,伪随机噪声的出现才使这一难题得到解决。

伪随机噪声具有类似于随机噪声的一些统计特性,同时又便于重复产生和处理。

由于它具有随机噪声的优点,又避免了它的缺点,因此获得了日益广泛的应用。

目前广泛应用的伪随机序列都是由数字电路产生的周期序列得到的,我们称这种周期序列为伪随机序列。

对与伪随机序列有如下几点要求:①应具有良好的伪随机性,即应具有和随机序列类似的随机性;②应具有良好的自相关、互相关和部分相关特性,即要求自相关峰值尖锐,而互相关和部分相关值接近于零。

(2021年整理)PN码的设计

(完整)PN码的设计编辑整理:尊敬的读者朋友们:这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望((完整)PN码的设计)的内容能够给您的工作和学习带来便利。

同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。

本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为(完整)PN码的设计的全部内容。

设计报告课程名称:通信系统课程设计课题名称: PN码的设计系部:电气与信息工程学院专业班级:通信13101学号: 201316020115学生姓名:朱恩邦指导教师: 侯清莲完成时间: 2016-12-28报告成绩:评阅意见:评阅教师日期目录摘要............................................... 错误!未定义书签。

ABSTRACT (5)第一章前言 (6)1。

1设计的提出 (6)1.2 伪随机序列的应用及其意义 (7)1.3 伪随机序列研究现状 (7)1。

4设计内容 (8)第二章伪随机序列与仿真工具的简介 (8)2。

1 伪随机序列理论的发展历史 (9)2。

2 伪随机序列的构造方法 (9)2。

3 MATLAB简介 (10)第三章 m序列 (11)3。

1 m序列的定义 (11)3。

2 m序列的产生 (12)3.3 m序列的性质 (14)3。

4 m序列的计数 (18)第四章 Gold序列 (18)4.1 Gold序列的定义 (18)4。

2 m序列优选对 (19)4.3 Gold序列的产生结构 (22)4。

4 Gold码的性质 (23)4。

5 平衡Gold码 (25)第五章序列的仿真及其仿真比较 (25)5。

1 m序列的仿真 (25)5.2 Gold序列的仿真 (28)5.3 MATLAB环境中伪随机序列相关函数的实现及特性 (30)5。

实验一CMI、PN码型变换实验

实验一CMI、PN码型变换实验一、实验目的1.熟悉光纤通信传输实验系统中信号发生器的组成原理、光发送端信号产生的方法。

2.了解单片机在光纤通信传输系统中的应用以及该单元电路对整个光纤实验系统的管理与控制过程。

3.掌握伪随机码(PN)发生器的工作原理和实验方法。

4.了解光纤通信采用的线路码型。

5.掌握传号烦转码(CMI)的特点,并了解其编码方法。

6.熟悉示波器的使用。

二、实验仪器1.光纤通信传输系统实验箱一台2.20MHz示波器一台三、实验内容与步骤1.连接电源线,按下电路分路开关PA、PB。

发光二极管D1、D2、D3、D4亮,表明实验箱上±5V 和±12V电源工作正常;2.按下“复位”键,使系统处于复位状态。

此时发光二极管D5~D12依次循环点亮,表明实验系统中的中央处理器电路进入正常工作状态;3.用示波器测出图中各测试点(TP101、TP102、TP103、TP104)以及测试点(89C51的主时钟TP1、89C51的地址锁存信号TP2)的波形;4.按下“PN”键,再按“确认”键,PN码对应的发光二极管D8闪烁,表示系统工作于PN码状态;5.用示波器测出图中各测试点(TP109、TP110)的波形,并做纪录;6.按下“复位”键,使系统处于复位状态。

按下“CMI”键,再按“确认”键,CMI码对应的发光二极管D7闪烁,表示系统工作于CMI码状态;7.用示波器测出图中各测试点(TP109、TP110、TP111、TP112、TP113、TP114、TP115)的波形,并做纪录。

四、实验报告要求1.分析伪随机码发生器的工作原理。

2.分析CMI码编码电路的工作原理。

3.比较CLK时钟、PN码、CMI码的波形,并对波形加以分析。

伪随机序列发生器设计

实验七伪随机序列发生器设计一、实验目的1.掌握伪随机序列(m序列)发生器的基本原理和设计方法;2.深入理解VHDL中signal和variable的不同及其应用;二、设计描述及方法1.伪随机序列概述在扩展频谱通信系统中,伪随机序列起着十分关键的作用。

在直接序列扩频系统得发射端,伪随机序列将信息序列的频谱扩展,在接收端,伪随机序列将扩频信号恢复为窄带信号,进而完成信息的接收。

m序列又称为最长线形反馈移位寄存器序列,该序列具有很好的相关性能。

m序列发生器的基本结构为:其中(C r,C r-1,…,C0)为反馈系数,也是特征多项式系数。

这些系数的取值为“1”或“0”,“1”表示该反馈支路连通,“0”表示该反馈支路断开。

下图为实际m序列发生器的电路图:图中利用D触发器级联的方式完成移位寄存器的功能。

在系统清零后,D触发器输出状态均为低电平,为了避免m序列发生器输出全“0”信号,图中在“模二加”运算后添加了一个“非门”。

从图中A、B、C、D四个节点均可得到同一m序列,只是序列的初始相位不同。

特征多项式系数决定了一个m序列的特征多项式,同时也决定了一个m序列。

下表给出了部分m 序列的反馈系数(表中的反馈系数采用八进制表示)2.电路设计基本方法本实验要设计一个寄存器级数为5的m序列发生器,从m序列发生器反馈系数表可知,有三个反馈系数可选,即可以产生三种不同的m序列;在以下设计的接口描述中choice(1 downto0)为m序列选择输入信号,clk为时钟输入信号,reset为复位信号,psout为m序列输出信号。

三、程序代码library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity mps isport (clk,reset : in std_logic;choice : in std_logic_vector(1 downto 0);psout: out std_logic );end mps;architecture behave of mps issignal a :std_logic_vector(4 downto 0);signal k:std_logic;beginprocess(clk,reset,choice,a)begincase choice iswhen "00"=> k<=not(a(3) xor a(2));when "01"=> k<=not(a(4) xor a(3)xor a(2)xor a(0));when "10"=> k<=not(a(4) xor a(2)xor a(1)xor a(0));when others =>k<='X';end case;if clk'event and clk='1' thena(0)<=k;for i in 1 to 4 loopa(i)<=a(i-1);end loop;end if;if(reset='1') thena<="00000";end if;end process;psout<=a(4);end behave;四、功能仿真五、RTL级电路。

实验一伪随机码发生器实验

实验一 伪随机码发生器实验一、实验目的1、 掌握伪随机码的特性。

2、 掌握不同周期伪随机码设计。

3、 用基本元件库和74LS系列元件库设计伪随机码。

4、 了解ALTERA公司大规模可编程逻辑器件EPM7128SLC84内部结构和应用。

5、 学习FPGA开发软件MAXPLUSⅡ,学习开发系统软件中的各种元件库应用。

6、 熟悉通信原理实验板的结构。

二、实验仪器1、 计算机 一台2、 通信基础实验箱 一台3、 100MHz 示波器 一台三、实验原理伪随机码是数字通信中重要信码之一,常作为数字通信中的基带信号源;扰码;误码测试;扩频通信;保密通信等领域。

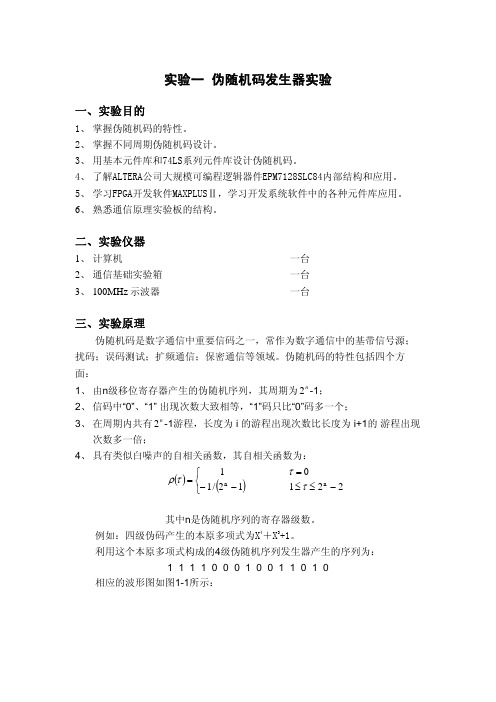

伪随机码的特性包括四个方面:1、 由n 级移位寄存器产生的伪随机序列,其周期为-1; n 22、 信码中“0”、“1” 出现次数大致相等,“1”码只比“0”码多一个;3、 在周期内共有-1游程,长度为 i 的游程出现次数比长度为 i+1的 游程出现次数多一倍;n 24、 具有类似白噪声的自相关函数,其自相关函数为:()()⎩⎨⎧−≤≤=−−=221012/11n nτττρ其中n 是伪随机序列的寄存器级数。

例如:四级伪码产生的本原多项式为X 4+X 3+1。

利用这个本原多项式构成的4级伪随机序列发生器产生的序列为:1 1 1 1 0 0 0 1 0 0 1 1 0 1 0相应的波形图如图1-1所示:图1-1 四级伪随机序列波形图用4个D 触发器和一个异或门构成的伪码发生器具有以下特性: 1、 周期为24-1=15;2、 在周期内“0”出现24 -1-1=7次,“1”出现24 -1=8次;3、 周期内共有24 -1 =8个游程;4、 具有双值自相关特性,其自相关系数为:⎩⎨⎧−≤≤−−==221)12(10144τ / τ ρ(τ)四、实验内容及步骤1、在MAXPLUSⅡ设计平台下进行电路设计 1.1 四级伪随机码发生器电路设计电路原理图如图1-2所示。

图1-2 四级伪随机码电路原理图在MAXPLUS II 环境下输入上述电路,其中: dff ------ 单D触发器 xor ------ 二输入异或门 nor4 ------ 四输入或非门 not ------ 反相器clk ------ 时钟输入引脚(16M时钟输入) 8M ------ 二分频输出测试点引脚 nrz ------ 伪随机码输出引脚 1.2 实验电路编译及FPGA 引脚定义完成原理图输入后按以下步骤进行编译:(1) 在Assign Device 菜单选择器件MAX7128SLC84。

01实验一 伪随机码发生器实验

实验一 伪随机码发生器实验一、实验目的1、 掌握伪随机码的特性。

2、 掌握不同周期伪随机码设计。

3、 用基本元件库和74LS系列元件库设计伪随机码。

4、 了解ALTERA公司大规模可编程逻辑器件EPM7128SLC84内部结构和应用。

5、 学习FPGA开发软件MAXPLUSⅡ,学习开发系统软件中的各种元件库应用。

6、 熟悉通信原理实验板的结构。

二、实验仪器1、 计算机 一台2、 通信基础实验箱 一台3、 100MHz 示波器 一台三、实验原理伪随机码是数字通信中重要信码之一,常作为数字通信中的基带信号源;扰码;误码测试;扩频通信;保密通信等领域。

伪随机码的特性包括四个方面:1、 由n 级移位寄存器产生的伪随机序列,其周期为-1; n 22、 信码中“0”、“1” 出现次数大致相等,“1”码只比“0”码多一个;3、 在周期内共有-1游程,长度为 i 的游程出现次数比长度为 i+1的 游程出现次数多一倍;n 24、 具有类似白噪声的自相关函数,其自相关函数为:()()⎩⎨⎧−≤≤=−−=221012/11n nτττρ其中n 是伪随机序列的寄存器级数。

例如:四级伪码产生的本原多项式为X 4+X 3+1。

利用这个本原多项式构成的4级伪随机序列发生器产生的序列为:1 1 1 1 0 0 0 1 0 0 1 1 0 1 0相应的波形图如图1-1所示:图1-1 四级伪随机序列波形图用4个D 触发器和一个异或门构成的伪码发生器具有以下特性: 1、 周期为24-1=15;2、 在周期内“0”出现24 -1-1=7次,“1”出现24 -1=8次;3、 周期内共有24 -1 =8个游程;4、 具有双值自相关特性,其自相关系数为:⎩⎨⎧−≤≤−−==221)12(10144τ / τ ρ(τ)四、实验内容及步骤1、在MAXPLUSⅡ设计平台下进行电路设计 1.1 四级伪随机码发生器电路设计电路原理图如图1-2所示。

图1-2 四级伪随机码电路原理图在MAXPLUS II 环境下输入上述电路,其中: dff ------ 单D触发器 xor ------ 二输入异或门 nor4 ------ 四输入或非门 not ------ 反相器clk ------ 时钟输入引脚(16M时钟输入) 8M ------ 二分频输出测试点引脚 nrz ------ 伪随机码输出引脚 1.2 实验电路编译及FPGA 引脚定义完成原理图输入后按以下步骤进行编译:(1) 在Assign Device 菜单选择器件MAX7128SLC84。

17伪随机数发生器的设计

119

原胞自动机伪随机数发生器同样是通过寄存器的延时来实现。每当一个时钟 脉冲到来时,每一级存储器 Qi 的值根据 CA 规则来决定,CA90 和 CA150(即 CA01011010B 和 CA10010110B)算法规则的规则查找表分别如表 1,2 所示,其中相 邻单元的值为η,输出值为 Q=f(η)。CA90 算法规则等价的逻辑函数是由当前单 元的相邻左右单元的状态值相异或,而 CA150 算法规则等价的逻辑函数是由相邻 当前单元和左右单元的状态值相异或。下面分别给出它们的逻辑函数表达式。

3.原胞自动机 一个原胞自动机(Cellular Automata,CA)是一种有限状态机,有 n 个离散

的单元,每个单元以离散的节拍进化,其中每个单元的下一个状态值由该单元的 当前状态值和其相邻的当前状态值通过查找表(Look-UpTable,LUT)(或等价的逻 辑函数)来决定,而相邻单元的状态值是独立的。

Cn

Cn-1

Cn-2

C1

C0=1

图 1 传统多级线性移位寄存器结构

3.m 序列 m 序列(maximum-length)是一类最大长度线性移位寄存器序列的简称。 m

序列是目前广泛应用的一种伪随机序列,其在通信领域有着广泛的应用,如扩频 通信,卫星通信的码分多址,数字数据中的加密、加扰、同步、误码率测量等领 域。

表 1 CA90 规则查找表

η 111 110 101 100 011 010 001 000

伪随机码发生器研究与设计

伪随机码发生器研究与设计伪随机码发生器是一种通过其中一种算法生成伪随机序列的电子设备或程序。

与真随机数发生器不同,伪随机码发生器是基于确定性算法生成的序列,其看似是随机的,但实际上可以通过逆向计算或算法分析来预测出后续的码值。

1.算法选择:伪随机码发生器的性能很大程度上取决于所选择的算法。

常用的算法包括线性反馈移位寄存器(LFSR)、离散余弦变换(DCT)、线性同余发生器(LCG)等。

研究者可以根据特定需求选择合适的算法,并通过数学分析、理论推导和模拟实验来评估其性能。

2.随机性测试:伪随机码发生器生成的序列是否具备足够的随机性是一个关键问题。

为了评估伪随机码发生器的性能,需要设计合适的随机性测试方法。

常用的测试方法包括统计分析、频谱分析、序列均匀性检测、序列独立性检验等。

3.秘密性与安全性:在密码学应用中,伪随机码发生器的秘密性和安全性是非常重要的。

秘密性指发生器的设计和参数应保密,只有掌握这些信息的人才能伪装成合法用户。

安全性指发生器生成的序列在密码攻击下能够抵抗各种攻击手段。

确保秘密性和安全性需要对伪随机码发生器进行全面的安全性分析和风险评估,以便发现可能存在的漏洞和弱点,并采取相应的安全措施和改进措施。

4.性能优化:伪随机码发生器的性能包括生成速度、存储空间和计算复杂度等方面。

研究者需要在保证安全性的前提下,尽可能提高伪随机码发生器的性能。

这包括改进算法、优化参数选择、使用硬件加速等。

总结起来,伪随机码发生器的研究与设计需要深入理解随机性、密码学和计算机科学等领域的知识,并结合具体应用需求来选择合适的算法和进行性能优化。

通过合理的算法设计、随机性测试和安全性分析评估,以及针对性的安全措施和改进措施,可以设计出安全可靠的伪随机码发生器。

伪随机序列发生器设计

伪随机序列发生器设计伪随机序列发生器(PRNG)是一种通过算法生成的看似随机的数字序列。

与真随机序列不同,伪随机序列是在一定条件下按照确定性算法生成的。

在计算机系统中,PRNG具有广泛的应用,包括密码学、模拟、游戏等领域。

本文将讨论如何设计一个伪随机序列发生器。

1.随机性的度量:在设计PRNG之前,我们需要了解随机性的度量。

一个好的伪随机序列发生器应该具有高周期性(周期长度大),均匀性(数字出现的频率相似)和不相关性(序列中的数字之间没有明显的关联)。

周期指的是序列重复之前所产生的数字数量。

均匀性可以通过观察数字出现的频率和统计分析来评估。

不相关性指的是序列中的任意两个数字之间没有明显的关联。

2.线性反馈移位寄存器(LFSR):LFSR是一种常见的PRNG设计方法。

它由一个位寄存器和一些异或门组成。

位寄存器中的每个位都线性地与寄存器中的其他位进行异或运算,并且每次循环位寄存器向右移位。

输入位是通过将一些位与1或0常量进行异或来确定的。

3.LFSR的优化:为了改善LFSR的性能,在设计中可以考虑一些优化措施。

一种常见的优化措施是增加反馈函数的复杂性。

通过使用非线性函数,可以在相同的位数下获得更长的周期。

另一个优化措施是根据需要选取适当的位数。

位数越大,周期越长,但计算成本也增加。

4.添加非线性元素:为了进一步提高伪随机序列的质量,我们可以添加一些非线性元素。

一种方法是使用置换函数。

置换函数将输入映射到不同的输出,从而增加了数字之间的不相关性。

另一种方法是使用哈希函数。

哈希函数将输入的随机性扩展到更大的空间中,并通过混淆输入来减少数字之间的关联。

5.分析和测试:设计一个PRNG后,我们需要对其进行分析和测试。

常用的测试方法包括统计测试、重复序列测试和关联测试。

统计测试可以用于检查输出数字的频率。

重复序列测试可以用于验证序列中是否存在重复数字。

关联测试则是用于检查序列中数字之间的关联性。

总结:设计一个高质量的伪随机序列发生器需要考虑随机性度量、LFSR和优化、非线性元素的添加以及分析和测试的步骤。

伪随机码发生器设计的控制

摘要伪随机码又称伪随机序列, 是一种可以预先确定并可以重复地产生和复制, 又具有随机统计特性的二进制码序列。

在现代工程实践中, 伪随机信号在移动通信、导航、雷达和保密通信、通信系统性能的测量等领域中有着广泛的应用。

例如, 在连续波雷达中可用作测距信号, 在遥控系统中可用作遥控信号, 在多址通信中可用作地址信号, 在数字通信中可用作群同步信号, 还可用作噪声源以及在保密通信中的加密作用等,伪随机发生器在测距、通信等领域的应用日益受到人们重视。

本文提出了一种产生m序列的方法,并针对这种方法设计了一个系统。

该系统包括PC机,控制器和片外围电路CPLD,本文主要是针对控制器部分的设计。

首先分析m序列的基本原理、结构、性质及产生方法,然后提出了整体设计思路,以单片机芯片AT89C2051作为控制器,利用MAX232实现与上位机的异步串行通信,并传送阶数信号给CPLD。

CPLD通过原理图产生所需的m序列。

接着利用PROTEL99SE软件完成硬件部分的设计,包括单片机最小系统,单片机与上位机的连接,单片机与CPLD的连接。

最后是采用汇编程序语言完成软件部分的设计,包括单片机与上位机的通信,单片机对CPLD的控制。

关键词:伪随机序列;m序列;单片机;PC机,CPLDABSTRACTPseudo random code is also called pseudorandom sequence, which can be determined in advance and can be repeatedly produced and reproduced, and have a random statistical properties of the binary code sequence. In modern engineering practice, pseudo random signal in mobile communication, navigation,radar and communication, communication system performance measurement are widely used in the field of. For example, continuous wave radar can be used as a ranging signal, the remote control system can be used as a remote control signal, a multiple access communication can be used as an address signal, digital communications can be used as a group synchronization signal and can also be used as a source of noise and in secret communication encryption function. pseudo random number generator in location, communication etc. field application is increasingly paid attention to. This paper presents a m sequence generation method, and the way to the design of a system.The system includes the PC machine, controller and peripheral circuit of CPLD, this paper is aimed at the control part of the design. The first analysis of the m sequence of basic principles, structure, properties and production method, and then put forward the overall design ideas, to the single chip AT89C2051 as the controller, using MAX232 to achieve computer asynchronous serial communication, and transmits the signal to the CPLD order number. Through the CPLD diagram to produce desired m sequences. Then use the PROTEL99SE software to complete the hardware design, including the smallest single-chip system, MCU and PC connection, single chip computer and CPLD connection. The last is the use of assembly language to complete the software part of the design, including the MCU and computer communications, single-chip microcomputer to control CPLD.Keywords:Pseudo-random sequence; m sequence; single chip microcomputer; PC, CPLD目录第1章绪论 (1)1.1 研究课题的提出 (1)1.2 伪随机序列的应用及其意义 (1)1.2.1在通信加密中的应用 (1)1.2.2 在雷达信号设计中的应用 (2)1.2.3 在扩频通信中的应用 (2)1.3 伪随机序列研究现状 (3)1.4本论文主要研究内容 (3)第2章 m序列伪随机码理论 (5)2.1伪随机码基本特性 (5)2.2 m序列伪随机码性质 (5)2.2.1 均衡特性(平衡性) (5)2.2.2 游程特性(游程分布的随机性) (5)2.2.3 移位相加特性(线性叠加性) (6)2.2.4 自相关特性 (6)2.2.5 伪噪声特性 (7)2.3 m序列的产生 (7)第3章伪随机码发生器的系统设计 (11)3.1系统总体设计 (11)3.2 PC机与单片机通信部分 (11)3.3 基于单片机的控制器部分 (12)3.4 CPLD部分 (12)第4章伪随机码序列发生器的硬件设计 (14)4.1发生器主控芯片介绍 (14)4.1.1 AT89C205芯片 (14)4.1.2 MAX232芯片 (16)4.1.3 XC9500芯片 (17)4.2 m序列发生器控制器电路设计 (20)4.2.1 AT89C2051与PC的连接电路 (20)4.2.2 单片机AT89C2051与CPLD的连接电路 (21)4.2.3 电路原理图的制作 (22)第5章伪随机码序列发生器的控制器软件设计 (27)5.1异步串行通信技术 (27)5.1.1 异步串行通信 (27)5.1.2 串行通信协议 (28)5.1.3 89C2051串行口 (29)5.2 单片机与上位机的通信 (29)5.3 单片机控制CPLD (30)结论 (32)参考文献 (33)致谢 (34)第1章绪论1.1 研究课题的提出伪随机序列系列具有良好的随机性和接近于白噪声的相关函数,并且有预先的可确定性和可重复性。

伪随机码脉冲信号发生器电路设计

伪随机码脉冲信号发生器电路设计摘要由于伪随机码在CDMA(Code Division Multiple Access)技术中得到了广泛的应用,为更好的利用CDMA技术,需了解伪随机码脉冲信号。

本课题主要是应用CPLD技术,设计一个伪随机码脉冲信号发生器电路,所用到的主要元器件有74LS74、EPM7128SLC84—15 MAX 7000可编程逻辑器件及一些门电路等,并利用MAX+PLUS Ⅱ软件来观察电路波形及CPLD综合实验板来检测电路的功能是否达到设计要求。

关键词伪随机码 CPLD 74LS74 EPM7128SLC-15ABSTRACTPseudorandom code is wide use in CDMA (Code Division Multiple Access)technology, to make use of CDMA technology,we should know Pseudorandom code Pulses. My design is based on CPLD technology ,and design a circuit to produce pseudorandom code. Device I used as follows:74LS74、EPM7128SLC84-15 MAX 7000 progranmable logic device 、some gate circuit and so on .At last ,we can use MAX+PLUSⅡsoftware and the board of CPLD which is comprehensive to inspect the application of this circuit is right or wrong.Keywords pseudorandom code;CPLD;74LS74;EPM7128SLC84-15 MAX 7000 progranmable logic device第1章绪论 (4)1.1伪随机序列的概念 (4)1.2伪随机序列的产生 (4)1..3几种伪随机序列的比较 (4)1.3.1 m序列 (4)1.3.2 M序列 (4)第2章主要元器件说明 (6)2.1 核心模块EPM7128SLC84-15 (6)2.1.1开关模块 (7)2.1.2 LED显示模块 (8)2.1.3 相关资源分配为: (9)2.2 74LS74 (10)2.2.1 74LS74引脚图 (10)2.2.2 74LS74功能表 (10)第3章原理图及逻辑示意图 (11)3.1原理框图 (11)3.1.1四级移位寄存器构成的m序列: (11)3.1.2四级移位寄存器构成的M序列: (11)3.2电路图 (12)3.2.1 四级移位寄存器构成的m序列: (12)3.2.2 四级移位寄存器构成的M序列: (13)第4章电路的时序波形及功能验证 (14)4.1 四级m序列: (14)4.2 四级M序列: (16)4.3 使用CPLD实验板检测电路功能是否达到实验要求: (18)第5章总结 (19)感谢辞 (20)参考文献 (21)第1章绪论在通信系统中,对误码率的测量、通信加密、数据序列的扰码和解码、扩频通信等方面均要用到伪随机序列,伪随机序列的特性对系统的性能有重要的影响,因此有必要了解和掌握伪随机序列的的概念和特性。

伪随机序列发生器设计

伪随机序列发生器设计

伪随机序列发生器(PRNG)是生成伪随机数字序列的算法,用于实现

一种统计分布的结果。

它与真正随机序列发生器(TRNG)有所不同,它会

生成完全随机的序列。

伪随机序列发生器(PRNG)一般用于实现加密算法、在游戏中实现随机数据,以及在模拟环境中实现随机事件等多种用途。

1)伪随机序列发生器的硬件部分:目前伪随机序列发生器均采用数

字电路来实现,一般是采用静态只读存储器(SRAM)实现,可以提供高速、稳定和可靠的性能。

2)伪随机序列发生器的算法:伪随机序列发生器需要一个有效的算

法来生成伪随机数字。

比较常用的算法有线性同余法、梅森旋转法、高斯

随机数法等。

3)伪随机序列发生器的参数:伪随机序列发生器需要选择适当的参

数来实现随机序列的变化,可以选择常数、Seed值、基量值等。

4)伪随机序列发生器的测试:需要对伪随机序列发生器进行充分的

测试,以确保它的算法是有效的,能够生成随机数字,而且经过测试不会

有规律性。

总而言之,伪随机序列发生器的设计需要考虑硬件部分、算法、参数

以及测试等多个要素,以确保它能够有效地生成伪随机数字,而且不会有

规律性。

伪随机码发生器设计

伪随机码发生器设计伪随机码发生器设计1 引言随着科学技术的进步,现代战争样式向信息战形式发展。

现代战争胜负对于信息获取的依赖程度前所未有的提高。

在现代战争中,若己方的通讯交流方式早敌军破获,则地方将获取己方部队动向或实施信息干扰。

将会使部队陷入极其危险地境地中。

因此,信息战对通讯加密手段的要求极高。

伪随机序列(Pseudonoise Sequence)又称伪噪声或伪随机码,具有类似随机信号的一些统计特性,但又是有规律的,容易产生和复制的。

最大长度线性移位寄存器序列(m序列)是保密通信中非常重要的一种伪随机序列,它具有随机性、规律性及较好的自相关和互相关性,而且密钥量很大。

利用m序列加密数字信号,使加密后的信号在携带原始信息的同时具有伪噪声的特点,以达到在信号传输的过程中隐藏信息的目的;在信号接收端,再次利用m序列加以解密,恢复出原始信号。

这样,通过对m序列的应用,将大大的提高通讯的保密程度和防窃取能力。

这样的通讯手段被称为扩展频谱通信扩展频谱通信(Spread Spectrum Communication)是将待传送的信息数据被伪随机编码也就是扩频序列调制,实现频谱扩展以后再在信道中传输,接收端则采用与发送端完全相同的编码进行解调和相关处理,从而恢复出原始的信息数据。

在这其中,伪随机码发生器是十分重要的一环,是对信息加密的核心器件。

m序列伪随机码发生器即使通过m序列的方式对信息数据编码。

本系统所设计的伪随机码发生器,产生m序列伪随机码。

系统采用AT89S51单片机作为控制芯片,控制使用LCD12864显示处理器产生的m序列伪随机码,并且可通过按键对参数修改,设置初始码及m 序列长度。

单片机根据设定的初始码及m序列长度,按照约定的逻辑运算关系,循环往复的产生0或者1。

2 发生器系统设计2.1总体设计系统分为信息处理、实时显示和按键修改共五大模块。

系统总体结构框图如图1所示:图1 系统总体结构框图如图所示,MCU 对信号进行处理,将所得数据送液晶屏显示。

PN码产生与特性分析实验

实验一 PN 码特性实验一、实验目的1、掌握PN 码的编解码原理。

2、掌握PN 码的软件仿真方法。

3、掌握PN 码的硬件仿真方法。

4、掌握PN 码的硬件设计方法。

二、预习要求1、掌握PN 码的编解码原理和方法。

2、熟悉matlab 的应用和仿真方法。

3、熟悉Quatus 的应用和FPGA 的开发方法。

三、实验原理1、m 序列简介m 序列主要功能为:扩展调制信号的带宽到更大的传输带宽,即扩展频谱,提高系统抗干扰能力;区分通过多址接入方式使用同一传输频带的不同用户的信号,在移动通信CDMA 系统中作为用户地址码和基站地址码;除此外还可以作为扰码,平衡通信中”0”和”1”的数目。

m 序列是有n 级线性移位寄存器产生的周期为21n-的码序列,是最大长度线性回馈移位寄存器序列的简称。

码分多址系统主要采用两种长度的m 序列:一种是周期为1521-的m 序列,又称短PN 码。

另一种是周期为4221-的m 序列,又称长PN 序列。

2、产生原理m 序列产生的一般结构模型如图1所示。

其中(1,2,3,......)k i a i n -=是各移位寄存器的状态,(1,2,......)i c i n =对应各各移位寄存器的回馈系数,1i c =表示该级移位寄存器参与回馈,0i c =表示该级移位寄存器不参与回馈。

0n c c 和不能为0,这是因为00c =意味着移位寄存器无回馈,而0n c =则意味着回馈移位寄存器蜕化为n-1级或更少的级数的回馈。

图1 回馈移位寄存器的结构模型回馈函数为: 1122...k k k n k n a c a c a c a ---=+++(mod 2) ( 1-1 )上述的回馈函数是一个线性递归函数。

当级数(n )和回馈系数确定后,输出就确定了。

回馈的移位寄存器级数不同,则m 序列的回馈系数也不同,表1列出了部分的m 序列发生器的回馈系数,供读者使用时参考。

表中给出的是八进制值,经转换成二进制数值后,可求出相应的回馈系数。

PN码序列发生器基于FPGA的设计实现

II

贵州民族大学本科毕业论文

目

录

摘要 ............................................................................................................................................ I Abstract ...................................................................................................................................... II 目 录 ...................................................................................................................................... III 第 1 章 绪论 .............................................................................................................................. 1 1.1 课题的研究背景及意义...................................................................................................... 1 1.2 PN 码国内外研究概述 ......................................................................................................... 1

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

通信系统专业课程设计一.课题名称:PN(伪随机码)码发生器的设计二.设计目的:1、巩固加深对电子线路的基本知识,提高综合运用专业知识的能力;2、培养学生查阅参考文献,独立思考、设计、钻研专业知识相关问题的能力;3、通过实际制作安装电子线路,学会单元电路以及整机电路的调试与分析方法;4、掌握相关电子线路工程技术规范以及常规电子元器件的性能技术指标;5、了解电气图国家标准以及电气制图国家标准,并利用电子CAD正确绘制电路图;6、培养严肃认真的工作作风与科学态度,建立严谨的工程技术观念;7、培养工程实践能力、创新能力和综合设计能力。

三.设计要求:1、通信系统的原理框图,说明系统中各主要组成部分的功能;2、根据选用的软件编好用于系统仿真的测试文件;3、拟采用的实验芯片的型号可选89c51、TSC 5402、5416、2407及ALTERA的EPM7128CPLD或EP1K30进行硬件验证;4、独立完成课程设计报告,严禁报告内容雷同;5、电路图中的图形符号必须符合国家或国际标准。

四.所用仪器设备:Altera的MAX 7000S系列芯片;方正文祥电脑。

五.设计内容:1、伪随机序列产生原理及作用:随着通信理论的发展,早在20世纪40年代,香农就曾指出,在某些情况下,为了实现最有效的通信,应采用具有白噪声的统计特性的信号。

另外,为了实现高可靠的保密通信,也希望利用随机噪声。

然而,利用随机噪声最大困难是它难以重复产生和处理。

直到60年代,伪随机噪声的出现才使这一难题得到解决。

伪随机噪声具有类似于随机噪声的一些统计特性,同时又便于重复产生和处理。

由于它具有随机噪声的优点,又避免了它的缺点,因此获得了日益广泛的应用。

目前广泛应用的伪随机序列都是由数字电路产生的周期序列得到的,我们称这种周期序列为伪随机序列。

对与伪随机序列有如下几点要求:①应具有良好的伪随机性,即应具有和随机序列类似的随机性;②应具有良好的自相关、互相关和部分相关特性,即要求自相关峰值尖锐,而互相关和部分相关值接近于零。

这是为了接收端准确检测,以减少差错;③要求随机序列的数目以保证在码分多址的通信系统中,有足够的地址提供给不同的用户;④要求设备简单,易实现,成本低。

通常产生伪随机序列的电路为一反馈移存器。

它又分为线形反馈移存器和非线形反馈移存器两类。

由线形反馈移存器产生出的周期最长的二进制数字序列称为最大长度线形反馈移存器,通常称为m序列。

由于它的理论比较成熟,实现比较简便,实际应用也比较广泛,故在这里以m序列发生器为例,设计伪随机序列发生器。

m序列是由带线形反馈的移存器产生的周期最长的一种序列。

线形反馈移位寄存器由时钟控制若干个串接的存储器所组成。

在时钟信号的控制下,寄存器的存储信号由上一级向下一级传递。

如果让某些寄存器的输出反馈回来进行运算,运算结果作为第一级寄存器的输入,则我们可以得到一个移位寄存器序列。

如果移位寄存器的反馈函数和初始状态不同,那么可得到不同的移位寄存器序列。

线性移位寄存器的一般形式如图1所示,总共有1,2,3,…,N个寄存器,他们的状态为Xi(i=1,2,3,…,n),经Ci (I=1,2,3,…,n)相乘后模2加,再反馈。

这里Ci∈(0,1),且乘法规则是0·0=0·1=1·0=0,1·1=1。

实际上Ci =0表示断开,Ci=1表示连接。

因此这个N阶移位寄存器的反馈函数为:F(X1,X2,…,X n)=∑i n=1C i X i特征多项式是:f(x)= ∑i n=1CiX i=C+C1X1+C2X2+…+CnX n特征多项式中的Xi(i=0,1,2...n)与移位寄存器的第i个触发器相对应。

图1 线形移位寄存器的一般形式上述的反馈函数是一个线形递归函数。

当级数(n)和反馈系数一旦确定,则反馈移位寄存器的输出序列就确定了。

反馈移存器的级数n不同,则m序列的反馈系数也不同,表1列出了部分的m序列发生器的反馈系数。

表中给出的是八进制数值,经转换成二进制数值后,可求出相应的反馈系数。

伪随机信号在雷达、遥控、遥测、通信加密和无线电测量系统领域有着广泛的应用。

利用VHDL语言进行软件编程,通过EDA设计软件对程序编译、优化、综合、仿真、适配,最后将生成的网表文件配置于制定的目标芯片中,可以实现不同序列长度的伪随机信号发生器。

2、m序列的性质:(1)均衡性m序列在一个周期内“1”和“0”的个数基本相等。

具体来说,m序列的一个周期中的“0”的个数比“1”的个数少一个。

(2)游程分布我们把伪随机序列中取值(“0”或“1”)相同的一段码位称为一个游程。

在一个游程中包含的位数称为游程长度。

把取值为“0”的游程称为“0”游程,取值为“1”的游程为“1”游程。

在m序列中的一个周期内,游程的总个数等于2n-1,而且“0”游程的数目与“1”游程的数目相等,即各占一半。

一般来说,在m序列中,长度为1的游程占游程总数的一半;长度为2的游程占游程总数的2-k,其中1≤k≤(n-2),而且“0”和“1”的游程各占一半。

长为n-1的游程只有一个,且为“0”游程,长为“1”。

表1 部分m序列发生器的反馈系数3、伪随机码发生器的VHDL实现:基于m序列的性质,我利用EDA技术,在Altera的MAX 7000S系列芯片上实现的伪随机序列发生器,为产生低成本的电子系统测试信号提供了一种简单易行的方法。

EDA (Electronic Design Automation)是以大规模可编程逻辑器件替代中小规模集成电路作为硬件载体,以EDA软件编程的方式对可编程器件进行电子系统设计的计算机辅助电路设计技术。

目前已经广泛应用于电子电路与系统的设计和产品的开发,逐渐取代了传统的手工硬件电路设计方式。

设计的系统具有体积小、重量轻、功耗小、速度快、价格低、可靠性高、设计周期短等优点。

一个功能完备的EDA设计软件加上一片普通功能的可编程逻辑芯片就可以构成以前需几百个集成电路才能构成的电子系统。

目前常用的可编程逻辑器件有CPLD(ComplexProgrammable Logic Device)和FPGA(Field Programmable Gate Array),常用的EDA软件包括VHDL,Verilog HDL,ABEL等硬件描述语言。

其中,VHDL作为IEEE 的工业标准硬件描述语言,又受到众多EDA工具厂家的支持,在电子工程领域,已成为事实上的通用硬件描述语言。

(1)PN码(m序列,n=7)发生器的VHDL源程序:library ieee;use ieee.std_logic_1164.all;entity PS7 is ——实体名为“PS7”port(clk:in std_logic;load:in std_logic;Q :out std_logic;); ——定义实体接口end PS7;architecture behav of PS7 issignal c0,c1,c2,c3,c4,c5,c6,c7:std_logic;beginprocess(clk,load)beginif clk’event and clk=’1’then ——定义时钟上升沿触发if(load=’1’)thenc7<=’0’;c6<=’0’;c5<=’0’;c4<=’0’;c3<=’0’;c2<=’0’;c1<=’0’;c0<=’1’;Q<=c7;ELSEc1<=c0;c2<=c1;c3<=c2;c4<=c3;c5<=c4;c6<=c5;c7<=c6;c0<=c7 xor c4 xor c3 xor c2; ——设置反馈方式Q<=c7;end if;end if;end process;end behav;(3)调试过程及现象:n=7的伪随机序列产生器的时序仿真波形如下图所示。

图中的“load”在“1”电平期间对伪随机序列发生器置初始信号,在“0”电平期间伪随机序列发生器进行移位操作;“CLK”表示移位寄存器的位同步信号;“Q”表示串行伪随机序列信号输出。

图3 n=7的伪随机序列产生器的时序仿真波形(4)出现的问题及解决方法:当m序列的序列的级数为n=7,序列长度为m=27-1=127,若选反馈系数的八进制数值为235,转换成二进制数值为10011101,依据建模图c0=(c7)xor(c4)xor(c3)xor(c2);Q=c;则可推出寄存器以后的状态。

如下:7c7c6 c5 c4 c3 c2 c1 c0输出1 0 0 1 1 1 0 10 0 1 1 1 0 1 0 Q=10 1 1 1 0 1 0 0 Q=01 1 1 0 1 0 0 0 Q=11 1 0 1 0 0 0 0 Q=11 0 1 0 0 0 0 0 Q=10 1 0 0 0 0 0 1 Q=11 0 0 0 0 0 1 0 Q=0续表:0 0 0 0 0 1 0 1 Q=10 0 0 0 1 0 1 1 Q=00 0 0 1 0 1 1 1 Q=00 0 1 0 1 1 1 0 Q=00 1 0 1 1 1 0 0 Q=01 0 1 1 1 0 0 1 Q=00 1 1 1 0 0 1 1 Q=11 1 1 0 0 1 1 1 Q=01 1 0 0 1 1 1 0 Q=1所以,n=7时反馈移位寄存器的输出为:1001110100000101,而这与实际仿真的波形不符(见图3)。

六.心得体会及建议:这两周进行的通信系统专业课程设计是通信工程专业的最后一次课程设计。

这次课程设计是在我们学完主要专业课程之后进行的,这使得这次课程设计能够综合以前所学的专业知识,是对前面知识的一次实际检验。

我选的是有关PN码(也就是伪随机序列)发生器的设计。

虽说我们的教材——《基于CPLD/FPGA的数字通信系统建模与设计》上面有一整套详细的设计,但是我还是从最基本的原理分析到设计原理框图,再到程序设计及仿真的完整设计流程做起,巩固已学知识,加深理解,力争做到灵活应用。

在选好课题之后,我在图书馆及互联网查找相关资料,确定详细的设计方案。

最后,参阅了大量资料后,确定了以m序列发生器的设计为例,阐述伪随机序列发生器设计的一般原理。

在通信工程应用中,常采用二进制伪随机序列。

而伪随机序列或称伪随机码,是模仿随机序列的随机特性而产生的一种玛字,也称为伪噪声序列或伪噪声码。

在数字通信中,伪随机序列有很多种,有m序列、Gold序列、M序列等。

本次课程设计,让我学到了很多东西,更让我明白了做任何事情没有正确的态度是不行的。

而且我发现有些事情看似容易,但是做起来就不象想象中的那么容易了。